Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga004t-i-ml |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | ile<br>ame | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----|------------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|-------|--------|-------|---------------|

| RCC | N          | 0740 | TRAPR  | IOPUWR | _      | —      |        | —      | CM     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE  | BOR    | POR   | (Note 1)      |

| OSC | CON        | 0742 |        | COSC2  | COSC1  | COSC0  |        | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | —     | CF    | —     | SOSCEN | OSWEN | (Note 2)      |

| CLK | DIV        | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       |        | —      | —     | —     | —     | —      |       | 3140          |

| OSC | TUN        | 0748 |        | _      | —      | _      |        | _      |        | _      |         |        | TUN5   | TUN4  | TUN3  | TUN2  | TUN1   | TUN0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by the type of Reset.

#### TABLE 4-23: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  |        | —      | _      | _     | _     |       | ERASE | -     | _     | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | _      | _      | _      | _      | _      | _      | -     |       |       |       |       | NVMKE | Y<7:0> |        |        |        | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for a POR only. The value on other Reset states is dependent on the state of the memory write or erase operations at the time of Reset.

#### TABLE 4-24: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|-------|--------|--------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —     |        | ADC1MD | 0000          |

| PMD2      | 0772 | -      | -      | _      | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | _      | _     | _     | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD  | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCPMD |       | —     | —      |        | —     | I2C2MD | —      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 7-31: | INTTREG: INTERRUPT CONTROL AND STATUS REGISTER |

|----------------|------------------------------------------------|

|----------------|------------------------------------------------|

| R-0                          | U-0                                                                   | R/W-0                                                                            | U-0                                           | R-0                                                     | R-0              | R-0                 | R-0            |  |  |

|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|------------------|---------------------|----------------|--|--|

| CPUIRQ                       | _                                                                     | VHOLD                                                                            | _                                             | ILR3                                                    | ILR2             | ILR1                | ILR0           |  |  |

| bit 15                       |                                                                       |                                                                                  |                                               |                                                         |                  |                     | bit 8          |  |  |

| U-0                          | R-0                                                                   | R-0                                                                              | R-0                                           | R-0                                                     | R-0              | R-0                 | R-0            |  |  |

| _                            | VECNUM6                                                               | VECNUM5                                                                          | VECNUM4                                       | VECNUM3                                                 | VECNUM2          | VECNUM1             | VECNUM0        |  |  |

| bit 7                        | ·                                                                     |                                                                                  |                                               | ·                                                       |                  |                     | bit (          |  |  |

| Legend:                      |                                                                       |                                                                                  |                                               |                                                         |                  |                     |                |  |  |

| R = Readal                   | ole bit                                                               | W = Writable                                                                     | pit                                           | U = Unimplem                                            | nented bit, read | l as '0'            |                |  |  |

| -n = Value a                 | at POR                                                                | '1' = Bit is set                                                                 |                                               | '0' = Bit is clea                                       | ared             | x = Bit is unkn     | nown           |  |  |

|                              | when the<br>0 = No interru                                            | CPU priority is<br>upt request is u                                              | higher than th<br>nacknowledge                | has not yet bee<br>he interrupt prior<br>ed             |                  | eu by the CPU       | , uns nappen   |  |  |

| bit 14                       | Unimplemented: Read as '0'                                            |                                                                                  |                                               |                                                         |                  |                     |                |  |  |

| bit 13                       | VHOLD: Vect                                                           | or Number Cap                                                                    | ture Configura                                | ation bit                                               |                  |                     |                |  |  |

|                              | 0 = VECNUM                                                            | 1x bits contain t                                                                | he value of the                               | e highest priority<br>last Acknowled<br>PU, even if oth | dged interrupt ( | i.e., the last inte | errupt that ha |  |  |

| bit 12                       |                                                                       | ted: Read as 'd                                                                  | -                                             |                                                         | ·                | 1 07                |                |  |  |

|                              | II D -2.0 - No                                                        |                                                                                  |                                               |                                                         |                  |                     |                |  |  |

| bit 11-8                     | 1111 = CPU  <br>•<br>•<br>0001 = CPU                                  | w CPU Interrup<br>Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit    | / Level is 15<br>/ Level is 1                 | l bits                                                  |                  |                     |                |  |  |

|                              | 1111 = CPU  <br>•<br>•<br>0001 = CPU  <br>0000 = CPU                  | Interrupt Priorit                                                                | / Level is 15<br>/ Level is 1<br>/ Level is 0 | l bits                                                  |                  |                     |                |  |  |

| bit 11-8<br>bit 7<br>bit 6-0 | 1111 = CPU  <br>•<br>•<br>0001 = CPU  <br>0000 = CPU  <br>Unimplement | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit | / Level is 15<br>/ Level is 1<br>/ Level is 0 | l bits<br>D bits (pending                               | vector number    | - is VECNUM +       | 8)             |  |  |

## 8.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 8-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. The Clock Divider register (Register 8-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The FRC Oscillator Tune register (Register 8-3) allows the user to fine-tune the FRC oscillator over a range of approximately ±12%.

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | U-0 | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|-----|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | —   | CF     | —   | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |     |        | bit 0 |

| Legend:           | CO = Clearable Only bit | SO = Settable Only bit     |                    |

|-------------------|-------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15 Unimplemented: Read as '0'

- bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

#### bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

#### REGISTER 10-7: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | —     | —     | —     | —     | —     |

| bit 15 |     |     |       |       | •     |       | bit 8 |

|        |     |     |       |       |       |       |       |

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | IC5R4 | IC5R3 | IC5R2 | IC5R1 | IC5R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 IC5R<4:0>: Assign Input Capture 5 (IC5) to the Corresponding RPn Pin bits

#### REGISTER 10-8: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

|                                   |     |                  |                                    | <b>D A A A</b>                          | D 444 4 | <b>D</b> 4 4 4 | D 11/ 1 |

|-----------------------------------|-----|------------------|------------------------------------|-----------------------------------------|---------|----------------|---------|

| U-0                               | U-0 | U-0              | R/W-1                              | R/W-1                                   | R/W-1   | R/W-1          | R/W-1   |

|                                   | —   | —                | OCFBR4                             | OCFBR3                                  | OCFBR2  | OCFBR1         | OCFBR0  |

| bit 15                            |     |                  |                                    |                                         |         |                | bit 8   |

|                                   |     |                  |                                    |                                         |         |                |         |

| U-0                               | U-0 | U-0              | R/W-1                              | R/W-1                                   | R/W-1   | R/W-1          | R/W-1   |

|                                   | —   | —                | OCFAR4                             | OCFAR3                                  | OCFAR2  | OCFAR1         | OCFAR0  |

| bit 7                             |     |                  |                                    |                                         |         |                | bit 0   |

|                                   |     |                  |                                    |                                         |         |                |         |

| Legend:                           |     |                  |                                    |                                         |         |                |         |

| R = Readable bit W = Writable bit |     | oit              | U = Unimplemented bit, read as '0' |                                         |         |                |         |

| -n = Value at I                   | POR | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknowr |         |                | nown    |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 OCFBR<4:0>: Assign Output Compare Fault B (OCFB) to the Corresponding RPn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

#### REGISTER 10-23: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _      | —   | —   | RP17R4 <sup>(1)</sup> | RP17R3 <sup>(1)</sup> | RP17R2 <sup>(1)</sup> | RP17R1 <sup>(1)</sup> | RP17R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | —   | —   | RP16R4 <sup>(1)</sup> | RP16R3 <sup>(1)</sup> | RP16R2 <sup>(1)</sup> | RP16R1 <sup>(1)</sup> | RP16R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|           |                            |

| bit 12-8 | <b>RP17R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP17 Output Pin bits <sup>(1)</sup> (see Table 10-3 for peripheral function numbers) |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-5  | Unimplemented: Read as '0'                                                                                                                              |

| bit 4-0  | <b>RP16R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP16 Output Pin bits <sup>(1)</sup>                                                  |

(see Table 10-3 for peripheral function numbers)

#### REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | —   | RP19R4 <sup>(1)</sup> | RP19R3 <sup>(1)</sup> | RP19R2 <sup>(1)</sup> | RP19R1 <sup>(1)</sup> | RP19R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | —   | —   | RP18R4 <sup>(1)</sup> | RP18R3 <sup>(1)</sup> | RP18R2 <sup>(1)</sup> | RP18R1 <sup>(1)</sup> | RP18R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP19R<4:0>:** Peripheral Output Function is Assigned to RP19 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP18R<4:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

- Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

| U-0                                | U-0        | U-0             | R/W-0                                   | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|------------------------------------|------------|-----------------|-----------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _                                  |            | _               | RP25R4 <sup>(1)</sup>                   | RP25R3 <sup>(1)</sup> | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> |

| bit 15                             |            |                 |                                         |                       |                       |                       | bit 8                 |

|                                    |            |                 |                                         |                       |                       |                       |                       |

| U-0                                | U-0        | U-0             | R/W-0                                   | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| _                                  |            | —               | RP24R4 <sup>(1)</sup>                   | RP24R3 <sup>(1)</sup> | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> |

| bit 7                              |            |                 | •                                       | •                     |                       |                       | bit 0                 |

|                                    |            |                 |                                         |                       |                       |                       |                       |

| Legend:                            |            |                 |                                         |                       |                       |                       |                       |

| R = Readable                       | e bit      | W = Writable    | bit                                     | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at POR '1' = Bit is set |            |                 | '0' = Bit is cleared x = Bit is unknown |                       |                       |                       |                       |

|                                    |            |                 |                                         |                       |                       |                       |                       |

| bit 15-13                          | Unimplemen | ted: Read as '@ | י'                                      |                       |                       |                       |                       |

#### REGISTER 10-27: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

bit 15-13 Unimplemented: Read as '0

RP25R<4:0>: Peripheral Output Function is Assigned to RP25 Output Pin bits<sup>(1)</sup> bit 12-8 (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

RP24R<4:0>: Peripheral Output Function is Assigned to RP24 Output Pin bits<sup>(1)</sup> bit 4-0 (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

| R/W-0        | U-0                                                                              | R/W-0                                                                     | U-0                                                             | U-0              | U-0             | U-0              | U-0   |

|--------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|------------------|-----------------|------------------|-------|

| TON          |                                                                                  | TSIDL                                                                     | _                                                               | _                |                 | _                |       |

| bit 15       |                                                                                  |                                                                           |                                                                 |                  |                 |                  | bit 8 |

|              |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| U-0          | R/W-0                                                                            | R/W-0                                                                     | R/W-0                                                           | U-0              | R/W-0           | R/W-0            | U-0   |

| —            | TGATE                                                                            | TCKPS1                                                                    | TCKPS0                                                          | —                | TSYNC           | TCS              |       |

| bit 7        |                                                                                  |                                                                           |                                                                 |                  |                 |                  | bit ( |

| Legend:      |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| R = Readab   | le bit                                                                           | W = Writable                                                              | bit                                                             | U = Unimpler     | nented bit, rea | d as '0'         |       |

| -n = Value a | t POR                                                                            | '1' = Bit is set                                                          |                                                                 | '0' = Bit is cle |                 | x = Bit is unkno | own   |

|              |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| bit 15       | TON: Timer1                                                                      | On bit                                                                    |                                                                 |                  |                 |                  |       |

|              | 1 = Starts 16                                                                    |                                                                           |                                                                 |                  |                 |                  |       |

|              | 0 = Stops 16                                                                     | 6-bit Timer1                                                              |                                                                 |                  |                 |                  |       |

| bit 14       | Unimplemer                                                                       | nted: Read as '                                                           | )'                                                              |                  |                 |                  |       |

| bit 13       | TSIDL: Time                                                                      | r1 Stop in Idle N                                                         | lode bit                                                        |                  |                 |                  |       |

|              |                                                                                  | ues module op<br>s module opera                                           |                                                                 |                  | le mode         |                  |       |

| bit 12-7     |                                                                                  | nted: Read as '                                                           |                                                                 |                  |                 |                  |       |

| bit 6        | TGATE: Time                                                                      | er1 Gated Time                                                            | Accumulation                                                    | Enable bit       |                 |                  |       |

|              | When TCS =                                                                       | 1:                                                                        |                                                                 |                  |                 |                  |       |

|              | This bit is ign                                                                  | ored.                                                                     |                                                                 |                  |                 |                  |       |

|              | When TCS =                                                                       |                                                                           |                                                                 |                  |                 |                  |       |

|              |                                                                                  | me accumulatio<br>me accumulatio                                          |                                                                 |                  |                 |                  |       |

| bit 5-4      |                                                                                  | -: Timer1 Input                                                           |                                                                 | e Select bits    |                 |                  |       |

|              | 11 <b>= 1:256</b>                                                                | ·                                                                         |                                                                 |                  |                 |                  |       |

|              | 10 <b>= 1:64</b>                                                                 |                                                                           |                                                                 |                  |                 |                  |       |

|              | 01 = 1:8                                                                         |                                                                           |                                                                 |                  |                 |                  |       |

|              | 00 = 1:1                                                                         |                                                                           |                                                                 |                  |                 |                  |       |

| bit 3        | -                                                                                | nted: Read as '                                                           | )′                                                              |                  |                 |                  |       |

|              |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| bit 2        |                                                                                  | er1 External Clo                                                          |                                                                 | hronization Sel  | ect bit         |                  |       |

|              | When TCS =                                                                       | 1:                                                                        | ock Input Sync                                                  | hronization Sel  | ect bit         |                  |       |

|              | <u>When TCS =</u><br>1 = Synchro                                                 | <u>1:</u><br>nizes external o                                             | ock Input Sync                                                  |                  | ect bit         |                  |       |

|              | <u>When TCS =</u><br>1 = Synchro<br>0 = Does no                                  | <u>1:</u><br>onizes external o<br>ot synchronize e                        | ock Input Sync                                                  |                  | ect bit         |                  |       |

|              | <u>When TCS =</u><br>1 = Synchro                                                 | <u>1:</u><br>onizes external o<br>ot synchronize e<br><u>0:</u>           | ock Input Sync                                                  |                  | ect bit         |                  |       |

|              | When TCS =<br>1 = Synchro<br>0 = Does no<br>When TCS =<br>This bit is ign        | <u>1:</u><br>onizes external o<br>ot synchronize e<br><u>0:</u>           | ock Input Sync<br>clock input<br>external clock i               |                  | ect bit         |                  |       |

| bit 2        | When TCS =1 = Synchro0 = Does noWhen TCS =This bit is ignTCS: Timer11 = External | <u>1:</u><br>onizes external o<br>ot synchronize e<br><u>0:</u><br>nored. | ock Input Sync<br>clock input<br>external clock i<br>Gelect bit | nput             | ect bit         |                  |       |

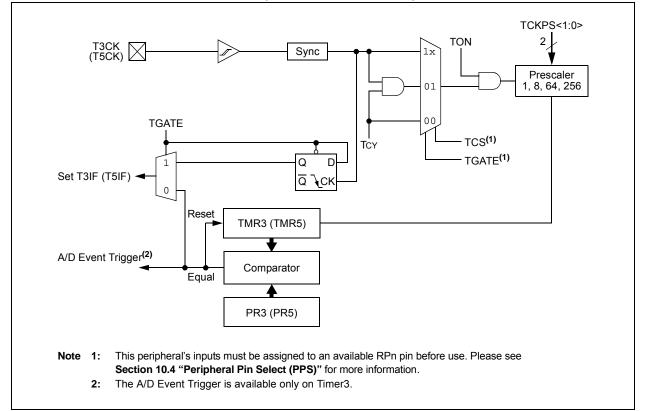

FIGURE 12-3: TIMER3 AND TIMER5 (16-BIT SYNCHRONOUS) BLOCK DIAGRAM

NOTES:

## 14.4 Output Compare Register

### REGISTER 14-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER

| U-0 | R/W-0  | U-0      | U-0                           | U-0                 | U-0                 | U-0                                                                                                                                          |

|-----|--------|----------|-------------------------------|---------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| —   | OCSIDL | —        | —                             | _                   | —                   | —                                                                                                                                            |

|     |        |          |                               |                     |                     | bit 8                                                                                                                                        |

|     |        |          |                               |                     |                     |                                                                                                                                              |

| U-0 | U-0    | R-0, HC  | R/W-0                         | R/W-0               | R/W-0               | R/W-0                                                                                                                                        |

|     | —      | OCFLT    | OCTSEL                        | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup> | OCM0 <sup>(1)</sup>                                                                                                                          |

|     |        |          |                               |                     |                     | bit 0                                                                                                                                        |

|     | _      | — OCSIDL | — OCSIDL —<br>U-0 U-0 R-0, HC | - OCSIDL            | - OCSIDL            | −         OCSIDL         −         −         −         −           U-0         U-0         R-0, HC         R/W-0         R/W-0         R/W-0 |

| Legend:           | HC = Hardware Clearable bit                         |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Output Compare x Stop in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in HW only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 3     | OCTSEL: Output Compare x Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | <ul> <li>1 = Timer3 is the clock source for Output Compare x</li> <li>0 = Timer2 is the clock source for Output Compare x</li> <li>Refer to the device data sheet for specific time bases available to the output compare module.</li> </ul>                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0   | OCM<2:0>: Output Compare x Mode Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = PWM mode on OCx; Fault pin, OCFx, is enabled<sup>(2)</sup></li> <li>110 = PWM mode on OCx; Fault pin, OCFx, is disabled<sup>(2)</sup></li> <li>101 = Initializes OCx pin low, generates continuous output pulses on OCx pin</li> <li>100 = Initializes OCx pin low, generates single output pulse on OCx pin</li> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initializes OCx pin high, compare event forces OCx pin low</li> <li>001 = Initializes OCx pin low, compare event forces OCx pin high</li> <li>000 = Output compare channel is disabled</li> </ul> |

| Note 1:   | RPORx (OCx) must be configured to an available RPn pin. For more information, see Section 10.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- "Peripheral Pin Select (PPS)".

- 2: The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

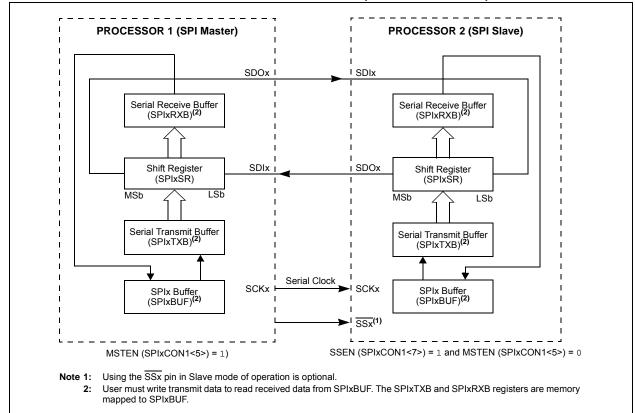

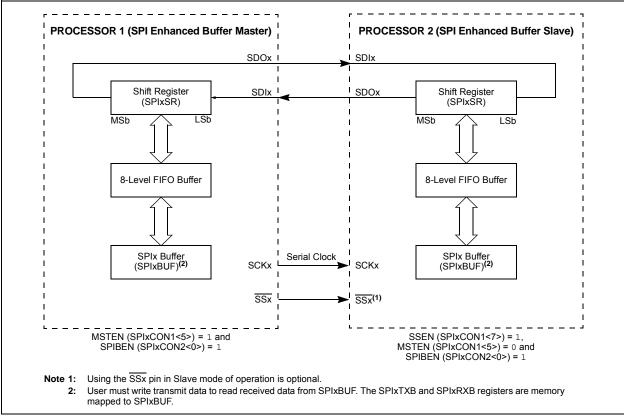

### FIGURE 15-3: SPIx MASTER/SLAVE CONNECTION (STANDARD MODE)

## REGISTER 19-6: WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   |     | —   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                       |

|-----------|------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits      |

|           | Contains a value from 0 to 6.                                    |

| bit 7-6   | Unimplemented: Read as '0'                                       |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|           | Contains a value from 0 to 2.                                    |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|           | Contains a value from 0 to 9.                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 19-7: MINSEC: MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

© 2010-2013 Microchip Technology Inc.

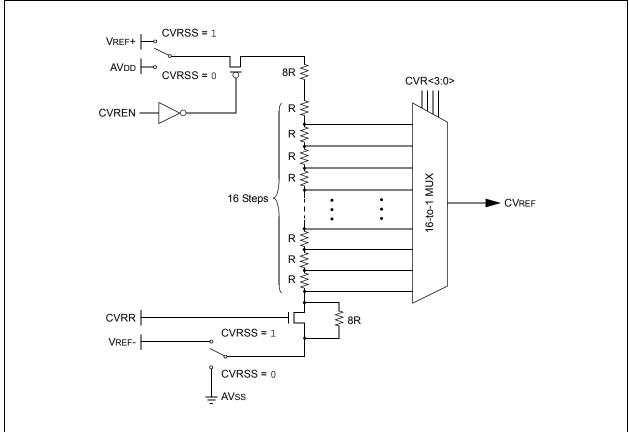

## 23.0 COMPARATOR VOLTAGE REFERENCE

| Note: | This data sheet summarizes the features of |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|

|       | this group of PIC24F devices. It is not    |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |

|       | source. For more information, refer to     |  |  |  |  |

|       | the "PIC24F Family Reference Manual",      |  |  |  |  |

|       | "Comparator Voltage Reference              |  |  |  |  |

|       | Module" (DS39709).                         |  |  |  |  |

### 23.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

## FIGURE 23-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 24.0 SPECIAL FEATURES

- Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the following sections of the *"PIC24F Family Reference Manual"*.

**"Watchdog Timer (WDT)"** (DS39697)

**"High-Level Device Integration"** (DS39719)

- "Programming and Diagnostics" (DS39716)

PIC24FJ64GA004 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- · Watchdog Timer (WDT)

- Code Protection

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming

- In-Circuit Emulation

## 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location, F80000h. A complete list of locations is shown in Table 24-1. A detailed explanation of the various bit functions is provided in Register 24-1 through Register 24-4.

Note that address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh), which can only be accessed using table reads and table writes.

#### 24.1.1 CONSIDERATIONS FOR CONFIGURING PIC24FJ64GA004 FAMILY DEVICES

In PIC24FJ64GA004 family devices, the configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the two words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 24-1. These are packed representations of the actual device Configuration bits, whose actual locations are distributed among five locations in configuration space. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets.

Note: Configuration data is reloaded on all types of device Resets.

#### TABLE 24-1: FLASH CONFIGURATION WORD LOCATIONS FOR PIC24FJ64GA004 FAMILY DEVICES

| Device      | Configuration Word<br>Addresses |         |  |  |

|-------------|---------------------------------|---------|--|--|

|             | 1                               | 2       |  |  |

| PIC24FJ16GA | 002BFEh                         | 002BFCh |  |  |

| PIC24FJ32GA | 0057FEh                         | 0057FCh |  |  |

| PIC24FJ48GA | 0083FEh                         | 0083FCh |  |  |

| PIC24FJ64GA | 00ABFEh                         | 00ABFCh |  |  |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The Configuration bits are reloaded from the Flash Configuration Word on any device Reset.

The upper byte of both Flash Configuration Words in program memory should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

## 24.4 JTAG Interface

PIC24FJ64GA004 family devices implement a JTAG interface, which supports boundary scan device testing.

## 24.5 Program Verification and Code Protection

For all devices in the PIC24FJ64GA004 family, the on-chip program memory space is treated as a single block. Code protection for this block is controlled by one Configuration bit, GCP. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

Write protection is controlled by the GWRP bit in Configuration Word 1. When GWRP is programmed to '0', internal write and erase operations to program memory are blocked.

#### 24.5.1 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against inadvertent or unwanted changes, or reads in two ways. The primary protection method is the same as that of the RP registers – shadow registers contain a complimentary value which is constantly compared with the actual value.

To safeguard against unpredictable events, Configuration bit changes, resulting from individual cell level disruptions (such as ESD events), will cause a parity error and trigger a device Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. When the GCP bit is set, the source data for device configuration is also protected as a consequence.

## 24.6 In-Circuit Serial Programming

PIC24FJ64GA004 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGCx) and data (PGDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 24.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the EMUCx (Emulation/Debug Clock) and EMUDx (Emulation/Debug Data) pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss, PGCx, PGDx and the EMUDx/EMUCx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

### 27.1 DC Characteristics

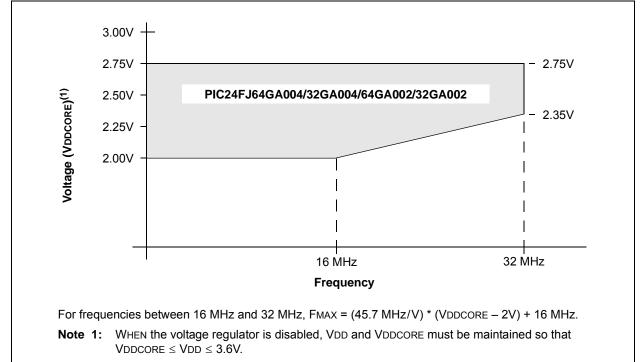

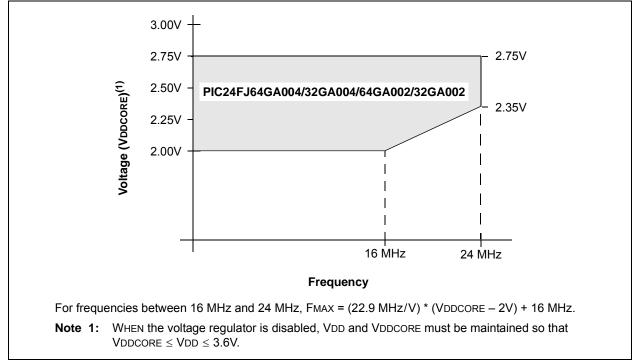

## FIGURE 27-2: PIC24FJ64GA004 FAMILY VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE)

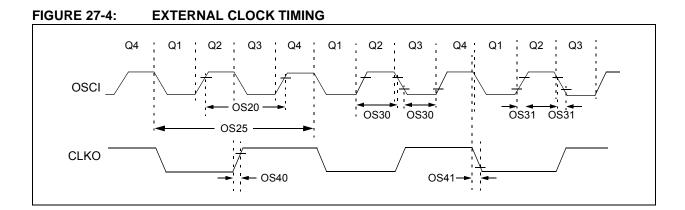

### TABLE 27-15: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CH        | ARACT | ERISTICS                              | Standard Operating ter | -                  |     | <b>3.6V (unless otherwise stated)</b><br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended |                                                |

|--------------|-------|---------------------------------------|------------------------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                        | Min                    | Typ <sup>(1)</sup> | Max | Units                                                                                                                  | Conditions                                     |

| OS10         | Fosc  | External CLKI Frequency               | DC                     | _                  | 32  | MHz                                                                                                                    | EC, $-40^{\circ}C \le TA \le +85^{\circ}C$     |

|              |       | (External clocks allowed              | 4                      | —                  | 8   | MHz                                                                                                                    | ECPLL, $-40^{\circ}C \le TA \le +85^{\circ}C$  |

|              |       | only in EC mode)                      | DC                     | —                  | 24  | MHz                                                                                                                    | EC, $-40^{\circ}C \le TA \le +125^{\circ}C$    |

|              |       |                                       | 4                      | —                  | 6   | MHz                                                                                                                    | ECPLL, -40°C $\leq$ TA $\leq$ +125°C           |

|              |       | Oscillator Frequency                  | 3                      | _                  | 10  | MHz                                                                                                                    | ХТ                                             |

|              |       |                                       | 3                      | —                  | 8   | MHz                                                                                                                    | XTPLL, $-40^{\circ}C \le TA \le +85^{\circ}C$  |

|              |       |                                       | 10                     | —                  | 32  | MHz                                                                                                                    | HS, $-40^{\circ}C \le TA \le +85^{\circ}C$     |

|              |       |                                       | 31                     | —                  | 33  | kHz                                                                                                                    | SOSC                                           |

|              |       |                                       | 3                      | —                  | 6   | MHz                                                                                                                    | XTPLL, $-40^{\circ}C \le TA \le +125^{\circ}C$ |

|              |       |                                       | 10                     | —                  | 24  | MHz                                                                                                                    | HS, $-40^{\circ}C \le TA \le +125^{\circ}C$    |

| OS20         | Tosc  | Tosc = 1/Fosc                         | _                      | _                  | _   | _                                                                                                                      | See Parameter OS10 for                         |

|              |       |                                       |                        |                    |     |                                                                                                                        | Fosc value                                     |

| OS25         | Тсү   | Instruction Cycle Time <sup>(2)</sup> | 62.5                   | _                  | DC  | ns                                                                                                                     |                                                |

| OS30         | TosL, | External Clock In (OSCI)              | 0.45 x Tosc            | _                  | _   | ns                                                                                                                     | EC                                             |

|              | TosH  | High or Low Time                      |                        |                    |     |                                                                                                                        |                                                |

| OS31         | TosR, | External Clock In (OSCI)              | _                      |                    | 20  | ns                                                                                                                     | EC                                             |

|              | TosF  | Rise or Fall Time                     |                        |                    |     |                                                                                                                        |                                                |

| OS40         | TckR  | CLKO Rise Time <sup>(3)</sup>         |                        | 6                  | 10  | ns                                                                                                                     |                                                |

| OS41         | TckF  | CLKO Fall Time <sup>(3)</sup>         | _                      | 6                  | 10  | ns                                                                                                                     |                                                |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- **3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

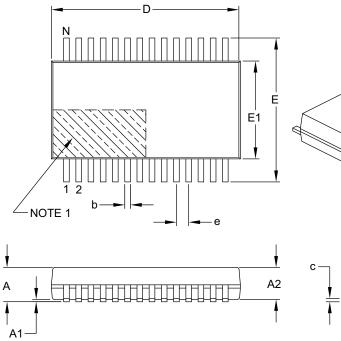

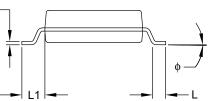

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |       |       |

|--------------------------|-------------|----------|-------|-------|

| Dimension Limits         |             | MIN      | NOM   | MAX   |

| Number of Pins           | Ν           | 28       |       |       |

| Pitch                    | е           | 0.65 BSC |       |       |

| Overall Height           | А           | _        | _     | 2.00  |

| Molded Package Thickness | A2          | 1.65     | 1.75  | 1.85  |

| Standoff                 | A1          | 0.05     | -     | -     |

| Overall Width            | E           | 7.40     | 7.80  | 8.20  |

| Molded Package Width     | E1          | 5.00     | 5.30  | 5.60  |

| Overall Length           | D           | 9.90     | 10.20 | 10.50 |

| Foot Length              | L           | 0.55     | 0.75  | 0.95  |

| Footprint                | L1          | 1.25 REF |       |       |

| Lead Thickness           | с           | 0.09     | -     | 0.25  |

| Foot Angle               | φ           | 0°       | 4°    | 8°    |

| Lead Width               | b           | 0.22     | _     | 0.38  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

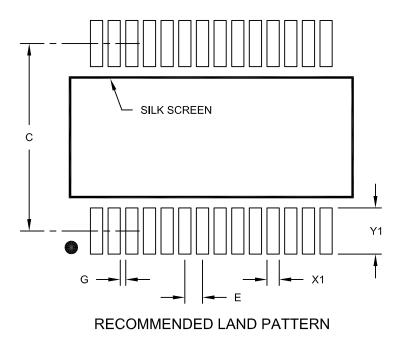

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A