Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

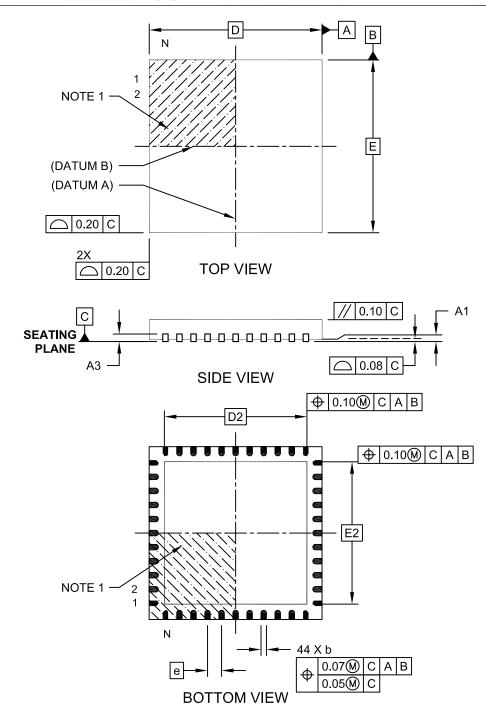

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj48ga002-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                               | Pin Number    |                    |     |                  |                                                                      |

|----------|-------------------------------|---------------|--------------------|-----|------------------|----------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer  | Description                                                          |

| AN0      | 2                             | 27            | 19                 |     | ANA              | A/D Analog Inputs.                                                   |

| AN1      | 3                             | 28            | 20                 | I   | ANA              |                                                                      |

| AN2      | 4                             | 1             | 21                 | Ι   | ANA              |                                                                      |

| AN3      | 5                             | 2             | 22                 | I   | ANA              |                                                                      |

| AN4      | 6                             | 3             | 23                 | Ι   | ANA              |                                                                      |

| AN5      | 7                             | 4             | 24                 | Ι   | ANA              |                                                                      |

| AN6      | _                             | _             | 25                 | I   | ANA              |                                                                      |

| AN7      |                               | _             | 26                 | Ι   | ANA              |                                                                      |

| AN8      |                               | _             | 27                 | Ι   | ANA              |                                                                      |

| AN9      | 26                            | 23            | 15                 | I   | ANA              |                                                                      |

| AN10     | 25                            | 22            | 14                 | Ι   | ANA              |                                                                      |

| AN11     | 24                            | 21            | 11                 | Ι   | ANA              |                                                                      |

| AN12     | 23                            | 20            | 10                 | I   | ANA              |                                                                      |

| ASCL1    | 15                            | 12            | 42                 | I/O | l <sup>2</sup> C | Alternate I2C1 Synchronous Serial Clock Input/Output. <sup>(1)</sup> |

| ASDA1    | 14                            | 11            | 41                 | I/O | l <sup>2</sup> C | Alternate I2C2 Synchronous Serial Clock Input/Output. (1)            |

| AVDD     | —                             | _             | 17                 | Р   | _                | Positive Supply for Analog Modules.                                  |

| AVss     | —                             | _             | 16                 | Р   | _                | Ground Reference for Analog Modules.                                 |

| C1IN-    | 6                             | 3             | 23                 | Ι   | ANA              | Comparator 1 Negative Input.                                         |

| C1IN+    | 7                             | 4             | 24                 | Ι   | ANA              | Comparator 1 Positive Input.                                         |

| C2IN-    | 4                             | 1             | 21                 | I   | ANA              | Comparator 2 Negative Input.                                         |

| C2IN+    | 5                             | 2             | 22                 | I   | ANA              | Comparator 2 Positive Input.                                         |

| CLKI     | 9                             | 6             | 30                 | I   | ANA              | Main Clock Input Connection.                                         |

| CLKO     | 10                            | 7             | 31                 | 0   | _                | System Clock Output.                                                 |

Legend: TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

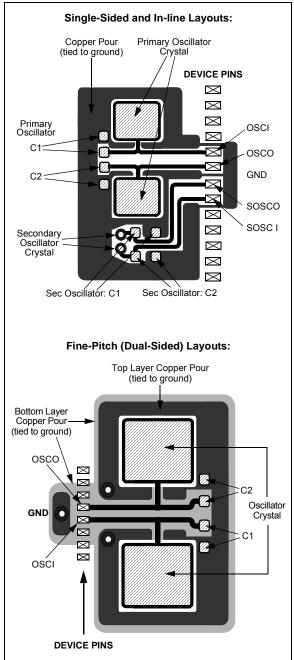

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-5:

### PLACEMENT OF THE OSCILLATOR CIRCUIT

SUGGESTED

### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

NOTES:

| R/W-0             | U-0                               | U-0                                                                                                            | U-0                                 | U-0               | U-0             | U-0              | U-0   |  |

|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-----------------|------------------|-------|--|

| NSTDIS            | —                                 | —                                                                                                              | —                                   | —                 | _               | —                | _     |  |

| bit 15            |                                   |                                                                                                                |                                     |                   |                 |                  | bit 8 |  |

|                   |                                   |                                                                                                                |                                     |                   |                 |                  |       |  |

| U-0               | U-0                               | U-0                                                                                                            | R/W-0                               | R/W-0             | R/W-0           | R/W-0            | U-0   |  |

|                   |                                   | —                                                                                                              | MATHERR                             | ADDRERR           | STKERR          | OSCFAIL          |       |  |

| bit 7             |                                   |                                                                                                                |                                     |                   |                 |                  | bit 0 |  |

|                   |                                   |                                                                                                                |                                     |                   |                 |                  |       |  |

| Legend:           |                                   |                                                                                                                |                                     |                   |                 |                  |       |  |

| R = Readab        | le bit                            | W = Writable                                                                                                   | bit                                 | U = Unimplem      | ented bit, read | d as '0'         |       |  |

| -n = Value a      | t POR                             | '1' = Bit is set                                                                                               |                                     | '0' = Bit is clea | ared            | x = Bit is unkno | own   |  |

|                   |                                   |                                                                                                                |                                     |                   |                 |                  |       |  |

| bit 15            |                                   | rrupt Nesting E                                                                                                |                                     |                   |                 |                  |       |  |

|                   |                                   | nesting is disat<br>nesting is enab                                                                            |                                     |                   |                 |                  |       |  |

| bit 14-5          |                                   | •                                                                                                              |                                     |                   |                 |                  |       |  |

| bit 14-5<br>bit 4 | •                                 | ted: Read as '                                                                                                 |                                     |                   |                 |                  |       |  |

| DIL 4             |                                   | trap has occur                                                                                                 | <sup>-</sup> Trap Status bit<br>red | L                 |                 |                  |       |  |

|                   |                                   | trap has not oc                                                                                                |                                     |                   |                 |                  |       |  |

| bit 3             | ADDRERR: A                        | Address Error ⊺                                                                                                | Frap Status bit                     |                   |                 |                  |       |  |

|                   | 1 = Address e                     | error trap has c                                                                                               | occurred                            |                   |                 |                  |       |  |

|                   | 0 = Address e                     | error trap has r                                                                                               | ot occurred                         |                   |                 |                  |       |  |

| bit 2             |                                   | ack Error Trap                                                                                                 |                                     |                   |                 |                  |       |  |

|                   | 1 = Stack error trap has occurred |                                                                                                                |                                     |                   |                 |                  |       |  |

| bit 1             |                                   | <ul> <li>0 = Stack error trap has not occurred</li> <li>OSCFAIL: Oscillator Failure Trap Status bit</li> </ul> |                                     |                   |                 |                  |       |  |

|                   |                                   | failure trap ha                                                                                                | •                                   |                   |                 |                  |       |  |

|                   |                                   | failure trap ha                                                                                                |                                     |                   |                 |                  |       |  |

| bit 0             |                                   | ted: Read as '                                                                                                 |                                     |                   |                 |                  |       |  |

|                   | •                                 |                                                                                                                |                                     |                   |                 |                  |       |  |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| U-0            | U-0                                                                                                | R/W-0                                                                                | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0                 |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------|-----------------------|--|--|--|

| _              | _                                                                                                  | AD1IE                                                                                | U1TXIE           | U1RXIE            | SPI1IE          | SPF1IE          | T3IE                  |  |  |  |

| bit 15         |                                                                                                    |                                                                                      |                  | •                 |                 |                 | bit                   |  |  |  |

|                |                                                                                                    |                                                                                      |                  |                   |                 |                 |                       |  |  |  |

| R/W-0          | R/W-0                                                                                              | R/W-0                                                                                | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0                 |  |  |  |

| T2IE           | OC2IE                                                                                              | IC2IE                                                                                | —                | T1IE              | OC1IE           | IC1IE           | INT0IE <sup>(1)</sup> |  |  |  |

| bit 7          |                                                                                                    |                                                                                      |                  |                   |                 |                 | bit                   |  |  |  |

| Legend:        |                                                                                                    |                                                                                      |                  |                   |                 |                 |                       |  |  |  |

| R = Readable   | e bit                                                                                              | W = Writable                                                                         | bit              | U = Unimplem      | ented bit, read | l as '0'        |                       |  |  |  |

| -n = Value at  | POR                                                                                                | '1' = Bit is set                                                                     |                  | '0' = Bit is clea | red             | x = Bit is unkn | iown                  |  |  |  |

|                |                                                                                                    |                                                                                      |                  |                   |                 |                 |                       |  |  |  |

| bit 15-14      | -                                                                                                  | ted: Read as '                                                                       |                  |                   |                 |                 |                       |  |  |  |

| bit 13         |                                                                                                    |                                                                                      | nplete Interrup  | t Enable bit      |                 |                 |                       |  |  |  |

|                | •                                                                                                  | equest is enab<br>equest is not e                                                    |                  |                   |                 |                 |                       |  |  |  |

| bit 12         | -                                                                                                  | -                                                                                    | r Interrupt Enal | hle hit           |                 |                 |                       |  |  |  |

|                |                                                                                                    | equest is enab                                                                       | •                |                   |                 |                 |                       |  |  |  |

|                |                                                                                                    | equest is not e                                                                      |                  |                   |                 |                 |                       |  |  |  |

| bit 11         | U1RXIE: UART1 Receiver Interrupt Enable bit                                                        |                                                                                      |                  |                   |                 |                 |                       |  |  |  |

|                | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                                                                      |                  |                   |                 |                 |                       |  |  |  |

| bit 10         | -                                                                                                  | -                                                                                    |                  | Enable bit        |                 |                 |                       |  |  |  |

|                |                                                                                                    | PI1IE: SPI1 Transfer Complete Interrupt Enable bit<br>= Interrupt request is enabled |                  |                   |                 |                 |                       |  |  |  |

|                | •                                                                                                  | equest is not e                                                                      |                  |                   |                 |                 |                       |  |  |  |

| bit 9          |                                                                                                    | Fault Interrup                                                                       |                  |                   |                 |                 |                       |  |  |  |

|                |                                                                                                    | equest is enab<br>equest is not e                                                    |                  |                   |                 |                 |                       |  |  |  |

| bit 8          | -                                                                                                  | Interrupt Enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

|                |                                                                                                    | equest is enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

|                | 0 = Interrupt r                                                                                    | equest is not e                                                                      | nabled           |                   |                 |                 |                       |  |  |  |

| bit 7          |                                                                                                    | Interrupt Enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

|                | •                                                                                                  | equest is enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

| bit 6          | •                                                                                                  | equest is not e                                                                      | annel 2 Interru  | unt Enable bit    |                 |                 |                       |  |  |  |

|                | -                                                                                                  | equest is enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

|                |                                                                                                    | equest is not e                                                                      |                  |                   |                 |                 |                       |  |  |  |

| bit 5          | IC2IE: Input C                                                                                     | Capture Chann                                                                        | el 2 Interrupt E | nable bit         |                 |                 |                       |  |  |  |

|                | •                                                                                                  | equest is enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

| L:1 1          | -                                                                                                  | equest is not e                                                                      |                  |                   |                 |                 |                       |  |  |  |

| bit 4<br>bit 3 | -                                                                                                  | ted: Read as '                                                                       |                  |                   |                 |                 |                       |  |  |  |

| UIL J          | I IIE. IIIIief I                                                                                   | Interrupt Enab                                                                       |                  |                   |                 |                 |                       |  |  |  |

|                | 1 = Interrupt r                                                                                    | equest is enab                                                                       | led              |                   |                 |                 |                       |  |  |  |

#### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

**Note 1:** If INTxIE = 1, this external interrupt input must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

|                    | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0                                | R/W-1            | R/W-0           | R/W-0  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-----------------|--------|

|                    | T4IP2                                                                                                                                                                | T4IP1                                                                                                                                                                    | T4IP0                                                                                                  | _                                  | OC4IP2           | OC4IP1          | OC4IP0 |

| bit 15             |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 | bit 8  |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| U-0                | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0                                | U-0              | U-0             | U-0    |

| <br>bit 7          | OC3IP2                                                                                                                                                               | OC3IP1                                                                                                                                                                   | OC3IP0                                                                                                 | —                                  | _                | _               | bit (  |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 | Ditt   |

| Legend:            |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| R = Readab         | ole bit                                                                                                                                                              | W = Writable                                                                                                                                                             | bit                                                                                                    | U = Unimplen                       | nented bit, read | d as '0'        |        |

| -n = Value a       | at POR                                                                                                                                                               | '1' = Bit is set                                                                                                                                                         |                                                                                                        | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown   |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| bit 15             | Unimplemen                                                                                                                                                           | ted: Read as '                                                                                                                                                           | 0'                                                                                                     |                                    |                  |                 |        |

| bit 14-12          | <b>T4IP&lt;2:0&gt;:</b> ⊺i                                                                                                                                           | imer4 Interrupt                                                                                                                                                          | Priority bits                                                                                          |                                    |                  |                 |        |

|                    | 111 = Interrup                                                                                                                                                       | pt is Priority 7 (                                                                                                                                                       | highest priority                                                                                       | / interrupt)                       |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •<br>001 = Interrup                                                                                                                                                  | pt is Priority 1                                                                                                                                                         |                                                                                                        |                                    |                  |                 |        |

|                    |                                                                                                                                                                      | pt is Priority 1<br>pt source is dis                                                                                                                                     | abled                                                                                                  |                                    |                  |                 |        |

| bit 11             | 000 = Interru                                                                                                                                                        |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| bit 11<br>bit 10-8 | 000 = Interrup<br>Unimplemen                                                                                                                                         | pt source is dis<br>ted: Read as '                                                                                                                                       | 0'                                                                                                     | Interrupt Priorit                  | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '                                                                                                                                       | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | y bits           |                 |        |

|                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4<br>highest priority                                                     | • •                                | / bits           |                 |        |

|                    | 000 = Interrup<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                        | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                             | <sub>0</sub> '<br>are Channel 4<br>highest priority<br>abled                                           | • •                                | / bits           |                 |        |

| bit 10-8           | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'                                      | • •                                |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:<br>111 = Interrup<br>001 = Interrup | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'<br>are Channel 3<br>highest priority | y interrupt)<br>Interrupt Priority |                  |                 |        |

#### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

### 10.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW2<4>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

#### 10.4.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '11111' and all RPORx registers reset to '00000', all Peripheral Pin Select inputs are tied to RP31 and all Peripheral Pin Select outputs are disconnected.

| Note: | In tying Peripheral Pin Select inputs to    |

|-------|---------------------------------------------|

|       | RP31, RP31 does not have to exist on a      |

|       | device for the registers to be reset to it. |

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in C or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output. The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use.

Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled, as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs, nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as a digital I/O when used with a Peripheral Pin Select.

Example 10-2 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 10-2: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

// Unlock Registers \_\_builtin\_write\_OSCCONL(OSCCON & 0xBF); // Configure Input Functions (Table 10-2)) // Assign UlRX To Pin RP0 RPINR18bits.UlRXR = 0; // Assign UlCTS To Pin RP1 RPINR18bits.UlCTSR = 1; // Configure Output Functions (Table 10-3) // Assign UlTX To Pin RP2 RPOR1bits.RP2R = 3; // Assign ULRTS To Pin RP3 RPOR1bits.RP3R = 4; // Lock Registers \_\_builtin\_write\_OSCCONL(OSCCON | 0x40);

#### REGISTER 10-7: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | —     | —     | —     | —     | —     |

| bit 15 |     |     |       |       | •     |       | bit 8 |

|        |     |     |       |       |       |       |       |

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | IC5R4 | IC5R3 | IC5R2 | IC5R1 | IC5R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 IC5R<4:0>: Assign Input Capture 5 (IC5) to the Corresponding RPn Pin bits

#### REGISTER 10-8: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

|                                   |     |                  |                                    | <b>D A A A</b>                          | D 444 4 | <b>D</b> 4 4 4 | D 11/ 1 |

|-----------------------------------|-----|------------------|------------------------------------|-----------------------------------------|---------|----------------|---------|

| U-0                               | U-0 | U-0              | R/W-1                              | R/W-1                                   | R/W-1   | R/W-1          | R/W-1   |

|                                   | —   | —                | OCFBR4                             | OCFBR3                                  | OCFBR2  | OCFBR1         | OCFBR0  |

| bit 15                            |     |                  |                                    |                                         |         |                | bit 8   |

|                                   |     |                  |                                    |                                         |         |                |         |

| U-0                               | U-0 | U-0              | R/W-1                              | R/W-1                                   | R/W-1   | R/W-1          | R/W-1   |

|                                   | —   | —                | OCFAR4                             | OCFAR3                                  | OCFAR2  | OCFAR1         | OCFAR0  |

| bit 7                             |     |                  |                                    |                                         |         |                | bit 0   |

|                                   |     |                  |                                    |                                         |         |                |         |

| Legend:                           |     |                  |                                    |                                         |         |                |         |

| R = Readable bit W = Writable bit |     | oit              | U = Unimplemented bit, read as '0' |                                         |         |                |         |

| -n = Value at I                   | POR | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |         | nown           |         |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 OCFBR<4:0>: Assign Output Compare Fault B (OCFB) to the Corresponding RPn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

#### 14.3 Pulse-Width Modulation Mode

| Note: | This peripheral contains input and output |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | functions that may need to be configured  |  |  |  |  |  |  |

|       | by the Peripheral Pin Select. See         |  |  |  |  |  |  |

|       | Section 10.4 "Peripheral Pin Select       |  |  |  |  |  |  |

|       | (PPS)" for more information.              |  |  |  |  |  |  |

The following steps should be taken when configuring the output compare module for PWM operation:

- 1. Set the PWM period by writing to the selected Timery Period register (PRy).

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Write the OCxR register with the initial duty cycle.

- 4. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- Configure the output compare module for one of two PWM Operation modes by writing to the Output Compare Mode bits, OCM<2:0> (OCxCON<2:0>).

- 6. Set the TMRy prescale value and enable the time base by setting TON (TyCON<15>) = 1.

- Note: The OCxR register should be initialized before the output compare module is first enabled. The OCxR register becomes a read-only Duty Cycle register when the module is operated in the PWM modes. The value held in OCxR will become the PWM duty cycle for the first PWM period. The contents of the Output Compare x Secondary register, OCxRS, will not be transferred into OCxR until a time base period match occurs.

#### 14.3.1 PWM PERIOD

The PWM period is specified by writing to PRy, the Timery Period register. The PWM period can be calculated using Equation 14-1.

# EQUATION 14-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period =  $[(PRy) + 1] \bullet TCY \bullet (Timer Prescale Value)$ Where:

PWM Frequency = 1/[PWM Period]

**Note 1:** Based on TCY = 2 \* TOSC; Doze mode and PLL are disabled.

Note: A PRy value of N will produce a PWM period of N + 1 time base count cycles. For example, a value of 7 written into the PRy register will yield a period consisting of 8 time base cycles.

### 14.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS register. The OCxRS register can be written to at any time, but the duty cycle value is not latched into OCxR until a match between PRy and TMRy occurs (i.e., the period is complete). This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation. In the PWM mode, OCxR is a read-only register.

Some important boundary parameters of the PWM duty cycle include:

- If the Output Compare x register, OCxR, is loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxR is greater than PRy (Timery Period register), the pin will remain high (100% duty cycle).

- If OCxR is equal to PRy, the OCx pin will be low for one time base count value and high for all other count values.

See Example 14-1 for PWM mode timing details. Table 14-1 and Table 14-2 show example PWM frequencies and resolutions for a device operating at 4 and 16 MIPS.

#### EQUATION 14-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC                                                           | R-0, HSC                                 | U-0                                                                                | U-0                     | U-0                          | R/C-0, HS                    | R-0, HSC           | R-0, HSC        |

|--------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------|-------------------------|------------------------------|------------------------------|--------------------|-----------------|

| ACKSTAT <sup>(</sup>                                               | <sup>1)</sup> TRSTAT                     | —                                                                                  | —                       | —                            | BCL                          | GCSTAT             | ADD10           |

| bit 15                                                             |                                          |                                                                                    |                         |                              |                              |                    | bit 8           |

|                                                                    |                                          |                                                                                    |                         |                              |                              |                    |                 |

| R/C-0, HS                                                          | 8 R/C-0, HS                              | R-0, HSC                                                                           | R/C-0, HSC              | R/C-0, HSC                   | R-0, HSC                     | R-0, HSC           | R-0, HSC        |

| IWCOL                                                              | I2COV                                    | D/A                                                                                | Р                       | S                            | R/W                          | RBF                | TBF             |

| bit 7                                                              |                                          |                                                                                    | 1                       |                              |                              | •                  | bit 0           |

|                                                                    |                                          |                                                                                    |                         |                              |                              |                    |                 |

| Legend:                                                            |                                          | C = Clearabl                                                                       | e bit                   | HS = Hardware                | e Settable bit               |                    |                 |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                          |                                                                                    |                         |                              |                              |                    |                 |

| -n = Value a                                                       | at POR                                   | '1' = Bit is se                                                                    | t                       | '0' = Bit is clear           | red                          | x = Bit is unkr    | nown            |

| HSC = Har                                                          | dware Settable/C                         | learable bit                                                                       |                         |                              |                              |                    |                 |

|                                                                    |                                          |                                                                                    |                         |                              |                              |                    |                 |

| bit 15                                                             | ACKSTAT: Ad                              | cknowledge St                                                                      | atus bit <sup>(1)</sup> |                              |                              |                    |                 |

|                                                                    |                                          | s detected las                                                                     |                         |                              |                              |                    |                 |

|                                                                    | 0 = ACK was                              |                                                                                    |                         |                              |                              |                    |                 |

|                                                                    | Hardware is s                            |                                                                                    |                         | -                            |                              |                    |                 |

| bit 14                                                             |                                          |                                                                                    |                         | ting as l <sup>2</sup> C™ ma | ister, applicable            | to master trans    | smit operation) |

|                                                                    |                                          | ansmit is in pro                                                                   | <b>U</b>                | + ACK)                       |                              |                    |                 |

|                                                                    |                                          | ansmit is not ir<br>et at the beginn                                               |                         | ansmission. Har              | dware is clear at            | the end of slave   | Acknowledge     |

| bit 13-11                                                          | Unimplemen                               | -                                                                                  | -                       |                              |                              |                    | ger             |

| bit 10                                                             | BCL: Master                              |                                                                                    |                         |                              |                              |                    |                 |

|                                                                    |                                          |                                                                                    |                         | ing a master op              | eration                      |                    |                 |

|                                                                    | 0 = No collisio                          | on                                                                                 |                         |                              |                              |                    |                 |

|                                                                    | Hardware is s                            | et at the dete                                                                     | ction of bus co         | ollision.                    |                              |                    |                 |

| bit 9                                                              | GCSTAT: Ger                              |                                                                                    |                         |                              |                              |                    |                 |

|                                                                    |                                          | 1 = General call address was received<br>0 = General call address was not received |                         |                              |                              |                    |                 |

|                                                                    |                                          |                                                                                    |                         | u<br>s the general call      | address. Hardw               | vare is clear at s | Stop detection. |

| bit 8                                                              | ADD10: 10-B                              |                                                                                    |                         | stre general eau             |                              |                    |                 |

|                                                                    |                                          | lress was mat                                                                      |                         |                              |                              |                    |                 |

|                                                                    |                                          | lress was not                                                                      |                         |                              |                              |                    |                 |

|                                                                    | Hardware is se                           | et at the match                                                                    | of the 2nd byte         | e of matched 10-b            | oit address. Hard            | ware is clear at   | Stop detection. |

| bit 7                                                              | IWCOL: I2Cx                              |                                                                                    |                         |                              | 2                            |                    |                 |

|                                                                    |                                          |                                                                                    | e I2CxTRN re            | egister failed beo           | cause the I <sup>2</sup> C m | odule is busy      |                 |

|                                                                    | 0 = No collisio<br>Hardware is s         |                                                                                    | rrence of a wr          | ite to I2CxTRN               | while busy (clea             | red by software    | e)              |

| bit 6                                                              | 12COV: 12Cx 1                            |                                                                                    |                         |                              |                              | . ca sy convar     |                 |

| 211.0                                                              |                                          |                                                                                    | -                       | CV register is sti           | Il holdina the pro           | evious bvte        |                 |

|                                                                    | 0 = No overflo                           |                                                                                    |                         |                              | 3 P.                         |                    |                 |

|                                                                    | Hardware is s                            | et at an attem                                                                     | pt to transfer          | 2CxRSR to 12C                | xRCV (cleared                | by software).      |                 |

| Note 1:                                                            | n both Master an                         | d Slave mode                                                                       | s, the ACKST            | AT bit is only up            | dated when tran              | ismitting data r   | esultina in the |

| r                                                                  | reception of an A<br>data, either as a s | CK or NACK f                                                                       | rom another d           | evice. Do not ch             | neck the state of            | ACKSTAT who        | en receiving    |