# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj48ga002-i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ABLE 1-1. DEVICE FEATURES FOR THE FIC24FJ04GA004 FAMILT |                  |           |             |                                    |           |            |            |         |  |

|---------------------------------------------------------|------------------|-----------|-------------|------------------------------------|-----------|------------|------------|---------|--|

| Features                                                | 16GA002          | 32GA002   | 48GA002     | 64GA002                            | 16GA004   | 32GA004    | 48GA004    | 64GA004 |  |

| Operating Frequency                                     | DC – 3           | 2 MHz     |             | •                                  |           |            |            |         |  |

| Program Memory (bytes)                                  | 16K              | 32K       | 48K         | 64K                                | 16K       | 32K        | 48K        | 64K     |  |

| Program Memory (instructions)                           | 5,504            | 11,008    | 16,512      | 22,016                             | 5,504     | 11,008     | 16,512     | 22,016  |  |

| Data Memory (bytes)                                     | 4096             |           | 8192        |                                    | 4096      |            | 8192       |         |  |

| Interrupt Sources<br>(soft vectors/NMI traps)           |                  |           |             | 4<br>(39                           |           | •          |            |         |  |

| I/O Ports                                               |                  | Ports     | ; А, В      |                                    |           | Ports /    | A, B, C    |         |  |

| Total I/O Pins                                          |                  | 2         | 1           |                                    |           | 3          | 5          |         |  |

| Timers:                                                 |                  |           |             |                                    |           |            |            |         |  |

| Total Number (16-bit)                                   |                  |           |             | 5(                                 | 1)        |            |            |         |  |

| 32-Bit (from paired 16-bit timers)                      |                  |           |             | 2                                  |           |            |            |         |  |

| Input Capture Channels                                  | 5 <sup>(1)</sup> |           |             |                                    |           |            |            |         |  |

| Output Compare/PWM Channels                             |                  |           |             | 5(                                 | 1)        |            |            |         |  |

| Input Change Notification Interrupt                     |                  | 2         | 1           |                                    |           | 3          | 0          |         |  |

| Serial Communications:                                  |                  |           |             |                                    |           |            |            |         |  |

| UART                                                    |                  |           |             | 2(                                 | 1)        |            |            |         |  |

| SPI (3-wire/4-wire)                                     | 2 <sup>(1)</sup> |           |             |                                    |           |            |            |         |  |

| I <sup>2</sup> C™                                       | 2                |           |             |                                    |           |            |            |         |  |

| Parallel Communications (PMP/PSP)                       |                  |           |             | Ye                                 | es        |            |            |         |  |

| JTAG Boundary Scan                                      |                  |           |             | Ye                                 | es        |            |            |         |  |

| 10-Bit Analog-to-Digital Module<br>(input channels)     |                  | 1         | 0           |                                    |           | 1          | 3          |         |  |

| Analog Comparators                                      |                  |           |             | 2                                  | 2         |            |            |         |  |

| Remappable Pins                                         |                  | 1         | 6           |                                    |           | 2          | 6          |         |  |

| Resets (and delays)                                     |                  |           | iction, Hai | nstruction<br>dware Tra<br>WRT, OS | ps, Confi | guration V |            |         |  |

| Instruction Set                                         |                  | 76 Base I | nstruction  | s, Multiple                        | Address   | ing Mode   | Variations |         |  |

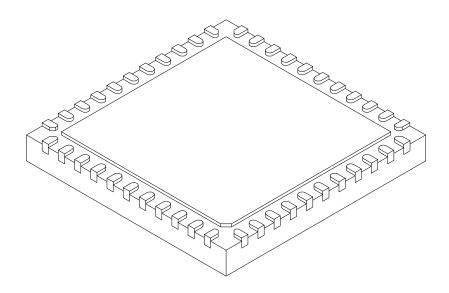

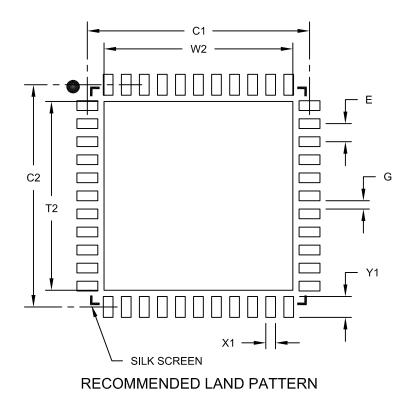

| Packages                                                | 28-Pin           | SPDIP/S   | SOP/SOI     | C/QFN                              |           | 44-Pin Q   | FN/TQFP    |         |  |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ64GA004 FAMILY

**Note 1:** Peripherals are accessible through remappable pins.

#### TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          | I                             | Pin Number    |                    |     |                 |                                                                      |

|----------|-------------------------------|---------------|--------------------|-----|-----------------|----------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                          |

| T1CK     | 12                            | 9             | 34                 | Ι   | ST              | Timer1 Clock.                                                        |

| TCK      | 17                            | 14            | 13                 | -   | ST              | JTAG Test Clock Input.                                               |

| TDI      | 21                            | 18            | 35                 | -   | ST              | JTAG Test Data Input.                                                |

| TDO      | 18                            | 15            | 32                 | 0   | _               | JTAG Test Data Output.                                               |

| TMS      | 22                            | 19            | 12                 | -   | ST              | JTAG Test Mode Select Input.                                         |

| Vdd      | 13, 28                        | 10, 25        | 28, 40             | Р   | _               | Positive Supply for Peripheral Digital Logic and I/O Pins.           |

| VDDCAP   | 20                            | 17            | 7                  | Р   | _               | External Filter Capacitor Connection (regulator enabled).            |

| VDDCORE  | 20                            | 17            | 7                  | Р   | —               | Positive Supply for Microcontroller Core Logic (regulator disabled). |

| VREF-    | 3                             | 28            | 20                 | -   | ANA             | A/D and Comparator Reference Voltage (low) Input.                    |

| VREF+    | 2                             | 27            | 19                 | Ι   | ANA             | A/D and Comparator Reference Voltage (high) Input.                   |

| Vss      | 8, 27                         | 5, 24         | 29, 39             | Р   | —               | Ground Reference for Logic and I/O Pins.                             |

| Legend:  | TTL = TTL inp                 | ut buffer     |                    |     | ST = 5          | Schmitt Trigger input buffer                                         |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffe  $I^2C^{TM} = I^2C/SMBus$  input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0               | U-0                                           | U-0                                                                            | U-0                           | U-0               | U-0                  | U-0      | R/W-0 |

|-------------------|-----------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|-------------------|----------------------|----------|-------|

|                   |                                               | —                                                                              |                               |                   | _                    | —        | LVDIE |

| bit 15            |                                               |                                                                                |                               |                   |                      |          | bit 8 |

|                   |                                               |                                                                                |                               |                   |                      |          |       |

| U-0               | U-0                                           | U-0                                                                            | U-0                           | R/W-0             | R/W-0                | R/W-0    | U-0   |

| _                 |                                               |                                                                                | _                             | CRCIE             | U2ERIE               | U1ERIE   | _     |

| bit 7             |                                               |                                                                                |                               |                   |                      |          | bit C |

|                   |                                               |                                                                                |                               |                   |                      |          |       |

| Legend:           |                                               |                                                                                |                               |                   |                      |          |       |

| R = Reada         | ble bit                                       | W = Writable b                                                                 | oit                           | U = Unimplen      | nented bit, read     | d as '0' |       |

| -n = Value        | at POR                                        | '1' = Bit is set                                                               |                               | '0' = Bit is clea | '0' = Bit is cleared |          | own   |

| bit 15-9<br>bit 8 | LVDIE: Low-<br>1 = Interrupt<br>0 = Interrupt | Noted: Read as 'C<br>Voltage Detect I<br>request is enabl<br>request is not en | nterrupt Enat<br>ed<br>nabled | ble Status bit    |                      |          |       |

| bit 7-4           | •                                             | nted: Read as '0                                                               |                               |                   |                      |          |       |

| bit 3             | 1 = Interrupt                                 | C Generator Inter<br>request is enabl<br>request is not er                     | ed                            | bit               |                      |          |       |

| bit 2             | U2ERIE: UA                                    | RT2 Error Interr                                                               | upt Enable bi                 | t                 |                      |          |       |

|                   |                                               | request is enabl<br>request is not en                                          |                               |                   |                      |          |       |

| bit 1             | 1 = Interrupt                                 | RT1 Error Interror<br>request is enabl<br>request is not en                    | ed                            | t                 |                      |          |       |

| bit 0             | Unimpleme                                     | nted: Read as 'o                                                               | )'                            |                   |                      |          |       |

|                   |                                               |                                                                                |                               |                   |                      |          |       |

| Legend:                      | U1RXIP2<br>R/W-1<br>SPF1IP2 | U1RXIP1<br>R/W-0<br>SPF1IP1          | U1RXIP0<br>R/W-0 | —                | SPI1IP2          | SPI1IP1         | SPI1IP0 |

|------------------------------|-----------------------------|--------------------------------------|------------------|------------------|------------------|-----------------|---------|

| U-0<br>—<br>Dit 7<br>Legend: |                             |                                      | B/M/ 0           |                  |                  |                 |         |

| bit 7                        |                             |                                      | D/M/ 0           |                  |                  |                 | bit     |

|                              |                             |                                      |                  | U-0              | R/W-1            | R/W-0           | R/W-0   |

|                              | 3FF IIFZ                    |                                      | SPF1IP0          | 0-0              | T3IP2            | T3IP1           | T3IP0   |

| Legend:                      |                             | SELIET                               | SFFIIFU          | _                | T JIF Z          |                 | bit     |

|                              |                             |                                      |                  |                  |                  |                 |         |

| R = Readable                 |                             |                                      |                  |                  |                  |                 |         |

| R = Readable                 | bit                         | W = Writable                         | bit              | U = Unimple      | mented bit, read | d as '0'        |         |

| -n = Value at F              | POR                         | '1' = Bit is set                     |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

| bit 15                       | Unimplement                 | ted: Read as '                       | )'               |                  |                  |                 |         |

| bit 14-12                    | -                           | UART1 Rece                           |                  | Priority bits    |                  |                 |         |

|                              | 111 = Interrup              | ot is Priority 7 (                   | highest priority | / interrupt)     |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | 001 = Interrup              |                                      |                  |                  |                  |                 |         |

|                              | -                           | ot source is dis                     |                  |                  |                  |                 |         |

| bit 11                       | -                           | ted: Read as '                       |                  |                  |                  |                 |         |

| bit 10-8                     |                             | SPI1 Event In                        |                  |                  |                  |                 |         |

|                              | 111 = Interrup              | ot is Priority 7 (                   | highest priority | / interrupt)     |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | 001 = Interrup              |                                      |                  |                  |                  |                 |         |

|                              |                             | ot source is dis                     |                  |                  |                  |                 |         |

| bit 7                        | -                           | ted: Read as '                       |                  |                  |                  |                 |         |

| bit 6-4                      |                             | : SPI1 Fault In                      |                  |                  |                  |                 |         |

|                              | 111 = Interrup              | ot is Priority 7 (                   | highest priority | / interrupt)     |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | 001 = Interrup              | ot is Priority 1<br>ot source is dis | abled            |                  |                  |                 |         |

| bit 3                        | -                           | ted: Read as '                       |                  |                  |                  |                 |         |

| bit 2-0                      | -                           | mer3 Interrupt                       |                  |                  |                  |                 |         |

|                              |                             | ot is Priority 7 (                   | -                | / interrupt)     |                  |                 |         |

|                              | •                           |                                      |                  | ,                |                  |                 |         |

|                              | •                           |                                      |                  |                  |                  |                 |         |

|                              | •<br>001 = Interrup         | nt is Priority 1                     |                  |                  |                  |                 |         |

|                              |                             | ot source is dis                     | abled            |                  |                  |                 |         |

#### REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

|              | _                                                         | _                                                                                                | -                         |                  |                 |                 |         |

|--------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|------------------|-----------------|-----------------|---------|

| U-0          | U-0                                                       | U-0                                                                                              | U-0                       | U-0              | R/W-1           | R/W-0           | R/W-0   |

| _            | _                                                         | _                                                                                                | —                         | _                | MI2C2P2         | MI2C2P1         | MI2C2P0 |

| bit 15       |                                                           |                                                                                                  | ·                         |                  | ·               |                 | bit     |

|              |                                                           |                                                                                                  |                           |                  |                 |                 |         |

| U-0          | R/W-1                                                     | R/W-0                                                                                            | R/W-0                     | U-0              | U-0             | U-0             | U-0     |

|              | SI2C2P2                                                   | SI2C2P1                                                                                          | SI2C2P0                   |                  | <u> </u>        |                 | —       |

| bit 7        |                                                           |                                                                                                  |                           |                  |                 |                 | bit (   |

|              |                                                           |                                                                                                  |                           |                  |                 |                 |         |

| Legend:      |                                                           |                                                                                                  |                           |                  |                 |                 |         |

| R = Readab   | le bit                                                    | W = Writable                                                                                     | bit                       | U = Unimpler     | mented bit, rea | d as '0'        |         |

| -n = Value a | t POR                                                     | '1' = Bit is set                                                                                 |                           | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |

| bit 7        | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru | >: Master I2C2<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as 'o | highest priority<br>abled | •                |                 |                 |         |

| bit 6-4      | -                                                         | Slave I2C2 E                                                                                     |                           | Priority hits    |                 |                 |         |

| DIL 0-4      | 111 = Interru<br>•<br>•<br>001 = Interru                  | pt is Priority 1<br>pt is Priority 1<br>pt source is dis                                         | highest priority          | •                |                 |                 |         |

| bit 3-0      | Unimplemen                                                | ted: Read as '                                                                                   | כ'                        |                  |                 |                 |         |

|              |                                                           |                                                                                                  |                           |                  |                 |                 |         |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | —   | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |     |     |        |        |        |        | bit 0  |

|        |     |     |        |        |        |        |        |

|        |     |     |        |        |        |        |        |

#### REGISTER 10-11: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 12-8  | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                     |

| bit 4-0   | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits    |

#### REGISTER 10-12: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0                               | U-0              | U-0   | U-0                                                                                                      | U-0                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|------------------|-------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                                 | —                | —     | —                                                                                                        | —                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                   |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                   |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| U-0                               | U-0              | R/W-1 | R/W-1                                                                                                    | R/W-1                                                                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _                                 | —                | SS1R4 | SS1R3                                                                                                    | SS1R2                                                                                                                                                                                                         | SS1R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SS1R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                   |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                   |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                   |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| R = Readable bit W = Writable bit |                  | bit   | U = Unimplemented bit, read as '0'                                                                       |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| POR                               | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown                                                                  |                                                                                                                                                                                                               | nown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                   |                  |       | U-0         U-0         R/W-1           —         —         SS1R4           bit         W = Writable bit | —         —         —         —           U-0         U-0         R/W-1         R/W-1           —         —         —         SS1R4         SS1R3           bit         W = Writable bit         U = Unimplem | —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         Image: Marce of the field of th | —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         — |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the Corresponding RPn Pin bits

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 4 **RXINV:** Receive Polarity Inversion bit 1 = UxRX Idle state is '0' 0 = UxRX Idle state is '1' bit 3 BRGH: High Baud Rate Enable bit 1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode) 0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode) bit 2-1 PDSEL<1:0>: Parity and Data Selection bits 11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity bit 0 STSEL: Stop Bit Selection bit 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: Bit availability depends on pin availability.

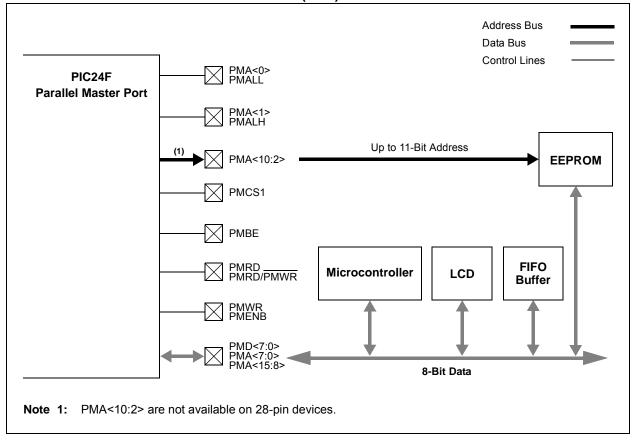

### 18.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features of |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | this group of PIC24F devices. It is not    |  |  |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |  |  |

|       | "Parallel Master Port (PMP)" (DS39713).    |  |  |  |  |  |  |  |  |

The Parallel Master Port (PMP) module is a parallel 8-bit I/O module, specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP is highly configurable.

**Note:** A number of the pins for the PMP are not present on PIC24FJ64GA004 devices. Refer to the specific device's pinout to determine which pins are available.

Key features of the PMP module include:

- Up to 16 Programmable Address Lines

- One Chip Select Line

- Programmable Strobe Options:

- Individual Read and Write Strobes or;

- Read/Write Strobe with Enable Strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- · Programmable Polarity on Control Signals

- Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address Support

- 4-Byte Deep Auto-Incrementing Buffer

- · Programmable Wait States

- · Selectable Input Voltage Levels

#### FIGURE 18-1: PARALLEL MASTER PORT (PMP) MODULE OVERVIEW

| R-0                   | R/W-0                 | R/W-0            | R/W-0                                | R/W-0             | R/W-0                                                                 | R/W-0                               | R/W-0                 |

|-----------------------|-----------------------|------------------|--------------------------------------|-------------------|-----------------------------------------------------------------------|-------------------------------------|-----------------------|

| BUSY                  | IRQM1                 | IRQM0            | INCM1                                | INCM0             | MODE16                                                                | MODE1                               | MODE0                 |

| bit 15                | 1                     |                  |                                      |                   |                                                                       |                                     | bit 8                 |

|                       |                       |                  |                                      |                   |                                                                       | <b>D</b> 444 A                      | 5444.6                |

| R/W-0                 | R/W-0                 | R/W-0            | R/W-0                                | R/W-0             | R/W-0                                                                 | R/W-0                               | R/W-0                 |

| WAITB1 <sup>(1)</sup> | WAITB0 <sup>(1)</sup> | WAITM3           | WAITM2                               | WAITM1            | WAITM0                                                                | WAITE1 <sup>(1)</sup>               | WAITE0 <sup>(1)</sup> |

| bit 7                 |                       |                  |                                      |                   |                                                                       |                                     | bit (                 |

| Legend:               |                       |                  |                                      |                   |                                                                       |                                     |                       |

| R = Readable          | e bit                 | W = Writable     | bit                                  | U = Unimplen      | nented bit, read                                                      | d as '0'                            |                       |

| -n = Value at         | POR                   | '1' = Bit is set |                                      | '0' = Bit is clea |                                                                       | x = Bit is unkr                     | nown                  |

|                       |                       |                  |                                      |                   |                                                                       |                                     |                       |

| bit 15                | BUSY: Busy b          | bit (Master mod  | de only)                             |                   |                                                                       |                                     |                       |

|                       | 1 = Port is bu        | usy (not useful  | when the proce                       | essor stall is ac | tive)                                                                 |                                     |                       |

|                       | 0 = Port is no        | ot busy          |                                      |                   |                                                                       |                                     |                       |

| bit 14-13             | IRQM<1:0>:            | Interrupt Reque  | est Mode bits                        |                   |                                                                       |                                     |                       |

|                       |                       |                  |                                      |                   |                                                                       | written (Buffer                     |                       |

|                       |                       |                  |                                      |                   |                                                                       | PSP mode onl                        | у)                    |

|                       |                       |                  | ed, processor s<br>at the end of the |                   |                                                                       |                                     |                       |

|                       |                       | rupt is generate |                                      |                   |                                                                       |                                     |                       |

| bit 12-11             |                       | ncrement Mod     |                                      |                   |                                                                       |                                     |                       |

|                       | 11 = PSP rea          | id and write bu  | ffers auto-incre                     | ment (Legacy      | PSP mode only                                                         | /)                                  |                       |

|                       |                       |                  | 0:0> by 1 every                      |                   |                                                                       |                                     |                       |

|                       |                       |                  | 0> by 1 every r                      | •                 | 9                                                                     |                                     |                       |

| hit 10                |                       |                  | ment of addres                       | S                 |                                                                       |                                     |                       |

| bit 10                |                       | 6-Bit Mode bit   | taria 10 hita a                      | read envirite to  | the Deterratio                                                        |                                     |                       |

|                       |                       |                  |                                      |                   |                                                                       | ter invokes two<br>er invokes one 8 |                       |

| bit 9-8               |                       | -                | lode Select bits                     |                   | ne Bata regiote                                                       |                                     |                       |

| bit 0 0               |                       |                  |                                      |                   | MRE PMA <x.< td=""><td>)&gt; and PMD&lt;7:</td><td>·0&gt;)</td></x.<> | )> and PMD<7:                       | ·0>)                  |

|                       |                       |                  |                                      |                   | A <x:0> and P</x:0>                                                   |                                     | .0- )                 |

|                       | 01 = Enhance          | ed PSP, contro   | l signals (PMR                       | D, PMWR, PM       | CS1, PMD<7:0                                                          | > and PMA<1:0                       |                       |

|                       | • •                   |                  | -                                    |                   |                                                                       | 1 and PMD<7:0                       | )>)                   |

| bit 7-6               | WAITB<1:0>:           | : Data Setup to  | Read/Write W                         | ait State Config  | guration bits <sup>(1)</sup>                                          |                                     |                       |

|                       |                       |                  | tiplexed addres                      | •                 |                                                                       |                                     |                       |

|                       |                       |                  | Itiplexed addres                     |                   |                                                                       |                                     |                       |

|                       |                       |                  | Itiplexed addres                     |                   |                                                                       |                                     |                       |