#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj48ga004-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

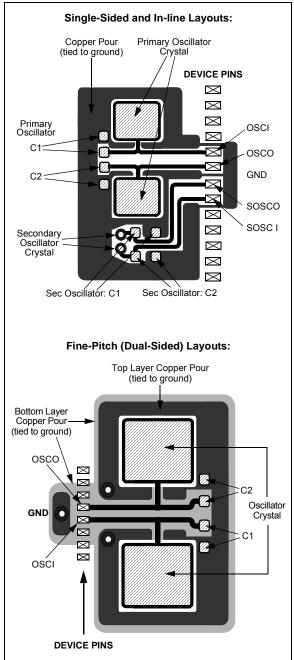

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-5:

### PLACEMENT OF THE OSCILLATOR CIRCUIT

SUGGESTED

### 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. Depending on the particular device, this is done by setting all bits in the ADnPCFG register(s), or clearing all bit in the ANSx registers.

All PIC24F devices will have either one or more ADnPCFG registers or several ANSx registers (one for each port); no device will have both. Refer to **Section 21.0 "10-Bit High-Speed A/D Converter"** for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must modify the appropriate bits during initialization of the A/D module, as follows:

- For devices with an ADnPCFG register, clear the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

- For devices with ANSx registers, set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

When a Microchip debugger/emulator is used as a programmer, the user application firmware must correctly configure the ADnPCFG or ANSx registers. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

| U-0          | U-0                                                                                           | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------|-----------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| _            | —                                                                                             | AD1IF                            | U1TXIF           | U1RXIF            | SPI1IF          | SPF1IF          | T3IF   |

| bit 15       |                                                                                               |                                  | •                |                   |                 | ·               | bit 8  |

| R/W-0        | R/W-0                                                                                         | R/W-0                            | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| T2IF         | OC2IF                                                                                         | IC2IF                            | _                | T1IF              | OC1IF           | IC1IF           | INTOIF |

| bit 7        | 002li                                                                                         | 10211                            |                  |                   | 0011            | 10111           | bit    |

| Legend:      |                                                                                               |                                  |                  |                   |                 |                 |        |

| R = Readab   | le bit                                                                                        | W = Writable                     | bit              | U = Unimplem      | nented bit. rea | d as '0'        |        |

| -n = Value a | t POR                                                                                         | '1' = Bit is set                 |                  | '0' = Bit is clea |                 | x = Bit is unkn | iown   |

|              |                                                                                               |                                  |                  |                   |                 |                 |        |

| bit 15-14    | Unimpleme                                                                                     | nted: Read as '                  | 0'               |                   |                 |                 |        |

| bit 13       | AD1IF: A/D                                                                                    | Conversion Cor                   | nplete Interrup  | t Flag Status bit |                 |                 |        |

|              | 1 = Interrupt                                                                                 | request has oc<br>request has no | curred           | U                 |                 |                 |        |

| bit 12       | •                                                                                             | RT1 Transmitte                   |                  | Status bit        |                 |                 |        |

|              | 1 = Interrupt                                                                                 | request has oc                   | curred           |                   |                 |                 |        |

| L:1 4 4      | -                                                                                             | request has no                   |                  |                   |                 |                 |        |

| oit 11       | <b>U1RXIF:</b> UART1 Receiver Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                  |                  |                   |                 |                 |        |

|              |                                                                                               | request has no                   |                  |                   |                 |                 |        |

| bit 10       | -                                                                                             | 1 Event Interrup                 |                  | it                |                 |                 |        |

|              | 1 = Interrupt                                                                                 | request has oc<br>request has no | curred           |                   |                 |                 |        |

| bit 9        |                                                                                               | 1 Fault Interrup                 |                  | it                |                 |                 |        |

| bit 0        |                                                                                               | request has oc                   | •                | it i              |                 |                 |        |

|              | •                                                                                             | request has no                   |                  |                   |                 |                 |        |

| bit 8        | T3IF: Timer3                                                                                  | B Interrupt Flag                 | Status bit       |                   |                 |                 |        |

|              |                                                                                               | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 7        | T2IF: Timer2                                                                                  | 2 Interrupt Flag                 | Status bit       |                   |                 |                 |        |

|              | •                                                                                             | request has oc                   |                  |                   |                 |                 |        |

| hit C        | •                                                                                             | request has no                   |                  | nt Flag Status k  | .:+             |                 |        |

| bit 6        | -                                                                                             | out Compare Ch<br>request has oc |                  | pi riag Status i  | JIL             |                 |        |

|              | •                                                                                             | request has no                   |                  |                   |                 |                 |        |

| bit 5        | IC2IF: Input                                                                                  | Capture Chann                    | el 2 Interrupt F | lag Status bit    |                 |                 |        |

|              | •                                                                                             | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 4        | -                                                                                             | nted: Read as '                  |                  |                   |                 |                 |        |

| bit 3        | -                                                                                             | Interrupt Flag                   |                  |                   |                 |                 |        |

|              |                                                                                               | request has oc                   |                  |                   |                 |                 |        |

|              |                                                                                               | request has no                   |                  |                   |                 |                 |        |

| bit 2        | -                                                                                             | out Compare Ch                   |                  | pt Flag Status b  | pit             |                 |        |

|              |                                                                                               | request has oc                   |                  |                   |                 |                 |        |

|              |                                                                                               | request has no                   |                  |                   |                 |                 |        |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

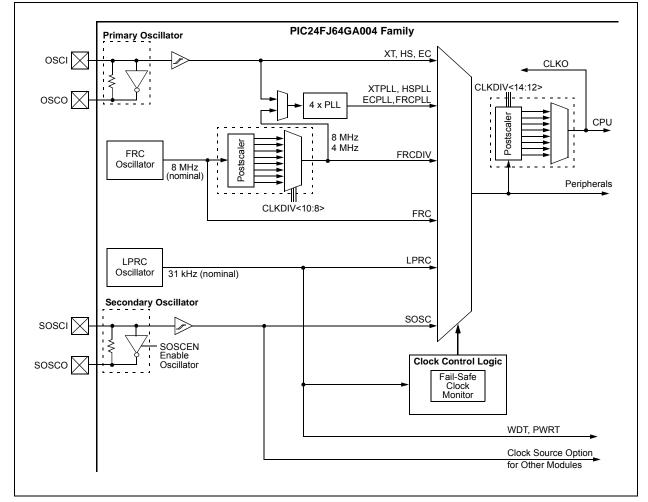

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features of |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | this group of PIC24F devices. It is not    |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |

|       | "Oscillator" (DS39700).                    |  |  |  |  |  |  |

The oscillator system for PIC24FJ64GA004 family devices has the following features:

- A total of four external and internal oscillator options as clock sources, providing 11 different clock modes

- On-chip 4x PLL to boost internal operating frequency on select internal and external oscillator sources

- Software-controllable switching between various clock sources

- Software-controllable postscaler for selective clocking of CPU for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

A simplified diagram of the oscillator system is shown in Figure 8-1.

# FIGURE 8-1: PIC24FJ64GA004 FAMILY CLOCK DIAGRAM

| U-0                                | U-0                      | U-0                                                | U-0                 | U-0                                     | U-0                 | U-0                 | U-0                 |  |  |  |

|------------------------------------|--------------------------|----------------------------------------------------|---------------------|-----------------------------------------|---------------------|---------------------|---------------------|--|--|--|

|                                    |                          | _                                                  |                     |                                         | _                   | _                   | _                   |  |  |  |

| oit 15                             |                          |                                                    |                     |                                         |                     |                     | bit 8               |  |  |  |

|                                    |                          |                                                    |                     |                                         |                     |                     |                     |  |  |  |

| U-0                                | U-0                      | R/W-0                                              | R/W-0               | R/W-0                                   | R/W-0               | R/W-0               | R/W-0               |  |  |  |

| _                                  | _                        | TUN5 <sup>(1)</sup>                                | TUN4 <sup>(1)</sup> | TUN3 <sup>(1)</sup>                     | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |  |  |  |

| oit 7                              |                          |                                                    | •                   |                                         | •                   | •                   | bit C               |  |  |  |

|                                    |                          |                                                    |                     |                                         |                     |                     |                     |  |  |  |

| _egend:                            |                          |                                                    |                     |                                         |                     |                     |                     |  |  |  |

| R = Readabl                        | e bit                    | W = Writable                                       | bit                 | U = Unimplen                            | nented bit, read    | l as '0'            |                     |  |  |  |

| -n = Value at POR '1' = Bit is set |                          |                                                    |                     | '0' = Bit is cleared x = Bit is unknown |                     |                     |                     |  |  |  |

|                                    |                          |                                                    |                     |                                         |                     |                     |                     |  |  |  |

| oit 15-6                           | Unimplemen               | ted: Read as '                                     | 0'                  |                                         |                     |                     |                     |  |  |  |

| oit 5-0                            | <b>TUN&lt;5:0&gt;:</b> F | UN<5:0>: FRC Oscillator Tuning bits <sup>(1)</sup> |                     |                                         |                     |                     |                     |  |  |  |

|                                    | 011111 <b>= Ma</b>       | ximum frequer                                      | ncy deviation       |                                         |                     |                     |                     |  |  |  |

|                                    | 011110 =                 |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | •                        |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | •                        |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | 000001 =                 |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | 000000 = Ce              | nter frequency,                                    | oscillator is ru    | inning at factory                       | / calibrated free   | quency              |                     |  |  |  |

|                                    | 111111 =                 |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | •                        |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | •                        |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | •                        |                                                    |                     |                                         |                     |                     |                     |  |  |  |

|                                    | •<br>100001 =            |                                                    |                     |                                         |                     |                     |                     |  |  |  |

#### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

## 8.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

#### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in Flash Configuration Word 2 must be programmed to '0'. (Refer to **Section 24.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains two 5-bit fields; each field being associated with one RPn pin (see Register 10-15 through Register 10-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-3).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '00000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

#### TABLE 10-3: SELECTABLE OUTPUT SOURCES (MAPS FUNCTION TO OUTPUT)

| Function             | Output Function<br>Number <sup>(1)</sup> | Output Name              |

|----------------------|------------------------------------------|--------------------------|

| NULL <sup>(2)</sup>  | 0                                        | NULL                     |

| C10UT                | 1                                        | Comparator 1 Output      |

| C2OUT                | 2                                        | Comparator 2 Output      |

| U1TX                 | 3                                        | UART1 Transmit           |

| U1RTS <sup>(3)</sup> | 4                                        | UART1 Request-to-Send    |

| U2TX                 | 5                                        | UART2 Transmit           |

| U2RTS <sup>(3)</sup> | 6                                        | UART2 Request-to-Send    |

| SDO1                 | 7                                        | SPI1 Data Output         |

| SCK10UT              | 8                                        | SPI1 Clock Output        |

| SS10UT               | 9                                        | SPI1 Slave Select Output |

| SDO2                 | 10                                       | SPI2 Data Output         |

| SCK2OUT              | 11                                       | SPI2 Clock Output        |

| SS2OUT               | 12                                       | SPI2 Slave Select Output |

| OC1                  | 18                                       | Output Compare 1         |

| OC2                  | 19                                       | Output Compare 2         |

| OC3                  | 20                                       | Output Compare 3         |

| OC4                  | 21                                       | Output Compare 4         |

| OC5                  | 22                                       | Output Compare 5         |

**Note 1:** Value assigned to the RPn<4:0> pins corresponds to the peripheral output function number.

- 2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

- **3:** IrDA<sup>®</sup> BCLK functionality uses this output.

#### 10.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention, caused by two physical pins being configured as the same functional input or two functional outputs configured as the same pin, there are no hardware enforced lockouts. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

# 10.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit remapping lock

#### 10.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

### 10.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW2<4>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

#### 10.4.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '11111' and all RPORx registers reset to '00000', all Peripheral Pin Select inputs are tied to RP31 and all Peripheral Pin Select outputs are disconnected.

| Note: | In tying Peripheral Pin Select inputs to    |

|-------|---------------------------------------------|

|       | RP31, RP31 does not have to exist on a      |

|       | device for the registers to be reset to it. |

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in C or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output. The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use.

Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled, as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs, nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as a digital I/O when used with a Peripheral Pin Select.

Example 10-2 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 10-2: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

// Unlock Registers \_\_builtin\_write\_OSCCONL(OSCCON & 0xBF); // Configure Input Functions (Table 10-2)) // Assign UIRX To Pin RP0 RPINR18bits.UIRXR = 0; // Assign UICTS To Pin RP1 RPINR18bits.UICTSR = 1; // Configure Output Functions (Table 10-3) // Assign UITX To Pin RP2 RPOR1bits.RP2R = 3; // Assign UIRTS To Pin RP3 RPOR1bits.RP3R = 4; // Lock Registers \_\_builtin\_write\_OSCCONL(OSCCON | 0x40); To set up the SPIx module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

- Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPIx module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- Clear the SPIxIF bit in the respective IFSx register.

- Set the SPIxIE bit in the respective IECx register.

- Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 8. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

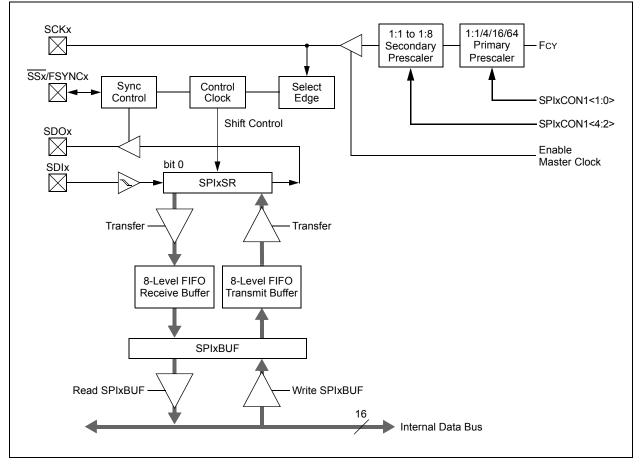

#### FIGURE 15-2: SPIX MODULE BLOCK DIAGRAM (ENHANCED MODE)

#### REGISTER 18-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

| U-0    | R/W-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                | R/W-0                |

|--------|-------|-----|-----|-----|-----------------------|----------------------|----------------------|

| —      | CS1   | —   | —   | —   | ADDR10 <sup>(1)</sup> | ADDR9 <sup>(1)</sup> | ADDR8 <sup>(1)</sup> |

| bit 15 |       |     |     |     |                       |                      | bit 8                |

| R/W-0                |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| ADDR7 <sup>(1)</sup> | ADDR6 <sup>(1)</sup> | ADDR5 <sup>(1)</sup> | ADDR4 <sup>(1)</sup> | ADDR3 <sup>(1)</sup> | ADDR2 <sup>(1)</sup> | ADDR1 <sup>(1)</sup> | ADDR0 <sup>(1)</sup> |

| bit 7                |                      |                      |                      |                      |                      |                      | bit 0                |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 14 CS1: Chip Select 1 bit

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Parallel Port Destination Address bits<sup>(1)</sup>

- **Note 1:** PMA<10:2> bits are not available on 28-pin devices.

#### REGISTER 18-4: PMAEN: PARALLEL PORT ENABLE REGISTER

| U-0    | R/W-0  | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                | R/W-0                |

|--------|--------|-----|-----|-----|-----------------------|----------------------|----------------------|

| _      | PTEN14 | —   | —   | —   | PTEN10 <sup>(1)</sup> | PTEN9 <sup>(1)</sup> | PTEN8 <sup>(1)</sup> |

| bit 15 |        |     |     |     |                       |                      | bit 8                |

| R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------|-------|

| PTEN7 <sup>(1)</sup> | PTEN6 <sup>(1)</sup> | PTEN5 <sup>(1)</sup> | PTEN4 <sup>(1)</sup> | PTEN3 <sup>(1)</sup> | PTEN2 <sup>(1)</sup> | PTEN1 | PTEN0 |

| bit 7                |                      |                      |                      |                      |                      |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15<br>bit 14 | Unimplemented: Read as '0'<br>PTEN14: PMCS1 Strobe Enable bit<br>1 = PMCS1 pin functions as chip select<br>0 = PMCS1 pin functions as port I/O   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-11        | Unimplemented: Read as '0'                                                                                                                       |

| bit 10-2         | PTEN<10:2>: PMP Address Port Enable bits <sup>(1)</sup>                                                                                          |

|                  | <ul><li>1 = PMA&lt;10:2&gt; function as PMP address lines</li><li>0 = PMA&lt;10:2&gt; function as port I/O</li></ul>                             |

| bit 1-0          | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                        |

|                  | <ul> <li>1 = PMA1 and PMA0 function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA1 and PMA0 pads functions as port I/O</li> </ul> |

**Note 1:** PMA<10:2> bits are not available on 28-pin devices.

| R-0<br>IBF<br>bit 15<br>R-1<br>OBE<br>bit 7<br>Legend: | R/W-0, HS<br>IBOV<br>R/W-0, HS<br>OBUF                                                                                                      | U-0<br>—<br>U-0<br>—                  | U-0<br>—<br>U-0<br>— | R-0<br>IB3F<br>R-1<br>OB3E         | R-0<br>IB2F<br>R-1<br>OB2E | R-0<br>IB1F<br>R-1   | R-0<br>IB0F<br>bit 8<br>R-1 |  |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|------------------------------------|----------------------------|----------------------|-----------------------------|--|

| R-1<br>OBE<br>bit 7                                    | R/W-0, HS                                                                                                                                   | U-0<br>—                              | U-0<br>—             | R-1                                | R-1                        | R-1                  | bit 8                       |  |

| OBE<br>bit 7                                           | ,                                                                                                                                           | U-0<br>—                              | U-0                  | 1                                  |                            |                      | R-1                         |  |

| OBE<br>bit 7                                           | ,                                                                                                                                           | <u> </u>                              | <u> </u>             | 1                                  |                            |                      | R-1                         |  |

| bit 7                                                  |                                                                                                                                             | —                                     | —                    | OB3E                               | OB2E                       |                      | 000                         |  |

|                                                        |                                                                                                                                             |                                       |                      |                                    |                            | OB1E                 | OB0E<br>bit 0               |  |

| l ogond:                                               |                                                                                                                                             |                                       |                      |                                    |                            |                      | DILC                        |  |

| Legenu.                                                |                                                                                                                                             | HS = Hardwar                          | e Settable bit       |                                    |                            |                      |                             |  |

| R = Readabl                                            | le bit                                                                                                                                      | W = Writable b                        | bit                  | U = Unimplem                       | ented bit, read            | l as '0'             |                             |  |

| -n = Value at                                          | POR                                                                                                                                         | '1' = Bit is set                      |                      | '0' = Bit is clea                  | ired                       | x = Bit is unkno     | own                         |  |

| bit 14                                                 | 0 = Some or a                                                                                                                               |                                       | le Input Buffer      | ull<br>r registers are ei          | mpty                       |                      |                             |  |

| bit 14                                                 | IBOV: Input B                                                                                                                               | uffer Overflow                        | Status bit           |                                    |                            |                      |                             |  |

|                                                        | 1 = A write at 0 = No overflo                                                                                                               |                                       | nput Byte regi       | ister occurred (n                  | nust de cleare             | a in software)       |                             |  |

| bit 13-12                                              | Unimplement                                                                                                                                 | ted: Read as '0                       | ,                    |                                    |                            |                      |                             |  |

| bit 11-8                                               |                                                                                                                                             | put Buffer x Sta<br>fer x contains d  |                      | ot been read (re                   | ading buffer w             | vill clear this bit) |                             |  |

|                                                        |                                                                                                                                             | fer x does not c                      |                      |                                    | <b>J</b>                   | ,                    |                             |  |

| bit 7                                                  | OBE: Output                                                                                                                                 | Buffer Empty S                        | tatus bit            |                                    |                            |                      |                             |  |

|                                                        |                                                                                                                                             | ble Output Buffe<br>all of the readal |                      | e empty<br>ffer registers are      | e full                     |                      |                             |  |

| bit 6                                                  | OBUF: Outpu                                                                                                                                 | t Buffer Underfl                      | ow Status bit        |                                    |                            |                      |                             |  |

|                                                        | <ul> <li>1 = A read occurred from an empty Output Byte register (must be cleared in software)</li> <li>0 = No underflow occurred</li> </ul> |                                       |                      |                                    |                            |                      |                             |  |

| bit 5-4                                                | Unimplement                                                                                                                                 | t <b>ed: Read as</b> '0               | ,                    |                                    |                            |                      |                             |  |

| bit 3-0                                                |                                                                                                                                             | Output Buffer x                       |                      |                                    |                            |                      |                             |  |

|                                                        |                                                                                                                                             |                                       |                      | to the buffer will not been transn |                            |                      |                             |  |

#### REGISTER 18-5: PMSTAT: PARALLEL PORT STATUS REGISTER

#### **REGISTER 19-3:** ALCFGRPT: ALARM CONFIGURATION REGISTER R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ALRMEN CHIME AMASK3 AMASK2 AMASK1 AMASK0 ALRMPTR1 ALRMPTR0 bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ARPT6 ARPT5 ARPT4 ARPT3 ARPT2 ARPT1 ARPT0 ARPT7 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15 ALRMEN: Alarm Enable bit 1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 00h and CHIME = 0) 0 = Alarm is disabled bit 14 CHIME: Chime Enable bit 1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 00h to FFh 0 = Chime is disabled; ARPT<7:0> bits stop once they reach 00h bit 13-10 AMASK<3:0>: Alarm Mask Configuration bits 0000 = Every half second 0001 = Every second 0010 = Every 10 seconds 0011 = Every minute 0100 = Every 10 minutes 0101 = Every hour 0110 = Once a day 0111 = Once a week 1000 = Once a month 1001 = Once a year (except when configured for February 29th, once every 4 years) 101x = Reserved; do not use 11xx = Reserved: do not use bit 9-8 ALRMPTR<1:0>: Alarm Value Register Window Pointer bits Points to the corresponding Alarm Value registers when reading ALRMVALH and ALRMVALL registers; the ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00'. ALRMVAL<15:8>: 00 = ALRMMIN 01 = ALRMWD 10 = ALRMMNTH 11 = Unimplemented ALRMVAL<7:0>: 00 = ALRMSEC 01 = ALRMHR 10 = ALRMDAY 11 = Unimplemented bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits 11111111 = Alarm will repeat 255 more times 00000000 = Alarm will not repeat The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

| FIGURE 19-2: | <b>ALARM MASK SETTINGS</b> |

|--------------|----------------------------|

|              |                            |

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month Day      | Hours | Minutes Seconds |

|-------------------------------------------------|-----------------------|----------------|-------|-----------------|

| 0000 – Every half second<br>0001 – Every second |                       |                |       | :               |

| 0010 – Every 10 seconds                         |                       |                |       | : S             |

| 0011 – Every minute                             |                       |                |       | : : : : :       |

| 0100 – Every 10 minutes                         |                       |                |       | : m : s s       |

| 0101 – Every hour                               |                       |                |       | : m m : s s     |

| 0110 – Every day                                |                       |                | h h   | : m m : s s     |

| 0111 – Every week                               | d                     |                | h h   | : m m : s s     |

| 1000 – Every month                              |                       | / d            | h h   | : m m : s s     |

| 1001 – Every year <sup>(1)</sup>                |                       | m m / d d      | h h   | : m m : s s     |

| Note 1: Annually, except when co                | nfigured fo           | r February 29. |       |                 |

| R/W-0               | U-0                              | R/C-0                                   | U-0               | U-0                    | U-0             | R/W-0             | R/W-0      |  |  |

|---------------------|----------------------------------|-----------------------------------------|-------------------|------------------------|-----------------|-------------------|------------|--|--|

| ADON <sup>(1)</sup> |                                  | ADSIDL                                  |                   |                        |                 | FORM1             | FORM0      |  |  |

| bit 15              |                                  |                                         |                   |                        |                 |                   | bit        |  |  |

|                     |                                  |                                         |                   |                        |                 |                   |            |  |  |

| R/W-0               | R/W-0                            | R/W-0                                   | U-0               | U-0                    | R/W-0           | R/W-0, HSC        | R/W-0, HSC |  |  |

| SSRC2               | SSRC1                            | SSRC0                                   | —                 |                        | ASAM            | SAMP              | DONE       |  |  |

| bit 7               |                                  |                                         |                   |                        |                 |                   | bit (      |  |  |

| Legend:             |                                  | C = Clearable                           | e bit             | HSC = Hardv            | vare Settable/C | Clearable bit     |            |  |  |

| R = Readabl         | e bit                            | W = Writable                            |                   | U = Unimpler           | nented bit, rea | d as '0'          |            |  |  |

| -n = Value at       | POR                              | '1' = Bit is set                        |                   | '0' = Bit is cle       |                 | x = Bit is unkr   | iown       |  |  |

|                     |                                  |                                         | <i></i>           |                        |                 |                   |            |  |  |

| bit 15              |                                  | Operating Mode                          |                   |                        |                 |                   |            |  |  |

|                     | 1 = A/D Con<br>0 = A/D Con       | verter module i                         | s operating       |                        |                 |                   |            |  |  |

| bit 14              |                                  | ted: Read as '                          | 0'                |                        |                 |                   |            |  |  |

| bit 13              | -                                | Stop in Idle M                          |                   |                        |                 |                   |            |  |  |

|                     |                                  | -                                       |                   | device enters lo       | dle mode        |                   |            |  |  |

|                     | 0 = Continue                     | es module oper                          | ation in Idle me  | ode                    |                 |                   |            |  |  |

| bit 12-10           | Unimplemer                       | ted: Read as '                          | 0'                |                        |                 |                   |            |  |  |

| bit 9-8             | FORM<1:0>:                       | Data Output F                           | ormat bits        |                        |                 |                   |            |  |  |

|                     |                                  | fractional (sdd                         |                   |                        |                 |                   |            |  |  |

|                     |                                  | nal (dddd_dddo<br>integer (ssss         |                   | ,                      |                 |                   |            |  |  |

|                     | -                                | (0000 00dd d                            |                   | lada)                  |                 |                   |            |  |  |

| bit 7-5             | SSRC<2:0>:                       | Conversion Tr                           | gger Source S     | elect bits             |                 |                   |            |  |  |

|                     |                                  |                                         | sampling and      | starts conversi        | on (auto-conve  | ert)              |            |  |  |

|                     | 110 = Reser                      |                                         |                   |                        |                 |                   |            |  |  |

|                     | 10x = Reserved<br>011 = Reserved |                                         |                   |                        |                 |                   |            |  |  |

|                     |                                  |                                         | s sampling and    | starts convers         | ion             |                   |            |  |  |

|                     |                                  |                                         |                   | ampling and sta        |                 | 1                 |            |  |  |

| bit 4-3             |                                  | ng the SAMP b<br><b>ited:</b> Read as ' |                   | ng and starts co       | nversion        |                   |            |  |  |

| bit 2               | -                                | Sample Auto-Si                          |                   |                        |                 |                   |            |  |  |

|                     |                                  | •                                       |                   | t conversion co        | moletes: SAM    | P bit is auto-set |            |  |  |

|                     | 0 = Sampling                     | g begins when                           | SAMP bit is se    | t                      |                 |                   |            |  |  |

| bit 1               | SAMP: A/D S                      | Sample Enable                           | bit               |                        |                 |                   |            |  |  |

|                     |                                  | ple-and-Hold (\$<br>ple-and-Hold a      |                   | s sampling inpu<br>ing | ıt              |                   |            |  |  |

| bit 0               |                                  | Conversion Stat                         | -                 | ing                    |                 |                   |            |  |  |

|                     |                                  | ersion is done                          |                   |                        |                 |                   |            |  |  |

|                     |                                  | ersion is NOT                           | done              |                        |                 |                   |            |  |  |

| Note 1. T           | he ADC1BUFn                      | registers do no                         | t retain their va |                        | ON is cloared   | Pood out any o    | onvorsion  |  |  |

#### REGISTER 21-1: AD1CON1: A/D CONTROL REGISTER 1

**Note 1:** The ADC1BUFn registers do not retain their values when ADON is cleared. Read out any conversion values from the buffer before disabling the module.

# 24.0 SPECIAL FEATURES

- Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the following sections of the *"PIC24F Family Reference Manual"*.

**"Watchdog Timer (WDT)"** (DS39697)

**"High-Level Device Integration"** (DS39719)

- "Programming and Diagnostics" (DS39716)

PIC24FJ64GA004 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- · Watchdog Timer (WDT)

- Code Protection

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming

- In-Circuit Emulation

# 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location, F80000h. A complete list of locations is shown in Table 24-1. A detailed explanation of the various bit functions is provided in Register 24-1 through Register 24-4.

Note that address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh), which can only be accessed using table reads and table writes.

#### 24.1.1 CONSIDERATIONS FOR CONFIGURING PIC24FJ64GA004 FAMILY DEVICES

In PIC24FJ64GA004 family devices, the configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the two words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 24-1. These are packed representations of the actual device Configuration bits, whose actual locations are distributed among five locations in configuration space. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets.

Note: Configuration data is reloaded on all types of device Resets.

#### TABLE 24-1: FLASH CONFIGURATION WORD LOCATIONS FOR PIC24FJ64GA004 FAMILY DEVICES

| Device      | Configuration Word<br>Addresses |         |  |  |  |

|-------------|---------------------------------|---------|--|--|--|

|             | 1                               | 2       |  |  |  |

| PIC24FJ16GA | 002BFEh                         | 002BFCh |  |  |  |

| PIC24FJ32GA | 0057FEh                         | 0057FCh |  |  |  |

| PIC24FJ48GA | 0083FEh                         | 0083FCh |  |  |  |

| PIC24FJ64GA | 00ABFEh                         | 00ABFCh |  |  |  |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The Configuration bits are reloaded from the Flash Configuration Word on any device Reset.

The upper byte of both Flash Configuration Words in program memory should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

#### REGISTER 24-2: CW2: FLASH CONFIGURATION WORD 2 (CONTINUED)

- bit 4 **IOL1WAY:** IOLOCK One-Way Set Enable bit

- 1 = The IOLOCK (OSCCON<6>) bit can be set once, provided the unlock sequence has been completed. Once set, the Peripheral Pin Select registers cannot be written to a second time.

- 0 = The IOLOCK (OSCCON<6>) bit can be set and cleared as needed, provided the unlock sequence has been completed

#### bit 3 Reserved

- bit 2 I2C1SEL: I2C1 Pin Select bit

- 1 = Use default SCL1/SDA1 pins

- 0 = Use alternate SCL1/SDA1 pins

bit 1-0 **POSCMD<1:0:>** Primary Oscillator Configuration bits

- 11 = Primary oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = EC Oscillator mode is selected

- **Note 1:** These bits are implemented only in devices with a major silicon revision level of B or later (DEVREV register value is 3042h or greater). Refer to **Section 28.0 "Packaging Information"** in the device data sheet for the location and interpretation of product date codes.

#### REGISTER 24-3: DEVID: DEVICE ID REGISTER

| U      | U | U | U | U | U | U | U      |

|--------|---|---|---|---|---|---|--------|

| —      | — | — | _ | _ | _ | — | —      |

| bit 23 |   |   |   |   |   |   | bit 16 |

| U      | U | R      | R      | R      | R      | R      | R      |

|--------|---|--------|--------|--------|--------|--------|--------|

| —      | — | FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 |

| bit 15 |   |        |        |        |        |        | bit 8  |

| R      | R      | R    | R    | R    | R    | R    | R     |

|--------|--------|------|------|------|------|------|-------|

| FAMID1 | FAMID0 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7  | •      |      |      |      |      |      | bit 0 |

| Legend: | R = Read-onl   | v bit | U = Unimplemented bit |

|---------|----------------|-------|-----------------------|

| Legenu. | IN - INeau-Oni | y Dit |                       |

bit 23-14 Unimplemented: Read as '1'

bit 13-6 FAMID<7:0>: Device Family Identifier bits

00010001 = PIC24FJ64GA004 family

- bit 5-0 DEV<5:0>: Individual Device Identifier bits

- 000100 = PIC24FJ16GA002

- 000101 = PIC24FJ32GA002

- 000110 = PIC24FJ48GA002

- 000111 = PIC24FJ64GA002

- 001100 = PIC24FJ16GA004

- 001101 = PIC24FJ32GA004

- 001110 = PIC24FJ48GA004 001111 = PIC24FJ64GA004

### 25.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 25.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

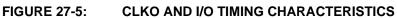

### TABLE 27-19: CLKO AND I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |      | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                             |    |    |     |            |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|----|-----|------------|

| Param<br>No.       | Sym  | Characteristic                                                                                                                                                                                       | Min Typ <sup>(1)</sup> Max Units Conditions |    |    |     | Conditions |

| DO31               | TIOR | Port Output Rise Time                                                                                                                                                                                | —                                           | 10 | 25 | ns  |            |

| DO32               | TIOF | Port Output Fall Time                                                                                                                                                                                | —                                           | 10 | 25 | ns  |            |

| DI35               | Tinp | INTx Pin High or Low<br>Time (output)                                                                                                                                                                | 20                                          | —  | —  | ns  |            |

| DI40               | Trbp | CNx High or Low Time (input)                                                                                                                                                                         | 2                                           | —  | —  | Тсү |            |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

| AC CHARACTERISTICS |               |                                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |      |       |                                          |  |  |  |

|--------------------|---------------|---------------------------------------------------|------------------------------------------------------|----------|------|-------|------------------------------------------|--|--|--|

| Param<br>No.       | Symbol        | Characteristic                                    | Min.                                                 | Тур      | Max. | Units | Conditions                               |  |  |  |

| Clock Parameters   |               |                                                   |                                                      |          |      |       |                                          |  |  |  |

| AD50               | Tad           | A/D Clock Period                                  | 75                                                   | —        | —    | ns    | Tcy = 75 ns, AD1CON3 in<br>default state |  |  |  |

| AD51               | tRC           | A/D Internal RC Oscillator<br>Period              | —                                                    | 250      | —    | ns    |                                          |  |  |  |

|                    |               |                                                   | Conv                                                 | ersion R | ate  |       |                                          |  |  |  |

| AD55               | tCONV         | Conversion Time                                   |                                                      | 12       |      | TAD   |                                          |  |  |  |

| AD56               | FCNV          | Throughput Rate                                   |                                                      | _        | 500  | ksps  | $AVDD \ge 2.7V$                          |  |  |  |

| AD57               | <b>t</b> SAMP | Sample Time                                       |                                                      | 1        |      | Tad   |                                          |  |  |  |

|                    | •             |                                                   | Clock                                                | Paramet  | ters | -     |                                          |  |  |  |

| AD61               | tPSS          | Sample Start Delay from Setting Sample bit (SAMP) | 2                                                    | _        | 3    | Tad   |                                          |  |  |  |

# TABLE 27-21: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

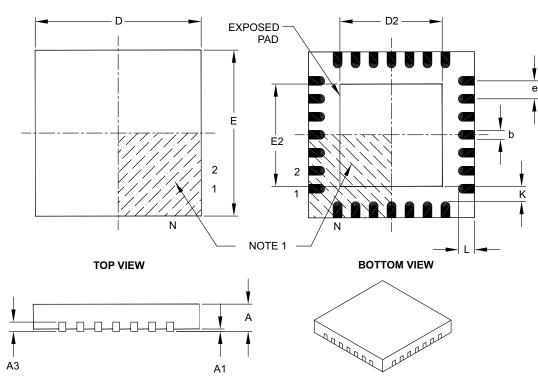

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |      |      |  |

|------------------------|-------------|----------|------|------|--|

|                        | MIN         | NOM      | MAX  |      |  |

| Number of Pins         | N           | 28       |      |      |  |

| Pitch                  | е           | 0.65 BSC |      |      |  |

| Overall Height         | A           | 0.80     | 0.90 | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02 | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |      |      |  |

| Overall Width          | E           | 6.00 BSC |      |      |  |

| Exposed Pad Width      | E2          | 3.65     | 3.70 | 4.20 |  |

| Overall Length         | D           | 6.00 BSC |      |      |  |

| Exposed Pad Length     | D2          | 3.65     | 3.70 | 4.20 |  |

| Contact Width          | b           | 0.23     | 0.30 | 0.35 |  |

| Contact Length         | L           | 0.50     | 0.55 | 0.70 |  |

| Contact-to-Exposed Pad | К           | 0.20     | -    | _    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B