#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj48ga004-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC24FJ64GA004 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG/DISVREG and VCAP/VDDCORE pins (PIC24F J devices only) (see Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},\,6.3\text{V}$  or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)" for an explanation of the ENVREG/DISVREG pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

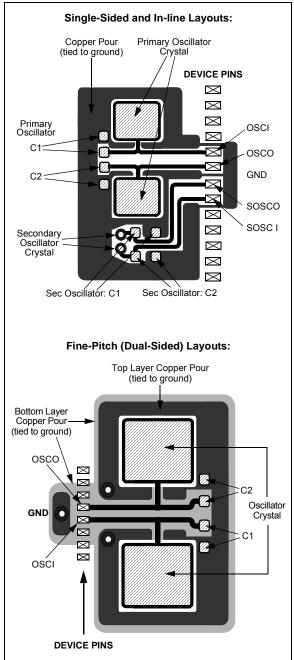

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-5:

### PLACEMENT OF THE OSCILLATOR CIRCUIT

SUGGESTED

# 3.0 CPU

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |

|-------|------------------------------------------------------------------------------------|

|       | intended to be a comprehensive reference                                           |

|       | source. For more information, refer to the                                         |

|       | "PIC24F Family Reference Manual",                                                  |

|       | "CPU" (DS39703).                                                                   |

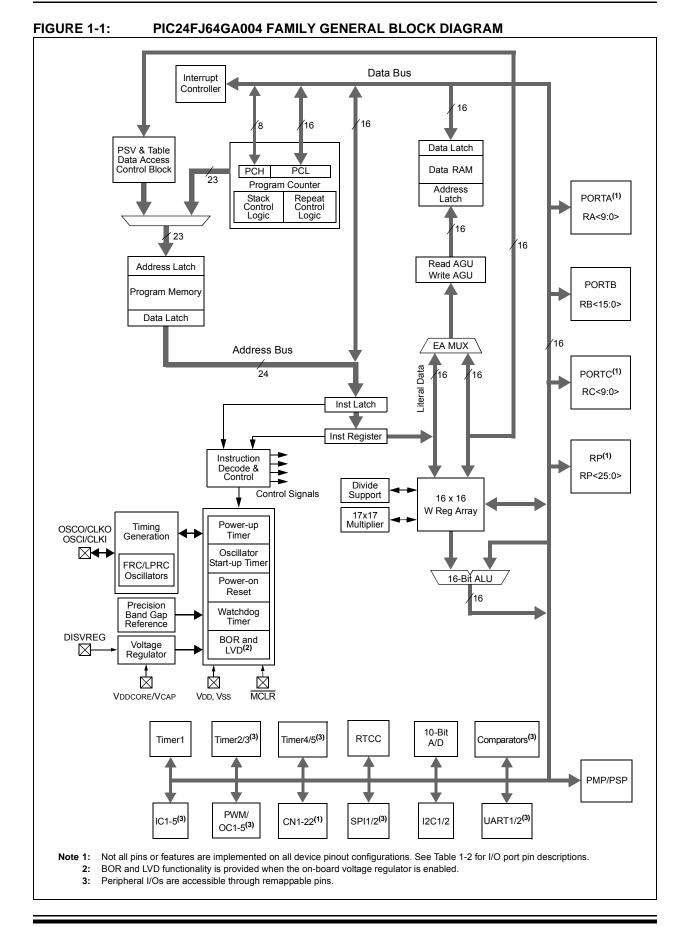

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit, integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A "block diagram of the CPU is shown in Figure 3-1.

# 3.1 Programmer's Model

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory mapped.

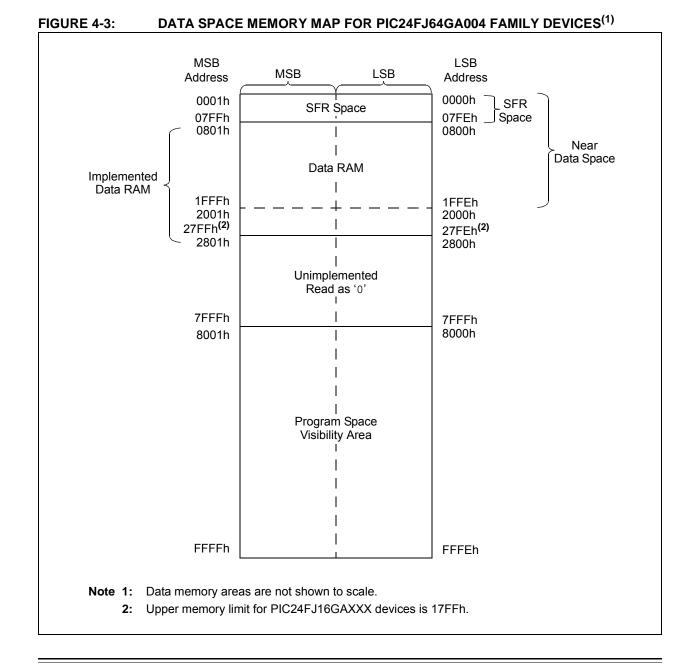

### 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility"). PIC24FJ64GA004 family devices implement a total of 8 Kbytes of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### TABLE 4-17: PARALLEL MASTER/SLAVE PORT REGISTER MAP

|              |      |        |                                                         |        |         | -       |        |                |              |                |              |        |        |        |        |        |        |               |

|--------------|------|--------|---------------------------------------------------------|--------|---------|---------|--------|----------------|--------------|----------------|--------------|--------|--------|--------|--------|--------|--------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14                                                  | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9          | Bit 8        | Bit 7          | Bit 6        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| PMCON        | 0600 | PMPEN  |                                                         | PSIDL  | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN         | PTRDEN       | CSF1           | CSF0         | ALP    |        | CS1P   | BEP    | WRSP   | RDSP   | 0000          |

| PMMODE       | 0602 | BUSY   | IRQM1                                                   | IRQM0  | INCM1   | INCM0   | MODE16 | MODE1          | MODE0        | WAITB1         | WAITB0       | WAITM3 | WAITM2 | WAITM1 | WAITM0 | WAITE1 | WAITE0 | 0000          |

| PMADDR       | 0604 |        | CS1                                                     | _      | _       | _       | ADDR10 | ADDR9          | ADDR8        | ADDR7          | ADDR6        | ADDR5  | ADDR4  | ADDR3  | ADDR2  | ADDR1  | ADDR0  | 0000          |

| PMDOUT1      |      |        | Parallel Port Data Out Register 1 (Buffers 0 and 1) 000 |        |         |         |        |                |              |                |              |        |        | 0000   |        |        |        |               |

| PMDOUT2      | 0606 |        |                                                         |        |         |         | Pa     | rallel Port D  | ata Out Reg  | jister 2 (Buff | fers 2 and 3 | )      |        |        |        |        |        | 0000          |

| PMDIN1       | 0608 |        |                                                         |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 1 (Buffe  | ers 0 and 1) |        |        |        |        |        |        | 0000          |

| PMDIN2       | 060A |        |                                                         |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 2 (Buffe  | ers 2 and 3) |        |        |        |        |        |        | 0000          |

| PMAEN        | 060C |        | PTEN14                                                  | _      | _       | _       | PTEN10 | PTEN9          | PTEN8        | PTEN7          | PTEN6        | PTEN5  | PTEN4  | PTEN3  | PTEN2  | PTEN1  | PTEN0  | 0000          |

| PMSTAT       | 060E | IBF    | IBOV                                                    | —      | _       | IB3F    | IB2F   | IB1F           | IB0F         | OBE            | OBUF         | _      | _      | OB3E   | OB2E   | OB1E   | OB0E   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-18: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File<br>Name | Addr                                                   | Bit 15 | Bit 14                                               | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|--------------------------------------------------------|--------|------------------------------------------------------|---------|---------|---------|--------|----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL      | 0620 Alarm Value Register Window Based on ALRMPTR<1:0> |        |                                                      |         |         |         |        |          |          |       |       |       |       | xxxx  |       |       |       |               |

| ALCFGRPT     | 0622                                                   | ALRMEN | CHIME                                                | AMASK3  | AMASK2  | AMASK1  | AMASK0 | ALRMPTR1 | ALRMPTR0 | ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL       | 0624                                                   |        | RTCC Value Register Window Based on RTCPTR<1:0> xxxx |         |         |         |        |          |          |       |       |       |       | xxxx  |       |       |       |               |

| RCFGCAL      | 0626                                                   | RTCEN  |                                                      | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1  | RTCPTR0  | CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: DUAL COMPARATOR REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CMCON        | 0630 | CMIDL  | _      | C2EVT  | C1EVT  | C2EN   | C1EN   | C2OUTEN | C1OUTEN | C2OUT | C10UT | C2INV | C1INV | C2NEG | C2POS | C1NEG | C1POS | 0000          |

| CVRCON       | 0632 | —      | _      | _      | —      | _      |        | _       | _       | CVREN | CVROE | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|------------------------|--------|--------|--------|--------|--------|-------------|--------------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CRCCON       | 0640 | _      | _                      | CSIDL  | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0      | CRCFUL       | CRCMPT | _     | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 | 0040          |

| CRCXOR       | 0642 | X15    | X14                    | X13    | X12    | X11    | X10    | X9     | X8          | X7           | X6     | X5    | X4    | X3    | X2    | X1    | _     | 0000          |

| CRCDAT       | 0644 |        |                        |        |        |        |        | (      | CRC Data Ir | nput Registe | er     |       |       |       |       |       |       | 0000          |

| CRCWDAT      | 0646 |        | CRC Result Register 00 |        |        |        |        |        |             |              |        |       |       | 0000  |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused addresses should be programmed with FFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

Configuration Word values are stored in the last two locations of program memory. Performing a page erase operation on the last page of program memory clears these values and enables code protection. As a result, avoid performing page erase operations on the last page of program memory.

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat Steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY BLOCK

| ; Set up | NVMCON  | I for block erase operation          |   |                                       |  |

|----------|---------|--------------------------------------|---|---------------------------------------|--|

| 1        | MOV     | #0x4042, W0                          | ; |                                       |  |

| 1        | MOV     | W0, NVMCON                           | ; | Initialize NVMCON                     |  |

| ; Init p | pointer | to row to be ERASED                  |   |                                       |  |

| 1        | MOV     | <pre>#tblpage(PROG_ADDR), W0</pre>   | ; |                                       |  |

| 1        | MOV     | W0, TBLPAG                           | ; | Initialize PM Page Boundary SFR       |  |

| 1        | MOV     | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; | Initialize in-page EA[15:0] pointer   |  |

|          | TBLWTL  | WO, [WO]                             | ; | Set base address of erase block       |  |

| 1        | DISI    | #5                                   | ; | Block all interrupts with priority <7 |  |

|          |         |                                      | ; | for next 5 instructions               |  |

| 1        | MOV     | #0x55, W0                            |   |                                       |  |

| 1        | MOV     | W0, NVMKEY                           | ; | Write the 55 key                      |  |

| 1        | MOV     | #0xAA, W1                            | ; |                                       |  |

| 1        | MOV     | W1, NVMKEY                           | ; | Write the AA key                      |  |

| 1        | BSET    | NVMCON, #WR                          | ; | Start the erase sequence              |  |

| 1        | NOP     |                                      | ; | Insert two NOPs after the erase       |  |

| ]        | NOP     |                                      | ; | command is asserted                   |  |

|          |         |                                      |   |                                       |  |

#### 5.5.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOPx bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit (see Example 5-4).

#### EXAMPLE 5-4: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

| ; Setup a p               | pointer to data Program Memory                             |    |                                                      |

|---------------------------|------------------------------------------------------------|----|------------------------------------------------------|

| MOV                       | <pre>#tblpage(PROG_ADDR), W0</pre>                         | ;  |                                                      |

| MOV                       | W0, TBLPAG                                                 | ;1 | Initialize PM Page Boundary SFR                      |

| MOV                       | <pre>#tbloffset(PROG_ADDR), W0</pre>                       | ;1 | initialize a register with program memory address    |

| MOV                       | #LOW_WORD_N, W2                                            | ;  |                                                      |

| MOV                       | #HIGH_BYTE_N, W3                                           | ;  |                                                      |

| TBLWTL                    | W2, [W0]                                                   | ;  | Write PM low word into program latch                 |

| TBLWTH                    | W3, [W0++]                                                 | ;  | Write PM high byte into program latch                |

| ; Setup NVN<br>MOV<br>MOV | 4CON for programming one word<br>#0x4003, W0<br>W0, NVMCON | ;  | data Program Memory<br>Set NVMOP bits to 0011        |

| DISI                      | #5                                                         | ;  | Disable interrupts while the KEY sequence is written |

| MOV                       | #0x55, W0                                                  | ;  | Write the key sequence                               |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| MOV                       | #0xAA, W0                                                  |    |                                                      |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| BSET                      | NVMCON, #WR                                                | ;  | Start the write cycle                                |

| NOP                       |                                                            | ;  | 2 NOPs required after setting WR                     |

| NOP                       |                                                            | ;  |                                                      |

|                           |                                                            |    |                                                      |

#### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. Refer to **Section 8.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | FNOSC<2:0> Configuration bits |

| BOR        | (CW2<10:8>)                   |

| MCLR       | COSC<2:0> Control bits        |

| WDTO       | (OSCCON<14:12>)               |

| SWR        |                               |

#### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the system Master Reset Signal, SYSRST, is released after the POR and PWRT delay times expire.

The time that the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay        | System Clock<br>Delay | Notes         |

|--------------------|--------------|---------------------|-----------------------|---------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT + TRST | _                     | 1, 2, 7       |

|                    | FRC, FRCDIV  | TPOR + TPWRT + TRST | TFRC                  | 1, 2, 3, 7    |

|                    | LPRC         | TPOR + TPWRT + TRST | TLPRC                 | 1, 2, 3, 7    |

|                    | ECPLL        | TPOR + TPWRT + TRST | TLOCK                 | 1, 2, 4, 7    |

|                    | FRCPLL       | TPOR + TPWRT + TRST | TFRC + TLOCK          | 1, 2, 3, 4, 7 |

|                    | XT, HS, SOSC | TPOR + TPWRT + TRST | Tost                  | 1, 2, 5, 7    |

|                    | XTPLL, HSPLL | TPOR + TPWRT + TRST | Tost + Tlock          | 1, 2, 4, 5, 7 |

| BOR                | EC           | TPWRT + TRST        | —                     | 2, 7          |

|                    | FRC, FRCDIV  | TPWRT + TRST        | TFRC                  | 2, 3, 7       |

|                    | LPRC         | TPWRT + TRST        | TLPRC                 | 2, 3, 7       |

|                    | ECPLL        | TPWRT + TRST        | TLOCK                 | 2, 4, 7       |

|                    | FRCPLL       | TPWRT + TRST        | TFRC + TLOCK          | 2, 3, 4, 7    |

|                    | XT, HS, SOSC | TPWRT + TRST        | Tost                  | 2, 5, 7       |

|                    | XTPLL, HSPLL | TPWRT + TRST        | TFRC + TLOCK          | 2, 3, 4, 7    |

| All Others         | Any Clock    | TRST                | —                     | 7             |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

- **2:** TPWRT = 64 ms nominal if regulator is disabled (ENVREG tied to Vss).

- **3:** TFRC and TLPRC = RC Oscillator Start-up Times.

- **4:** TLOCK = PLL Lock Time.

- **5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- 6: If Two-Speed Start-up is enabled, regardless of the primary oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

- 7: TRST = Internal State Reset Timer

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 T3CKR<4:0>: Assign Timer3 External Clock (T3CK) to the Corresponding RPn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T2CKR<4:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn Pin bits

#### REGISTER 10-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| _      | —   | —   | T5CKR4 | T5CKR3 | T5CKR2 | T5CKR1 | T5CKR0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 T5CKR<4:0>: Assign Timer5 External Clock (T5CK) to the Corresponding RPn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T4CKR<4:0>: Assign Timer4 External Clock (T4CK) to the Corresponding RPn Pin bits

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | —   | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |     |     |        |        |        |        | bit 0  |

|        |     |     |        |        |        |        |        |

|        |     |     |        |        |        |        |        |

#### REGISTER 10-11: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 12-8  | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                     |

| bit 4-0   | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits    |

#### REGISTER 10-12: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| 11.0                              | 11.0 | 11.0             | 11.0                               | 11.0              | 11.0                 | 11.0  | 11.0               |  |

|-----------------------------------|------|------------------|------------------------------------|-------------------|----------------------|-------|--------------------|--|

| U-0                               | U-0  | U-0              | U-0                                | U-0               | U-0                  | U-0   | U-0                |  |

| _                                 |      | —                | —                                  | —                 |                      | _     | —                  |  |

| bit 15                            |      |                  |                                    |                   |                      |       | bit 8              |  |

|                                   |      |                  |                                    |                   |                      |       |                    |  |

| U-0                               | U-0  | U-0              | R/W-1                              | R/W-1             | R/W-1                | R/W-1 | R/W-1              |  |

| —                                 |      | —                | SS1R4                              | SS1R3             | SS1R2                | SS1R1 | SS1R0              |  |

| bit 7                             |      |                  |                                    |                   |                      |       | bit 0              |  |

|                                   |      |                  |                                    |                   |                      |       |                    |  |

| Legend:                           |      |                  |                                    |                   |                      |       |                    |  |

| R = Readable bit W = Writable bit |      | bit              | U = Unimplemented bit, read as '0' |                   |                      |       |                    |  |

| -n = Value at POR '1              |      | '1' = Bit is set |                                    | '0' = Bit is clea | '0' = Bit is cleared |       | x = Bit is unknown |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the Corresponding RPn Pin bits

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Serial Peripheral Interface (SPI)"* (DS39699)

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the SPI and SIOP Motorola<sup>®</sup> interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 15-1 and Figure 15-2.

Depending on the pin count, PIC24FJ64GA004 family devices offer one or two SPI modules on a single device.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON1 or SPIxCON2 refers to the control register for the SPI1 or SPI2 module. To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit (SPIxCON1<9>).

- 5. If the CKE bit is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

| R/W-0                | U-0                                 | R/W-0                                                                | R/W-0               | R/W-0                             | U-0                         | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> |

|----------------------|-------------------------------------|----------------------------------------------------------------------|---------------------|-----------------------------------|-----------------------------|----------------------|----------------------|

| UARTEN <sup>(1</sup> | ) _                                 | USIDL                                                                | IREN <sup>(2)</sup> | RTSMD                             | _                           | UEN1                 | UEN0                 |

| bit 15               |                                     |                                                                      |                     | ·                                 |                             | •                    | bit 8                |

|                      |                                     |                                                                      | <b>D</b> 444 A      | <b>D</b> 444 0                    | <b>D</b> 444 0              | <b>D</b> 444 A       | <b>D</b> 444 0       |

| R/C-0, HC            |                                     | R/W-0, HC                                                            | R/W-0               | R/W-0                             | R/W-0                       | R/W-0                | R/W-0                |

| WAKE                 | LPBACK                              | ABAUD                                                                | RXINV               | BRGH                              | PDSEL1                      | PDSEL0               | STSEL                |

| bit 7                |                                     |                                                                      |                     |                                   |                             |                      | bit 0                |

| Legend:              |                                     | C = Clearable                                                        | hit                 | HC = Hardwa                       | are Clearable bi            | t                    |                      |

| R = Readat           | ole hit                             | W = Writable b                                                       |                     |                                   | mented bit, read            |                      |                      |

| -n = Value a         |                                     | '1' = Bit is set                                                     | it.                 | '0' = Bit is cle                  |                             |                      |                      |

| -n = value a         | al POR                              | I = BILIS SEL                                                        |                     | 0 = Bit is cle                    | ared                        | x = Bit is unkn      | IOWN                 |

| bit 15               |                                     | ARTx Enable bit <sup>(</sup>                                         | 1)                  |                                   |                             |                      |                      |

| bit io               |                                     | s enabled; all UA                                                    |                     | e controlled by                   | UARTx as defin              | ed by UEN<1.         | )>                   |

|                      |                                     | s disabled; all UA                                                   |                     |                                   |                             |                      |                      |

| bit 14               |                                     | ted: Read as '0                                                      |                     |                                   |                             |                      |                      |

| bit 13               | USIDL: UAR                          | Tx Stop in Idle M                                                    | ode bit             |                                   |                             |                      |                      |

|                      | 1 = Discontir                       | nues module ope                                                      | ration when         | device enters le                  | dle mode                    |                      |                      |

|                      |                                     | es module operation                                                  |                     |                                   |                             |                      |                      |

| bit 12               | IREN: IrDA®                         | Encoder and De                                                       | coder Enabl         | e bit <sup>(2)</sup>              |                             |                      |                      |

|                      |                                     | oder and decode                                                      |                     |                                   |                             |                      |                      |

| bit 11               |                                     | de Selection for I                                                   |                     |                                   |                             |                      |                      |

| 2                    | $1 = \overline{\text{UxRTS}} p$     | oin in Simplex mo<br>oin in Flow Contr                               | ode                 |                                   |                             |                      |                      |

| bit 10               |                                     | ted: Read as '0                                                      |                     |                                   |                             |                      |                      |

| bit 9-8              | •                                   | JARTx Enable bi                                                      |                     |                                   |                             |                      |                      |

|                      | 10 = UxTX, U<br>01 = UxTX, U        | JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins are | d UxRTS pins are er | ns are enabled<br>habled and used | and used<br>d; UxCTS pin is | controlled by F      | ORT latches          |

| bit 7                | WAKE: Wake                          | e-up on Start Bit                                                    | Detect Durin        | g Sleep Mode I                    | Enable bit                  |                      |                      |

|                      | hardware                            | vill continue to sa<br>e on following ris                            | -                   | RX pin; interrup                  | t is generated o            | n falling edge, b    | it is cleared in     |

| hit C                |                                     | -up is enabled                                                       | Mada Salaat         | hit                               |                             |                      |                      |

| bit 6                |                                     | ARTx Loopback  <br>Loopback mode                                     |                     | DIL                               |                             |                      |                      |

|                      |                                     | k mode is disabl                                                     |                     |                                   |                             |                      |                      |

| bit 5                |                                     | o-Baud Enable b                                                      |                     |                                   |                             |                      |                      |

|                      | cleared i                           | baud rate meas<br>n hardware upor                                    | n completion        |                                   | ter – requires re           | ception of a Sy      | nc field (55h);      |

|                      | 0 = Baud rat                        | e measurement                                                        | is disabled o       | r completed                       |                             |                      |                      |

|                      | f UARTEN = 1, t<br>Section 10.4 "Pe |                                                                      |                     |                                   |                             | vailable RPn p       | in. See              |

|                      | This feature is or                  | -                                                                    |                     |                                   |                             |                      |                      |

|                      | Bit availability de                 | -                                                                    |                     |                                   |                             |                      |                      |

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER

**3:** Bit availability depends on pin availability.

| at 15       bit         RW-0       R/W-0       R/W-0 <sup>(2)</sup> U-0       R/W-0 <sup>(2)</sup> R/W-0       R/W-0       R/W-0         CSF1       CSF0       ALP       -       CS1P       BEP       WRSP       RDSP         poit 7       bit       -       CS1P       BEP       WRSP       RDSP         poit 7       bit       -       CS1P       BEP       WRSP       RDSP         poit 7       bit       -       CS1P       BEP       WRSP       RDSP         poit 7       -       bit       -       CS1P       BEP       WRSP       RDSP         poit 7       -       -       CS1P       BEP       WRSP       RDSP       bit         acgend:       -       -       CS1P       BEP       WRSP       RDSP       bit         commodel point 1       CS1P       DEF       WRSP       RDSP       bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0         | U-0                                                                  | R/W-0           | R/W-0                  | R/W-0                  | R/W-0          | R/W-0           | R/W-0  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------|-----------------|------------------------|------------------------|----------------|-----------------|--------|--|--|--|--|

| RW-0       RW-0       RW-0 <sup>(2)</sup> U-0       RW-0 <sup>(2)</sup> RW-0       RW and 0       Image: Constanding the constandis the constanding the constanding the cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PMPEN         |                                                                      | PSIDL           | ADRMUX1 <sup>(1)</sup> | ADRMUX0 <sup>(1)</sup> | PTBEEN         | PTWREN          | PTRDEN |  |  |  |  |

| CSF1       CSF0       ALP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 15        |                                                                      |                 |                        |                        |                |                 | bit 8  |  |  |  |  |

| CSF1       CSF0       ALP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P/M/0         | P///_0                                                               |                 | 11-0                   | P/M/_0(2)              | P/M/ 0         | P/M/_0          | P/M/_0 |  |  |  |  |

| bit 7                                                                                                                                                                                                        |               | -                                                                    |                 | 0-0                    |                        |                | -               |        |  |  |  |  |

| egend:         2 = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PMPEN: PMP Enable bit       1 = PMP is enabled       0 = PMP is disabled, no off-chip access is performed         bit 13       PSIDL: PMP Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         bit 13       PSIDL: PMP Stop in Idle Mode bit       1 = Discontinues module operation in Idle mode         bit 13       PSIDL: PMP Stop in Idle Mode bit       1 = Discontinues module operation in Idle mode         bit 13       PSIDL: PMP Stop in Idle Mode bit       1 = Discontinues module operation in Idle mode         bit 14       Unimplemented: Read as '0'       11 = Reserved         bit 15       ADRMUX<1:0>: Address are multiplexed on the PMD<7:0> pins, upper 3 bits are multiplexed or PMA<10:8>         bit 10       PTBEEN: PMP Byte Enable Port Enable bit (16-Bit Master mode)       1 = PMBE port is disabled         bit 9       PTWREN: PMP Write Enable Strobe Port Enable bit       1 = PMRD/PMWR port is disabled         bit 8       PTRDEN: PMP Read/Write Strobe Port Enable bit       1 = PMRD/PMWR port is disabled         bit 7-6       CSF<1:0>: Chip Select Function bits       1 = Reserved         bit 8       PTRDEN: PMP Read/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | CSFU                                                                 | ALF             | —                      | COTF                   | DLF            | WNOF            | -      |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PMPEN: PMP Enable bit       1 = PMP is enabled       0 = PMP is disabled, no off-chip access is performed         bit 14       Unimplemented: Read as '0'       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation when device enters Idle mode         bit 12-11       ADRMUX<1:0:: Address/Data Multiplexing Selection bits <sup>(1)</sup> 1 = Reserved       10 = All 16 bits of address are multiplexed on the PMD<7:0> pins         bit 10       PTBEEN: PMP Byte Enable Port Enable bit (16-Bit Master mode)       1 = PMBE port is disabled       0 = PMWRPMENB port is enabled         bit 9       PTWREN: PMP Write Enable Strobe Port Enable bit       1 = PMWRPMENB port is enabled       0 = PMWRPMENB port is enabled         bit 8       PTRDEN: PMP Read/Write Strobe Port Enable bit       1 = PMWRP/PMWR port is enabled       0 = PMWR/PMWR port is disabled         bit 7-6       CSF<1:0:: Chip Select Function bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                      |                 |                        |                        |                |                 | bit t  |  |  |  |  |

| n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PMPEN: PMP Enable bit<br>1 = PMP is enabled<br>0 = PMP is disabled, no off-chip access is performed<br>bit 14 Unimplemented: Read as '0'<br>PSDL: PMP Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode<br>10 = Continues module operation in Idle mode<br>10 = Continues module operation in Idle mode<br>11 = Reserved<br>10 = All 16 bits of address are multiplexed on the PMD<7:0> pins<br>01 = Lower 8 bits of address are multiplexed on the PMD<7:0> pins, upper 3 bits are multiplexed or<br>PMA<10.8><br>00 = Address and data appear on separate pins<br>bit 10 PTBEEN: PMP Byte Enable Port Enable bit (16-Bit Master mode)<br>1 = PMBE port is enabled<br>0 = PMBE port is enabled<br>0 = PMBE port is disabled<br>0 = PMWR/PMENB port is enabled<br>0 = PMWR/PMENB port is disabled<br>0 = PMWR/PMENB port is disabled<br>0 = PMWR/PMENB port is disabled<br>0 = PMRD/PMWR port is disabled<br>0 = Reserved<br>0 =                          | Legend:       |                                                                      |                 |                        |                        |                |                 |        |  |  |  |  |

| <ul> <li>phi 15 PMPEN: PMP Enable bit</li> <li>1 = PMP is enabled</li> <li>0 = PMP is disabled, no off-chip access is performed</li> <li>unimplemented: Read as '0'</li> <li>phi 13 PSIDL: PMP Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>o = Continues module operation in Idle mode</li> <li>1 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on the PMD&lt;7:0&gt; pins</li> <li>01 = Aul 16 bits of address are multiplexed on the PMD&lt;7:0&gt; pins, upper 3 bits are multiplexed on the PMD&lt;7:0&gt; pins, upper 3 bits are multiplexed on the PMD&lt;7:0&gt; pins, upper 3 bits are multiplexed on PMA&lt;10.8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>pt = Lower 8 bits of address are multiplexed on the PMD&lt;7:0&gt; pins, upper 3 bits are multiplexed or PMA&lt;10.8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>pt = DMBE port is enabled</li> <li>0 = PMBE port is enabled</li> <li>0 = PMBE port is enabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMWR/PMENB port is disabled</li> <li>0 = PMWR/PMENB port is disabled</li> <li>0 = PMRD/PMWR port is disabled</li> <li>0 = PMRCS1 functions as chip set</li> <li>0 = Reserved</li> <l< td=""><td>R = Readabl</td><td>e bit</td><td>W = Writable</td><td>bit</td><td>U = Unimpleme</td><td>ented bit, rea</td><td>d as '0'</td><td></td></l<></ul> | R = Readabl   | e bit                                                                | W = Writable    | bit                    | U = Unimpleme          | ented bit, rea | d as '0'        |        |  |  |  |  |

| <pre>1 = PMP is enabled<br/>0 = PMP is disabled, no off-chip access is performed<br/>0 = PMP is disabled, no off-chip access is performed<br/>0 = Continues module operation when device enters Idle mode<br/>0 = Continues module operation in Idle mode<br/>0 = ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup><br/>11 = Reserved<br/>10 = All 16 bits of address are multiplexed on the PMD&lt;7:0&gt; pins<br/>01 = Lower 8 bits of address are multiplexed on the PMD&lt;7:0&gt; pins, upper 3 bits are multiplexed of<br/>PMA&lt;10:8&gt;<br/>00 = Address and data appear on separate pins<br/>00 = Address and data appear on separate pins<br/>01 = PMBE port is enabled<br/>0 = PMBE port is disabled<br/>0 = PMBE port is disabled<br/>0 = PMWR/PMENB port is enabled<br/>0 = PMWR/PMENB port is disabled<br/>0 = PMWR/PMENB port is disabled<br/>0 = PMWR/PMENB port is disabled<br/>0 = PMRD/PMWR port is disabled<br/>0 = PMCRD/PMWR port is disabled<br/>0 = Reserved<br/>10 = PMCS1 functions as chip set<br/>01 = Reserved<br/>10 = Active-ligh (PMALL and PMALH)<br/>0 = Active-ligh (PMALL and PMALH)<br/>0 = Active-ligh (PMALL and PMALH)<br/>0 = Active-ligh (PMCS1/PMCS1)<br/>0 = Active-low (PMCS1/PMCS1)</pre>                                                                                                                                                                                                                                                                                                                                                                                                       | -n = Value at | POR                                                                  | '1' = Bit is se | t                      | '0' = Bit is clea      | red            | x = Bit is unkr | iown   |  |  |  |  |

| <pre>1 = PMP is enabled<br/>0 = PMP is disabled, no off-chip access is performed<br/>0 = PMP is disabled, no off-chip access is performed<br/>0 = Continues module operation when device enters Idle mode<br/>0 = Continues module operation in Idle mode<br/>0 = ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup><br/>11 = Reserved<br/>10 = All 16 bits of address are multiplexed on the PMD&lt;7:0&gt; pins<br/>01 = Lower 8 bits of address are multiplexed on the PMD&lt;7:0&gt; pins, upper 3 bits are multiplexed of<br/>PMA&lt;10:8&gt;<br/>00 = Address and data appear on separate pins<br/>00 = Address and data appear on separate pins<br/>01 = PMBE port is enabled<br/>0 = PMBE port is disabled<br/>0 = PMBE port is disabled<br/>0 = PMWR/PMENB port is enabled<br/>0 = PMWR/PMENB port is disabled<br/>0 = PMWR/PMENB port is disabled<br/>0 = PMWR/PMENB port is disabled<br/>0 = PMRD/PMWR port is disabled<br/>0 = PMCRD/PMWR port is disabled<br/>0 = Reserved<br/>10 = PMCS1 functions as chip set<br/>01 = Reserved<br/>10 = Active-ligh (PMALL and PMALH)<br/>0 = Active-ligh (PMALL and PMALH)<br/>0 = Active-ligh (PMALL and PMALH)<br/>0 = Active-ligh (PMCS1/PMCS1)<br/>0 = Active-low (PMCS1/PMCS1)</pre>                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                      |                 |                        |                        |                |                 |        |  |  |  |  |