Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 48KB (16K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

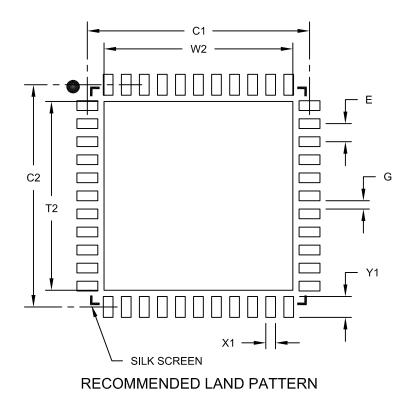

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj48ga004t-i-ml |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | I                             | Pin Number    |                    |     |                             |                                                                                            |

|----------|-------------------------------|---------------|--------------------|-----|-----------------------------|--------------------------------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer             | Description                                                                                |

| CN0      | 12                            | 9             | 34                 | I   | ST                          | Interrupt-on-Change Inputs.                                                                |

| CN1      | 11                            | 8             | 33                 | Ι   | ST                          |                                                                                            |

| CN2      | 2                             | 27            | 19                 | Ι   | ST                          |                                                                                            |

| CN3      | 3                             | 28            | 20                 | I   | ST                          |                                                                                            |

| CN4      | 4                             | 1             | 21                 | I   | ST                          |                                                                                            |

| CN5      | 5                             | 2             | 22                 | Ι   | ST                          |                                                                                            |

| CN6      | 6                             | 3             | 23                 | I   | ST                          |                                                                                            |

| CN7      | 7                             | 4             | 24                 | I   | ST                          |                                                                                            |

| CN8      | _                             | _             | 25                 | Ι   | ST                          |                                                                                            |

| CN9      | —                             | _             | 26                 | I   | ST                          |                                                                                            |

| CN10     | _                             | _             | 27                 | Ι   | ST                          |                                                                                            |

| CN11     | 26                            | 23            | 15                 | Ι   | ST                          |                                                                                            |

| CN12     | 25                            | 22            | 14                 | Ι   | ST                          |                                                                                            |

| CN13     | 24                            | 21            | 11                 | Ι   | ST                          |                                                                                            |

| CN14     | 23                            | 20            | 10                 | Ι   | ST                          |                                                                                            |

| CN15     | 22                            | 19            | 9                  | Ι   | ST                          |                                                                                            |

| CN16     | 21                            | 18            | 8                  | Ι   | ST                          |                                                                                            |

| CN17     | _                             | _             | 3                  | Ι   | ST                          |                                                                                            |

| CN18     | _                             | _             | 2                  | Ι   | ST                          |                                                                                            |

| CN19     | _                             | _             | 5                  | Ι   | ST                          |                                                                                            |

| CN20     | _                             | _             | 4                  | Ι   | ST                          |                                                                                            |

| CN21     | 18                            | 15            | 1                  | Ι   | ST                          |                                                                                            |

| CN22     | 17                            | 14            | 44                 | Ι   | ST                          |                                                                                            |

| CN23     | 16                            | 13            | 43                 | Ι   | ST                          |                                                                                            |

| CN24     | 15                            | 12            | 42                 | Ι   | ST                          |                                                                                            |

| CN25     | —                             | —             | 37                 | I   | ST                          | ]                                                                                          |

| CN26     | _                             | _             | 38                 | I   | ST                          | 1                                                                                          |

| CN27     | 14                            | 11            | 41                 | I   | ST                          | ]                                                                                          |

| CN28     | _                             | _             | 36                 | I   | ST                          | 1                                                                                          |

| CN29     | 10                            | 7             | 31                 | I   | ST                          | 1                                                                                          |

| CN30     | 9                             | 6             | 30                 | I   | ST                          | 1                                                                                          |

| CVREF    | 25                            | 22            | 14                 | 0   | ANA                         | Comparator Voltage Reference Output.                                                       |

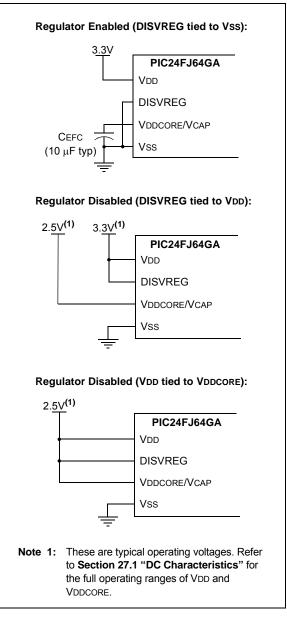

| DISVREG  | 19                            | 16            | 6                  | Ι   | ST                          | Voltage Regulator Disable.                                                                 |

| INT0     | 16                            | 13            | 43                 | I   | ST                          | External Interrupt Input.                                                                  |

| MCLR     | 1                             | 26            | 18                 | I   | ST                          | Master Clear (device Reset) Input. This line is brought lov to cause a Reset.              |

| Legend:  | TTL = TTL inp<br>ANA = Analog |               | utput              |     | ST = S<br>I <sup>2</sup> C™ | to cause a Reset.<br>Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer |

## TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Note 1: Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

# 3.2 CPU Control Registers

## REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                  | U-0                  | U-0                                    | U-0             | U-0                                      | U-0                | U-0               | R/W-0           |

|----------------------|----------------------|----------------------------------------|-----------------|------------------------------------------|--------------------|-------------------|-----------------|

| —                    | _                    | _                                      | —               | _                                        |                    | _                 | DC              |

| bit 15               |                      |                                        |                 |                                          |                    |                   | bit 8           |

|                      |                      |                                        |                 |                                          |                    |                   |                 |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                   | R-0             | R/W-0                                    | R/W-0              | R/W-0             | R/W-0           |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>                    | RA              | N                                        | OV                 | Z                 | С               |

| bit 7                |                      |                                        |                 |                                          |                    |                   | bit (           |

| Legend:              |                      |                                        |                 |                                          |                    |                   |                 |

| R = Readat           | ole bit              | W = Writable                           | oit             | U = Unimplem                             | nented bit, read   | d as '0'          |                 |

| -n = Value a         | at POR               | '1' = Bit is set                       |                 | '0' = Bit is clea                        |                    | x = Bit is unki   | nown            |

|                      |                      |                                        |                 |                                          |                    |                   |                 |

| bit 15-9             | -                    | ted: Read as '0                        |                 |                                          |                    |                   |                 |

| bit 8                |                      | f Carry/Borrow I                       |                 |                                          |                    |                   |                 |

|                      |                      | out from the 4th sult occurred         | low-order bit ( | for byte-sized da                        | ata) or 8th low-   | order bit (for we | ord-sized data  |

|                      |                      |                                        | h or 8th low-o  | rder bit of the re                       | sult has occurr    | red               |                 |

| bit 7-5              | IPL<2:0>: CF         | PU Interrupt Price                     | ority Level Sta | itus bits <sup>(1,2)</sup>               |                    |                   |                 |

|                      |                      |                                        |                 | i); user interrupts                      | s are disabled     |                   |                 |

|                      |                      | nterrupt Priority                      |                 |                                          |                    |                   |                 |

|                      |                      | nterrupt Priority<br>nterrupt Priority |                 |                                          |                    |                   |                 |

|                      |                      | nterrupt Priority                      |                 |                                          |                    |                   |                 |

|                      | 010 = CPU Ir         | nterrupt Priority                      | Level is 2 (10  | )                                        |                    |                   |                 |

|                      |                      | nterrupt Priority<br>nterrupt Priority |                 |                                          |                    |                   |                 |

| bit 4                |                      | Loop Active bit                        |                 |                                          |                    |                   |                 |

|                      |                      | oop in progress                        |                 |                                          |                    |                   |                 |

|                      |                      | oop not in prog                        |                 |                                          |                    |                   |                 |

| bit 3                | N: ALU Nega          | itive bit                              |                 |                                          |                    |                   |                 |

|                      | 1 = Result wa        |                                        | , .             | <i></i> 、                                |                    |                   |                 |

| 1.11.0               |                      | as non-negative                        | (zero or posi   | tive)                                    |                    |                   |                 |

| bit 2                | OV: ALU Ove          |                                        | uned (O'e eero  | nlanaant) arithma                        | atia in this avith | motio operatio    | _               |

|                      |                      | occurred for sig                       |                 | plement) arithm                          | etic in this anth  | imetic operatio   | n               |

| bit 1                | Z: ALU Zero          | bit                                    |                 |                                          |                    |                   |                 |

|                      |                      |                                        |                 | as set it at some<br>ets the Z bit has o |                    |                   | sult)           |

| bit 0                | C: ALU Carry         | //Borrow bit                           |                 |                                          |                    |                   |                 |

|                      |                      |                                        |                 | bit of the result o<br>bit of the result |                    |                   |                 |

| Note 1: 7            | The IPL Status bi    | its are read-only                      | when NSTD       | IS (INTCON1<1                            | <b>5&gt;) =</b> 1. |                   |                 |

|                      | The IPL Status bi    | -                                      |                 |                                          |                    | n the CPU Inte    | errupt Priority |

| 1                    | aval (IDL) Thay      | value in parenth                       | oooo indiaata   | a tha IDI when                           |                    |                   | -               |

2: The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

## TABLE 4-8: OUTPUT COMPARE REGISTER MAP

|              |      |        | •••••  |        | LOIOI  |        |        |          |           |             |          |       |       |        |       |       |       |               |

|--------------|------|--------|--------|--------|--------|--------|--------|----------|-----------|-------------|----------|-------|-------|--------|-------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8     | Bit 7       | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| OC1RS        | 0180 |        |        |        |        |        |        | Output 0 | Compare 1 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC1R         | 0182 |        |        |        |        |        |        | Οι       | tput Comp | are 1 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC1CON       | 0184 | _      | —      | OCSIDL | _      | _      | —      | —        | _         | _           | —        | —     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC2RS        | 0186 |        |        |        |        |        |        | Output 0 | Compare 2 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC2R         | 0188 |        |        |        |        |        |        | Οι       | tput Comp | are 2 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC2CON       | 018A | _      | _      | OCSIDL | _      | _      | _      | _        | _         | _           | _        | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC3RS        | 018C |        |        |        |        |        |        | Output 0 | Compare 3 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC3R         | 018E |        |        |        |        |        |        | Οι       | tput Comp | are 3 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC3CON       | 0190 | _      | _      | OCSIDL | _      | _      | _      | _        | _         | _           | _        | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC4RS        | 0192 |        |        |        |        |        |        | Output 0 | Compare 4 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC4R         | 0194 |        |        |        |        |        |        | Οι       | tput Comp | are 4 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC4CON       | 0196 | _      | _      | OCSIDL | _      | _      | _      | _        | _         | _           | _        | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC5RS        | 0198 |        |        |        |        |        |        | Output ( | Compare 5 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC5R         | 019A |        |        |        |        |        |        | Οι       | tput Comp | are 5 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC5CON       | 019C | _      | _      | OCSIDL | _      | _      | —      | —        | —         | _           | —        | —     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-9: I<sup>2</sup>C<sup>™</sup> REGISTER MAP

|              | -    |         |        |         |        |        |        |        |                                |       |       |            |             |              |       |       |       |               |

|--------------|------|---------|--------|---------|--------|--------|--------|--------|--------------------------------|-------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                          | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| I2C1RCV      | 0200 | _       |        | —       | _      | _      | _      | —      | – – I2C1 Receive Register      |       |       |            |             |              | 0000  |       |       |               |

| I2C1TRN      | 0202 | _       | _      | _       | _      | _      | _      | _      | – – I2C1 Transmit Register     |       |       |            |             |              | OOFF  |       |       |               |

| I2C1BRG      | 0204 | _       | _      | _       | _      | _      | _      | _      | Baud Rate Generator Register 1 |       |       |            |             |              | 0000  |       |       |               |

| I2C1CON      | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                           | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                          | IWCOL | I2COV | D/A        | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A | _       | _      | _       | _      | _      | _      |        |                                |       |       | I2C1 Addre | ss Register |              |       |       |       | 0000          |

| I2C1MSK      | 020C | _       | _      | _       | _      | _      | _      | AMSK9  | AMSK8                          | AMSK7 | AMSK6 | AMSK5      | AMSK4       | AMSK3        | AMSK2 | AMSK1 | AMSK0 | 0000          |

| I2C2RCV      | 0210 | _       | —      | _       | _      | _      | _      | _      | _                              |       |       |            | I2C2 Receiv | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212 | _       | —      | _       | _      | _      | _      | _      | _                              |       |       |            | I2C2 Transr | nit Register | r     |       |       | OOFF          |

| I2C2BRG      | 0214 | _       | —      | _       | _      | _      | _      | _      |                                |       |       | Baud Rate  | Generator   | Register 2   |       |       |       | 0000          |

| I2C2CON      | 0216 | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                           | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                          | IWCOL | I2COV | D/A        | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A | _       |        | _       | _      | _      | _      |        | •                              |       | •     | I2C2 Addre | ss Register |              | •     | •     | •     | 0000          |

| I2C2MSK      | 021C | _       |        | _       | _      | _      | _      | AMSK9  | AMSK8                          | AMSK7 | AMSK6 | AMSK5      | AMSK4       | AMSK3        | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0      | ) R/W-0                                   | U-0                                 | U-0            | U-0                   | U-0               | R/W-0            | R/W-0          |

|------------|-------------------------------------------|-------------------------------------|----------------|-----------------------|-------------------|------------------|----------------|

| TRAP       | R IOPUWR                                  | _                                   |                | _                     | _                 | CM               | PMSLP          |

| bit 15     |                                           |                                     |                | 1                     |                   |                  | bit 8          |

| R/W-0      | ) R/W-0                                   | R/W-0                               | R/W-0          | R/W-0                 | R/W-0             | R/W-1            | R/W-1          |

| EXTR       |                                           | SWDTEN <sup>(2)</sup>               | WDTO           | SLEEP                 | IDLE              | BOR              | POR            |

| bit 7      | SVIR                                      | SWDTEN,                             | WDTO           | SLEEP                 | IDLE              | BUR              | bit 0          |

|            |                                           |                                     |                |                       |                   |                  |                |

| Legend:    |                                           |                                     |                |                       |                   |                  |                |

| R = Reada  | able bit                                  | W = Writable I                      | oit            | U = Unimple           | mented bit, read  | l as '0'         |                |

| -n = Value | at POR                                    | '1' = Bit is set                    |                | '0' = Bit is cle      | eared             | x = Bit is unk   | nown           |

| bit 15     | TRAPR. Trar                               | Reset Flag bit                      |                |                       |                   |                  |                |

|            | -                                         | onflict Reset ha                    |                |                       |                   |                  |                |

|            |                                           | onflict Reset ha                    |                | d                     |                   |                  |                |

| bit 14     | IOPUWR: Ille                              | egal Opcode or                      | Uninitialized  | W Access Res          | et Flag bit       |                  |                |

|            |                                           |                                     |                |                       | ode or Uninitial  | ized W registe   | er used as an  |

|            |                                           | Pointer caused                      |                | -                     |                   | · ·              |                |

|            | 0 = An illega                             | I opcode or Uni                     | nitialized W r | egister Reset h       | nas not occurred  | ł                |                |

| bit 13-10  | Unimplemen                                | ted: Read as '                      | )'             |                       |                   |                  |                |

| bit 9      | CM: Configur                              | ration Word Mis                     | match Reset    | Flag bit              |                   |                  |                |

|            |                                           | uration Word Mi<br>uration Word Mi  |                |                       |                   |                  |                |

| bit 8      |                                           | gram Memory P                       |                |                       |                   |                  |                |

|            |                                           | memory bias v                       |                |                       | ring Sleep        |                  |                |

|            |                                           |                                     |                |                       | ng Sleep and vol  | tage regulator   | enters Standby |

| bit 7      | EXTR: Extern                              | nal Reset (MCL                      | R) Pin bit     |                       |                   |                  |                |

|            |                                           | Clear (pin) Res                     |                | red                   |                   |                  |                |

|            |                                           | Clear (pin) Res                     |                |                       |                   |                  |                |

| bit 6      | SWR: Softwa                               | are Reset (Instru                   | iction) Flag b | it                    |                   |                  |                |

|            | 1 <b>= A</b> reset                        | instruction has                     | been execute   | ed                    |                   |                  |                |

|            |                                           | instruction has                     |                |                       |                   |                  |                |

| bit 5      | SWDTEN: So                                | oftware Enable/                     | Disable of W   | DT bit <sup>(2)</sup> |                   |                  |                |

|            | 1 = WDT is e                              |                                     |                |                       |                   |                  |                |

|            | 0 = WDT is d                              |                                     |                |                       |                   |                  |                |

| bit 4      |                                           | hdog Timer Tim                      | -              | t                     |                   |                  |                |

|            |                                           | e-out has occur                     |                |                       |                   |                  |                |

|            |                                           | e-out has not or                    |                |                       |                   |                  |                |

| bit 3      |                                           | e from Sleep Fl                     | -              |                       |                   |                  |                |

|            |                                           | as been in Slee<br>as not been in S |                |                       |                   |                  |                |

| Note 1:    | All of the Reset sta<br>cause a device Re | •                                   | set or cleare  | d in software.        | Setting one of th | ese bits in soft | ware does not  |

| 2:         | If the FWDTEN Co                          | onfiguration bit i                  | s '1' (unprogi | rammed), the V        | NDT is always e   | enabled, regard  | lless of the   |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

SWDTEN bit setting.

# REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0    | U-0    | U-0    | U-0    | U-0 | U-0     | U-0     | U-0     |

|--------|--------|--------|--------|-----|---------|---------|---------|

| —      | —      | —      | —      | —   | —       | —       | —       |

| bit 15 |        |        |        |     |         |         | bit 8   |

|        |        |        |        |     |         |         |         |

| U-0    | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _      | AD1IP2 | AD1IP1 | AD1IP0 | —   | U1TXIP2 | U1TXIP1 | U1TXIP0 |

| bit 7  |        |        |        |     |         |         | bit 0   |

| Legend:      |           |                                                   |                             |                    |

|--------------|-----------|---------------------------------------------------|-----------------------------|--------------------|

| R = Readal   | ble bit   | W = Writable bit                                  | U = Unimplemented bit,      | read as '0'        |

| -n = Value a | at POR    | '1' = Bit is set                                  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-7     | Unimple   | mented: Read as '0'                               |                             |                    |

| bit 6-4      | AD1IP<2   | :0>: A/D Conversion Comple                        | ete Interrupt Priority bits |                    |

|              |           | errupt is Priority 7 (highest p                   | · ·                         |                    |

|              | •         | . , , , , , , , , , , , , , , , , , , ,           | · · ·                       |                    |

|              | •         |                                                   |                             |                    |

|              | •         |                                                   |                             |                    |

|              |           | errupt is Priority 1<br>errupt source is disabled |                             |                    |

| bit 3        |           | mented: Read as '0'                               |                             |                    |

| bit 2-0      | U1TXIP<   | 2:0>: UART1 Transmitter Int                       | errupt Priority bits        |                    |

|              | 111 = Int | errupt is Priority 7 (highest p                   | riority interrupt)          |                    |

|              | •         |                                                   | -                           |                    |

|              | •         |                                                   |                             |                    |

|              | •         |                                                   |                             |                    |

|              |           | errupt is Priority 1<br>errupt source is disabled |                             |                    |

|                    | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0                                | R/W-1            | R/W-0           | R/W-0  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-----------------|--------|

|                    | T4IP2                                                                                                                                                                | T4IP1                                                                                                                                                                    | T4IP0                                                                                                  | _                                  | OC4IP2           | OC4IP1          | OC4IP0 |

| bit 15             |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 | bit 8  |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| U-0                | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0                                | U-0              | U-0             | U-0    |

| <br>bit 7          | OC3IP2                                                                                                                                                               | OC3IP1                                                                                                                                                                   | OC3IP0                                                                                                 | _                                  | _                | _               | bit (  |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 | Ditt   |

| Legend:            |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| R = Readab         | ole bit                                                                                                                                                              | W = Writable                                                                                                                                                             | bit                                                                                                    | U = Unimplen                       | nented bit, read | d as '0'        |        |

| -n = Value a       | at POR                                                                                                                                                               | '1' = Bit is set                                                                                                                                                         |                                                                                                        | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown   |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| bit 15             | Unimplemen                                                                                                                                                           | ted: Read as '                                                                                                                                                           | 0'                                                                                                     |                                    |                  |                 |        |

| bit 14-12          | <b>T4IP&lt;2:0&gt;:</b> ⊺i                                                                                                                                           | imer4 Interrupt                                                                                                                                                          | Priority bits                                                                                          |                                    |                  |                 |        |

|                    | 111 = Interrup                                                                                                                                                       | pt is Priority 7 (                                                                                                                                                       | highest priority                                                                                       | / interrupt)                       |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •<br>001 = Interrup                                                                                                                                                  | pt is Priority 1                                                                                                                                                         |                                                                                                        |                                    |                  |                 |        |

|                    |                                                                                                                                                                      | pt is Priority 1<br>pt source is dis                                                                                                                                     | abled                                                                                                  |                                    |                  |                 |        |

| bit 11             | 000 = Interru                                                                                                                                                        |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| bit 11<br>bit 10-8 | 000 = Interrup<br>Unimplemen                                                                                                                                         | pt source is dis<br>ted: Read as '                                                                                                                                       | 0'                                                                                                     | Interrupt Priorit                  | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '                                                                                                                                       | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | y bits           |                 |        |

|                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4<br>highest priority                                                     | • •                                | / bits           |                 |        |

|                    | 000 = Interrup<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                        | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                             | <sub>0</sub> '<br>are Channel 4<br>highest priority<br>abled                                           | • •                                | / bits           |                 |        |

| bit 10-8           | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'                                      | • •                                |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:<br>111 = Interrup<br>001 = Interrup | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'<br>are Channel 3<br>highest priority | y interrupt)<br>Interrupt Priority |                  |                 |        |

### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

REGISTER 7-25: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0           | U-0           | U-0                | U-0              | U-0                | U-0              | U-0             | U-0   |

|---------------|---------------|--------------------|------------------|--------------------|------------------|-----------------|-------|

| _             | —             |                    |                  | —                  | —                | —               | _     |

| bit 15        |               |                    |                  |                    |                  |                 | bit 8 |

|               |               |                    |                  |                    |                  |                 |       |

| U-0           | R/W-1         | R/W-0              | R/W-0            | U-0                | U-0              | U-0             | U-0   |

| _             | OC5IP2        | OC5IP1             | OC5IP0           | —                  | —                | —               | —     |

| bit 7         |               |                    |                  | ·                  |                  |                 | bit 0 |

|               |               |                    |                  |                    |                  |                 |       |

| Legend:       |               |                    |                  |                    |                  |                 |       |

| R = Readable  | e bit         | W = Writable       | bit              | U = Unimplen       | nented bit, read | l as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea  | ared             | x = Bit is unkr | iown  |

|               |               |                    |                  |                    |                  |                 |       |

| bit 15-7      | Unimplemen    | ted: Read as '     | 0'               |                    |                  |                 |       |

| bit 6-4       | OC5IP<2:0>:   | Output Compa       | are Channel 5 I  | Interrupt Priority | y bits           |                 |       |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | / interrupt)       |                  |                 |       |

|               | •             |                    |                  |                    |                  |                 |       |

|               | •             |                    |                  |                    |                  |                 |       |

|               | •             |                    |                  |                    |                  |                 |       |

|               | 001 = Interru |                    |                  |                    |                  |                 |       |

|               | 000 = Interru | pt source is dis   | abled            |                    |                  |                 |       |

|               |               |                    |                  |                    |                  |                 |       |

bit 3-0 Unimplemented: Read as '0'

### REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

| U-0          | U-0           | U-0                | U-0              | U-0                  | U-0              | U-0             | U-0   |

|--------------|---------------|--------------------|------------------|----------------------|------------------|-----------------|-------|

| _            | —             | —                  | —                | —                    | —                | —               | —     |

| bit 15       |               |                    |                  |                      |                  |                 | bit 8 |

|              |               |                    |                  |                      |                  |                 |       |

| U-0          | R/W-1         | R/W-0              | R/W-0            | U-0                  | U-0              | U-0             | U-0   |

| _            | PMPIP2        | PMPIP1             | PMPIP0           | —                    | —                | —               |       |

| bit 7        |               |                    |                  |                      |                  |                 | bit 0 |

|              |               |                    |                  |                      |                  |                 |       |

| Legend:      |               |                    |                  |                      |                  |                 |       |

| R = Readab   | le bit        | W = Writable       | bit              | U = Unimplem         | nented bit, read | l as '0'        |       |

| -n = Value a | t POR         | '1' = Bit is set   |                  | '0' = Bit is cleared |                  | x = Bit is unkr | nown  |

|              |               |                    |                  |                      |                  |                 |       |

| bit 15-7     | Unimplemen    | ted: Read as '0    | )'               |                      |                  |                 |       |

| bit 6-4      | PMPIP<2:0>    | : Parallel Maste   | r Port Interrupt | t Priority bits      |                  |                 |       |

|              | 111 = Interru | pt is Priority 7 ( | highest priority | interrupt)           |                  |                 |       |

|              | •             |                    |                  |                      |                  |                 |       |

|              | •             |                    |                  |                      |                  |                 |       |

|              | •             |                    |                  |                      |                  |                 |       |

|              | 001 = Interru | pt is Priority 1   |                  |                      |                  |                 |       |

|              | 000 = Interru | pt source is dis   | abled            |                      |                  |                 |       |

| bit 3-0      | Unimplemen    | ted: Read as '     | )'               |                      |                  |                 |       |

|              |               |                    |                  |                      |                  |                 |       |

| U-0          | U-0                      | U-0                 | U-0                       | U-0                 | U-0                 | U-0                 | U-0                 |

|--------------|--------------------------|---------------------|---------------------------|---------------------|---------------------|---------------------|---------------------|

|              |                          | _                   |                           |                     | _                   | _                   | _                   |

| oit 15       |                          |                     |                           |                     |                     |                     | bit 8               |

|              |                          |                     |                           |                     |                     |                     |                     |

| U-0          | U-0                      | R/W-0               | R/W-0                     | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

| _            | _                        | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| oit 7        |                          |                     | •                         |                     | •                   | •                   | bit C               |

|              |                          |                     |                           |                     |                     |                     |                     |

| _egend:      |                          |                     |                           |                     |                     |                     |                     |

| R = Readabl  | e bit                    | W = Writable        | bit                       | U = Unimplem        | nented bit, read    | l as '0'            |                     |

| n = Value at | POR                      | '1' = Bit is set    |                           | '0' = Bit is clea   | ared                | x = Bit is unkn     | iown                |

|              |                          |                     |                           |                     |                     |                     |                     |

| oit 15-6     | Unimplemen               | ted: Read as '      | 0'                        |                     |                     |                     |                     |

| oit 5-0      | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator T     | uning bits <sup>(1)</sup> |                     |                     |                     |                     |

|              | 011111 <b>= Ma</b>       | ximum frequer       | ncy deviation             |                     |                     |                     |                     |

|              | 011110 =                 |                     |                           |                     |                     |                     |                     |

|              | •                        |                     |                           |                     |                     |                     |                     |

|              | •                        |                     |                           |                     |                     |                     |                     |

|              | 000001 =                 |                     |                           |                     |                     |                     |                     |

|              | 000000 = Ce              | nter frequency,     | oscillator is ru          | inning at factory   | / calibrated free   | quency              |                     |

|              | 111111 =                 |                     |                           |                     |                     |                     |                     |

|              | •                        |                     |                           |                     |                     |                     |                     |

|              | •                        |                     |                           |                     |                     |                     |                     |

|              | •                        |                     |                           |                     |                     |                     |                     |

|              | •<br>100001 =            |                     |                           |                     |                     |                     |                     |

### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

# 8.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in Flash Configuration Word 2 must be programmed to '0'. (Refer to **Section 24.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

# 8.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or SOSC (if SOSCEN remains set).

- Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

A recommended code sequence for a clock switch includes the following:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- 2. Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8> in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0> in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 8-1.

### EXAMPLE 8-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| .globalreset                              |

|-------------------------------------------|

| .include "p24fxxxx.inc"                   |

| .text                                     |

| reset:                                    |

| ;Place the new oscillator selection in WO |

| ;OSCCONH (high byte) Unlock Sequence      |

| DISI #18                                  |

| PUSH w1                                   |

| PUSH w2                                   |

| PUSH w3                                   |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

| POP w3                                    |

| POP w2                                    |

| POP w1                                    |

| .end                                      |

|                                           |

NOTES:

### REGISTER 18-6: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| <br>bit 7 | —   | —   | —   | —   | —   | RTSECSEL <sup>(1)</sup> | PMPTTL<br>bit 0 |

|-----------|-----|-----|-----|-----|-----|-------------------------|-----------------|

| U-0       | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                   | R/W-0           |

| bit 15    |     |     |     |     |     |                         | bit 8           |

| _         | —   | —   | —   | —   | —   | —                       |                 |

| U-0       | U-0 | U-0 | U-0 | U-0 | U-0 | U-0                     | U-0             |

bit 15-2 Unimplemented: Read as '0'

- bit 1RTSECSEL: RTCC Seconds Clock Output Select bit(1)1 = RTCC seconds clock is selected for the RTCC pin0 = RTCC alarm pulse is selected for the RTCC pinbit 0PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffers

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL) bit needs to be set.

NOTES:

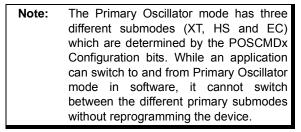

# 22.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, **"Output Compare"** (DS39706).

## FIGURE 22-1: COMPARATOR I/O OPERATING MODES

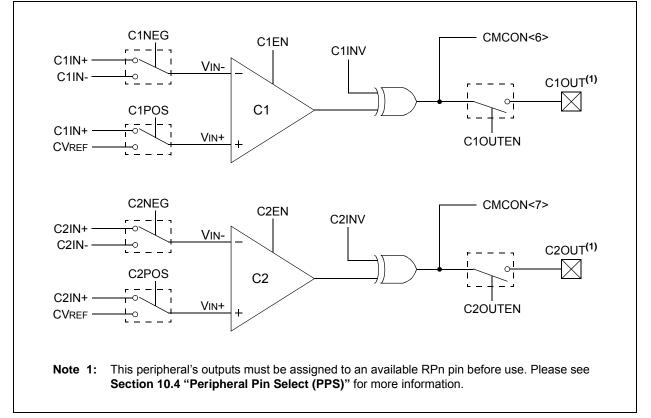

# 23.0 COMPARATOR VOLTAGE REFERENCE

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to     |

|       | the "PIC24F Family Reference Manual",      |

|       | "Comparator Voltage Reference              |

|       | Module" (DS39709).                         |

## 23.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides two ranges of

output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

# FIGURE 23-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# REGISTER 24-2: CW2: FLASH CONFIGURATION WORD 2

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1 | R/PO-1     | R/PO-1                 | R/PO-1      | R/PO-1                  | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|------------|------------------------|-------------|-------------------------|--------|--------|--------|

| IESO   | WUTSEL1(1) | WUTSEL0 <sup>(1)</sup> | SOSCSEL1(1) | SOSCSEL0 <sup>(1)</sup> | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 15 |            |                        |             |                         |        |        | bit 8  |

| R/PO-1 | R/PO-1 | R/PO-1   | R/PO-1  | r | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|--------|----------|---------|---|---------|---------|---------|

| FCKSM1 | FCKSM0 | OSCIOFCN | IOL1WAY | r | I2C1SEL | POSCMD1 | POSCMD0 |