# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

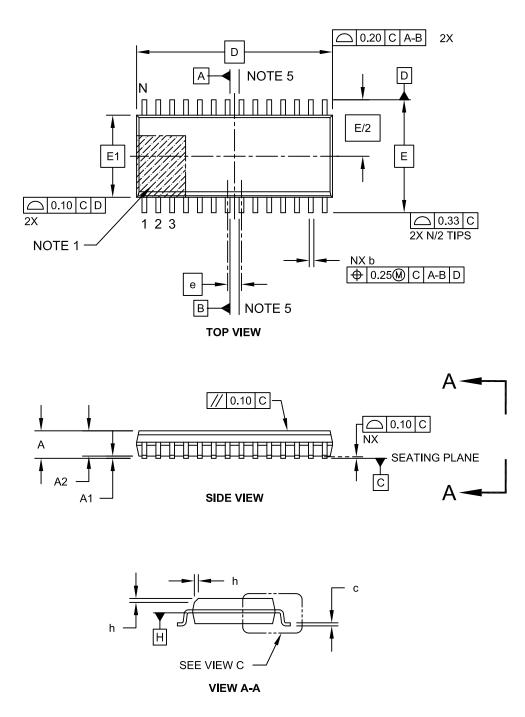

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga002-e-ss |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ABLE 1-1. DEVICE FEATURES FOR THE FIC24FJ04GA004 FAMILT |         |           |             |                                    |           |                                                                                                                                                              |            |         |

|---------------------------------------------------------|---------|-----------|-------------|------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|

| Features                                                | 16GA002 | 32GA002   | 48GA002     | 64GA002                            | 16GA004   | 32GA004                                                                                                                                                      | 48GA004    | 64GA004 |

| Operating Frequency                                     |         | •         | •           | DC – 3                             | 2 MHz     | 32K       48K       64         11,008       16,512       22,0         8192       8192         Ports A, B, C       35         30       30         13       26 |            |         |

| Program Memory (bytes)                                  | 16K     | 32K       | 48K         | 64K                                | 16K       | 32K                                                                                                                                                          | 48K        | 64K     |

| Program Memory (instructions)                           | 5,504   | 11,008    | 16,512      | 22,016                             | 5,504     | 11,008                                                                                                                                                       | 16,512     | 22,016  |

| Data Memory (bytes)                                     | 4096    |           | 8192        |                                    | 4096      |                                                                                                                                                              |            |         |

| Interrupt Sources<br>(soft vectors/NMI traps)           |         |           |             | 4<br>(39                           |           | •                                                                                                                                                            |            |         |

| I/O Ports                                               |         | Ports     | ; А, В      |                                    |           | Ports /                                                                                                                                                      | A, B, C    |         |

| Total I/O Pins                                          |         | 2         | 1           |                                    |           | 3                                                                                                                                                            | 5          |         |

| Timers:                                                 |         |           |             |                                    |           |                                                                                                                                                              |            |         |

| Total Number (16-bit)                                   |         |           |             | 5(                                 | 1)        |                                                                                                                                                              |            |         |

| 32-Bit (from paired 16-bit timers)                      |         |           |             | 2                                  |           |                                                                                                                                                              |            |         |

| Input Capture Channels                                  |         |           |             | 5(                                 | 1)        |                                                                                                                                                              |            |         |

| Output Compare/PWM Channels                             |         |           |             | 5(                                 | 1)        |                                                                                                                                                              |            |         |

| Input Change Notification Interrupt                     |         | 2         | 1           |                                    |           | 3                                                                                                                                                            | 0          |         |

| Serial Communications:                                  |         |           |             |                                    |           |                                                                                                                                                              |            |         |

| UART                                                    |         |           |             | 2(                                 | 1)        |                                                                                                                                                              |            |         |

| SPI (3-wire/4-wire)                                     |         |           |             | 2(                                 | 1)        |                                                                                                                                                              |            |         |

| I <sup>2</sup> C™                                       |         |           |             | 2                                  | 2         |                                                                                                                                                              |            |         |

| Parallel Communications (PMP/PSP)                       |         |           |             | Ye                                 | es        |                                                                                                                                                              |            |         |

| JTAG Boundary Scan                                      |         |           |             | Ye                                 | es        |                                                                                                                                                              |            |         |

| 10-Bit Analog-to-Digital Module<br>(input channels)     |         | 10        |             |                                    |           | 1                                                                                                                                                            | 3          |         |

| Analog Comparators                                      |         |           |             | 2                                  | 2         |                                                                                                                                                              |            |         |

| Remappable Pins                                         |         | 1         | 6           |                                    |           | 2                                                                                                                                                            | 6          |         |

| Resets (and delays)                                     |         |           | iction, Hai | nstruction<br>dware Tra<br>WRT, OS | ps, Confi | guration V                                                                                                                                                   |            |         |

| Instruction Set                                         |         | 76 Base I | nstruction  | s, Multiple                        | Address   | ing Mode                                                                                                                                                     | Variations |         |

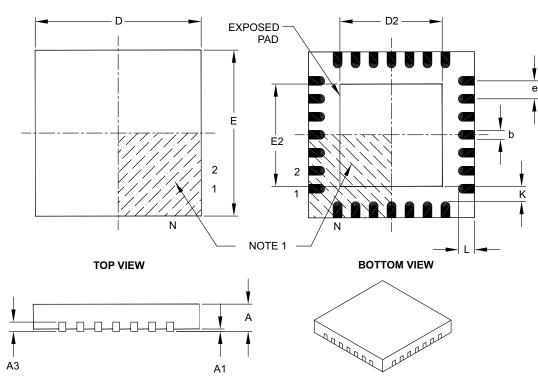

| Packages                                                | 28-Pin  | SPDIP/S   | SOP/SOI     | C/QFN                              |           | 44-Pin Q                                                                                                                                                     | FN/TQFP    |         |

### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ64GA004 FAMILY

**Note 1:** Peripherals are accessible through remappable pins.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC24FJ64GA004 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG/DISVREG and VCAP/VDDCORE pins (PIC24F J devices only) (see Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

Note: The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},\,6.3\text{V}$  or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)" for an explanation of the ENVREG/DISVREG pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

|              | <del>-</del> J. |        |         |         |         |        |         |         |         |       |         |         |         |         |         |         |               |               |

|--------------|-----------------|--------|---------|---------|---------|--------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|---------------|---------------|

| File<br>Name | Addr            | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

| INTCON1      | 0080            | NSTDIS | _       | -       |         | _      | _       |         | _       | _     | _       | _       | MATHERR | ADDRERR | STKERR  | OSCFAIL | _             | 0000          |

| INTCON2      | 0082            | ALTIVT | DISI    | _       | _       | _      | _       | _       | _       | _     | —       | _       | —       | _       | INT2EP  | INT1EP  | INT0EP        | 0000          |

| IFS0         | 0084            | —      | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF  | SPF1IF  | T3IF    | T2IF  | OC2IF   | IC2IF   | _       | T1IF    | OC1IF   | IC1IF   | INTOIF        | 0000          |

| IFS1         | 0086            | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | OC4IF   | OC3IF   | _       | _     | _       | _       | INT1IF  | CNIF    | CMIF    | MI2C1IF | SI2C1IF       | 0000          |

| IFS2         | 0088            | —      | _       | PMPIF   |         | —      | _       | OC5IF   | _       | IC5IF | IC4IF   | IC3IF   | —       | _       |         | SPI2IF  | SPF2IF        | 0000          |

| IFS3         | 008A            | —      | RTCIF   | —       |         | —      | _       |         | _       | —     | —       |         | —       | _       | MI2C2IF | SI2C2IF | _             | 0000          |

| IFS4         | 008C            | —      | _       | —       |         | —      | _       |         | LVDIF   | —     | —       |         | —       | CRCIF   | U2ERIF  | U1ERIF  | _             | 0000          |

| IEC0         | 0094            | _      | _       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE  | SPF1IE  | T3IE    | T2IE  | OC2IE   | IC2IE   | —       | T1IE    | OC1IE   | IC1IE   | <b>INTOIE</b> | 0000          |

| IEC1         | 0096            | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | OC4IE   | OC3IE   | —       | —     | _       |         | INT1IE  | CNIE    | CMIE    | MI2C1IE | SI2C1IE       | 0000          |

| IEC2         | 0098            | —      | —       | PMPIE   | _       | —      | —       | OC5IE   | —       | IC5IE | IC4IE   | IC3IE   | —       | —       | —       | SPI2IE  | SPF2IE        | 0000          |

| IEC3         | 009A            | —      | RTCIE   | —       | _       | —      | —       | _       | —       | —     | —       | —       | —       | —       | MI2C2IE | SI2C2IE | —             | 0000          |

| IEC4         | 009C            | —      | —       | —       | _       | —      | —       | _       | LVDIE   | —     | —       | —       | —       | CRCIE   | U2ERIE  | U1ERIE  | —             | 0000          |

| IPC0         | 00A4            | —      | T1IP2   | T1IP1   | T1IP0   | —      | OC1IP2  | OC1IP1  | OC1IP0  | —     | IC1IP2  | IC1IP1  | IC1IP0  | —       | INT0IP2 | INT0IP1 | INT0IP0       | 4444          |

| IPC1         | 00A6            | —      | T2IP2   | T2IP1   | T2IP0   | —      | OC2IP2  | OC2IP1  | OC2IP0  | _     | IC2IP2  | IC2IP1  | IC2IP0  | _       | _       | —       | _             | 4444          |

| IPC2         | 00A8            | —      | U1RXIP2 | U1RXIP1 | U1RXIP0 | —      | SPI1IP2 | SPI1IP1 | SPI1IP0 | _     | SPF1IP2 | SPF1IP1 | SPF1IP0 | —       | T3IP2   | T3IP1   | T3IP0         | 4444          |

| IPC3         | 00AA            | —      | —       | —       | _       | —      | —       | _       | —       | _     | AD1IP2  | AD1IP1  | AD1IP0  | _       | U1TXIP2 | U1TXIP1 | U1TXIP0       | 4444          |

| IPC4         | 00AC            | —      | CNIP2   | CNIP1   | CNIP0   | —      | CMIP2   | CMIP1   | CMIP0   | _     | MI2C1P2 | MI2C1P1 | MI2C1P0 | _       | SI2C1P2 | SI2C1P1 | SI2C1P0       | 4444          |

| IPC5         | 00AE            | —      | —       | —       | _       | —      | —       | _       | _       | _     | _       | _       | _       | _       | INT1IP2 | INT1IP1 | INT1IP0       | 4444          |

| IPC6         | 00B0            | —      | T4IP2   | T4IP1   | T4IP0   | —      | OC4IP2  | OC4IP1  | OC4IP0  | —     | OC3IP2  | OC3IP1  | OC3IP0  | —       | —       | —       | —             | 4444          |

| IPC7         | 00B2            | —      | U2TXIP2 | U2TXIP1 | U2TXIP0 | —      | U2RXIP2 | U2RXIP1 | U2RXIP0 | —     | INT2IP2 | INT2IP1 | INT2IP0 | —       | T5IP2   | T5IP1   | T5IP0         | 4444          |

| IPC8         | 00B4            | —      | —       | —       | -       | —      | —       | -       | —       | _     | SPI2IP2 | SPI2IP1 | SPI2IP0 | _       | SPF2IP2 | SPF2IP1 | SPF2IP0       | 4444          |

| IPC9         | 00B6            | —      | IC5IP2  | IC5IP1  | IC5IP0  | —      | IC4IP2  | IC4IP1  | IC4IP0  | _     | IC3IP2  | IC3IP1  | IC3IP0  | _       | _       | —       | _             | 4444          |

| IPC10        | 00B8            | —      | _       | —       | _       | —      | —       | _       | —       | _     | OC5IP2  | OC5IP1  | OC5IP0  | _       | _       | —       | _             | 4444          |

| IPC11        | 00BA            | —      | _       | —       | _       | —      | —       | _       | —       | _     | PMPIP2  | PMPIP1  | PMPIP0  | _       | _       | —       | _             | 4444          |

| IPC12        | 00BC            | —      | —       | —       | —       | —      | MI2C2P2 | MI2C2P1 | MI2C2P0 | —     | SI2C2P2 | SI2C2P1 | SI2C2P0 | —       | —       | —       | —             | 4444          |

| IPC15        | 00C2            | —      | —       | —       | —       | —      | RTCIP2  | RTCIP1  | RTCIP0  | —     | —       | —       | —       |         | _       | —       | —             | 4444          |

| IPC16        | 00C4            | —      | CRCIP2  | CRCIP1  | CRCIP0  | —      | U2ERIP2 | U2ERIP1 | U2ERIP0 | —     | U1ERIP2 | U1ERIP1 | U1ERIP0 | —       | —       | —       | _             | 4444          |

| IPC18        | 00C8            | —      | —       | —       | —       | —      | —       | —       | —       | —     | —       | —       | —       | —       | LVDIP2  | LVDIP1  | LVDIP0        | 4444          |

| INTTREG      | 00E0            | CPUIRQ | —       | VHOLD   | —       | ILR3   | ILR2    | ILR1    | ILR0    | _     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0       | 0000          |

DS39881E-page 34

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

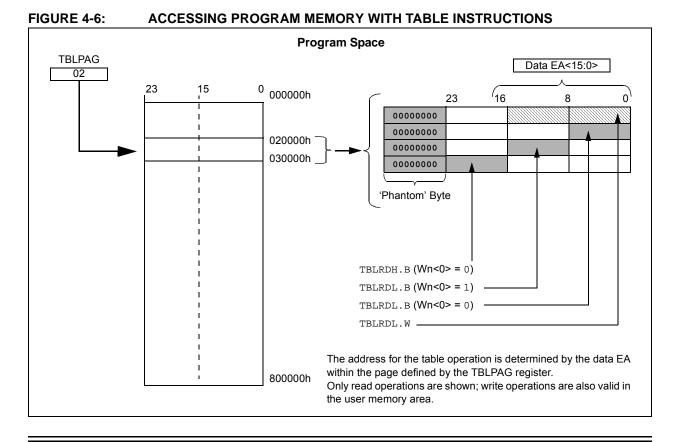

### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only table read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

### 7.3 Interrupt Control and Status Registers

The PIC24FJ64GA004 family of devices implements a total of 29 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC12, IPC15, IPC16 and IPC18

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU priority level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-31, in the following pages.

### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0          | U-0   | U-0          | U-0 | U-0                                | U-0     | U-0     | U-0     |

|--------------|-------|--------------|-----|------------------------------------|---------|---------|---------|

| _            | —     | —            | —   |                                    | —       | —       | —       |

| bit 15       | •     |              |     |                                    |         |         | bit 8   |

|              |       |              |     |                                    |         |         |         |

| U-0          | U-0   | U-0          | U-0 | U-0                                | R/W-1   | R/W-0   | R/W-0   |

|              | —     | —            | —   |                                    | INT1IP2 | INT1IP1 | INT1IP0 |

| bit 7        | ·     |              | •   |                                    |         | •       | bit 0   |

|              |       |              |     |                                    |         |         |         |

| Legend:      |       |              |     |                                    |         |         |         |

| R = Readable | e bit | W = Writable | bit | U = Unimplemented bit, read as '0' |         |         |         |

| -n | = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|----|----------------|------------------|----------------------|--------------------|

### bit 15-3 Unimplemented: Read as '0'

INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

bit 2-0

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

|                                                                      | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0               | R/W-1            | R/W-0           | R/W-0  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|

|                                                                      | T4IP2                                                                                                                                                                | T4IP1                                                                                                                                                                    | T4IP0                                                                                                  | —                 | OC4IP2           | OC4IP1          | OC4IP0 |

| bit 15                                                               |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                   |                  |                 | bit 8  |

|                                                                      |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| U-0                                                                  | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0               | U-0              | U-0             | U-0    |

| <br>bit 7                                                            | OC3IP2                                                                                                                                                               | OC3IP1                                                                                                                                                                   | OC3IP0                                                                                                 | —                 | _                | _               | bit (  |

|                                                                      |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                   |                  |                 | Ditt   |

| Legend:                                                              |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| R = Readable bit W = Writable bit                                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                   |                  | x = Bit is unkr | nown   |

|                                                                      |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| bit 15                                                               | Unimplemen                                                                                                                                                           | ted: Read as '                                                                                                                                                           | 0'                                                                                                     |                   |                  |                 |        |

| bit 14-12                                                            | <b>T4IP&lt;2:0&gt;:</b> ⊺i                                                                                                                                           | imer4 Interrupt                                                                                                                                                          | Priority bits                                                                                          |                   |                  |                 |        |

|                                                                      | 111 = Interrup                                                                                                                                                       | pt is Priority 7 (                                                                                                                                                       | highest priority                                                                                       | / interrupt)      |                  |                 |        |

|                                                                      | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

|                                                                      | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

|                                                                      | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

|                                                                      | •<br>001 = Interrup                                                                                                                                                  | pt is Priority 1                                                                                                                                                         |                                                                                                        |                   |                  |                 |        |

|                                                                      |                                                                                                                                                                      | pt is Priority 1<br>pt source is dis                                                                                                                                     | abled                                                                                                  |                   |                  |                 |        |

| bit 11                                                               | 000 = Interru                                                                                                                                                        |                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| bit 11<br>bit 10-8                                                   | 000 = Interrup<br>Unimplemen                                                                                                                                         | pt source is dis<br>ted: Read as '                                                                                                                                       | 0'                                                                                                     | Interrupt Priorit | / bits           |                 |        |

|                                                                      | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '                                                                                                                                       | <sup>0'</sup><br>are Channel 4                                                                         | • •               | / bits           |                 |        |

|                                                                      | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •               | / bits           |                 |        |

|                                                                      | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •               | / bits           |                 |        |

|                                                                      | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4                                                                         | • •               | y bits           |                 |        |

|                                                                      | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4<br>highest priority                                                     | • •               | / bits           |                 |        |

|                                                                      | 000 = Interrup<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                        | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                             | <sub>0</sub> '<br>are Channel 4<br>highest priority<br>abled                                           | • •               | / bits           |                 |        |

| bit 10-8                                                             | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'                                      | • •               |                  |                 |        |

| bit 10-8<br>bit 7                                                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)      |                  |                 |        |

| bit 10-8<br>bit 7                                                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)      |                  |                 |        |

| bit 10-8<br>bit 7                                                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)      |                  |                 |        |

| bit 10-8<br>bit 7                                                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)      |                  |                 |        |

| bit 10-8<br>bit 7                                                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:<br>111 = Interrup<br>001 = Interrup | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'<br>are Channel 3<br>highest priority | y interrupt)      |                  |                 |        |

### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0                   | R/W-1                                                                                                                                  | R/W-0                                   | R/W-0            | U-0                 | R/W-1                                                                          | R/W-0           | R/W-0  |  |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|---------------------|--------------------------------------------------------------------------------|-----------------|--------|--|--|--|--|--|--|

| _                     | IC5IP2                                                                                                                                 | IC5IP1                                  | IC5IP0           |                     | IC4IP2                                                                         | IC4IP1          | IC4IP0 |  |  |  |  |  |  |

| bit 15                |                                                                                                                                        |                                         |                  |                     |                                                                                |                 | bit    |  |  |  |  |  |  |

| U-0                   | R/W-1                                                                                                                                  | R/W-0                                   | R/W-0            | U-0                 | U-0                                                                            | U-0             | U-0    |  |  |  |  |  |  |

|                       | IC3IP2                                                                                                                                 | IC3IP1                                  | IC3IP0           | _                   | _                                                                              | _               | _      |  |  |  |  |  |  |

| bit 7                 |                                                                                                                                        |                                         |                  |                     |                                                                                |                 | bit    |  |  |  |  |  |  |

| Lonondi               |                                                                                                                                        |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

| Legend:<br>R = Readat | ala hit                                                                                                                                | W = Writable                            | h:t              |                     | aantad hit raa                                                                 | 1 00'           |        |  |  |  |  |  |  |

| -n = Value a          |                                                                                                                                        | '1' = Bit is set                        |                  | '0' = Bit is clea   | nented bit, read                                                               | x = Bit is unkr | 0000   |  |  |  |  |  |  |

|                       |                                                                                                                                        |                                         |                  |                     | areu                                                                           |                 | IOWII  |  |  |  |  |  |  |

| bit 15                | Unimpleme                                                                                                                              | nted: Read as '                         | o'               |                     |                                                                                |                 |        |  |  |  |  |  |  |

| bit 14-12             | -                                                                                                                                      |                                         |                  | rrupt Priority bits | 3                                                                              |                 |        |  |  |  |  |  |  |

| 511 112               | <b>IC5IP&lt;2:0&gt;:</b> Input Capture Channel 5 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | •                                                                                                                                      | •                                       |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | •                                                                                                                                      |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | •                                                                                                                                      | untin Drianity (                        |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       |                                                                                                                                        | upt is Priority 1<br>upt source is dis  | abled            |                     |                                                                                |                 |        |  |  |  |  |  |  |

| bit 11                |                                                                                                                                        | •                                       |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

| bit 10-8              | Unimplemented: Read as '0'                                                                                                             |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits                                                                            |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                                         |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | •                                                                                                                                      |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | •                                                                                                                                      |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       |                                                                                                                                        | upt is Priority 1                       | ablad            |                     |                                                                                |                 |        |  |  |  |  |  |  |

| 🗕                     |                                                                                                                                        | upt source is dis<br>nted: Read as '(   |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

|                       | -                                                                                                                                      |                                         |                  | rrupt Drigrity bits | _                                                                              |                 |        |  |  |  |  |  |  |

| bit 7                 | IC3IP<2:0>: Input Capture Channel 3 Interrupt Priority bits                                                                            |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |

| bit 7<br>bit 6-4      |                                                                                                                                        | • •                                     | hish a sturiouit | (intermunt)         | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                 |        |  |  |  |  |  |  |

|                       |                                                                                                                                        | • •                                     | highest priorit  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |

|                       |                                                                                                                                        | • •                                     | highest priorit  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |

|                       | 111 = Interr<br>•<br>•                                                                                                                 | upt is Priority 7 (                     | highest priorit  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |

|                       | 111 = Interr<br>•<br>•<br>001 = Interr                                                                                                 | upt is Priority 7(<br>upt is Priority 1 |                  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |

|                       | 111 = Interr<br>•<br>•<br>001 = Interr<br>000 = Interr                                                                                 | upt is Priority 7 (                     | abled            | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |

# 9.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Power-Saving Features"* (DS39698). Additional power-saving tips can also be found in Appendix B: "Additional Guidance for PIC24FJ64GA004 Family Applications" of this document.

The PIC24FJ64GA004 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0** "Oscillator Configuration".

### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 9-1. Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

### 9.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the Input Change Notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

Additional power reductions can be achieved by disabling the on-chip voltage regulator whenever Sleep mode is invoked. This is done by clearing the PMSLP bit (RCON<8>). Disabling the regulator adds an additional delay of about 190  $\mu$ s to the device wake-up time. It is recommended that applications not using the voltage regulator leave the PMSLP bit set. For additional details on the regulator and Sleep mode, see **Section 24.2.5 "Voltage Regulator Standby Mode"**.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled.

- · On any form of device Reset.

- On a WDT time-out.

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; Put the device into SLEEP mode |

|--------|-------------|----------------------------------|

| PWRSAV | #IDLE_MODE  | ; Put the device into IDLE mode  |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | —   | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |     |     |        |        |        |        | bit 0  |

|        |     |     |        |        |        |        |        |

|        |     |     |        |        |        |        |        |

### REGISTER 10-11: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 12-8  | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                     |

| bit 4-0   | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits    |

### REGISTER 10-12: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0                                                       | U-0          | U-0   | U-0                                                                                                      | U-0                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------|--------------|-------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                                                         | —            | —     | —                                                                                                        | —                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                           |              |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |