Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

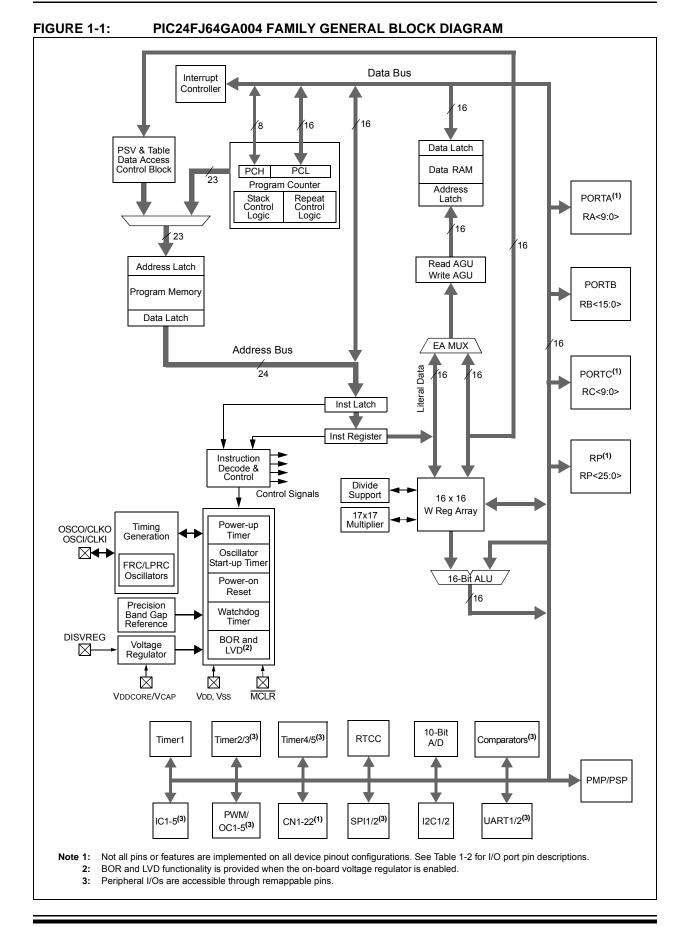

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

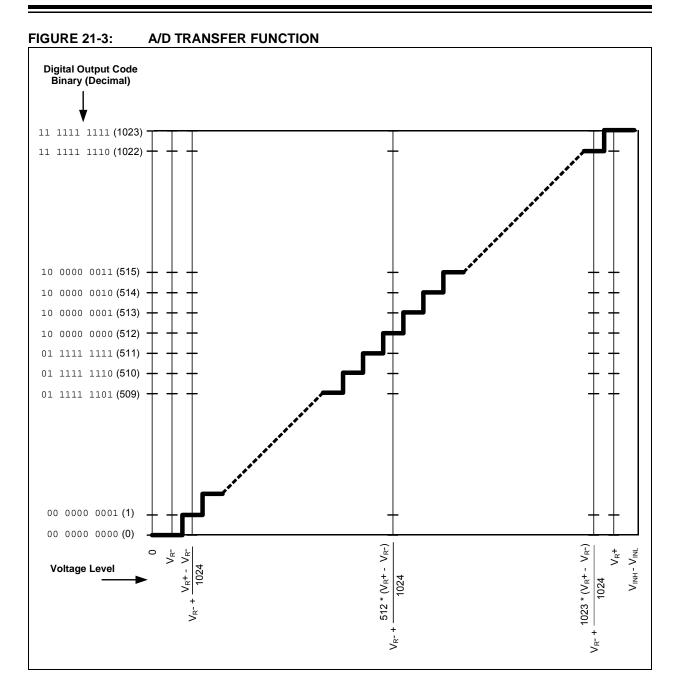

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga002-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

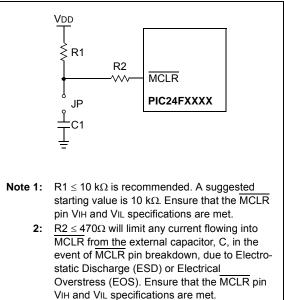

### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

#### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |  |  |  |  |

|-------------|-------------------------------------------------------------|--|--|--|--|

| ASR         | Arithmetic shift right source register by one or more bits. |  |  |  |  |

| SL          | Shift left source register by one or more bits.             |  |  |  |  |

| LSR         | Logical shift right source register by one or more bits.    |  |  |  |  |

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| -                   | row programming operations      |     |                                       |

|---------------------|---------------------------------|-----|---------------------------------------|

|                     | 0x4001, W0                      | ;   |                                       |

|                     | ), NVMCON                       |     | Initialize NVMCON                     |

| ; Set up a pointer  | to the first program memory lo  | C   | ation to be written                   |

| ; program memory se | elected, and writes enabled     |     |                                       |

|                     | )x0000, W0                      | ;   |                                       |

| MOV WO              | ), TBLPAG                       | ;   | Initialize PM Page Boundary SFR       |

|                     | )x6000, W0                      |     | An example program memory address     |

|                     | ' instructions to write the lat | tcl | hes                                   |

| ; 0th_program_word  |                                 |     |                                       |

| MOV #I              | LOW_WORD_0, W2                  | ;   |                                       |

|                     | HIGH_BYTE_0, W3                 | ;   |                                       |

| TBLWTL W2           | 2, [WO]                         |     | Write PM low word into program latch  |

| TBLWTH W3           | 3, [WO++]                       | ;   | Write PM high byte into program latch |

| ; 1st_program_word  |                                 |     |                                       |

|                     | LOW_WORD_1, W2                  | ;   |                                       |

|                     | HIGH_BYTE_1, W3                 | ;   |                                       |

|                     | 2, [WO]                         |     | Write PM low word into program latch  |

|                     | 3, [WO++]                       | ;   | Write PM high byte into program latch |

| ; 2nd_program_word  |                                 |     |                                       |

|                     | LOW_WORD_2, W2                  | ;   |                                       |

|                     | HIGH_BYTE_2, W3                 | ;   |                                       |

| TBLWTL W2           |                                 |     | Write PM low word into program latch  |

| TBLWTH W3           | 3, [WO++]                       | ;   | Write PM high byte into program latch |

| •                   |                                 |     |                                       |

| •                   |                                 |     |                                       |

| •                   |                                 |     |                                       |

| ; 63rd_program_word |                                 |     |                                       |

|                     | LOW_WORD_31, W2                 | ;   |                                       |

|                     | HIGH_BYTE_31, W3                | ;   |                                       |

| TBLWTL W2           |                                 |     | Write PM low word into program latch  |

| TBLWTH W3           | 3, [WO]                         | ;   | Write PM high byte into program latch |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI |             | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; 2 NOPs required after setting WR      |

| NOP  |             | ;                                       |

| BTSC | NVMCON, #15 | ; Wait for the sequence to be completed |

| BRA  | \$-2        | ;                                       |

|      |             |                                         |

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device has been in Idle mode

- 0 = Device has not been in Idle mode

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred (note that BOR is also set after a Power-on Reset)

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

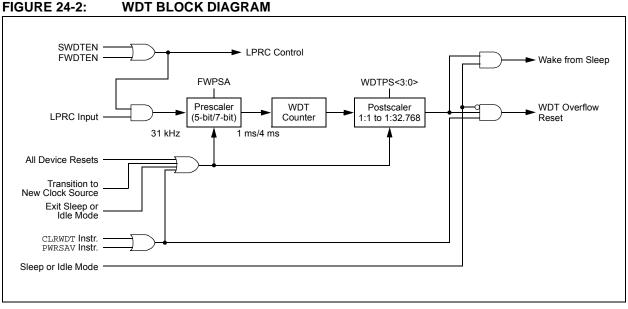

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

#### TABLE 6-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, will automatically be inserted after the POR and PWRT delay times. The FSCM will not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 100  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay will prevent an oscillator failure trap at a device Reset when the PWRT is disabled.

### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the CW2 register (see Table 6-2). The RCFGCAL and NVMCON registers are only affected by a POR.

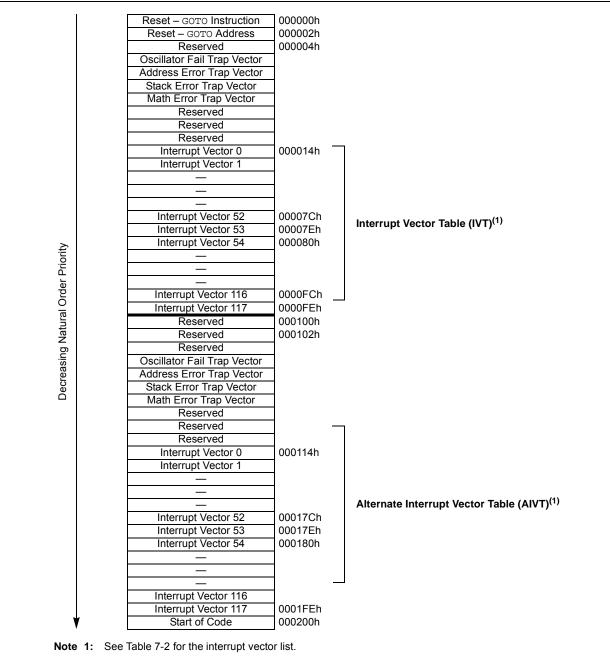

#### FIGURE 7-1: PIC24F INTERRUPT VECTOR TABLE

#### TABLE 7-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 0001172h     | Reserved           |

|                           | Vector |             | ΑΙντ    | Interrupt Bit Locations |          |              |  |

|---------------------------|--------|-------------|---------|-------------------------|----------|--------------|--|

| Interrupt Source          | Number | IVT Address | Address | Flag                    | Enable   | Priority     |  |

| ADC1 Conversion Done      | 13     | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |

| Comparator Event          | 18     | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |

| CRC Generator             | 67     | 00009Ah     | 00019Ah | IFS4<3>                 | IEC4<3>  | IPC16<14:12> |  |

| External Interrupt 0      | 0      | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |

| External Interrupt 1      | 20     | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |

| External Interrupt 2      | 29     | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |

| I2C1 Master Event         | 17     | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |

| I2C1 Slave Event          | 16     | 000034h     | 000034h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |

| I2C2 Master Event         | 50     | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |

| I2C2 Slave Event          | 49     | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |

| Input Capture 1           | 1      | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |

| Input Capture 2           | 5      | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |

| Input Capture 3           | 37     | 00005Eh     | 00015Eh | IFS2<5>                 | IEC2<5>  | IPC9<6:4>    |  |

| Input Capture 4           | 38     | 000060h     | 000160h | IFS2<6>                 | IEC2<6>  | IPC9<10:8>   |  |

| Input Capture 5           | 39     | 000062h     | 000162h | IFS2<7>                 | IEC2<7>  | IPC9<14:12>  |  |

| Input Change Notification | 19     | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |

| Output Compare 1          | 2      | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |

| Output Compare 2          | 6      | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |

| Output Compare 3          | 25     | 000046h     | 000146h | IFS1<9>                 | IEC1<9>  | IPC6<6:4>    |  |

| Output Compare 4          | 26     | 000048h     | 000148h | IFS1<10>                | IEC1<10> | IPC6<10:8>   |  |

| Output Compare 5          | 41     | 000066h     | 000166h | IFS2<9>                 | IEC2<9>  | IPC10<6:4>   |  |

| Parallel Master Port      | 45     | 00006Eh     | 00016Eh | IFS2<13>                | IEC2<13> | IPC11<6:4>   |  |

| Real-Time Clock/Calendar  | 62     | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |

| SPI1 Error                | 9      | 000026h     | 000126h | IFS0<9>                 | IEC0<9>  | IPC2<6:4>    |  |

| SPI1 Event                | 10     | 000028h     | 000128h | IFS0<10>                | IEC0<10> | IPC2<10:8>   |  |

| SPI2 Error                | 32     | 000054h     | 000154h | IFS2<0>                 | IEC0<0>  | IPC8<2:0>    |  |

| SPI2 Event                | 33     | 000056h     | 000156h | IFS2<1>                 | IEC2<1>  | IPC8<6:4>    |  |

| Timer1                    | 3      | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |

| Timer2                    | 7      | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |

| Timer3                    | 8      | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |

| Timer4                    | 27     | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |

| Timer5                    | 28     | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |

| UART1 Error               | 65     | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |

| UART1 Receiver            | 11     | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |

| UART1 Transmitter         | 12     | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |

| UART2 Error               | 66     | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |

| UART2 Receiver            | 30     | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |

| UART2 Transmitter         | 31     | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |

| Low-Voltage Detect (LVD)  | 72     | 0000A4h     | 000124h | IFS4<8>                 | IEC4<8>  | IPC17<2:0>   |  |

TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

| R/W-0         | R/W-0           | R/W-0                               | R/W-0                 | R/W-0             | R/W-0           | R/W-0           | U-0     |

|---------------|-----------------|-------------------------------------|-----------------------|-------------------|-----------------|-----------------|---------|

| U2TXIE        | U2RXIE          | INT2IE <sup>(1)</sup>               | T5IE                  | T4IE              | OC4IE           | OC3IE           |         |

| bit 15        |                 |                                     |                       |                   |                 |                 | bit 8   |

| U-0           | U-0             | U-0                                 | R/W-0                 | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|               | 0-0             | 0-0                                 | INT1IE <sup>(1)</sup> | CNIE              | CMIE            | MI2C1IE         | SI2C1IE |

| bit 7         |                 |                                     |                       | ONL               | OWIL            | WIZO IIL        | bit     |

|               |                 |                                     |                       |                   |                 |                 |         |

| Legend:       |                 |                                     |                       |                   |                 |                 |         |

| R = Readabl   |                 | W = Writable                        |                       | -                 | nented bit, rea |                 |         |

| -n = Value at | POR             | '1' = Bit is set                    |                       | '0' = Bit is clea | ared            | x = Bit is unkn | own     |

| bit 15        | U2TXIE: UAF     | RT2 Transmitter                     | Interrupt Enat        | ole bit           |                 |                 |         |

|               |                 | request is enab                     | -                     |                   |                 |                 |         |

|               |                 | request is not e                    |                       |                   |                 |                 |         |

| bit 14        | U2RXIE: UAF     | RT2 Receiver Ir                     | nterrupt Enable       | bit               |                 |                 |         |

|               | 1 = Interrupt   | request is enab                     | led                   |                   |                 |                 |         |

|               |                 | request is not e                    |                       |                   |                 |                 |         |

| bit 13        |                 | rnal Interrupt 2                    |                       |                   |                 |                 |         |

|               |                 | request is enab                     |                       |                   |                 |                 |         |

| bit 12        | -               | request is not e<br>Interrupt Enab  |                       |                   |                 |                 |         |

|               |                 | request is enab                     |                       |                   |                 |                 |         |

|               |                 | request is not e                    |                       |                   |                 |                 |         |

| bit 11        | T4IE: Timer4    | Interrupt Enab                      | le bit                |                   |                 |                 |         |

|               |                 | request is enab<br>request is not e |                       |                   |                 |                 |         |

| bit 10        | OC4IE: Outp     | ut Compare Ch                       | annel 4 Interru       | pt Enable bit     |                 |                 |         |

|               |                 | request is enab                     |                       |                   |                 |                 |         |

| 1.1.0         |                 | request is not e                    |                       |                   |                 |                 |         |

| bit 9         | -               | ut Compare Ch                       |                       | pt Enable bit     |                 |                 |         |

|               |                 | request is enab<br>request is not e |                       |                   |                 |                 |         |

| bit 8-5       |                 | ted: Read as '                      |                       |                   |                 |                 |         |

| bit 4         | -               | rnal Interrupt 1                    |                       |                   |                 |                 |         |

|               |                 | request is enab                     |                       |                   |                 |                 |         |

|               | 0 = Interrupt   | request is not e                    | nabled                |                   |                 |                 |         |

| bit 3         | CNIE: Input C   | Change Notifica                     | tion Interrupt E      | nable bit         |                 |                 |         |

|               | •               | request is enab                     |                       |                   |                 |                 |         |

| bit 2         | •               | request is not e                    |                       |                   |                 |                 |         |

| DIL Z         | -               | arator Interrupt<br>request is enab |                       |                   |                 |                 |         |

|               |                 | request is enab                     |                       |                   |                 |                 |         |

| bit 1         | -               | ster I2C1 Even                      |                       | ble bit           |                 |                 |         |

|               |                 | request is enab                     | -                     |                   |                 |                 |         |

|               | 0 = Interrupt   | request is not e                    | nabled                |                   |                 |                 |         |

| bit 0         |                 | ve I2C1 Event                       | •                     | e bit             |                 |                 |         |

|               |                 | request is enab                     |                       |                   |                 |                 |         |

|               | 0 = Interrupt I | request is not e                    | napled                |                   |                 |                 |         |

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

#### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

|              | _                                                         | _                                                                                                | -                         |                  |                 |                 |         |  |  |  |

|--------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|------------------|-----------------|-----------------|---------|--|--|--|

| U-0          | U-0                                                       | U-0                                                                                              | U-0                       | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |

| _            | _                                                         | _                                                                                                | —                         | _                | MI2C2P2         | MI2C2P1         | MI2C2P0 |  |  |  |

| bit 15       |                                                           |                                                                                                  | ·                         |                  | ·               |                 | bit     |  |  |  |

|              |                                                           |                                                                                                  |                           |                  |                 |                 |         |  |  |  |

| U-0          | R/W-1                                                     | R/W-0                                                                                            | R/W-0                     | U-0              | U-0             | U-0             | U-0     |  |  |  |

|              | SI2C2P2                                                   | SI2C2P1                                                                                          | SI2C2P0                   |                  | <u> </u>        |                 | —       |  |  |  |

| bit 7        |                                                           |                                                                                                  |                           |                  |                 |                 | bit (   |  |  |  |

|              |                                                           |                                                                                                  |                           |                  |                 |                 |         |  |  |  |

| Legend:      |                                                           |                                                                                                  |                           |                  |                 |                 |         |  |  |  |

| R = Readab   | le bit                                                    | W = Writable                                                                                     | bit                       | U = Unimpler     | mented bit, rea | d as '0'        |         |  |  |  |

| -n = Value a | t POR                                                     | '1' = Bit is set                                                                                 |                           | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |

| bit 7        | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru | >: Master I2C2<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as 'o | highest priority<br>abled | •                |                 |                 |         |  |  |  |

| bit 6-4      | -                                                         | Slave I2C2 E                                                                                     |                           | Priority hits    |                 |                 |         |  |  |  |

| DIL 0-4      | 111 = Interru<br>•<br>•<br>001 = Interru                  | pt is Priority 1<br>pt is Priority 1<br>pt source is dis                                         | highest priority          | •                |                 |                 |         |  |  |  |

| bit 3-0      | Unimplemen                                                | ted: Read as '                                                                                   | o'                        |                  |                 |                 |         |  |  |  |

|              |                                                           |                                                                                                  |                           |                  |                 |                 |         |  |  |  |

| U-0                                | U-0        | U-0             | R/W-0                                   | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |  |

|------------------------------------|------------|-----------------|-----------------------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|

| _                                  |            | _               | RP25R4 <sup>(1)</sup>                   | RP25R3 <sup>(1)</sup>              | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> |  |

| bit 15                             |            |                 |                                         |                                    |                       |                       | bit 8                 |  |

|                                    |            |                 |                                         |                                    |                       |                       |                       |  |

| U-0                                | U-0        | U-0             | R/W-0                                   | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |  |

| _                                  |            | —               | RP24R4 <sup>(1)</sup>                   | RP24R3 <sup>(1)</sup>              | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> |  |

| bit 7                              |            |                 | •                                       | •                                  |                       |                       | bit 0                 |  |

|                                    |            |                 |                                         |                                    |                       |                       |                       |  |

| Legend:                            |            |                 |                                         |                                    |                       |                       |                       |  |

| R = Readable                       | e bit      | W = Writable    | bit                                     | U = Unimplemented bit, read as '0' |                       |                       |                       |  |

| -n = Value at POR '1' = Bit is set |            |                 | '0' = Bit is cleared x = Bit is unknown |                                    |                       |                       |                       |  |

|                                    |            |                 |                                         |                                    |                       |                       |                       |  |

| bit 15-13                          | Unimplemen | ted: Read as '@ | י'                                      |                                    |                       |                       |                       |  |

#### REGISTER 10-27: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

bit 15-13 Unimplemented: Read as '0

RP25R<4:0>: Peripheral Output Function is Assigned to RP25 Output Pin bits<sup>(1)</sup> bit 12-8 (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

RP24R<4:0>: Peripheral Output Function is Assigned to RP24 Output Pin bits<sup>(1)</sup> bit 4-0 (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

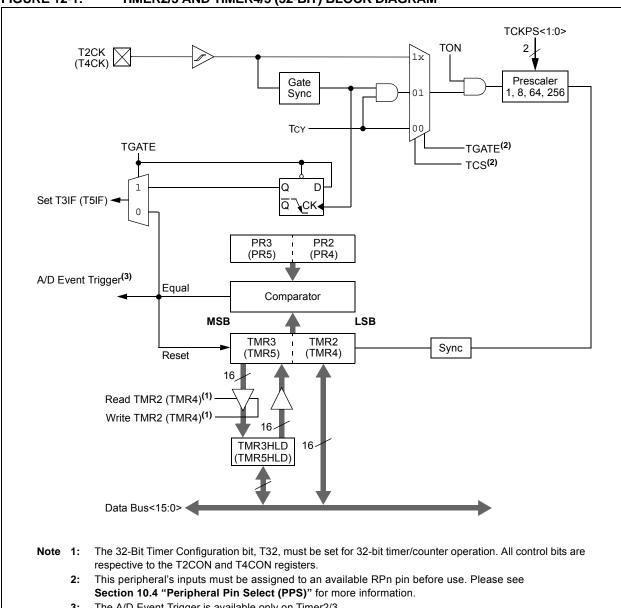

#### **FIGURE 12-1:** TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

3: The A/D Event Trigger is available only on Timer2/3.

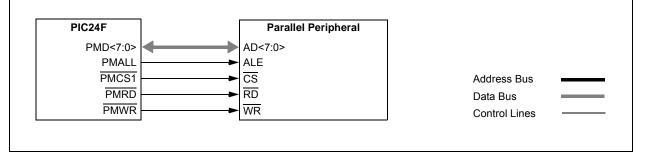

#### FIGURE 18-9: EXAMPLE OF AN 8-BIT MULTIPLEXED ADDRESS AND DATA APPLICATION

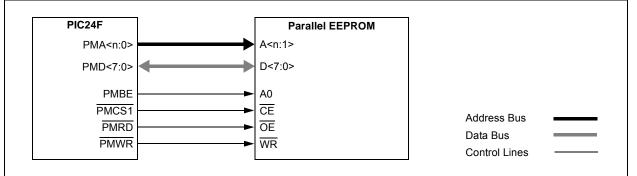

#### FIGURE 18-10: PARALLEL EEPROM EXAMPLE (UP TO 11-BIT ADDRESS, 8-BIT DATA)

| PIC24F          |                       | Parallel EEPROM |               |  |

|-----------------|-----------------------|-----------------|---------------|--|

| PMA <n:0></n:0> |                       | A <n:0></n:0>   |               |  |

| PMD<7:0>        | $\longleftrightarrow$ | D<7:0>          |               |  |

| PMCS1           | -                     | CE              | Address Bus   |  |

| PMRD<br>PMWR    |                       |                 | Data Bus      |  |

| PINIVR          |                       | VVR             | Control Lines |  |

#### FIGURE 18-11: PARALLEL EEPROM EXAMPLE (UP TO 11-BIT ADDRESS, 16-BIT DATA)

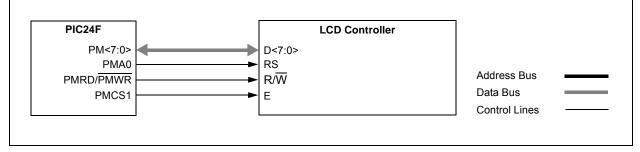

#### FIGURE 18-12: LCD CONTROL EXAMPLE (BYTE MODE OPERATION)

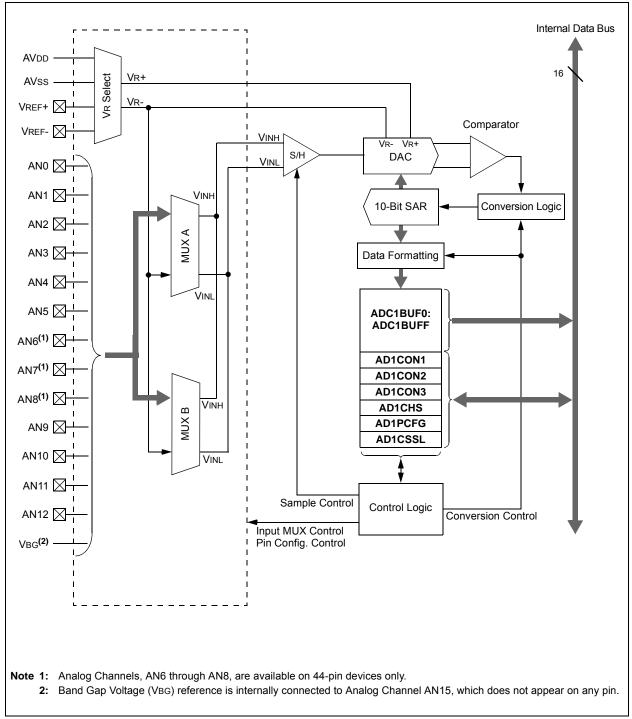

#### FIGURE 21-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

| R/W-0        | U-0                                                                                                   | R/C-0                                  | R/C-0                            | R/W-0                                   | R/W-0           | R/W-0                  | R/W-0                  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|-----------------------------------------|-----------------|------------------------|------------------------|--|--|--|

| CMIDL        |                                                                                                       | C2EVT                                  | C1EVT                            | C2EN                                    | C1EN            | C2OUTEN <sup>(1)</sup> | C1OUTEN <sup>(2)</sup> |  |  |  |

| bit 15       |                                                                                                       |                                        |                                  |                                         |                 |                        | bit 8                  |  |  |  |

| R-0          | R-0                                                                                                   | R/W-0                                  | R/W-0                            | R/W-0                                   | R/W-0           | R/W-0                  | R/W-0                  |  |  |  |

| C2OUT        | C1OUT                                                                                                 | C2INV                                  | C1INV                            | C2NEG                                   | C2POS           | C1NEG                  | C1POS                  |  |  |  |

| bit 7        | 01001                                                                                                 | 02111                                  | Onite                            | OZINEO                                  | 021 00          | OINEO                  | bit (                  |  |  |  |

|              |                                                                                                       |                                        |                                  |                                         |                 |                        |                        |  |  |  |

| Legend:      |                                                                                                       | C = Clearable                          | bit                              |                                         |                 |                        |                        |  |  |  |

| R = Readab   | le bit                                                                                                | W = Writable                           | bit                              | U = Unimplem                            | nented bit, rea | ad as '0'              |                        |  |  |  |

| -n = Value a | t POR                                                                                                 | '1' = Bit is set                       |                                  | '0' = Bit is clea                       | ared            | x = Bit is unkr        | iown                   |  |  |  |

| bit 15       |                                                                                                       | naratar Stan in                        | Idla Mada hit                    |                                         |                 |                        |                        |  |  |  |

| DIC 15       |                                                                                                       | parator Stop in<br>vice enters Idle    |                                  | e does not aene                         | erate interrunt | s; module is still     | enabled                |  |  |  |

|              |                                                                                                       | s normal modu                          |                                  |                                         |                 |                        | onabioa                |  |  |  |

| bit 14       | Unimplemen                                                                                            | ted: Read as '                         | )'                               |                                         |                 |                        |                        |  |  |  |

| bit 13       | C2EVT: Com                                                                                            | parator 2 Event                        | :                                |                                         |                 |                        |                        |  |  |  |

|              |                                                                                                       | tor output char                        | 0                                |                                         |                 |                        |                        |  |  |  |

|              | -                                                                                                     | itor output did r                      | -                                | tes                                     |                 |                        |                        |  |  |  |

| bit 12       | C1EVT: Comparator 1 Event                                                                             |                                        |                                  |                                         |                 |                        |                        |  |  |  |

|              | <ol> <li>Comparator output changed states</li> <li>Comparator output did not change states</li> </ol> |                                        |                                  |                                         |                 |                        |                        |  |  |  |

| bit 11       | -                                                                                                     | arator 2 Enable                        | -                                |                                         |                 |                        |                        |  |  |  |

|              |                                                                                                       | tor is enabled<br>tor is disabled      |                                  |                                         |                 |                        |                        |  |  |  |

| bit 10       | C1EN: Comp                                                                                            | C1EN: Comparator 1 Enable              |                                  |                                         |                 |                        |                        |  |  |  |

|              |                                                                                                       | tor is enabled                         |                                  |                                         |                 |                        |                        |  |  |  |

|              | •                                                                                                     | itor is disabled                       |                                  | <b>`</b>                                |                 |                        |                        |  |  |  |

| bit 9        |                                                                                                       | Comparator 2 O                         | -                                |                                         |                 |                        |                        |  |  |  |

|              |                                                                                                       | itor output is dr<br>itor output is no |                                  |                                         |                 |                        |                        |  |  |  |

| bit 8        |                                                                                                       | comparator 1 O                         |                                  |                                         |                 |                        |                        |  |  |  |

|              | 1 = Compara                                                                                           | ntor output is dr<br>ntor output is no | iven on the ou                   | tput pad                                |                 |                        |                        |  |  |  |

| bit 7        |                                                                                                       | parator 2 Outp                         |                                  |                                         |                 |                        |                        |  |  |  |

|              | When C2INV                                                                                            |                                        |                                  |                                         |                 |                        |                        |  |  |  |

|              | 1 = C2 VIN + 3                                                                                        |                                        |                                  |                                         |                 |                        |                        |  |  |  |

|              | $0 = C2 VIN + \frac{1}{2}$                                                                            |                                        |                                  |                                         |                 |                        |                        |  |  |  |

|              | $\frac{\text{When C2INV}}{0 = C2 \text{VIN} + 3}$                                                     |                                        |                                  |                                         |                 |                        |                        |  |  |  |

|              | 1 = C2 VIN+                                                                                           | -                                      |                                  |                                         |                 |                        |                        |  |  |  |

| Note 1: If   | C2OUTEN = 1,                                                                                          | the C2OUT pe                           | ripheral outpu<br>elect (PPS)" f | t must be config<br>or more information | gured to an av  | ailable RPn pin.       | See                    |  |  |  |

#### REGISTER 22-1: CMCON: COMPARATOR CONTROL REGISTER

- Section 10.4 "Peripheral Pin Select (PPS)" for more information.

If C10UTEN = 1, the C10UT peripheral output must be configured to an available RPn pin. See

- If C100TEN = 1, the C100T peripheral output must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

#### 24.3.1 WINDOWED OPERATION

The Watchdog Timer has an optional Fixed Window mode of operation. In this Windowed mode, CLRWDT instructions can only reset the WDT during the last 1/4 of the programmed WDT period. A CLRWDT instruction executed before that window causes a WDT Reset, similar to a WDT time-out.

Windowed WDT mode is enabled by programming the WINDIS Configuration bit (CW1<6>) to '0'.

#### 24.3.2 CONTROL REGISTER

The WDT is enabled or disabled by the FWDTEN Configuration bit. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

| Assembly<br>Mnemonic | Assembly Syntax |              | Description                                      | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|--------------|--------------------------------------------------|---------------|----------------|--------------------------|

| ADD                  | ADD f           |              | f = f + WREG                                     | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD             | f,WREG       | WREG = f + WREG                                  | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD             | #lit10,Wn    | Wd = lit10 + Wd                                  | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD             | Wb,Ws,Wd     | Wd = Wb + Ws                                     | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD             | Wb,#lit5,Wd  | Wd = Wb + lit5                                   | 1             | 1              | C, DC, N, OV, Z          |

| ADDC                 | ADDC            | f            | f = f + WREG + (C)                               | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC            | f,WREG       | WREG = f + WREG + (C)                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC            | #lit10,Wn    | Wd = lit10 + Wd + (C)                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC            | Wb,Ws,Wd     | Wd = Wb + Ws + (C)                               | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC            | Wb,#lit5,Wd  | Wd = Wb + Iit5 + (C)                             | 1             | 1              | C, DC, N, OV, Z          |

| AND                  | AND             | f            | f = f .AND. WREG                                 | 1             | 1              | N, Z                     |

|                      | AND             | f,WREG       | WREG = f .AND. WREG                              | 1             | 1              | N, Z                     |

|                      | AND             | #lit10,Wn    | Wd = lit10 .AND. Wd                              | 1             | 1              | N, Z                     |

|                      | AND             | Wb,Ws,Wd     | Wd = Wb .AND. Ws                                 | 1             | 1              | N, Z                     |

|                      | AND             | Wb,#lit5,Wd  | Wd = Wb .AND. lit5                               | 1             | 1              | N, Z                     |

| ASR                  | ASR             | f            | f = Arithmetic Right Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | ASR             | f,WREG       | WREG = Arithmetic Right Shift f                  | 1             | 1              | C, N, OV, Z              |

|                      | ASR             | Ws,Wd        | Wd = Arithmetic Right Shift Ws                   | 1             | 1              | C, N, OV, Z              |

|                      | ASR             | Wb,Wns,Wnd   | Wnd = Arithmetic Right Shift Wb by Wns           | 1             | 1              | N, Z                     |

|                      | ASR             | Wb,#lit4,Wnd | Wnd = Arithmetic Right Shift Wb by lit4          | 1             | 1              | N, Z                     |

| BCLR                 | BCLR            | f,#bit4      | Bit Clear f                                      | 1             | 1              | None                     |

|                      | BCLR            | Ws,#bit4     | Bit Clear Ws                                     | 1             | 1              | None                     |

| BRA                  | BRA             | C,Expr       | Branch if Carry                                  | 1             | 1 (2)          | None                     |

|                      | BRA             | GE, Expr     | Branch if Greater than or Equal                  | 1             | 1 (2)          | None                     |

|                      | BRA             | GEU, Expr    | Branch if Unsigned Greater than or Equal         | 1             | 1 (2)          | None                     |

|                      | BRA             | GT, Expr     | Branch if Greater than                           | 1             | 1 (2)          | None                     |

|                      | BRA             | GTU, Expr    | Branch if Unsigned Greater than                  | 1             | 1 (2)          | None                     |

|                      | BRA             | LE, Expr     | Branch if Less than or Equal                     | 1             | 1 (2)          | None                     |

|                      | BRA             | LEU, Expr    | Branch if Unsigned Less than or Equal            | 1             | 1 (2)          | None                     |

|                      | BRA             | LT, Expr     | Branch if Less than                              | 1             | 1 (2)          | None                     |

|                      | BRA             | LTU, Expr    | Branch if Unsigned Less than                     | 1             | 1 (2)          | None                     |

|                      | BRA             |              | Branch if Negative                               | 1             | 1 (2)          | None                     |

|                      |                 | N, Expr      | Branch if Not Carry                              | 1             |                | None                     |

|                      | BRA             | NC, Expr     |                                                  | 1             | 1 (2)          | None                     |

|                      | BRA             | NN, Expr     | Branch if Not Negative<br>Branch if Not Overflow |               | 1 (2)<br>1 (2) | None                     |

|                      | BRA             | NOV, Expr    |                                                  | 1             |                |                          |

|                      | BRA             | NZ,Expr      | Branch if Not Zero                               | 1             | 1 (2)          | None                     |

|                      | BRA             | OV,Expr      | Branch if Overflow                               | 1             | 1 (2)          | None                     |

|                      | BRA             | Expr         | Branch Unconditionally                           | 1             | 2              | None                     |

|                      | BRA             | Z,Expr       | Branch if Zero                                   | 1             | 1 (2)          | None                     |

|                      | BRA             | Wn           | Computed Branch                                  | 1             | 2              | None                     |

| BSET                 | BSET            | f,#bit4      | Bit Set f                                        | 1             | 1              | None                     |

|                      | BSET            | Ws,#bit4     | Bit Set Ws                                       | 1             | 1              | None                     |

| BSW                  | BSW.C           | Ws,Wb        | Write C bit to Ws <wb></wb>                      | 1             | 1              | None                     |

|                      | BSW.Z           | Ws,Wb        | Write Z bit to Ws <wb></wb>                      | 1             | 1              | None                     |

| BTG                  | BTG             | f,#bit4      | Bit Toggle f                                     | 1             | 1              | None                     |

|                      | BTG             | Ws,#bit4     | Bit Toggle Ws                                    | 1             | 1              | None                     |

| BTSC                 | BTSC            | f,#bit4      | Bit Test f, Skip if Clear                        | 1             | 1<br>(2 or 3)  | None                     |

|                      | BTSC            | Ws,#bit4     | Bit Test Ws, Skip if Clear                       | 1             | 1<br>(2 or 3)  | None                     |

| TABLE 26-2: | <b>INSTRUCTION SET</b> | <b>OVERVIEW</b> |

|-------------|------------------------|-----------------|

|             |                        |                 |

| Assembly<br>Mnemonic |        | Assembly Syntax | ntax Description             |   | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|------------------------------|---|----------------|--------------------------|

| TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>  | 1 | 2              | None                     |

| TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1 | 2              | None                     |

| TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1 | 2              | None                     |

| TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1 | 2              | None                     |

| ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1 | 1              | None                     |

| XOR                  | XOR    | f               | f = f .XOR. WREG             | 1 | 1              | N, Z                     |

|                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1 | 1              | N, Z                     |

|                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1 | 1              | N, Z                     |

|                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1 | 1              | N, Z                     |

|                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1 | 1              | N, Z                     |

| ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws         | 1 | 1              | C, Z, N                  |

#### TABLE 26-2: INSTRUCTION SET OVERVIEW (CONTINUED)

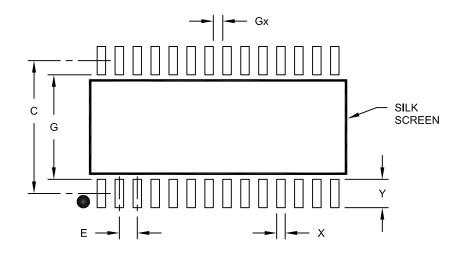

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units |          | MILLIMETERS |      |  |  |

|--------------------------|-------|----------|-------------|------|--|--|

| Dimension Limits         |       | MIN      | NOM         | MAX  |  |  |

| Contact Pitch            | E     | 1.27 BSC |             |      |  |  |

| Contact Pad Spacing      | С     |          | 9.40        |      |  |  |

| Contact Pad Width (X28)  | X     |          |             | 0.60 |  |  |

| Contact Pad Length (X28) | Y     |          |             | 2.00 |  |  |

| Distance Between Pads    | Gx    | 0.67     |             |      |  |  |

| Distance Between Pads    | G     | 7.40     |             |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A