# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga002-i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | 1                             | Pin Number    |                    |     |                   |                                                                                            |  |  |  |  |  |

|----------|-------------------------------|---------------|--------------------|-----|-------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer   | Description                                                                                |  |  |  |  |  |

| OSCI     | 9                             | 6             | 30                 | Ι   | ANA               | Main Oscillator Input Connection.                                                          |  |  |  |  |  |

| OSCO     | 10                            | 7             | 31                 | 0   | ANA               | Main Oscillator Output Connection.                                                         |  |  |  |  |  |

| PGEC1    | 5                             | 2             | 22                 | I/O | ST                | In-Circuit Debugger/Emulator and ICSP™ Programming                                         |  |  |  |  |  |

| PGEC2    | 22                            | 19            | 9                  | I/O | ST                | Clock.                                                                                     |  |  |  |  |  |

| PGEC3    | 14                            | 12            | 42                 | I/O | ST                |                                                                                            |  |  |  |  |  |

| PGED1    | 4                             | 1             | 21                 | I/O | ST                | In-Circuit Debugger/Emulator and ICSP Programming                                          |  |  |  |  |  |

| PGED2    | 21                            | 18            | 8                  | I/O | ST                | Data.                                                                                      |  |  |  |  |  |

| PGED3    | 15                            | 11            | 41                 | I/O | ST                |                                                                                            |  |  |  |  |  |

| PMA0     | 10                            | 7             | 3                  | I/O | ST/TTL            | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |  |  |  |  |  |

| PMA1     | 12                            | 9             | 2                  | I/O | ST/TTL            | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |  |  |  |  |  |

| PMA2     | —                             | _             | 27                 | 0   | —                 | Parallel Master Port Address (Demultiplexed Master                                         |  |  |  |  |  |

| PMA3     | —                             | _             | 38                 | 0   | —                 | modes).                                                                                    |  |  |  |  |  |

| PMA4     | —                             | _             | 37                 | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA5     | —                             | _             | 4                  | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA6     | —                             | _             | 5                  | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA7     | —                             | _             | 13                 | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA8     | —                             | —             | 32                 | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA9     | —                             | _             | 35                 | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA10    | —                             | _             | 12                 | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA11    | —                             | —             | _                  | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA12    | —                             | _             | _                  | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMA13    | —                             | _             | _                  | 0   | —                 |                                                                                            |  |  |  |  |  |

| PMBE     | 11                            | 8             | 36                 | 0   | —                 | Parallel Master Port Byte Enable Strobe.                                                   |  |  |  |  |  |

| PMCS1    | 26                            | 23            | 15                 | 0   | —                 | Parallel Master Port Chip Select 1 Strobe/Address Bit 14.                                  |  |  |  |  |  |

| PMD0     | 23                            | 20            | 10                 | I/O | ST/TTL            | Parallel Master Port Data (Demultiplexed Master mode) o                                    |  |  |  |  |  |

| PMD1     | 22                            | 19            | 9                  | I/O | ST/TTL            | Address/Data (Multiplexed Master modes).                                                   |  |  |  |  |  |

| PMD2     | 21                            | 18            | 8                  | I/O | ST/TTL            |                                                                                            |  |  |  |  |  |

| PMD3     | 18                            | 15            | 1                  | I/O | ST/TTL            |                                                                                            |  |  |  |  |  |

| PMD4     | 17                            | 14            | 44                 | I/O | ST/TTL            |                                                                                            |  |  |  |  |  |

| PMD5     | 16                            | 13            | 43                 | I/O | ST/TTL            |                                                                                            |  |  |  |  |  |

| PMD6     | 15                            | 12            | 42                 | I/O | ST/TTL            |                                                                                            |  |  |  |  |  |

| PMD7     | 14                            | 11            | 41                 | I/O | ST/TTL            |                                                                                            |  |  |  |  |  |

| PMRD     | 24                            | 21            | 11                 | 0   | _                 | Parallel Master Port Read Strobe.                                                          |  |  |  |  |  |

| PMWR     | 25                            | 22            | 14                 | 0   | _                 | Parallel Master Port Write Strobe.                                                         |  |  |  |  |  |

| Legend:  | TTL = TTL inp<br>ANA = Analog | level input/o | utput              |     | l <sup>2</sup> C™ | Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer                      |  |  |  |  |  |

### TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Note 1: Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

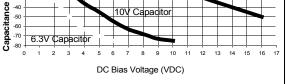

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

Typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

# FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V or 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to

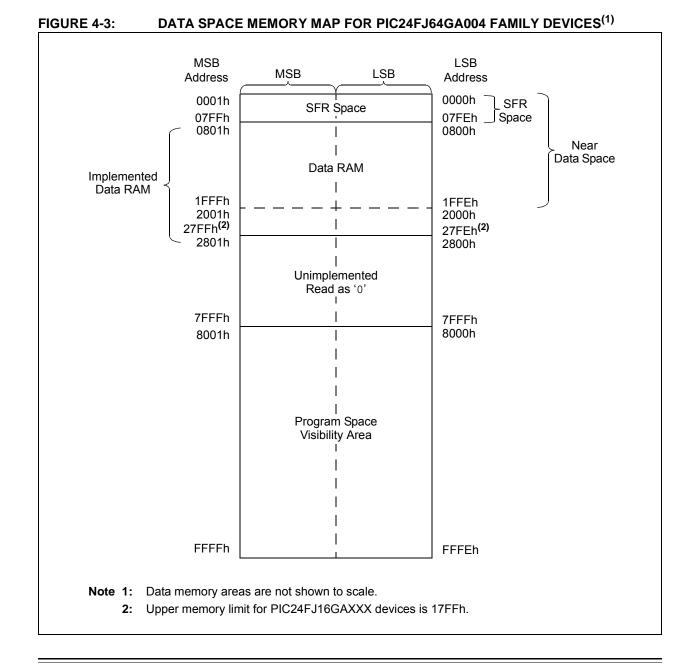

### 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility"). PIC24FJ64GA004 family devices implement a total of 8 Kbytes of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

| TABLE 4-6: | TIMER REGISTER MAP |

|------------|--------------------|

|            |                    |

|   | 0                   |

|---|---------------------|

|   | 201                 |

|   | 10-20               |

|   | ω                   |

|   | Mici                |

|   | Microchip Technolog |

|   | ъ<br>Н              |

|   | ech                 |

|   | no                  |

| : | <                   |

|   | n                   |

|   | •                   |

0

| File Name | Addr | Bit 15 | Bit 14                                                          | Bit 13                                        | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8        | Bit 7        | Bit 6       | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|-----------------------------------------------------------------|-----------------------------------------------|--------|--------|--------|-------------|--------------|--------------|-------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1      | 0100 |        |                                                                 |                                               |        |        |        |             | Timer1       | Register     |             |        |        |       |       |       |       | 0000          |

| PR1       | 0102 |        |                                                                 |                                               |        |        |        |             | Timer1 Peri  | iod Registe  | r           |        |        |       |       |       |       | FFFF          |

| T1CON     | 0104 | TON    | _                                                               | - TSIDL TGATE TCKPS1 TCKPS0 - TSYNC TCS - 000 |        |        |        |             |              |              |             |        | 0000   |       |       |       |       |               |

| TMR2      | 0106 |        | Timer2 Register 000                                             |                                               |        |        |        |             |              | 0000         |             |        |        |       |       |       |       |               |

| TMR3HLD   | 0108 |        | Timer3 Holding Register (for 32-bit timer operations only) 0000 |                                               |        |        |        |             |              | 0000         |             |        |        |       |       |       |       |               |

| TMR3      | 010A |        | Timer3 Register 0000                                            |                                               |        |        |        |             |              | 0000         |             |        |        |       |       |       |       |               |

| PR2       | 010C |        | Timer2 Period Register FFF                                      |                                               |        |        |        |             |              | FFFF         |             |        |        |       |       |       |       |               |

| PR3       | 010E |        |                                                                 |                                               |        |        |        |             | Timer3 Peri  | iod Registe  | r           |        |        |       |       |       |       | FFFF          |

| T2CON     | 0110 | TON    |                                                                 | TSIDL                                         | _      |        | _      |             | —            |              | TGATE       | TCKPS1 | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T3CON     | 0112 | TON    |                                                                 | TSIDL                                         | _      |        | _      |             | —            |              | TGATE       | TCKPS1 | TCKPS0 |       | —     | TCS   | —     | 0000          |

| TMR4      | 0114 |        |                                                                 |                                               |        |        |        |             | Timer4       | Register     |             |        |        |       |       |       |       | 0000          |

| TMR5HLD   | 0116 |        |                                                                 |                                               |        |        | Tin    | ner5 Holdin | g Register ( | for 32-bit o | perations o | nly)   |        |       |       |       |       | 0000          |

| TMR5      | 0118 |        |                                                                 |                                               |        |        |        |             | Timer5       | Register     |             |        |        |       |       |       |       | 0000          |

| PR4       | 011A |        | Timer4 Period Register FFF                                      |                                               |        |        |        |             | FFFF         |              |             |        |        |       |       |       |       |               |

| PR5       | 011C |        | Timer5 Period Register FFFF                                     |                                               |        |        |        |             | FFFF         |              |             |        |        |       |       |       |       |               |

| T4CON     | 011E | TON    |                                                                 | TSIDL                                         | _      |        | —      |             | —            |              | TGATE       | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T5CON     | 0120 | TON    | -                                                               | TSIDL                                         | _      | -      | _      | _           | —            | -            | TGATE       | TCKPS1 | TCKPS0 | _     | —     | TCS   | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-7: INPUT CAPTURE REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|-----------------------------|--------|--------|--------|--------|-------|-------------|-------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140 |        | Input Capture 1 Register FF |        |        |        |        |       |             |             |       |       |       | FFFF  |       |       |       |               |

| IC1CON       | 0142 | _      | _                           | ICSIDL | _      | _      | _      | _     | _           | ICTMR       | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC2BUF       | 0144 |        |                             |        |        |        |        | l     | nput Captur | e 2 Registe | er    |       |       |       |       |       |       | FFFF          |

| IC2CON       | 0146 | _      | _                           | ICSIDL | _      | _      | _      | _     | _           | ICTMR       | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC3BUF       | 0148 |        |                             |        |        |        |        | l     | nput Captur | e 3 Registe | er    |       |       |       |       |       |       | FFFF          |

| IC3CON       | 014A | _      | _                           | ICSIDL | _      | _      | _      | _     | _           | ICTMR       | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC4BUF       | 014C |        |                             |        |        |        |        | l     | nput Captur | e 4 Registe | er    |       |       |       |       |       |       | FFFF          |

| IC4CON       | 014E | _      | _                           | ICSIDL | _      | _      | _      | _     | _           | ICTMR       | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC5BUF       | 0150 |        |                             |        |        |        |        | l     | nput Captur | e 5 Registe | er    |       |       |       |       |       |       | FFFF          |

| IC5CON       | 0152 | _      | _                           | ICSIDL | _      | _      | —      | —     | _           | ICTMR       | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| Logondu      |      |        |                             |        |        |        |        |       |             |             |       |       |       |       |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: UART REGISTER MAP

|              | -    | -                                 |        |          |        |        |        |        |            |              |            |       |       |       |        |        |       |               |

|--------------|------|-----------------------------------|--------|----------|--------|--------|--------|--------|------------|--------------|------------|-------|-------|-------|--------|--------|-------|---------------|

| File<br>Name | Addr | Bit 15                            | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7        | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE       | 0220 | UARTEN                            |        | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0       | WAKE         | LPBACK     | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1                          | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT       | URXISEL1     | URXISEL0   | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | _                                 | _      | —        | —      | —      | _      | _      | UTX8       | UTX7         | UTX6       | UTX5  | UTX4  | UTX3  | UTX2   | UTX1   | UTX0  | 0000          |

| U1RXREG      | 0226 | _                                 | _      | _        | _      | _      | _      | _      | URX8       | URX7         | URX6       | URX5  | URX4  | URX3  | URX2   | URX1   | URX0  | 0000          |

| U1BRG        | 0228 |                                   |        |          |        |        |        | Baud R | ate Genera | tor Prescale | r Register |       |       |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN                            | _      | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0       | WAKE         | LPBACK     | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1                          | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT       | URXISEL1     | URXISEL0   | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _                                 | _      | _        | _      | _      | _      | _      | UTX8       | UTX7         | UTX6       | UTX5  | UTX4  | UTX3  | UTX2   | UTX1   | UTX0  | 0000          |

| U2RXREG      | 0236 | _                                 | _      | —        | —      | —      | _      | _      | URX8       | URX7         | URX6       | URX5  | URX4  | URX3  | URX2   | URX1   | URX0  | 0000          |

| U2BRG        | 0238 | Baud Rate Generator Prescaler 000 |        |          |        |        |        |        |            |              |            | 0000  |       |       |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-11: SPI REGISTER MAP

| File<br>Name | Addr | Bit 15                       | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8        | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|------------------------------|--------|---------|--------|--------|---------|---------|--------------|------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN                        | —      | SPISIDL | —      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 | -                            | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN                        | SPIFSD | SPIFPOL | -      | _      | _       | _       | _            | _          | _      | _      | -      | -      | _      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 |                              |        |         |        |        |         | SP      | 11 Transmit/ | Receive Bu | ffer   |        |        |        |        |        |        | 0000          |

| SPI2STAT     | 0260 | SPIEN                        | _      | SPISIDL | -      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1     | 0262 | -                            | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2     | 0264 | FRMEN                        | SPIFSD | SPIFPOL | -      | _      | _       | _       | _            | _          | _      | _      | -      | -      | _      | SPIFE  | SPIBEN | 0000          |

| SPI2BUF      | 0268 | SPI2 Transmit/Receive Buffer |        |         |        |        |         |         |              |            |        | 0000   |        |        |        |        |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

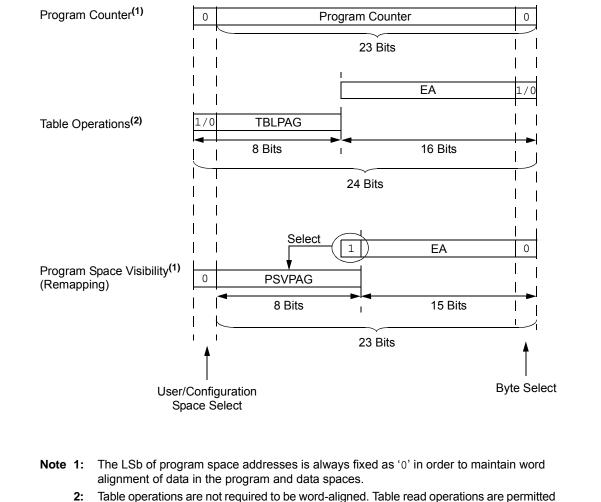

### TABLE 4-25: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        |                              | Program Space Address |                                   |            |   |  |  |  |  |  |  |  |

|--------------------------|---------------|------------------------------|-----------------------|-----------------------------------|------------|---|--|--|--|--|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>               | <15>                              | <14:1> <0> |   |  |  |  |  |  |  |  |

| Instruction Access       | User          | 0                            |                       | PC<22:1>                          |            | 0 |  |  |  |  |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |                       |                                   |            |   |  |  |  |  |  |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0>             | Data EA<15:0>                     |            |   |  |  |  |  |  |  |  |

| (Byte/Word Read/Write)   |               | 02                           | xxx xxxx              | XXXX XXXX XXXX XXXX               |            |   |  |  |  |  |  |  |  |

|                          | Configuration | TB                           | LPAG<7:0>             | Data EA<15:0>                     |            |   |  |  |  |  |  |  |  |

|                          |               | 1:                           | xxx xxxx              | XXXX XXXX XXXX XXXX               |            |   |  |  |  |  |  |  |  |

| Program Space Visibility | User          | 0                            | PSVPAG<7              | 7:0> Data EA<14:0> <sup>(1)</sup> |            |   |  |  |  |  |  |  |  |

| (Block Remap/Read)       |               | 0                            | XXXX XX               | x xxx xxxx xxxx xxxx              |            |   |  |  |  |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

### FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

**2:** Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat Steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY BLOCK

| ; Set up | NVMCON  | I for block erase operation          |   |                                       |  |

|----------|---------|--------------------------------------|---|---------------------------------------|--|

| 1        | MOV     | #0x4042, W0                          | ; |                                       |  |

| 1        | MOV     | W0, NVMCON                           | ; | Initialize NVMCON                     |  |

| ; Init p | pointer | to row to be ERASED                  |   |                                       |  |

| 1        | MOV     | <pre>#tblpage(PROG_ADDR), W0</pre>   | ; |                                       |  |

| 1        | MOV     | W0, TBLPAG                           | ; | Initialize PM Page Boundary SFR       |  |

| 1        | MOV     | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; | Initialize in-page EA[15:0] pointer   |  |

|          | TBLWTL  | WO, [WO]                             | ; | Set base address of erase block       |  |

| 1        | DISI    | #5                                   | ; | Block all interrupts with priority <7 |  |

|          |         |                                      | ; | for next 5 instructions               |  |

| 1        | MOV     | #0x55, W0                            |   |                                       |  |

| 1        | MOV     | W0, NVMKEY                           | ; | Write the 55 key                      |  |

| 1        | MOV     | #0xAA, W1                            | ; |                                       |  |

| 1        | MOV     | W1, NVMKEY                           | ; | Write the AA key                      |  |

| 1        | BSET    | NVMCON, #WR                          | ; | Start the erase sequence              |  |

| 1        | NOP     |                                      | ; | Insert two NOPs after the erase       |  |

| ]        | NOP     |                                      | ; | command is asserted                   |  |

|          |         |                                      |   |                                       |  |

### 5.5.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOPx bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit (see Example 5-4).

### EXAMPLE 5-4: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

| ; Setup a p               | pointer to data Program Memory                             |    |                                                      |

|---------------------------|------------------------------------------------------------|----|------------------------------------------------------|

| MOV                       | <pre>#tblpage(PROG_ADDR), W0</pre>                         | ;  |                                                      |

| MOV                       | W0, TBLPAG                                                 | ;1 | Initialize PM Page Boundary SFR                      |

| MOV                       | <pre>#tbloffset(PROG_ADDR), W0</pre>                       | ;1 | initialize a register with program memory address    |

| MOV                       | #LOW_WORD_N, W2                                            | ;  |                                                      |

| MOV                       | #HIGH_BYTE_N, W3                                           | ;  |                                                      |

| TBLWTL                    | W2, [W0]                                                   | ;  | Write PM low word into program latch                 |

| TBLWTH                    | W3, [W0++]                                                 | ;  | Write PM high byte into program latch                |

| ; Setup NVN<br>MOV<br>MOV | 4CON for programming one word<br>#0x4003, W0<br>W0, NVMCON | ;  | data Program Memory<br>Set NVMOP bits to 0011        |

| DISI                      | #5                                                         | ;  | Disable interrupts while the KEY sequence is written |

| MOV                       | #0x55, W0                                                  | ;  | Write the key sequence                               |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| MOV                       | #0xAA, W0                                                  |    |                                                      |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| BSET                      | NVMCON, #WR                                                | ;  | Start the write cycle                                |

| NOP                       |                                                            | ;  | 2 NOPs required after setting WR                     |

| NOP                       |                                                            | ;  |                                                      |

|                           |                                                            |    |                                                      |

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device has been in Idle mode

- 0 = Device has not been in Idle mode

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred (note that BOR is also set after a Power-on Reset)

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

#### TABLE 6-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

### REGISTER 7-1: SR: ALU STATUS REGISTER (IN CPU)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0             |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   |     |     |     | —   | _   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0                 | R/W-0                 | R/W-0                 | R-0               | R/W-0            | R/W-0             | R/W-0            | R/W-0            |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

- 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: See Register 3-1 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

- **2:** The IPLx bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### REGISTER 7-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0                 | U-0                | U-0 | U-0   |

|--------|-----|-----|-----|---------------------|--------------------|-----|-------|

|        | _   | —   | —   |                     | —                  | _   | —     |

| bit 15 |     |     |     |                     |                    |     | bit 8 |

|        |     |     |     |                     |                    |     |       |

| U-0    | U-0 | U-0 | U-0 | R/C-0               | R/W-0              | U-0 | U-0   |

| —      | —   | —   | —   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —   | —     |

| bit 7  |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: See Register 3-2 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0: bits (SR<7:5>) to form the CPU Interrupt priority Level.

bit 3

| U-0          | U-0           | R/W-0                             | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------|---------------|-----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| _            | —             | AD1IF                             | U1TXIF           | U1RXIF            | SPI1IF          | SPF1IF          | T3IF   |

| bit 15       |               |                                   | •                |                   |                 | ·               | bit 8  |

| R/W-0        | R/W-0         | R/W-0                             | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| T2IF         | OC2IF         | IC2IF                             | _                | T1IF              | OC1IF           | IC1IF           | INTOIF |

| bit 7        | 002li         | 10211                             |                  |                   | 00111           | 10111           | bit    |

| Legend:      |               |                                   |                  |                   |                 |                 |        |

| R = Readab   | le bit        | W = Writable                      | bit              | U = Unimplem      | nented bit. rea | d as '0'        |        |

| -n = Value a | t POR         | '1' = Bit is set                  |                  | '0' = Bit is clea |                 | x = Bit is unkn | iown   |

|              |               |                                   | ·                |                   |                 |                 |        |

| bit 15-14    | Unimpleme     | nted: Read as '                   | 0'               |                   |                 |                 |        |

| bit 13       | AD1IF: A/D    | Conversion Cor                    | nplete Interrup  | t Flag Status bit |                 |                 |        |

|              | 1 = Interrupt | request has oc<br>request has no  | curred           | U                 |                 |                 |        |

| bit 12       | •             | RT1 Transmitte                    |                  | Status bit        |                 |                 |        |

|              | 1 = Interrupt | request has oc                    | curred           |                   |                 |                 |        |

| L:1 4 4      | -             | request has no                    |                  |                   |                 |                 |        |

| oit 11       |               | RT1 Receiver li<br>request has oc |                  |                   |                 |                 |        |

|              |               | request has no                    |                  |                   |                 |                 |        |

| bit 10       | -             | 1 Event Interrup                  |                  | it                |                 |                 |        |

|              | 1 = Interrupt | request has oc<br>request has no  | curred           |                   |                 |                 |        |

| bit 9        |               | 1 Fault Interrup                  |                  | it                |                 |                 |        |

| bit 0        |               | request has oc                    | •                | it i              |                 |                 |        |

|              | •             | request has no                    |                  |                   |                 |                 |        |

| bit 8        | T3IF: Timer3  | B Interrupt Flag                  | Status bit       |                   |                 |                 |        |

|              |               | request has oc<br>request has no  |                  |                   |                 |                 |        |

| bit 7        | T2IF: Timer2  | 2 Interrupt Flag                  | Status bit       |                   |                 |                 |        |

|              | •             | request has oc                    |                  |                   |                 |                 |        |

| hit C        | •             | request has no                    |                  | nt Flag Status k  | .:+             |                 |        |

| bit 6        | -             | out Compare Ch<br>request has oc  |                  | pi riag Status i  | JIL             |                 |        |

|              | •             | request has no                    |                  |                   |                 |                 |        |

| bit 5        | IC2IF: Input  | Capture Chann                     | el 2 Interrupt F | lag Status bit    |                 |                 |        |

|              | •             | request has oc<br>request has no  |                  |                   |                 |                 |        |

| bit 4        | -             | nted: Read as '                   |                  |                   |                 |                 |        |

| bit 3        | -             | Interrupt Flag                    |                  |                   |                 |                 |        |

|              |               | request has oc                    |                  |                   |                 |                 |        |

|              |               | request has no                    |                  |                   |                 |                 |        |

| bit 2        | -             | out Compare Ch                    |                  | pt Flag Status b  | pit             |                 |        |

|              |               | request has oc                    |                  |                   |                 |                 |        |

|              |               | request has no                    |                  |                   |                 |                 |        |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0              | U-0                                | R/W-0                             | U-0                     | U-0                        | U-0            | U-0                  | U-0 |  |  |

|--------------------|------------------------------------|-----------------------------------|-------------------------|----------------------------|----------------|----------------------|-----|--|--|

| TON <sup>(1)</sup> | —                                  | TSIDL <sup>(1)</sup>              |                         | _                          | —              | _                    | —   |  |  |

| bit 15             |                                    |                                   |                         |                            |                |                      | bit |  |  |

|                    |                                    |                                   |                         |                            |                |                      |     |  |  |

| U-0                | R/W-0                              | R/W-0                             | R/W-0                   | U-0                        | U-0            | R/W-0                | U-0 |  |  |

| —                  | TGATE <sup>(1)</sup>               | TCKPS1 <sup>(1)</sup>             | TCKPS0 <sup>(1)</sup>   | —                          | —              | TCS <sup>(1,2)</sup> | —   |  |  |

| bit 7              |                                    |                                   |                         |                            |                |                      | bit |  |  |

| Legend:            |                                    |                                   |                         |                            |                |                      |     |  |  |

| R = Readable       | e bit                              | W = Writable                      | bit                     | U = Unimplem               | ented bit, rea | d as '0'             |     |  |  |

| -n = Value at      | POR                                | '1' = Bit is set                  |                         | '0' = Bit is clea          | red            | x = Bit is unkno     | own |  |  |

|                    |                                    |                                   |                         |                            |                |                      |     |  |  |

| bit 15             | TON: Timery                        | On bit <sup>(1)</sup>             |                         |                            |                |                      |     |  |  |

|                    | 1 = Starts 16                      | -bit Timery                       |                         |                            |                |                      |     |  |  |

|                    | 0 = Stops 16                       | -bit Timery                       |                         |                            |                |                      |     |  |  |

| bit 14             | Unimplemen                         | ted: Read as '0                   | )'                      |                            |                |                      |     |  |  |

| bit 13             | TSIDL: Time                        | ry Stop in Idle N                 | lode bit <sup>(1)</sup> |                            |                |                      |     |  |  |

|                    |                                    |                                   |                         | evice enters Idle          | e mode         |                      |     |  |  |

|                    | 0 = Continue                       | s module opera                    | tion in Idle mod        | de                         |                |                      |     |  |  |

| bit 12-7           |                                    | ted: Read as '0                   |                         |                            |                |                      |     |  |  |

| bit 6              | TGATE: Time                        | ery Gated Time                    | Accumulation I          | Enable bit <sup>(1)</sup>  |                |                      |     |  |  |

|                    | When TCS =                         |                                   |                         |                            |                |                      |     |  |  |

|                    | -                                  | his bit is ignored.               |                         |                            |                |                      |     |  |  |

|                    | <u>When TCS =</u><br>1 = Cated tir | <u>_0:</u><br>ne accumulatio      | a is onabled            |                            |                |                      |     |  |  |

|                    |                                    | ne accumulation                   |                         |                            |                |                      |     |  |  |

| bit 5-4            |                                    | : Timery Input (                  |                         | Select bits <sup>(1)</sup> |                |                      |     |  |  |

|                    | 11 <b>= 1:256</b>                  | 5 1                               |                         |                            |                |                      |     |  |  |

|                    | 10 <b>= 1:64</b>                   |                                   |                         |                            |                |                      |     |  |  |

|                    | 01 = 1:8                           |                                   |                         |                            |                |                      |     |  |  |

|                    | 00 = 1:1                           |                                   |                         |                            |                |                      |     |  |  |

| bit 3-2            | •                                  | ted: Read as '0                   |                         |                            |                |                      |     |  |  |

| bit 1              |                                    | Clock Source S                    |                         |                            |                |                      |     |  |  |

|                    |                                    | clock from pin,<br>clock (Fosc/2) | TyCK (on the r          | ising edge)                |                |                      |     |  |  |

|                    | Unimplemen                         |                                   |                         |                            |                |                      |     |  |  |

operation; all timer functions are set through T2CON and T4CON.

2: If TCS = 1, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

### REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends a NACK during Acknowledge<br>0 = Sends an ACK during Acknowledge                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at the end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)<br>1 = Enables Receive mode for I <sup>2</sup> C. Hardware is clear at the end of eighth bit of master receive data byte.<br>0 = Receive sequence is not in progress                                                                                                                 |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                   |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                                          |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                               |

Note 1: In Slave mode, the module will not automatically clock stretch after receiving the address byte.

### REGISTER 20-2: CRCXOR: CRC XOR POLYNOMIAL REGISTER

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0 | R/W-0 |

|------------------------------------|-------|-----------------------------------------|--------------|------------------|----------|-------|-------|

| X15                                | X14   | X13                                     | X12          | X11              | X10      | X9    | X8    |

| bit 15                             |       |                                         |              |                  | •        |       | bit 8 |

|                                    |       |                                         |              |                  |          |       |       |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0 | U-0   |

| X7                                 | X6    | X5                                      | X4           | X3               | X2       | X1    | —     |

| bit 7                              |       |                                         |              |                  |          |       | bit 0 |

|                                    |       |                                         |              |                  |          |       |       |

| Legend:                            |       |                                         |              |                  |          |       |       |

| R = Readable bit W = Writable bit  |       | bit                                     | U = Unimplem | nented bit, read | d as '0' |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |              |                  | nown     |       |       |

bit 15-1 X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

### EQUATION 21-1: A/D CONVERSION CLOCK PERIOD<sup>(1)</sup>

$$TAD = TCY \bullet (ADCS + 1)$$

$$ADCS = \frac{TAD}{TCY} - 1$$

**Note 1:** Based on TCY = 2 \* TOSC; Doze mode and PLL are disabled.

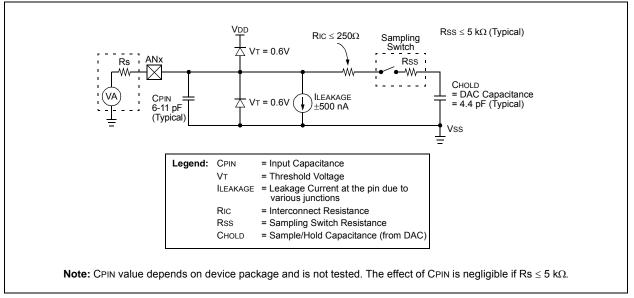

### FIGURE 21-2: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

### REGISTER 24-4: DEVREV: DEVICE REVISION REGISTER

| U      | U      | U | U | U | U    | U    | U      |

|--------|--------|---|---|---|------|------|--------|

|        | —      | — | — | — | —    | —    | —      |

| bit 23 |        |   |   |   |      |      | bit 16 |

|        |        |   |   |   |      |      |        |

| U      | U      | U | U | U | U    | U    | R      |

| —      | —      | — | — | — |      | —    | MAJRV2 |

| bit 15 |        |   |   |   |      |      | bit 8  |

|        |        |   |   |   |      |      |        |

| R      | R      | U | U | U | R    | R    | R      |

| MAJRV1 | MAJRV0 | — | — | — | DOT2 | DOT1 | DOT0   |

| bit 7  |        |   |   |   |      |      | bit 0  |

|        |        |   |   |   |      |      |        |

| Legend: R = Read-only bit | U = Unimplemented bit |  |

|---------------------------|-----------------------|--|

|---------------------------|-----------------------|--|

- bit 23-9 Unimplemented: Read as '0'

- bit 8-6 MAJRV<2:0>: Major Revision Identifier bits

- bit 5-3 Unimplemented: Read as '0'

- bit 2-0 DOT<2:0>: Minor Revision Identifier bits

### 27.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24FJ64GA004 family AC characteristics and timing parameters.

### TABLE 27-13: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions:     | 2.0V to 3.6V (unless otherwise stated)                |

|--------------------|------------------------------------|-------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature              | $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |

| AC CHARACTERISTICS |                                    | $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended  |

|                    | Operating voltage VDD range as des | cribed in Section 27.1 "DC Characteristics".          |

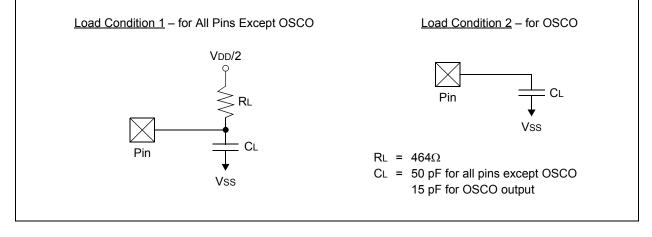

### FIGURE 27-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSCO/CLKO Pin         | _   |                    | 15  | pF    | In XT and HS modes when<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | —   | —                  | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     | —                  | 400 | pF    | In I <sup>2</sup> C™ mode                                          |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

NOTES:

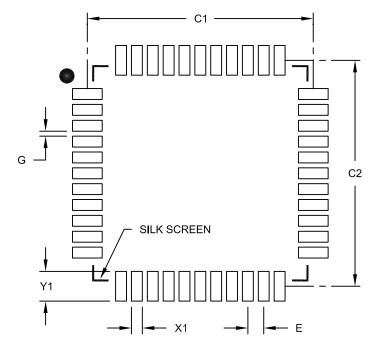

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units            | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

| Dimensi                  | Dimension Limits |             | NOM      | MAX  |  |

| Contact Pitch            | E                |             | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1               |             | 11.40    |      |  |

| Contact Pad Spacing      | C2               |             | 11.40    |      |  |

| Contact Pad Width (X44)  | X1               |             |          | 0.55 |  |

| Contact Pad Length (X44) | Y1               |             |          | 1.50 |  |

| Distance Between Pads    | G                | 0.25        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

### INDEX

| Α                                           |  |

|---------------------------------------------|--|

| A/D Converter                               |  |

| Analog Input Model                          |  |

| Transfer Function                           |  |

| AC Characteristics                          |  |

| A/D Conversion Requirements                 |  |

| A/D Specifications                          |  |

| CLKO and I/O Requirements                   |  |

| External Clock Requirements                 |  |

| Internal RC Accuracy                        |  |

| Internal RC Oscillator Specifications       |  |

| PLL Clock Specifications                    |  |

| Temperature and Voltage Specifications      |  |

| Additional Guidance for Family Applications |  |

| Assembler                                   |  |

| MPASM Assembler                             |  |

### В

| Block Diagrams                                |   |

|-----------------------------------------------|---|

| 10-Bit High-Speed A/D Converter               | 4 |

| 16-Bit Timer1 125                             | 5 |

| Accessing Program Memory with                 |   |

| Table Instructions45                          | 5 |

| Addressable Parallel Slave Port Example 174   | 4 |

| Addressing for Table Registers47              | 7 |

| CALL Stack Frame43                            | 3 |

| Comparator I/O Operating Modes203             | 3 |

| Comparator Voltage Reference 207              | 7 |

| CPU Programmer's Model25                      |   |

| CRC Module189                                 |   |

| CRC Shift Engine190                           | С |

| Data Access from Program Space                |   |

| Address Generation 44                         |   |

| I <sup>2</sup> C Module 152                   | 2 |

| Input Capture x133                            |   |

| LCD Control Example, Byte Mode 176            |   |

| Legacy Parallel Slave Port Example174         |   |

| Load Conditions for Timing Specifications244  |   |

| MCLR Pin Connections18                        |   |

| On-Chip Regulator Connections 215             |   |

| Output Compare x138                           | 3 |

| Parallel EEPROM (Up to 11-Bit Address,        |   |

| 16-Bit Data)176                               | 3 |

| Parallel EEPROM (Up to 11-Bit Address,        |   |

| 8-Bit Data)176                                |   |

| Parallel Master Port (PMP) Module Overview    |   |

| PIC24F CPU Core                               |   |

| PIC24FJ64GA004 Family (General)10             | ) |

| PMP 8-Bit Multiplexed Addressing and          | _ |

| Data Application176                           |   |

| PMP Master Mode, Demultiplexed Addressing 174 | 1 |

| PMP Master Mode, Fully                        | _ |

| Multiplexed Addressing                        | С |

| PMP Master Mode, Partially                    | _ |

| Multiplexed Addressing                        |   |

| PMP Multiplexed Addressing Application        | C |

| PMP Partially Multiplexed                     | _ |

| Addressing Application                        |   |

| PSV Operation                                 |   |

| Real-Time Clock and Calendar (RTCC) 177       | ſ |

| Recommended Minimum Connections             | 17  |

|---------------------------------------------|-----|

| Reset System                                | 53  |

| Shared I/O Port Structure                   | 105 |

| Simplified UARTx Module                     | 159 |

| SPIx Master/Frame Master Connection         | 149 |

| SPIx Master/Frame Slave Connection          | 149 |

| SPIx Master/Slave Connection                |     |

| (Enhanced Buffer Mode)                      | 148 |

| SPIx Master/Slave Connection                |     |

| (Standard Mode)                             | 148 |

| SPIx Module (Enhanced Mode)                 | 143 |

| SPIx Module (Standard Mode)                 | 142 |

| SPIx Slave/Frame Master Connection          | 149 |

| SPIx Slave/Frame Slave Connection           | 149 |

| Suggested Placement of Oscillator Circuit   | 21  |

| System Clock                                | 95  |

| Timer2 and Timer4 (16-Bit Synchronous Mode) | 129 |

| Timer2/3 and Timer4/5 (32-Bit Mode)         | 128 |

| Timer3 and Timer5 (16-Bit Synchronous Mode) | 129 |

| Watchdog Timer (WDT)                        | 217 |

|                                             |     |

### С

| C Compilers                          |     |

|--------------------------------------|-----|

| MPLAB C18                            | 220 |

| Code Examples                        |     |

| Basic Clock Switching Example        | 101 |

| Configuring UART1 Input and Output   |     |

| Functions (PPS)                      | 110 |

| Erasing a Program Memory Block       | 50  |

| I/O Port Read/Write                  | 106 |

| Initiating a Programming Sequence    | 51  |

| Loading the Write Buffers            |     |

| Setting the RTCWREN Bit              |     |

| Single-Word Flash Programming        | 52  |

| Code Protection                      | 218 |

| Comparator Voltage Reference         |     |

| Configuring                          | 207 |

| Configuration Bits                   | 209 |

| Core Features                        | 7   |

| CPU                                  |     |

| Arithmetic Logic Unit (ALU)          | 27  |

| Control Registers                    | 26  |

| Core Registers                       | 25  |

| Programmer's Model                   | 23  |

| CRC                                  |     |

| Operation in Power Save Modes        | 190 |

| Setup Example                        | 189 |

| User Interface                       | 190 |

| Customer Change Notification Service | 273 |

| Customer Notification Service        | 273 |

| Customer Support                     | 273 |

| р                                    |     |

| D               |    |

|-----------------|----|

| Data Memory     |    |

| Address Space   | 31 |

| Memory Map      | 31 |

| Near Data Space | 32 |

| Organization    | 32 |

| SFR Space       | 32 |

| Software Stack  | 43 |

|                 |    |