#### Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga002-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                               | Pin Number    |                    |     |                  |                                             |  |  |  |  |

|----------|-------------------------------|---------------|--------------------|-----|------------------|---------------------------------------------|--|--|--|--|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer  | Description                                 |  |  |  |  |

| RP0      | 4                             | 1             | 21                 | I/O | ST               | Remappable Peripheral.                      |  |  |  |  |

| RP1      | 5                             | 2             | 22                 | I/O | ST               | ]                                           |  |  |  |  |

| RP2      | 6                             | 3             | 23                 | I/O | ST               |                                             |  |  |  |  |

| RP3      | 7                             | 4             | 24                 | I/O | ST               |                                             |  |  |  |  |

| RP4      | 11                            | 8             | 33                 | I/O | ST               |                                             |  |  |  |  |

| RP5      | 14                            | 11            | 41                 | I/O | ST               |                                             |  |  |  |  |

| RP6      | 15                            | 12            | 42                 | I/O | ST               |                                             |  |  |  |  |

| RP7      | 16                            | 13            | 43                 | I/O | ST               |                                             |  |  |  |  |

| RP8      | 17                            | 14            | 44                 | I/O | ST               |                                             |  |  |  |  |

| RP9      | 18                            | 15            | 1                  | I/O | ST               |                                             |  |  |  |  |

| RP10     | 21                            | 18            | 8                  | I/O | ST               |                                             |  |  |  |  |

| RP11     | 22                            | 19            | 9                  | I/O | ST               |                                             |  |  |  |  |

| RP12     | 23                            | 20            | 10                 | I/O | ST               |                                             |  |  |  |  |

| RP13     | 24                            | 21            | 11                 | I/O | ST               |                                             |  |  |  |  |

| RP14     | 25                            | 22            | 14                 | I/O | ST               |                                             |  |  |  |  |

| RP15     | 26                            | 23            | 15                 | I/O | ST               |                                             |  |  |  |  |

| RP16     | _                             |               | 25                 | I/O | ST               |                                             |  |  |  |  |

| RP17     | _                             |               | 26                 | I/O | ST               |                                             |  |  |  |  |

| RP18     | _                             | _             | 27                 | I/O | ST               |                                             |  |  |  |  |

| RP19     | _                             | _             | 36                 | I/O | ST               |                                             |  |  |  |  |

| RP20     | _                             |               | 37                 | I/O | ST               |                                             |  |  |  |  |

| RP21     | _                             | _             | 38                 | I/O | ST               |                                             |  |  |  |  |

| RP22     | —                             |               | 2                  | I/O | ST               |                                             |  |  |  |  |

| RP23     | —                             |               | 3                  | I/O | ST               |                                             |  |  |  |  |

| RP24     | —                             | _             | 4                  | I/O | ST               |                                             |  |  |  |  |

| RP25     | —                             |               | 5                  | I/O | ST               |                                             |  |  |  |  |

| RTCC     | 25                            | 22            | 14                 | 0   |                  | Real-Time Clock Alarm Output.               |  |  |  |  |

| SCL1     | 17                            | 14            | 44                 | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output. |  |  |  |  |

| SCL2     | 7                             | 4             | 24                 | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output. |  |  |  |  |

| SDA1     | 18                            | 15            | 1                  | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                     |  |  |  |  |

| SDA2     | 6                             | 3             | 23                 | I/O | l <sup>2</sup> C | I2C2 Data Input/Output.                     |  |  |  |  |

| SOSCI    | 11                            | 8             | 33                 | I   | ANA              | Secondary Oscillator/Timer1 Clock Input.    |  |  |  |  |

| SOSCO    | 12                            | 9             | 34                 | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.   |  |  |  |  |

| Legend:  | TTL = TTL inp                 | ut buffer     | •                  | •   | ST = 5           | Schmitt Trigger input buffer                |  |  |  |  |

**Legend:** TTL = TTL input buffer

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

ANA = Analog level input/output  $I^2 C^{TM} = I^2 C/SMBu$ **Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

## TABLE 4-10: UART REGISTER MAP

|              | -    | -        |        |          |        |        |        |        |            |               |            |       |       |       |        |        |       |               |

|--------------|------|----------|--------|----------|--------|--------|--------|--------|------------|---------------|------------|-------|-------|-------|--------|--------|-------|---------------|

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7         | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE       | 0220 | UARTEN   |        | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0       | WAKE          | LPBACK     | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT       | URXISEL1      | URXISEL0   | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | _        | _      | —        | —      | —      | _      | _      | UTX8       | UTX7          | UTX6       | UTX5  | UTX4  | UTX3  | UTX2   | UTX1   | UTX0  | 0000          |

| U1RXREG      | 0226 | _        | _      | _        | _      | _      | _      | _      | URX8       | URX7          | URX6       | URX5  | URX4  | URX3  | URX2   | URX1   | URX0  | 0000          |

| U1BRG        | 0228 |          |        |          |        |        |        | Baud R | ate Genera | tor Prescale  | r Register |       |       |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0       | WAKE          | LPBACK     | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT       | URXISEL1      | URXISEL0   | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _        | _      | _        | _      | _      | _      | _      | UTX8       | UTX7          | UTX6       | UTX5  | UTX4  | UTX3  | UTX2   | UTX1   | UTX0  | 0000          |

| U2RXREG      | 0236 | _        | _      | —        | —      | —      | _      | _      | URX8       | URX7          | URX6       | URX5  | URX4  | URX3  | URX2   | URX1   | URX0  | 0000          |

| U2BRG        | 0238 |          |        |          |        |        |        | Bai    | ud Rate Ge | enerator Pres | caler      |       |       |       |        |        |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-11: SPI REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8        | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|---------|--------|--------|---------|---------|--------------|------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN  | —      | SPISIDL | —      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 | -      | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN  | SPIFSD | SPIFPOL | -      | _      | _       | _       | _            | _          | _      | _      | -      | -      | _      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 |        |        |         |        |        |         | SP      | 11 Transmit/ | Receive Bu | ffer   |        |        |        |        |        |        | 0000          |

| SPI2STAT     | 0260 | SPIEN  | _      | SPISIDL | -      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1     | 0262 | -      | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2     | 0264 | FRMEN  | SPIFSD | SPIFPOL | -      | _      | _       | _       | _            | _          | _      | _      | -      | -      | _      | SPIFE  | SPIBEN | 0000          |

| SPI2BUF      | 0268 |        |        |         |        |        |         | SP      | 12 Transmit/ | Receive Bu | ffer   |        |        |        |        |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

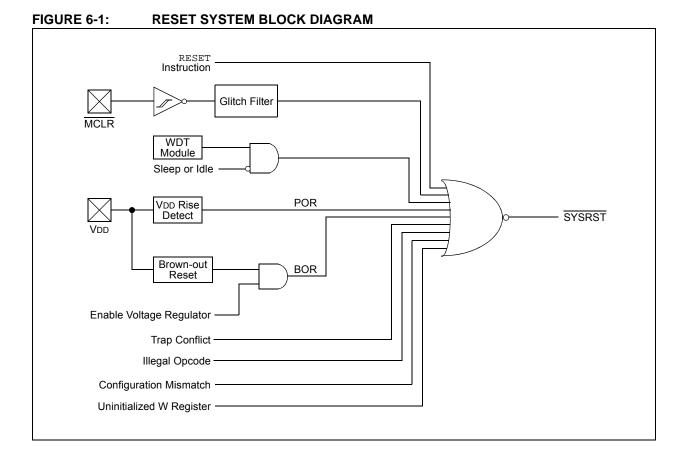

## 6.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, **"Reset"** (DS39712).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- · UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

NOTES:

|                           | Vector |             | AIVT    | Inte     | errupt Bit Loca | tions        |

|---------------------------|--------|-------------|---------|----------|-----------------|--------------|

| Interrupt Source          | Number | IVT Address | Address | Flag     | Enable          | Priority     |

| ADC1 Conversion Done      | 13     | 00002Eh     | 00012Eh | IFS0<13> | IEC0<13>        | IPC3<6:4>    |

| Comparator Event          | 18     | 000038h     | 000138h | IFS1<2>  | IEC1<2>         | IPC4<10:8>   |

| CRC Generator             | 67     | 00009Ah     | 00019Ah | IFS4<3>  | IEC4<3>         | IPC16<14:12> |

| External Interrupt 0      | 0      | 000014h     | 000114h | IFS0<0>  | IEC0<0>         | IPC0<2:0>    |

| External Interrupt 1      | 20     | 00003Ch     | 00013Ch | IFS1<4>  | IEC1<4>         | IPC5<2:0>    |

| External Interrupt 2      | 29     | 00004Eh     | 00014Eh | IFS1<13> | IEC1<13>        | IPC7<6:4>    |

| I2C1 Master Event         | 17     | 000036h     | 000136h | IFS1<1>  | IEC1<1>         | IPC4<6:4>    |

| I2C1 Slave Event          | 16     | 000034h     | 000034h | IFS1<0>  | IEC1<0>         | IPC4<2:0>    |

| I2C2 Master Event         | 50     | 000078h     | 000178h | IFS3<2>  | IEC3<2>         | IPC12<10:8>  |

| I2C2 Slave Event          | 49     | 000076h     | 000176h | IFS3<1>  | IEC3<1>         | IPC12<6:4>   |

| Input Capture 1           | 1      | 000016h     | 000116h | IFS0<1>  | IEC0<1>         | IPC0<6:4>    |

| Input Capture 2           | 5      | 00001Eh     | 00011Eh | IFS0<5>  | IEC0<5>         | IPC1<6:4>    |

| Input Capture 3           | 37     | 00005Eh     | 00015Eh | IFS2<5>  | IEC2<5>         | IPC9<6:4>    |

| Input Capture 4           | 38     | 000060h     | 000160h | IFS2<6>  | IEC2<6>         | IPC9<10:8>   |

| Input Capture 5           | 39     | 000062h     | 000162h | IFS2<7>  | IEC2<7>         | IPC9<14:12>  |

| Input Change Notification | 19     | 00003Ah     | 00013Ah | IFS1<3>  | IEC1<3>         | IPC4<14:12>  |

| Output Compare 1          | 2      | 000018h     | 000118h | IFS0<2>  | IEC0<2>         | IPC0<10:8>   |

| Output Compare 2          | 6      | 000020h     | 000120h | IFS0<6>  | IEC0<6>         | IPC1<10:8>   |

| Output Compare 3          | 25     | 000046h     | 000146h | IFS1<9>  | IEC1<9>         | IPC6<6:4>    |

| Output Compare 4          | 26     | 000048h     | 000148h | IFS1<10> | IEC1<10>        | IPC6<10:8>   |

| Output Compare 5          | 41     | 000066h     | 000166h | IFS2<9>  | IEC2<9>         | IPC10<6:4>   |

| Parallel Master Port      | 45     | 00006Eh     | 00016Eh | IFS2<13> | IEC2<13>        | IPC11<6:4>   |

| Real-Time Clock/Calendar  | 62     | 000090h     | 000190h | IFS3<14> | IEC3<14>        | IPC15<10:8>  |

| SPI1 Error                | 9      | 000026h     | 000126h | IFS0<9>  | IEC0<9>         | IPC2<6:4>    |

| SPI1 Event                | 10     | 000028h     | 000128h | IFS0<10> | IEC0<10>        | IPC2<10:8>   |

| SPI2 Error                | 32     | 000054h     | 000154h | IFS2<0>  | IEC0<0>         | IPC8<2:0>    |

| SPI2 Event                | 33     | 000056h     | 000156h | IFS2<1>  | IEC2<1>         | IPC8<6:4>    |

| Timer1                    | 3      | 00001Ah     | 00011Ah | IFS0<3>  | IEC0<3>         | IPC0<14:12>  |

| Timer2                    | 7      | 000022h     | 000122h | IFS0<7>  | IEC0<7>         | IPC1<14:12>  |

| Timer3                    | 8      | 000024h     | 000124h | IFS0<8>  | IEC0<8>         | IPC2<2:0>    |

| Timer4                    | 27     | 00004Ah     | 00014Ah | IFS1<11> | IEC1<11>        | IPC6<14:12>  |

| Timer5                    | 28     | 00004Ch     | 00014Ch | IFS1<12> | IEC1<12>        | IPC7<2:0>    |

| UART1 Error               | 65     | 000096h     | 000196h | IFS4<1>  | IEC4<1>         | IPC16<6:4>   |

| UART1 Receiver            | 11     | 00002Ah     | 00012Ah | IFS0<11> | IEC0<11>        | IPC2<14:12>  |

| UART1 Transmitter         | 12     | 00002Ch     | 00012Ch | IFS0<12> | IEC0<12>        | IPC3<2:0>    |

| UART2 Error               | 66     | 000098h     | 000198h | IFS4<2>  | IEC4<2>         | IPC16<10:8>  |

| UART2 Receiver            | 30     | 000050h     | 000150h | IFS1<14> | IEC1<14>        | IPC7<10:8>   |

| UART2 Transmitter         | 31     | 000052h     | 000152h | IFS1<15> | IEC1<15>        | IPC7<14:12>  |

| Low-Voltage Detect (LVD)  | 72     | 0000A4h     | 000124h | IFS4<8>  | IEC4<8>         | IPC17<2:0>   |

TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7                   | CLKLOCK: Clock Selection Lock Enable bit                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | <u>If FSCM is enabled (FCKSM1 = 1):</u>                                                                                                                                                                                                                                                                                                                                           |

|                         | 1 = Clock and PLL selections are locked                                                                                                                                                                                                                                                                                                                                           |

|                         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit                                                                                                                                                                                                                                                                                          |

|                         | <u>If FSCM is disabled (FCKSM1 = 0):</u>                                                                                                                                                                                                                                                                                                                                          |

|                         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.                                                                                                                                                                                                                                                                                           |

| bit 6                   | IOLOCK: I/O Lock Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                        |

|                         | 1 = I/O lock is active                                                                                                                                                                                                                                                                                                                                                            |

|                         | 0 = I/O lock is not active                                                                                                                                                                                                                                                                                                                                                        |

| bit 5                   | LOCK: PLL Lock Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                          |

|                         | 1 = PLL module is in lock or PLL module start-up timer is satisfied                                                                                                                                                                                                                                                                                                               |

|                         | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled                                                                                                                                                                                                                                                                                                   |

|                         |                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 4                   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                        |

| bit 4<br>bit 3          | <b>CF:</b> Clock Fail Detect bit                                                                                                                                                                                                                                                                                                                                                  |

|                         | •                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | CF: Clock Fail Detect bit                                                                                                                                                                                                                                                                                                                                                         |

|                         | <b>CF:</b> Clock Fail Detect bit<br>1 = FSCM has detected a clock failure                                                                                                                                                                                                                                                                                                         |

| bit 3                   | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                                                                                                                                                                                                                                      |

| bit 3<br>bit 2          | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                  |

| bit 3<br>bit 2          | CF: Clock Fail Detect bit<br>1 = FSCM has detected a clock failure<br>0 = No clock failure has been detected<br>Unimplemented: Read as '0'<br>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                               |

| bit 3<br>bit 2          | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> <li>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit</li> <li>1 = Enables Secondary Oscillator</li> </ul>                                                                                         |

| bit 3<br>bit 2<br>bit 1 | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> <li>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit</li> <li>1 = Enables Secondary Oscillator</li> <li>0 = Disables Secondary Oscillator</li> </ul>                                              |

| bit 3<br>bit 2<br>bit 1 | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> <li>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit</li> <li>1 = Enables Secondary Oscillator</li> <li>0 = Disables Secondary Oscillator</li> <li>OSWEN: Oscillator Switch Enable bit</li> </ul> |

Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | —   | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |     |     |        |        |        |        | bit 0  |

|        |     |     |        |        |        |        |        |

|        |     |     |        |        |        |        |        |

## REGISTER 10-11: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 12-8  | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                     |

| bit 4-0   | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits    |

## REGISTER 10-12: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0                                | U-0 | U-0   | U-0                                                                                                      | U-0                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------------------------|-----|-------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| _                                  | —   | —     | —                                                                                                        | —                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                    |     |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                    |     |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| U-0                                | U-0 | R/W-1 | R/W-1                                                                                                    | R/W-1                                                                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| _                                  | —   | SS1R4 | SS1R3                                                                                                    | SS1R2                                                                                                                                                                                                         | SS1R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SS1R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                    |     |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                    |     |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                    |     |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| R = Readable bit W = Writable bit  |     |       | U = Unimplemented bit, read as '0'                                                                       |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| -n = Value at POR '1' = Bit is set |     |       | '0' = Bit is clea                                                                                        | ared                                                                                                                                                                                                          | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                    |     |       | U-0         U-0         R/W-1           —         —         SS1R4           bit         W = Writable bit | —         —         —         —           U-0         U-0         R/W-1         R/W-1           —         —         —         SS1R4         SS1R3           bit         W = Writable bit         U = Unimplem | —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         Image: Marce of the field of th | —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         — |  |  |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the Corresponding RPn Pin bits

## REGISTER 10-13: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| _      | —   | —   | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 12-8  | SCK2R<4:0>: Assign SPI2 Clock Input (SCK2IN) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                     |

| bit 4-0   | SDI2R<4:0>: Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits    |

## REGISTER 10-14: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0             | U-0                                                           | U-0              | U-0   | U-0                                     | U-0   | U-0   | U-0   |

|-----------------|---------------------------------------------------------------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 | —                                                             | —                | —     | —                                       | —     | —     | —     |

| bit 15          |                                                               |                  |       | bit 8                                   |       |       |       |

|                 |                                                               |                  |       |                                         |       |       |       |

| U-0             | U-0                                                           | U-0              | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |

| _               | —                                                             | —                | SS2R4 | SS2R3                                   | SS2R2 | SS2R1 | SS2R0 |

| bit 7           |                                                               |                  |       |                                         |       | bit 0 |       |

|                 |                                                               |                  |       |                                         |       |       |       |

| Legend:         |                                                               |                  |       |                                         |       |       |       |

| R = Readable    | dable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                                         |       |       |       |

| -n = Value at I | POR                                                           | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

|                 |                                                               |                  |       |                                         |       |       |       |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS2R<4:0>: Assign SPI2 Slave Select Input (SS2IN) to the Corresponding RPn Pin bits

| U-0                                | U-0                               | U-0             | R/W-0                                   | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |

|------------------------------------|-----------------------------------|-----------------|-----------------------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|

| _                                  |                                   | _               | RP25R4 <sup>(1)</sup>                   | RP25R3 <sup>(1)</sup>              | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> |

| bit 15                             |                                   |                 |                                         |                                    |                       |                       | bit 8                 |

|                                    |                                   |                 |                                         |                                    |                       |                       |                       |

| U-0                                | U-0                               | U-0             | R/W-0                                   | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |

| _                                  |                                   | —               | RP24R4 <sup>(1)</sup>                   | RP24R3 <sup>(1)</sup>              | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> |

| bit 7                              |                                   |                 | •                                       | •                                  |                       |                       | bit 0                 |

|                                    |                                   |                 |                                         |                                    |                       |                       |                       |

| Legend:                            |                                   |                 |                                         |                                    |                       |                       |                       |

| R = Readable                       | R = Readable bit W = Writable bit |                 | bit                                     | U = Unimplemented bit, read as '0' |                       |                       |                       |

| -n = Value at POR '1' = Bit is set |                                   |                 | '0' = Bit is cleared x = Bit is unknown |                                    |                       | iown                  |                       |

|                                    |                                   |                 |                                         |                                    |                       |                       |                       |

| bit 15-13                          | Unimplemen                        | ted: Read as '@ | י'                                      |                                    |                       |                       |                       |

## REGISTER 10-27: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

bit 15-13 Unimplemented: Read as '0

RP25R<4:0>: Peripheral Output Function is Assigned to RP25 Output Pin bits<sup>(1)</sup> bit 12-8 (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

RP24R<4:0>: Peripheral Output Function is Assigned to RP24 Output Pin bits<sup>(1)</sup> bit 4-0 (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

| R/W-0         | U-0                                                                                                          | R/W-0                              | U-0                       | U-0                | U-0              | U-0                | U-0    |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------|--------------------|------------------|--------------------|--------|--|--|--|

| TON           |                                                                                                              | TSIDL                              |                           |                    |                  | _                  | _      |  |  |  |

| bit 15        |                                                                                                              |                                    |                           |                    |                  |                    | bit 8  |  |  |  |

|               |                                                                                                              |                                    |                           |                    |                  |                    |        |  |  |  |