#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga002t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          | I                             | Pin Number    |                    |     |                 |                                                                      |

|----------|-------------------------------|---------------|--------------------|-----|-----------------|----------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                          |

| T1CK     | 12                            | 9             | 34                 | Ι   | ST              | Timer1 Clock.                                                        |

| TCK      | 17                            | 14            | 13                 | -   | ST              | JTAG Test Clock Input.                                               |

| TDI      | 21                            | 18            | 35                 | -   | ST              | JTAG Test Data Input.                                                |

| TDO      | 18                            | 15            | 32                 | 0   | _               | JTAG Test Data Output.                                               |

| TMS      | 22                            | 19            | 12                 | -   | ST              | JTAG Test Mode Select Input.                                         |

| Vdd      | 13, 28                        | 10, 25        | 28, 40             | Р   | _               | Positive Supply for Peripheral Digital Logic and I/O Pins.           |

| VDDCAP   | 20                            | 17            | 7                  | Р   | _               | External Filter Capacitor Connection (regulator enabled).            |

| VDDCORE  | 20                            | 17            | 7                  | Р   | —               | Positive Supply for Microcontroller Core Logic (regulator disabled). |

| VREF-    | 3                             | 28            | 20                 | -   | ANA             | A/D and Comparator Reference Voltage (low) Input.                    |

| VREF+    | 2                             | 27            | 19                 | Ι   | ANA             | A/D and Comparator Reference Voltage (high) Input.                   |

| Vss      | 8, 27                         | 5, 24         | 29, 39             | Р   | —               | Ground Reference for Logic and I/O Pins.                             |

| Legend:  | TTL = TTL inp                 | ut buffer     |                    |     | ST = 5          | Schmitt Trigger input buffer                                         |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffe  $I^2C^{TM} = I^2C/SMBus$  input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

| U-0          | R/W-0        | U-0              | U-0            | U-0               | U-0              | U-0              | U-0   |

|--------------|--------------|------------------|----------------|-------------------|------------------|------------------|-------|

| _            | RTCIF        | _                | _              | _                 |                  | —                | _     |

| bit 15       |              |                  |                |                   |                  |                  | bit 8 |

|              |              |                  |                |                   |                  |                  |       |

| U-0          | U-0          | U-0              | U-0            | U-0               | R/W-0            | R/W-0            | U-0   |

|              |              |                  | —              |                   | MI2C2IF          | SI2C2IF          |       |

| bit 7        |              |                  |                |                   |                  |                  | bit 0 |

|              |              |                  |                |                   |                  |                  |       |

| Legend:      |              |                  |                |                   |                  |                  |       |

| R = Readat   | ole bit      | W = Writable     | bit            | U = Unimplem      | nented bit, read | l as '0'         |       |

| -n = Value a | at POR       | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkno | own   |

|              |              |                  |                |                   |                  |                  |       |

| bit 15       | Unimplemen   | ted: Read as '   | )'             |                   |                  |                  |       |

| bit 14       | RTCIF: Real- | Time Clock/Cal   | endar Interrup | t Flag Status bi  | t                |                  |       |

|              |              | request has occ  |                |                   |                  |                  |       |

|              |              | request has not  |                |                   |                  |                  |       |

| bit 13-3     | Unimplemen   | ted: Read as 'o  | )'             |                   |                  |                  |       |

| bit 2        |              | ster I2C2 Event  |                | Status bit        |                  |                  |       |

|              | •            | request has occ  |                |                   |                  |                  |       |

|              | -            | request has not  |                |                   |                  |                  |       |

| bit 1        |              | ve I2C2 Event I  |                | Status bit        |                  |                  |       |

|              |              | request has occ  |                |                   |                  |                  |       |

| 1.11.0       | -            | request has not  |                |                   |                  |                  |       |

| bit 0        | Unimplemen   | ted: Read as '0  | ).             |                   |                  |                  |       |

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0               | U-0                                                | U-0                                                                         | U-0                                | U-0                                    | U-0              | U-0      | R/W-0 |

|-------------------|----------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------|----------------------------------------|------------------|----------|-------|

| _                 | —                                                  | —                                                                           |                                    | —                                      | —                |          | LVDIF |

| bit 15            |                                                    |                                                                             |                                    |                                        |                  |          | bit 8 |

|                   |                                                    |                                                                             |                                    |                                        |                  |          |       |

| U-0               | U-0                                                | U-0                                                                         | U-0                                | R/W-0                                  | R/W-0            | R/W-0    | U-0   |

|                   |                                                    | —                                                                           |                                    | CRCIF                                  | U2ERIF           | U1ERIF   |       |

| bit 7             |                                                    |                                                                             |                                    |                                        |                  |          | bit C |

|                   |                                                    |                                                                             |                                    |                                        |                  |          |       |

| Legend:           |                                                    |                                                                             |                                    |                                        |                  |          |       |

| R = Readal        | ble bit                                            | W = Writable b                                                              | bit                                | U = Unimplem                           | nented bit, read | d as '0' |       |

| -n = Value a      | at POR                                             | '1' = Bit is set                                                            |                                    | '0' = Bit is cleared x = Bit is unknow |                  |          | own   |

| bit 15-9<br>bit 8 | LVDIF: Low-V<br>1 = Interrupt i<br>0 = Interrupt i | Ited: Read as '0<br>/oltage Detect In<br>request has occ<br>request has not | nterrupt Flag<br>urred<br>occurred | Status bit                             |                  |          |       |

| bit 7-4           | Unimplemen                                         | ted: Read as '0                                                             | 3                                  |                                        |                  |          |       |

| bit 3             | 1 = Interrupt i                                    | Generator Inter<br>request has occ<br>request has not                       | urred                              | tus bit                                |                  |          |       |

| bit 2             | 1 = Interrupt                                      | RT2 Error Interru<br>request has occ<br>request has not                     | urred                              | ıs bit                                 |                  |          |       |

| bit 1             | 1 = Interrupt                                      | RT1 Error Interru<br>request has occ<br>request has not                     | urred                              | ıs bit                                 |                  |          |       |

| bit 0             | Unimplemen                                         | ted: Read as '0                                                             | ,                                  |                                        |                  |          |       |

|                   |                                                    |                                                                             |                                    |                                        |                  |          |       |

#### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0              | R/W-1                                                            | R/W-0                                                     | R/W-0                                                        | U-0                 | R/W-1            | R/W-0           | R/W-0  |

|------------------|------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|---------------------|------------------|-----------------|--------|

| —                | T2IP2                                                            | T2IP1                                                     | T2IP0                                                        | —                   | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15           |                                                                  |                                                           |                                                              |                     |                  |                 | bit 8  |

| U-0              | R/W-1                                                            | R/W-0                                                     | R/W-0                                                        | U-0                 | U-0              | U-0             | U-0    |

| 0-0              | IC2IP2                                                           | IC2IP1                                                    | IC2IP0                                                       | 0-0                 | 0-0              | 0-0             | 0-0    |

| bit 7            | 10211 2                                                          | 10211 1                                                   | 10211 0                                                      |                     |                  |                 | bit C  |

|                  |                                                                  |                                                           |                                                              |                     |                  |                 |        |

| Legend:          |                                                                  |                                                           |                                                              |                     |                  |                 |        |

| R = Readab       | le bit                                                           | W = Writable                                              | bit                                                          | U = Unimplem        | nented bit, read | l as '0'        |        |

| -n = Value a     | t POR                                                            | '1' = Bit is set                                          |                                                              | '0' = Bit is clea   | ared             | x = Bit is unkr | nown   |

|                  |                                                                  |                                                           |                                                              |                     |                  |                 |        |

| bit 15           | -                                                                | nted: Read as '                                           |                                                              |                     |                  |                 |        |

| bit 14-12        |                                                                  | Timer2 Interrupt                                          | •                                                            |                     |                  |                 |        |

|                  | 111 = Interru                                                    | pt is Priority 7 (                                        | highest priority                                             | (interrupt)         |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  |                                                                  | ipt is Priority 1<br>ipt source is dis                    | abled                                                        |                     |                  |                 |        |

| bit 11           | Unimplemer                                                       | nted: Read as '                                           | 0'                                                           |                     |                  |                 |        |

| bit 10-8         | OC2IP<2:0>                                                       | : Output Compa                                            | are Channel 2                                                | Interrupt Priority  | / bits           |                 |        |

|                  | 111 = Interru                                                    | pt is Priority 7 (                                        | highest priority                                             | / interrupt)        |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •<br>001 = Interru                                               | ipt is Priority 1                                         |                                                              |                     |                  |                 |        |

|                  |                                                                  | ipt is Priority 1<br>ipt source is dis                    | abled                                                        |                     |                  |                 |        |

| bit 7            | 000 = Interru                                                    |                                                           |                                                              |                     |                  |                 |        |

|                  | 000 = Interru<br>Unimplemer                                      | ipt source is dis<br>nted: Read as '                      | 0'                                                           | rrupt Priority bits | 6                |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                       | ipt source is dis<br>nted: Read as '                      | <sup>0'</sup><br>Channel 2 Inte                              |                     | 3                |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                       | ipt source is dis<br>nted: Read as fi<br>Input Capture C  | <sup>0'</sup><br>Channel 2 Inte                              |                     | 3                |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                       | ipt source is dis<br>nted: Read as fi<br>Input Capture C  | <sup>0'</sup><br>Channel 2 Inte                              |                     | 5                |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>• | nted: Read as f<br>Input Capture C<br>Input Spriority 7 ( | <sup>0'</sup><br>Channel 2 Inte                              |                     | 3                |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru      | ipt source is dis<br>nted: Read as fi<br>Input Capture C  | <sup>0'</sup><br>Channel 2 Inter<br>highest priorit <u>y</u> |                     | 5                |                 |        |

| U-0                   | R/W-1                                                                   | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                              | U-0                                              | R/W-1           | R/W-0           | R/W-0   |

|-----------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-----------------|---------|

| —                     | CNIP2                                                                   | CNIP1                                                                                                                                                                                                                       | CNIP0                                                                              |                                                  | CMIP2           | CMIP1           | CMIP0   |

| bit 15                |                                                                         |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 | bit     |

| U-0                   | R/W-1                                                                   | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                              | U-0                                              | R/W-1           | R/W-0           | R/W-0   |

|                       | MI2C1P2                                                                 | MI2C1P1                                                                                                                                                                                                                     | MI2C1P0                                                                            |                                                  | SI2C1P2         | SI2C1P1         | SI2C1P0 |

| bit 7                 |                                                                         | 11120111                                                                                                                                                                                                                    | 11120110                                                                           |                                                  | 012011 2        | 0120111         | bit     |

|                       |                                                                         |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 | _       |

| Legend:<br>R = Readab | ole bit                                                                 | W = Writable                                                                                                                                                                                                                | bit                                                                                | U = Unimple                                      | mented bit, rea | d as '0'        |         |

| -n = Value a          |                                                                         | '1' = Bit is set                                                                                                                                                                                                            |                                                                                    | '0' = Bit is cle                                 |                 | x = Bit is unkr | nown    |

|                       |                                                                         |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |

| bit 15                | Unimplemen                                                              | ted: Read as '                                                                                                                                                                                                              | 0'                                                                                 |                                                  |                 |                 |         |

| bit 14-12             | CNIP<2:0>:                                                              | nput Change N                                                                                                                                                                                                               | otification Inte                                                                   | rrupt Priority bi                                | ts              |                 |         |

|                       | 111 = Interru                                                           | pt is Priority 7 (                                                                                                                                                                                                          | highest priority                                                                   | / interrupt)                                     |                 |                 |         |

|                       | •                                                                       |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |

|                       | •                                                                       |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |

|                       | 001 = Interru                                                           |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |

|                       |                                                                         | pt source is dis                                                                                                                                                                                                            |                                                                                    |                                                  |                 |                 |         |

| bit 11                | -                                                                       | ted: Read as '                                                                                                                                                                                                              |                                                                                    |                                                  |                 |                 |         |

| bit 10-8              |                                                                         | Comparator Inte                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |

|                       | 111 = Interru                                                           | pt is Priority 7 (                                                                                                                                                                                                          | highest priority                                                                   | (interrupt)                                      |                 |                 |         |

|                       |                                                                         |                                                                                                                                                                                                                             | rightest priority                                                                  | / interrupt)                                     |                 |                 |         |

|                       | •                                                                       |                                                                                                                                                                                                                             | nightest phones                                                                    | / interrupt)                                     |                 |                 |         |

|                       | •                                                                       |                                                                                                                                                                                                                             | night st phone                                                                     | / interrupt)                                     |                 |                 |         |

|                       | •<br>•<br>001 = Interru                                                 | pt is Priority 1                                                                                                                                                                                                            |                                                                                    | , interrupt)                                     |                 |                 |         |

| bit 7                 | •<br>•<br>001 = Interru<br>000 = Interru                                | pt is Priority 1<br>pt source is dis                                                                                                                                                                                        | abled                                                                              | , interrupt)                                     |                 |                 |         |

| bit 7<br>bit 6-4      | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                  | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                                                                                                                                               | abled<br>0'                                                                        |                                                  |                 |                 |         |

| bit 7<br>bit 6-4      | •<br>•<br>• 001 = Interru<br>000 = Interru<br>Unimplemen<br>MI2C1P<2:0> | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1                                                                                                                                             | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |

|                       | •<br>•<br>• 001 = Interru<br>000 = Interru<br>Unimplemen<br>MI2C1P<2:0> | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                                                                                                                                               | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |

|                       | •<br>•<br>• 001 = Interru<br>000 = Interru<br>Unimplemen<br>MI2C1P<2:0> | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1                                                                                                                                             | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |

|                       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (                                                                                                                       | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |

|                       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1                                                                                                   | abled<br>o'<br>Event Interrup<br>highest priority                                  | t Priority bits                                  |                 |                 |         |

| bit 6-4               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                               | abled<br>o'<br>Event Interrup<br>highest priority<br>abled                         | t Priority bits                                  |                 |                 |         |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                                      | abled<br><sup>0'</sup><br>Event Interrup<br>highest priority<br>abled              | t Priority bits<br>/ interrupt)                  |                 |                 |         |

|                       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                               | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Slave I2C1 E                                   | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Slave I2C1 E                                   | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br><b>:</b> Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br><b>:</b> Slave I2C1 E<br>pt is Priority 7 ( | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |

#### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

#### 8.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- · Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The primary oscillator and FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

#### 8.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to Section 24.1 "Configuration Bits" for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits. FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, shown in Table 8-1.

#### 8.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|----------------------------------------------------|-------------------|-------------|------------|-------|

| Fast RC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| (Reserved)                                         | Internal          | xx          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                     | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator<br>(SOSC)            | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL) | Primary           | 01          | 011        |       |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL) | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        |       |

| Fast RC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| Fast RC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

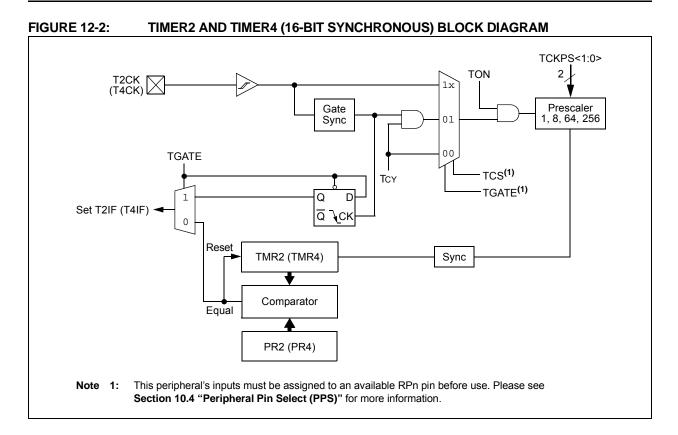

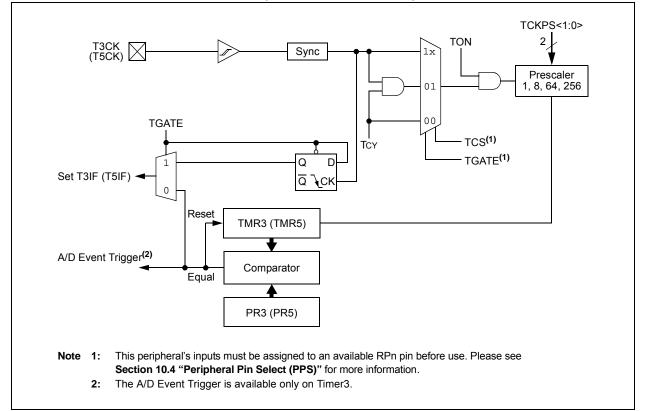

FIGURE 12-3: TIMER3 AND TIMER5 (16-BIT SYNCHRONOUS) BLOCK DIAGRAM

#### 14.3 Pulse-Width Modulation Mode

| Note: | This peripheral contains input and output |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | functions that may need to be configured  |  |  |  |  |  |  |  |  |  |

|       | by the Peripheral Pin Select. See         |  |  |  |  |  |  |  |  |  |

|       | Section 10.4 "Peripheral Pin Select       |  |  |  |  |  |  |  |  |  |

|       | (PPS)" for more information.              |  |  |  |  |  |  |  |  |  |

The following steps should be taken when configuring the output compare module for PWM operation:

- 1. Set the PWM period by writing to the selected Timery Period register (PRy).

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Write the OCxR register with the initial duty cycle.

- 4. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- Configure the output compare module for one of two PWM Operation modes by writing to the Output Compare Mode bits, OCM<2:0> (OCxCON<2:0>).

- 6. Set the TMRy prescale value and enable the time base by setting TON (TyCON<15>) = 1.

- Note: The OCxR register should be initialized before the output compare module is first enabled. The OCxR register becomes a read-only Duty Cycle register when the module is operated in the PWM modes. The value held in OCxR will become the PWM duty cycle for the first PWM period. The contents of the Output Compare x Secondary register, OCxRS, will not be transferred into OCxR until a time base period match occurs.

#### 14.3.1 PWM PERIOD

The PWM period is specified by writing to PRy, the Timery Period register. The PWM period can be calculated using Equation 14-1.

## EQUATION 14-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period =  $[(PRy) + 1] \bullet TCY \bullet (Timer Prescale Value)$ Where:

PWM Frequency = 1/[PWM Period]

**Note 1:** Based on TCY = 2 \* TOSC; Doze mode and PLL are disabled.

Note: A PRy value of N will produce a PWM period of N + 1 time base count cycles. For example, a value of 7 written into the PRy register will yield a period consisting of 8 time base cycles.

#### 14.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS register. The OCxRS register can be written to at any time, but the duty cycle value is not latched into OCxR until a match between PRy and TMRy occurs (i.e., the period is complete). This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation. In the PWM mode, OCxR is a read-only register.

Some important boundary parameters of the PWM duty cycle include:

- If the Output Compare x register, OCxR, is loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxR is greater than PRy (Timery Period register), the pin will remain high (100% duty cycle).

- If OCxR is equal to PRy, the OCx pin will be low for one time base count value and high for all other count values.

See Example 14-1 for PWM mode timing details. Table 14-1 and Table 14-2 show example PWM frequencies and resolutions for a device operating at 4 and 16 MIPS.

#### EQUATION 14-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

### 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Serial Peripheral Interface (SPI)"* (DS39699)

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the SPI and SIOP Motorola<sup>®</sup> interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 15-1 and Figure 15-2.

Depending on the pin count, PIC24FJ64GA004 family devices offer one or two SPI modules on a single device.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON1 or SPIxCON2 refers to the control register for the SPI1 or SPI2 module. To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit (SPIxCON1<9>).

- 5. If the CKE bit is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

| U-0                 | U-0                                    | U-0              | R/W-0                                  | R/W-0                 | R/W-0                  | R/W-0            | R/W-0              |

|---------------------|----------------------------------------|------------------|----------------------------------------|-----------------------|------------------------|------------------|--------------------|

| _                   | _                                      | _                | DISSCK <sup>(1)</sup>                  | DISSDO <sup>(2)</sup> | MODE16                 | SMP              | CKE <sup>(3)</sup> |

| bit 15              |                                        |                  |                                        |                       |                        |                  | bit                |

|                     |                                        |                  |                                        |                       |                        |                  |                    |

| R/W-0               |                                        | R/W-0            | R/W-0                                  | R/W-0                 | R/W-0                  | R/W-0            | R/W-0              |

| SSEN <sup>(4)</sup> | ) CKP                                  | MSTEN            | SPRE2                                  | SPRE1                 | SPRE0                  | PPRE1            | PPRE0              |

| bit 7               |                                        |                  |                                        |                       |                        |                  | bit                |

| Legend:             |                                        |                  |                                        |                       |                        |                  |                    |

| R = Reada           | able bit                               | W = Writable     | bit                                    | U = Unimplem          | nented bit, read       | as '0'           |                    |

| -n = Value          | at POR                                 | '1' = Bit is set |                                        | '0' = Bit is clea     |                        | x = Bit is unkn  | iown               |

|                     |                                        |                  | -                                      |                       |                        |                  | -                  |

| bit 15-13           | Unimplemen                             | ted: Read as '   | 0'                                     |                       |                        |                  |                    |

| bit 12              | DISSCK: Disa                           | ables SCKx Pi    | n bit (SPI Maste                       | er modes only)        | (1)                    |                  |                    |

|                     |                                        |                  | abled; pin funct                       | ions as I/O           |                        |                  |                    |

|                     |                                        | SPI clock is en  |                                        |                       |                        |                  |                    |

| bit 11              |                                        | ables SDOx Pi    |                                        |                       |                        |                  |                    |

|                     |                                        |                  | y the module; p                        | in functions as       | I/O                    |                  |                    |

| bit 10              |                                        | n is controlled  | •                                      | at hit                |                        |                  |                    |

|                     |                                        | -                | unication Seleo                        |                       |                        |                  |                    |

|                     |                                        | ication is byte- | , ,                                    |                       |                        |                  |                    |

| bit 9               |                                        | ata Input Sam    |                                        |                       |                        |                  |                    |

|                     | Master mode:                           |                  |                                        |                       |                        |                  |                    |

|                     |                                        |                  | t end of data ou                       |                       |                        |                  |                    |

|                     | -                                      | a is sampled a   | t middle of data                       | output time           |                        |                  |                    |

|                     | <u>Slave mode:</u>                     | cleared when     | SPIx is used in                        | Slave mode            |                        |                  |                    |

| bit 8               |                                        | lock Edge Sele   |                                        |                       |                        |                  |                    |

| bit 0               |                                        | •                |                                        | n from active c       | lock state to Idl      | e clock state (s | see bit 6)         |

|                     |                                        |                  |                                        |                       | ck state to active     |                  |                    |

| bit 7               | SSEN: Slave                            | Select Enable    | bit (Slave mode                        | ∋) <sup>(4)</sup>     |                        |                  |                    |

|                     |                                        | s used for Slav  |                                        |                       |                        |                  |                    |

|                     | 0 = SSx pin i                          | s not used by    | he module; pin                         | is controlled by      | y port function        |                  |                    |

| bit 6               |                                        | Polarity Select  |                                        |                       |                        |                  |                    |

|                     |                                        |                  | s a high level; a<br>s a low level; ac |                       |                        |                  |                    |

| bit 5               |                                        | ter Mode Enat    | -                                      |                       | lignievei              |                  |                    |

| DIUD                | 1 = Master m                           |                  | ne bit                                 |                       |                        |                  |                    |

|                     | 0 = Slave mo                           |                  |                                        |                       |                        |                  |                    |

| Note 1:             | If DISSCK = 0, So<br>Select (PPS)" for |                  |                                        | available RPn         | pin. See <b>Sectio</b> | on 10.4 "Perip   | heral Pin          |

| 2:                  | If DISSDO = 0, S<br>Select (PPS)" for  | DOx must be o    | configured to an                       | available RPn         | pin. See <b>Secti</b>  | on 10.4 "Perip   | oheral Pin         |

| 3:                  | The CKE bit is no SPI modes (FRM       | EN = 1).         |                                        |                       |                        |                  |                    |

| 4:                  | If SSEN = 1, SSx<br>(PPS)" for more i  |                  | gured to an ava                        | ilable RPn pin.       | See Section 1          | 0.4 "Peripher    | al Pin Selec       |

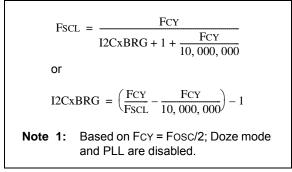

#### 16.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 16-1.

## EQUATION 16-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

#### TABLE 16-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1)</sup>

#### 16.4 Slave Address Masking

The I2CxMSK register (Register 16-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000', the slave module will detect both addresses, '00000000' and '00100000'.

To enable address masking, the IPMI (Intelligent Peripheral Management Interface) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 16-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required       | _      | I2CxB     | Actual        |           |

|----------------|--------|-----------|---------------|-----------|

| System<br>FscL | FCY    | (Decimal) | (Hexadecimal) | FSCL      |

| 100 kHz        | 16 MHz | 157       | 9D            | 100 kHz   |

| 100 kHz        | 8 MHz  | 78        | 4E            | 100 kHz   |

| 100 kHz        | 4 MHz  | 39        | 27            | 99 kHz    |

| 400 kHz        | 16 MHz | 37        | 25            | 404 kHz   |

| 400 kHz        | 8 MHz  | 18        | 12            | 404 kHz   |

| 400 kHz        | 4 MHz  | 9         | 9             | 385 kHz   |

| 400 kHz        | 2 MHz  | 4         | 4             | 385 kHz   |

| 1 MHz          | 16 MHz | 13        | D             | 1.026 MHz |

| 1 MHz          | 8 MHz  | 6         | 6             | 1.026 MHz |

| 1 MHz          | 4 MHz  | 3         | 3             | 0.909 MHz |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

#### TABLE 16-2: $I^2 C^{TM} RESERVED ADDRESSES^{(1)}$

| Slave<br>Address | R/W<br>Bit | Description                            |

|------------------|------------|----------------------------------------|

| 0000 000         | 0          | General Call Address <sup>(2)</sup>    |

| 0000 000         | 1          | Start Byte                             |

| 0000 001         | x          | Cbus Address                           |

| 0000 010         | x          | Reserved                               |

| 0000 011         | x          | Reserved                               |

| 0000 1xx         | x          | HS Mode Master Code                    |

| 1111 1xx         | x          | Reserved                               |

| 1111 0xx         | х          | 10-Bit Slave Upper Byte <sup>(3)</sup> |

Note 1: The address bits listed here will never cause an address match, independent of the address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

#### 17.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt 2 cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bits, UTXISEL<1:0>.

#### 17.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 17.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt 2 cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bits, UTXISEL<1:0>.

## 17.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

#### 17.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 17.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received as per interrupt control bits, URXISEL<1:0>.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

#### 17.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control mode. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

#### 17.7 Infrared Support

The UARTx module provides two types of infrared UART support: one is the IrDA clock output to support external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder. Note that because the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 17.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the BCLKx pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. With UEN<1:0> = 11, the BCLKx pin will output the 16x baud clock if the UARTx module is enabled. It can be used to support the IrDA codec chip.

## 17.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

#### REGISTER 21-2: AD1CON2: A/D CONTROL REGISTER 2

| VCFG2         VCFG1         VCFG0         —         —         CSCNA         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         _         bit 8         bit 8         Dit 9         Dit 9 <thdit 9<="" th=""> <thdit 9<="" th=""> <thdit 9<="" t<="" th=""><th>R/W-0</th><th>R/W-0</th><th>R/W-0</th><th>U-0</th><th>U-0</th><th>R/W-0</th><th>U-0</th><th>U-0</th></thdit></thdit></thdit> | R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | U-0 | U-0   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|-----|-----|-------|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VCFG2  | VCFG1 | VCFG0 | —   | —   | CSCNA | -   | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 15 |       |       |     |     |       |     | bit 8 |

| R-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| BUFS  | —   | SMPI3 | SMPI2 | SMPI1 | SMPI0 | BUFM  | ALTS  |

| bit 7 |     |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

| VCFG<2:0> | VR+                | VR-                |

|-----------|--------------------|--------------------|

| 000       | AVDD*              | AVss*              |

| 001       | External VREF+ Pin | AVss*              |

| 010       | AVDD*              | External VREF- Pin |

| 011       | External VREF+ Pin | External VREF- Pin |

| lxx       | AVDD*              | AVss*              |

\* AVDD and AVss inputs are tied to VDD and Vss on 28-pin devices.

#### bit 12-11 Unimplemented: Read as '0'

|         | •                                                                                                                                                                                    |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | CSCNA: Scan Input Selections for CH0+ S/H Input for MUX A Input Multiplexer Setting bit                                                                                              |

|         | 1 = Scans inputs                                                                                                                                                                     |

|         | 0 = Does not scan inputs                                                                                                                                                             |

| bit 9-8 | Unimplemented: Read as '0'                                                                                                                                                           |

| bit 7   | BUFS: Buffer Fill Status bit (valid only when BUFM = 1)                                                                                                                              |

|         | <ul> <li>1 = A/D is currently filling Buffer 08-0F, user should access data in 00-07</li> <li>0 = A/D is currently filling Buffer 00-07, user should access data in 08-0F</li> </ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                           |

| bit 5-2 | SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits                                                                                                                     |

|         | 1111 = Interrupts at the completion of conversion for each 16th sample/convert sequence                                                                                              |