Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga004-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                    | 7     |

|-------|--------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers        | 17    |

| 3.0   | CPU                                                                | 23    |

| 4.0   | Memory Organization                                                | 29    |

| 5.0   | Flash Program Memory                                               | 47    |

| 6.0   | Resets                                                             | 53    |

| 7.0   | Interrupt Controller                                               | 59    |

| 8.0   | Oscillator Configuration                                           | 95    |

| 9.0   | Power-Saving Features                                              | . 103 |

| 10.0  | I/O Ports                                                          | . 105 |

| 11.0  | Timer1                                                             | . 125 |

| 12.0  | Timer2/3 and Timer4/5                                              | . 127 |

| 13.0  | Input Capture                                                      | . 133 |

| 14.0  | Output Compare                                                     | . 135 |

| 15.0  | Serial Peripheral Interface (SPI)                                  |       |

| 16.0  | Inter-Integrated Circuit (I <sup>2</sup> C <sup>™</sup> )          | . 151 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)                 | . 159 |

|       | Parallel Master Port (PMP)                                         |       |

| 19.0  | Real-Time Clock and Calendar (RTCC)                                |       |

| 20.0  | Programmable Cyclic Redundancy Check (CRC) Generator               | . 189 |

| 21.0  | 10-Bit High-Speed A/D Converter                                    | . 193 |

| 22.0  | Comparator Module                                                  | 203   |

| 23.0  | Comparator Voltage Reference                                       | 207   |

| 24.0  | Special Features                                                   | 209   |

| 25.0  | Development Support                                                | 219   |

| 26.0  | Instruction Set Summary                                            | 223   |

| 27.0  | Electrical Characteristics                                         | . 231 |

| 28.0  | Packaging Information                                              | 251   |

|       | ndix A: Revision History                                           |       |

| Appe  | ndix B: Additional Guidance for PIC24FJ64GA004 Family Applications | 268   |

| Index |                                                                    | 269   |

| The N | /icrochip Web Site                                                 | . 273 |

| Custo | mer Change Notification Service                                    | 273   |

| Custo | mer Support                                                        | . 273 |

| Read  | er Response                                                        | . 274 |

| Produ | Ict Identification System                                          | 275   |

#### 2.4 **Voltage Regulator Pins** (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This section applies only to PIC24F J      |

|-------|--------------------------------------------|

|       | devices with an on-chip voltage regulator. |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator. or to ground to disable the regulator

- · For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to Section 24.2 "On-Chip Voltage Regulator" for details on connecting and using the on-chip regulator.

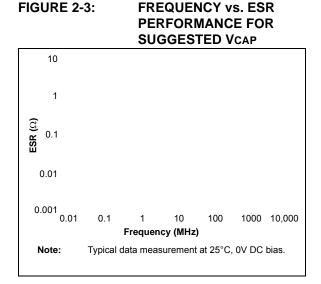

When the regulator is enabled, a low-ESR (<  $5\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10 µF connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specification can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to Section 27.0 "Electrical Characteristics" for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to Section 27.0 "Electrical Characteristics" for information on VDD and VDDCORE.

| TABLE 2-1: | SUITABLE CAPACITOR EQUIVALENTS |                        |                |               |               |  |  |  |  |

|------------|--------------------------------|------------------------|----------------|---------------|---------------|--|--|--|--|

| Make       | Part #                         | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |  |  |  |  |

| TDK        | C3216X7R1C106K                 | 10 µF                  | ±10%           | 16V           | -55 to +125°C |  |  |  |  |

| TDK        | C3216X5R1C106K                 | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |  |  |  |  |

| Panasonic  | ECJ-3YX1C106K                  | 10 µF                  | ±10%           | 16V           | -55 to +125°C |  |  |  |  |

| Panasonic  | ECJ-4YB1C106K                  | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |  |  |  |  |

| Murata     | GRM32DR71C106KA01L             | 10 µF                  | ±10%           | 16V           | -55 to +125°C |  |  |  |  |

| Murata     | GRM31CR61C106KC31L             | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |  |  |  |  |

# 8.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- · Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The primary oscillator and FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

# 8.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to Section 24.1 "Configuration Bits" for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits. FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, shown in Table 8-1.

#### 8.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|----------------------------------------------------|-------------------|-------------|------------|-------|

| Fast RC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| (Reserved)                                         | Internal          | xx          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                     | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator<br>(SOSC)            | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL) | Primary           | 01          | 011        |       |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL) | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        |       |

| Fast RC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| Fast RC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

# TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | —   | RP21R4 <sup>(1)</sup> | RP21R3 <sup>(1)</sup> | RP21R2 <sup>(1)</sup> | RP21R1 <sup>(1)</sup> | RP21R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|       | —   | —   | RP20R4 <sup>(1)</sup> | RP20R3 <sup>(1)</sup> | RP20R2 <sup>(1)</sup> | RP20R1 <sup>(1)</sup> | RP20R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP21R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-3 for peripheral function numbers)                                                       |

| bit 7-5 | Unimplemented: Read as '0' |  |

|---------|----------------------------|--|

| bit 7-5 | Unimplemented: Read as '0' |  |

bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|        | —   | _   | RP23R4 <sup>(1)</sup> | RP23R3 <sup>(1)</sup> | RP23R2 <sup>(1)</sup> | RP23R1 <sup>(1)</sup> | RP23R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

|        |     |     |                       |                       |                       |                       |                       |

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|        | —   | —   | RP22R4 <sup>(1)</sup> | RP22R3 <sup>(1)</sup> | RP22R2 <sup>(1)</sup> | RP22R1 <sup>(1)</sup> | RP22R0 <sup>(1)</sup> |

| bit 7  |     |     |                       |                       |                       |                       | bit 0                 |

#### REGISTER 10-26: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

# 12.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, **"Timers"** (DS39704).

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 and Timer4/5 operate in three modes:

- Two independent, 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer

- · Single 32-bit synchronous counter

They also support these features:

- Timer gate operation

- Selectable prescaler settings

- · Timer operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period register match

- A/D Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the A/D Event Trigger; this is implemented only with Timer3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1; T3CON and T5CON are shown in generic form in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON and T5CON      |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | control bits are ignored. Only T2CON and   |  |  |  |  |  |

|       | T4CON control bits are used for setup and  |  |  |  |  |  |

|       | control. Timer2 and Timer4 clock and gate  |  |  |  |  |  |

|       | inputs are utilized for the 32-bit timer   |  |  |  |  |  |

|       | modules, but an interrupt is generated     |  |  |  |  |  |

|       | with the Timer3 or Timer5 interrupt flags. |  |  |  |  |  |

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to the external clock, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word of the value while PR2 (or PR4) contains the least significant word.

- 5. If interrupts are required, set the Timer3/5 Interrupt Enable bit, T3IE or T5IE; use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR3:TMR2 (or TMR5:TMR4). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the Timerx Interrupt Enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

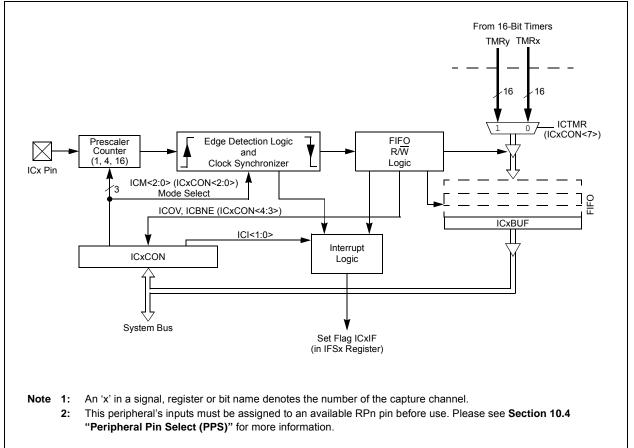

# **13.0 INPUT CAPTURE**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Input Capture"* (DS39701).

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 4 **RXINV:** Receive Polarity Inversion bit 1 = UxRX Idle state is '0' 0 = UxRX Idle state is '1' bit 3 BRGH: High Baud Rate Enable bit 1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode) 0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode) bit 2-1 PDSEL<1:0>: Parity and Data Selection bits 11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity bit 0 STSEL: Stop Bit Selection bit 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: Bit availability depends on pin availability.

# PIC24FJ64GA004 FAMILY

### REGISTER 18-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

| U-0    | R/W-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                | R/W-0                |

|--------|-------|-----|-----|-----|-----------------------|----------------------|----------------------|

| —      | CS1   | —   | —   | —   | ADDR10 <sup>(1)</sup> | ADDR9 <sup>(1)</sup> | ADDR8 <sup>(1)</sup> |

| bit 15 |       |     |     |     |                       |                      | bit 8                |

| R/W-0                |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| ADDR7 <sup>(1)</sup> | ADDR6 <sup>(1)</sup> | ADDR5 <sup>(1)</sup> | ADDR4 <sup>(1)</sup> | ADDR3 <sup>(1)</sup> | ADDR2 <sup>(1)</sup> | ADDR1 <sup>(1)</sup> | ADDR0 <sup>(1)</sup> |

| bit 7 bit 0          |                      |                      |                      |                      |                      |                      |                      |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 14 CS1: Chip Select 1 bit

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Parallel Port Destination Address bits<sup>(1)</sup>

- **Note 1:** PMA<10:2> bits are not available on 28-pin devices.

#### REGISTER 18-4: PMAEN: PARALLEL PORT ENABLE REGISTER

| U-0    | R/W-0  | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                | R/W-0                |

|--------|--------|-----|-----|-----|-----------------------|----------------------|----------------------|

| _      | PTEN14 | —   | —   | —   | PTEN10 <sup>(1)</sup> | PTEN9 <sup>(1)</sup> | PTEN8 <sup>(1)</sup> |

| bit 15 |        |     |     |     |                       |                      | bit 8                |

| R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------|-------|

| PTEN7 <sup>(1)</sup> | PTEN6 <sup>(1)</sup> | PTEN5 <sup>(1)</sup> | PTEN4 <sup>(1)</sup> | PTEN3 <sup>(1)</sup> | PTEN2 <sup>(1)</sup> | PTEN1 | PTEN0 |

| bit 7                |                      |                      |                      |                      |                      |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15<br>bit 14 | Unimplemented: Read as '0'<br>PTEN14: PMCS1 Strobe Enable bit<br>1 = PMCS1 pin functions as chip select<br>0 = PMCS1 pin functions as port I/O   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-11        | Unimplemented: Read as '0'                                                                                                                       |

| bit 10-2         | PTEN<10:2>: PMP Address Port Enable bits <sup>(1)</sup>                                                                                          |

|                  | <ul><li>1 = PMA&lt;10:2&gt; function as PMP address lines</li><li>0 = PMA&lt;10:2&gt; function as port I/O</li></ul>                             |

| bit 1-0          | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                        |

|                  | <ul> <li>1 = PMA1 and PMA0 function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA1 and PMA0 pads functions as port I/O</li> </ul> |

**Note 1:** PMA<10:2> bits are not available on 28-pin devices.

# PIC24FJ64GA004 FAMILY

## REGISTER 20-2: CRCXOR: CRC XOR POLYNOMIAL REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

| X15                               | X14   | X13              | X12                                | X11                  | X10   | X9                 | X8    |

| bit 15                            |       |                  |                                    |                      | •     |                    | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | U-0   |

| X7                                | X6    | X5               | X4                                 | X3                   | X2    | X1                 | —     |

| bit 7                             |       |                  |                                    |                      |       |                    | bit 0 |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR '               |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-1 X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

#### REGISTER 22-1: CMCON: COMPARATOR CONTROL REGISTER (CONTINUED)

| bit 6   | C1OUT: Comparator 1 Output bit                                |

|---------|---------------------------------------------------------------|

|         | <u>When C1INV = 0:</u>                                        |

|         | 1 = C1 VIN+ > C1 VIN-                                         |

|         | 0 = C1 VIN + < C1 VIN -                                       |

|         | When C1INV = 1:                                               |

|         | 0 = C1 VIN + > C1 VIN -                                       |

|         | 1 = C1 VIN + < C1 VIN -                                       |

| bit 5   | C2INV: Comparator 2 Output Inversion bit                      |

|         | 1 = C2 output is inverted                                     |

|         | 0 = C2 output is not inverted                                 |

| bit 4   | C1INV: Comparator 1 Output Inversion bit                      |

|         | 1 = C1 output is inverted                                     |

|         | 0 = C1 output is not inverted                                 |

| bit 3   | C2NEG: Comparator 2 Negative Input Configure bit              |

|         | 1 = Input is connected to VIN+                                |

|         | 0 = Input is connected to VIN-                                |

|         | See Figure 22-1 for the Comparator modes.                     |

| bit 2   | C2POS: Comparator 2 Positive Input Configure bit              |

|         | 1 = Input is connected to VIN+                                |

|         | 0 = Input is connected to CVREF                               |

|         | See Figure 22-1 for the Comparator modes.                     |

| bit 1   | C1NEG: Comparator 1 Negative Input Configure bit              |

|         | 1 = Input is connected to VIN+                                |

|         | 0 = Input is connected to VIN-                                |

|         | See Figure 22-1 for the Comparator modes.                     |

| bit 0   | C1POS: Comparator 1 Positive Input Configure bit              |

|         | 1 = Input is connected to VIN+                                |

|         | 0 = Input is connected to CVREF                               |

|         | See Figure 22-1 for the Comparator modes.                     |

| Note 1: | If C2OUTEN = 1, the C2OUT peripheral output must be configure |

- If C2OUTEN = 1, the C2OUT peripheral output must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 2: If C1OUTEN = 1, the C1OUT peripheral output must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

#### REGISTER 24-2: CW2: FLASH CONFIGURATION WORD 2 (CONTINUED)

- bit 4 IOL1WAY: IOLOCK One-Way Set Enable bit

- 1 = The IOLOCK (OSCCON<6>) bit can be set once, provided the unlock sequence has been completed. Once set, the Peripheral Pin Select registers cannot be written to a second time.

- 0 = The IOLOCK (OSCCON<6>) bit can be set and cleared as needed, provided the unlock sequence has been completed

#### bit 3 Reserved

- bit 2 I2C1SEL: I2C1 Pin Select bit

- 1 = Use default SCL1/SDA1 pins

- 0 = Use alternate SCL1/SDA1 pins

bit 1-0 **POSCMD<1:0:>** Primary Oscillator Configuration bits

- 11 = Primary oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = EC Oscillator mode is selected

- **Note 1:** These bits are implemented only in devices with a major silicon revision level of B or later (DEVREV register value is 3042h or greater). Refer to **Section 28.0 "Packaging Information"** in the device data sheet for the location and interpretation of product date codes.

#### REGISTER 24-3: DEVID: DEVICE ID REGISTER

| U             | U | U | U | U | U | U | U |

|---------------|---|---|---|---|---|---|---|

| —             | — | — | _ | _ | _ | — | — |

| bit 23 bit 16 |   |   |   |   |   |   |   |

| U      | U | R      | R      | R      | R      | R      | R      |

|--------|---|--------|--------|--------|--------|--------|--------|

| _      | — | FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 |

| bit 15 |   |        |        |        |        |        | bit 8  |

| R      | R      | R    | R    | R    | R    | R    | R     |

|--------|--------|------|------|------|------|------|-------|

| FAMID1 | FAMID0 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7  | •      |      |      |      |      |      | bit 0 |

| Legend: | R = Read-onl   | v bit | U = Unimplemented bit |

|---------|----------------|-------|-----------------------|

| Legenu. | IN - INeau-Oni | y Dit |                       |

bit 23-14 Unimplemented: Read as '1'

bit 13-6 FAMID<7:0>: Device Family Identifier bits

00010001 = PIC24FJ64GA004 family

- bit 5-0 DEV<5:0>: Individual Device Identifier bits

- 000100 = PIC24FJ16GA002

- 000101 = PIC24FJ32GA002

- 000110 = PIC24FJ48GA002

- 000111 = PIC24FJ64GA002

- 001100 = PIC24FJ16GA004

- 001101 = PIC24FJ32GA004

- 001110 = PIC24FJ48GA004 001111 = PIC24FJ64GA004

# 24.2.3 ON-CHIP REGULATOR AND POR

When the voltage regulator is enabled, it takes approximately 10 µs for it to generate output. During this time, designated as TVREG, code execution is disabled. TVREG is applied every time the device resumes operation after any power-down, including Sleep mode. TVREG is determined by the setting of the PMSLP bit (RCON<8>) and the WUTSELx Configuration bits (CW2<14:13>). For more information on TVREG, see **Section 27.0 "Electrical Characteristics"**.

If the regulator is disabled, a separate Power-up Timer (PWRT) is automatically enabled. The PWRT adds a fixed delay of 64 ms nominal delay at device start-up (POR or BOR only). When waking up from Sleep with the regulator disabled, TVREG is used to determine the wake-up time. To decrease the device wake-up time when operating with the regulator disabled, the PMSLP bit can be set.

# 24.2.4 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VDDCORE must never exceed VDD by 0.3 volts.

| Note: | For more information, see Section 27.0 |

|-------|----------------------------------------|

|       | "Electrical Characteristics".          |

#### 24.2.5 VOLTAGE REGULATOR STANDBY MODE

When enabled, the on-chip regulator always consumes a small incremental amount of current over IDD/IPD, including when the device is in Sleep mode, even though the core digital logic does not require power. To provide additional savings in applications where power resources are critical, the regulator automatically places itself into Standby mode whenever the device goes into Sleep mode. This feature is controlled by the PMSLP bit (RCON<8>). By default, this bit is cleared, which enables Standby mode.

For select PIC24FJ64GA004 family devices, the time required for regulator wake-up from Standby mode is controlled by the WUTSEL<1:0> Configuration bits (CW2<14:13>). The default wake-up time for all devices is 190  $\mu$ s. Where the WUTSELx Configuration bits are implemented, a fast wake-up option is also available. When WUTSEL<1:0> = 01, the regulator wake-up time is 25  $\mu$ s.

Note: This feature is implemented only on PIC24FJ64GA004 family devices with a major silicon revision level of B or later (DEVREV register value is 3042h or greater). When the regulator's Standby mode is turned off (PMSLP = 1), Flash program memory stays powered in Sleep mode and the device can wake-up in less than 10  $\mu$ s. When PMSLP is set, the power consumption while in Sleep mode will be approximately 40  $\mu$ A higher than power consumption when the regulator is allowed to enter Standby mode.

# 24.3 Watchdog Timer (WDT)

For PIC24FJ64GA004 family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT Time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPS<3:0> Configuration bits (CW1<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3:2>) will need to be cleared in software after the device wakes up.

The WDT Flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

| DC CHARACTE     | RISTICS                |              | Standard Ope<br>Operating tem |            | 2 <b>.0V to 3.6V (unless o</b><br>40°C ≤ TA ≤ +85°C foi<br>40°C ≤ TA ≤ +125°C foi | r Industrial  |  |  |  |

|-----------------|------------------------|--------------|-------------------------------|------------|-----------------------------------------------------------------------------------|---------------|--|--|--|

| Parameter No.   | Typical <sup>(1)</sup> | Max          | Units                         | Conditions |                                                                                   |               |  |  |  |

| Operating Curre | ent (IDD): PMI         | D Bits are S | et <sup>(2)</sup>             | •          |                                                                                   |               |  |  |  |

| DC20            | 0.650                  | 0.850        | mA                            | -40°C      |                                                                                   |               |  |  |  |

| DC20a           | 0.650                  | 0.850        | mA                            | +25°C      | 2.0∨ <sup>(3)</sup>                                                               |               |  |  |  |

| DC20b           | 0.650                  | 0.850        | mA                            | +85°C      | 2.000                                                                             |               |  |  |  |

| DC20c           | 0.650                  | 0.850        | mA                            | +125°C     |                                                                                   |               |  |  |  |

| DC20d           | 1.2                    | 1.6          | mA                            | -40°C      |                                                                                   | 1 MIPS        |  |  |  |

| DC20e           | 1.2                    | 1.6          | mA                            | +25°C      |                                                                                   |               |  |  |  |

| DC20f           | 1.2                    | 1.6          | mA                            | +85°C      | 3.3007                                                                            |               |  |  |  |

| DC20g           | 1.2                    | 1.6          | mA                            | +125°C     |                                                                                   |               |  |  |  |

| DC23            | 2.6                    | 3.4          | mA                            | -40°C      |                                                                                   |               |  |  |  |

| DC23a           | 2.6                    | 3.4          | mA                            | +25°C      | -<br>                                                                             |               |  |  |  |

| DC23b           | 2.6                    | 3.4          | mA                            | +85°C      | 2.0V <sup>(3)</sup>                                                               |               |  |  |  |

| DC23c           | 2.6                    | 3.4          | mA                            | +125°C     |                                                                                   |               |  |  |  |

| DC23d           | 4.1                    | 5.4          | mA                            | -40°C      |                                                                                   | 4 MIPS        |  |  |  |

| DC23e           | 4.1                    | 5.4          | mA                            | +25°C      | -<br>                                                                             |               |  |  |  |

| DC23f           | 4.1                    | 5.4          | mA                            | +85°C      | - 3.3∨ <sup>(4)</sup>                                                             |               |  |  |  |

| DC23g           | 4.1                    | 5.4          | mA                            | +125°C     |                                                                                   |               |  |  |  |

| DC24            | 13.5                   | 17.6         | mA                            | -40°C      |                                                                                   |               |  |  |  |

| DC24a           | 13.5                   | 17.6         | mA                            | +25°C      | -<br>                                                                             |               |  |  |  |

| DC24b           | 13.5                   | 17.6         | mA                            | +85°C      | 2.5V <sup>(3)</sup>                                                               |               |  |  |  |

| DC24c           | 13.5                   | 17.6         | mA                            | +125°C     |                                                                                   | 40 14/100     |  |  |  |

| DC24d           | 15                     | 20           | mA                            | -40°C      |                                                                                   | 16 MIPS       |  |  |  |

| DC24e           | 15                     | 20           | mA                            | +25°C      | 3.3√(4)                                                                           |               |  |  |  |

| DC24f           | 15                     | 20           | mA                            | +85°C      | 3.3007                                                                            |               |  |  |  |

| DC24g           | 15                     | 20           | mA                            | +125°C     |                                                                                   |               |  |  |  |

| DC31            | 13                     | 17           | μA                            | -40°C      |                                                                                   |               |  |  |  |

| DC31a           | 13                     | 17           | μA                            | +25°C      | 2.0∨ <sup>(3)</sup>                                                               |               |  |  |  |

| DC31b           | 20                     | 26           | μA                            | +85°C      | 2.000                                                                             |               |  |  |  |

| DC31c           | 40                     | 50           | μA                            | +125°C     |                                                                                   |               |  |  |  |

| DC31d           | 54                     | 70           | μA                            | -40°C      |                                                                                   | LPRC (31 kHz) |  |  |  |

| DC31e           | 54                     | 70           | μA                            | +25°C      | a a (4)                                                                           |               |  |  |  |

| DC31f           | 95                     | 124          | μA                            | +85°C      | - 3.3√ <sup>(4)</sup>                                                             |               |  |  |  |

| DC31g           | 120                    | 260          | μA                            | +125°C     |                                                                                   |               |  |  |  |

#### TABLE 27-4: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSCI driven with external square wave from rail-to-rail. All I/O pins are configured as inputs and pulled to VDD. MCLR = VDD; WDT and FSCM are disabled. CPU, SRAM, program memory and data memory are operational. No peripheral modules are operating and all of the Peripheral Module Disable (PMD) bits are set.

3: On-chip voltage regulator is disabled (DISVREG tied to VDD).

4: On-chip voltage regulator is enabled (DISVREG tied to Vss). Low-Voltage Detect (LVD) and Brown-out Detect (BOD) are enabled.

#### TABLE 27-10: COMPARATOR SPECIFICATIONS

| Operatir     | <b>Operating Conditions:</b> $2.0V < VDD < 3.6V$ , $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) |                                            |     |     |     |       |          |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|-------|----------|--|--|

| Param<br>No. | Symbol                                                                                                          | Characteristic                             | Min | Тур | Max | Units | Comments |  |  |

| D300         | VIOFF                                                                                                           | Input Offset Voltage*                      | _   | 10  | 30  | mV    |          |  |  |

| D301         | VICM                                                                                                            | Input Common-Mode Voltage*                 | 0   | _   | Vdd | V     |          |  |  |

| D302         | CMRR                                                                                                            | Common-Mode Rejection<br>Ratio*            | 55  | —   | _   | dB    |          |  |  |

| 300          | TRESP                                                                                                           | Response Time <sup>*(1)</sup>              |     | 150 | 400 | ns    |          |  |  |

| 301          | Тмс2оv                                                                                                          | Comparator Mode Change to<br>Output Valid* | _   | —   | 10  | μS    |          |  |  |

\* Parameters are characterized but not tested.

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 27-11: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| Operatin     | <b>Operating Conditions:</b> 2.0V < V <sub>DD</sub> < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                              |        |     |        |       |          |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|------------------------------|--------|-----|--------|-------|----------|--|--|--|

| Param<br>No. | Symbol                                                                                                   | Characteristic               | Min    | Тур | Мах    | Units | Comments |  |  |  |

| VRD310       | CVRES                                                                                                    | Resolution                   | VDD/24 | _   | Vdd/32 | LSb   |          |  |  |  |

| VRD311       | CVRAA                                                                                                    | Absolute Accuracy            | _      | _   | 1      | LSb   |          |  |  |  |

| VRD312       | CVRur                                                                                                    | Unit Resistor Value (R)      | -      | 2k  | —      | Ω     |          |  |  |  |

| VR310        | TSET                                                                                                     | Settling Time <sup>(1)</sup> | _      | —   | 10     | μS    |          |  |  |  |

Note 1: Settling time is measured while CVRR = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

#### TABLE 27-12: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Operatin     | g Conditio | <b>ns:</b> -40°C < TA < +125°C (unles | s otherw | ise statec | d)  |       |                                                               |

|--------------|------------|---------------------------------------|----------|------------|-----|-------|---------------------------------------------------------------|

| Param<br>No. | Symbol     | Characteristics                       | Min      | Тур        | Max | Units | Comments                                                      |

|              | Vrgout     | Regulator Output Voltage              | _        | 2.5        |     | V     |                                                               |

|              | Vbg        | Band Gap Reference Voltage            | —        | 1.2        | _   | V     |                                                               |

|              | Cefc       | External Filter Capacitor<br>Value    | 4.7      | 10         | —   | μF    | Series resistance < 3 Ohm<br>recommended;<br>< 5 Ohm required |

|              | TVREG      | Voltage Regulator Start-up<br>Time    |          | 10         | —   | μS    | POR, BOR or when<br>PMSLP = 1                                 |

|              |            |                                       | _        | 25         | —   | μS    | PMSLP = 0,<br>WUTSEL<1:0> = 01 <sup>(1)</sup>                 |

|              |            |                                       | _        | 190        | —   | μS    | PMSLP = 0,<br>WUTSEL<1:0> = 11 <sup>(2)</sup>                 |

|              | TPWRT      |                                       | _        | 64         |     | ms    | DISVREG = VDD                                                 |

**Note 1:** Available only in devices with a major silicon revision level of B or later (DEVREV register value is 3042h or greater).

2: WUTSELx Configuration bits setting is applicable only in devices with a major silicon revision level of B or later. This specification also applies to all devices prior to Revision Level B whenever PMSLP = 0.

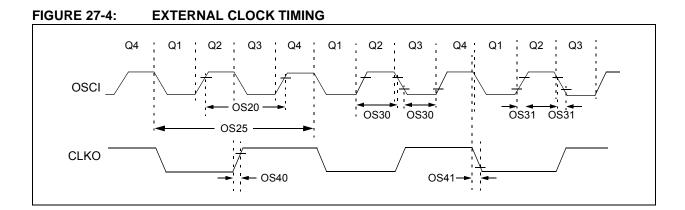

## TABLE 27-15: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CH        | ARACT | ERISTICS                              | Standard Operating ter | -                  |     | -40°C | <b>3.6V (unless otherwise stated)</b><br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended |

|--------------|-------|---------------------------------------|------------------------|--------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                        | Min                    | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                                                             |

| OS10         | Fosc  | External CLKI Frequency               | DC                     | _                  | 32  | MHz   | EC, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                             |

|              |       | (External clocks allowed              | 4                      | —                  | 8   | MHz   | ECPLL, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                          |

|              |       | only in EC mode)                      | DC                     | —                  | 24  | MHz   | EC, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                            |

|              |       |                                       | 4                      | —                  | 6   | MHz   | ECPLL, -40°C $\leq$ TA $\leq$ +125°C                                                                                   |

|              |       | Oscillator Frequency                  | 3                      | _                  | 10  | MHz   | ХТ                                                                                                                     |

|              |       |                                       | 3                      | —                  | 8   | MHz   | XTPLL, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                          |

|              |       |                                       | 10                     | —                  | 32  | MHz   | HS, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                             |

|              |       |                                       | 31                     | —                  | 33  | kHz   | SOSC                                                                                                                   |

|              |       |                                       | 3                      | —                  | 6   | MHz   | XTPLL, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                         |

|              |       |                                       | 10                     | —                  | 24  | MHz   | HS, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                            |

| OS20         | Tosc  | Tosc = 1/Fosc                         | _                      | _                  | _   | _     | See Parameter OS10 for                                                                                                 |

|              |       |                                       |                        |                    |     |       | Fosc value                                                                                                             |

| OS25         | Тсү   | Instruction Cycle Time <sup>(2)</sup> | 62.5                   | _                  | DC  | ns    |                                                                                                                        |

| OS30         | TosL, | External Clock In (OSCI)              | 0.45 x Tosc            | _                  | _   | ns    | EC                                                                                                                     |

|              | TosH  | High or Low Time                      |                        |                    |     |       |                                                                                                                        |

| OS31         | TosR, | External Clock In (OSCI)              | _                      |                    | 20  | ns    | EC                                                                                                                     |

|              | TosF  | Rise or Fall Time                     |                        |                    |     |       |                                                                                                                        |

| OS40         | TckR  | CLKO Rise Time <sup>(3)</sup>         |                        | 6                  | 10  | ns    |                                                                                                                        |

| OS41         | TckF  | CLKO Fall Time <sup>(3)</sup>         | _                      | 6                  | 10  | ns    |                                                                                                                        |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- **3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

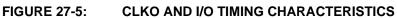

## TABLE 27-19: CLKO AND I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |      |                                       | Standard O<br>Operating te               |    | -4 | $40^{\circ}C \le TA \le$ | (unless otherwise stated)<br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|------|---------------------------------------|------------------------------------------|----|----|--------------------------|--------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                        | Min Typ <sup>(1)</sup> Max Units Conditi |    |    |                          |                                                                          |

| DO31               | TIOR | Port Output Rise Time                 | —                                        | 10 | 25 | ns                       |                                                                          |

| DO32               | TIOF | Port Output Fall Time                 | —                                        | 10 | 25 | ns                       |                                                                          |

| DI35               | Tinp | INTx Pin High or Low<br>Time (output) | 20                                       | —  | —  | ns                       |                                                                          |

| DI40               | Trbp | CNx High or Low Time (input)          | 2 — — TCY                                |    |    |                          |                                                                          |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

### TABLE 27-20: A/D MODULE SPECIFICATIONS

| АС СН        | ARACTE    | RISTICS                                              | Standard Operating te              |         |                                   | 2.0V to 3.6V (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |                                                                                                |  |

|--------------|-----------|------------------------------------------------------|------------------------------------|---------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol    | Characteristic                                       | Min.                               | Тур     | Max.                              | Units                                                                                                                               | Conditions                                                                                     |  |

|              |           |                                                      | Device                             | Supply  | /                                 |                                                                                                                                     |                                                                                                |  |

| AD01         | AVDD      | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 2.0 | —       | Lesser of:<br>VDD + 0.3<br>or 3.6 | V                                                                                                                                   |                                                                                                |  |

| AD02         | AVss      | Module Vss Supply                                    | Vss – 0.3                          | —       | Vss + 0.3                         | V                                                                                                                                   |                                                                                                |  |

|              |           |                                                      | Referen                            | ce Inpu | ts                                |                                                                                                                                     |                                                                                                |  |

| AD05         | Vrefh     | Reference Voltage High                               | AVss + 1.7                         | _       | AVdd                              | V                                                                                                                                   |                                                                                                |  |

| AD06         | Vrefl     | Reference Voltage Low                                | AVss                               | _       | AVDD – 1.7                        | V                                                                                                                                   |                                                                                                |  |

| AD07         | VREF      | Absolute Reference<br>Voltage                        | AVss – 0.3                         | _       | AVDD + 0.3                        | V                                                                                                                                   |                                                                                                |  |

| AD08         | IVREF     | Reference Voltage Input<br>Current                   | —                                  | _       | 1.25                              | mA                                                                                                                                  | Measured during conversion, 3.3V, +25°C (Note 1)                                               |  |

| AD09         | Zref      | Reference Input Impedance                            | —                                  | 10k     | —                                 | Ω                                                                                                                                   | Measured during sampling,<br>3.3V, +25°C                                                       |  |

|              |           |                                                      | Analo                              | g Input |                                   |                                                                                                                                     |                                                                                                |  |

| AD10         | VINH-VINL | Full-Scale Input Span                                | VREFL                              | _       | VREFH                             | V                                                                                                                                   | (Note 1)                                                                                       |  |

| AD11         | Vin       | Absolute Input Voltage                               | AVss - 0.3                         |         | AVDD + 0.3                        | V                                                                                                                                   |                                                                                                |  |

| AD12         | Vinl      | Absolute VINL Input Voltage                          | AVss - 0.3                         |         | AVDD/2                            | V                                                                                                                                   |                                                                                                |  |

| AD13         |           | Leakage Current                                      | _                                  | ±1      | ±610                              | nA                                                                                                                                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3V$ ,<br>Source Impedance = $2.5 \text{ k}\Omega$ |  |

| AD17         | Rin       | Recommended<br>Impedance of Analog<br>Voltage Source | _                                  | —       | 2.5K                              | Ω                                                                                                                                   | 10-bit                                                                                         |  |

|              |           |                                                      | A/D A                              | ccuracy | ,                                 |                                                                                                                                     |                                                                                                |  |

| AD20b        | Nr        | Resolution                                           |                                    | 10      | _                                 | bits                                                                                                                                |                                                                                                |  |

| AD21b        | INL       | Integral Nonlinearity                                | —                                  | ±1      | <±2                               | LSb                                                                                                                                 | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD22b        | DNL       | Differential Nonlinearity                            | —                                  | ±1      | <±1.25                            | LSb                                                                                                                                 | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD23b        | Gerr      | Gain Error                                           | —                                  | ±1      | ±3                                | LSb                                                                                                                                 | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD24b        | Eoff      | Offset Error                                         |                                    | ±1      | ±2                                | LSb                                                                                                                                 | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD25b        | _         | Monotonicity <sup>(2)</sup>                          | _                                  | _       | _                                 | _                                                                                                                                   | Guaranteed                                                                                     |  |

Note 1: Measurements are taken with external VREF+ and VREF- used as the A/D voltage reference.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

# PIC24FJ64GA004 FAMILY

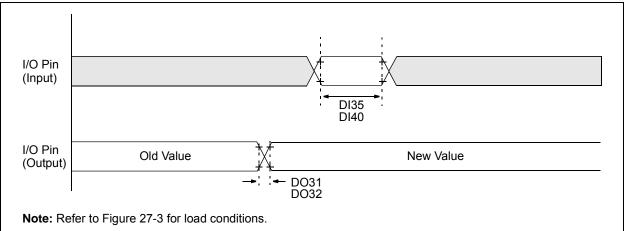

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units    | Ν    | <b>ILLIMETER</b> | S    |  |

|--------------------------|----------|------|------------------|------|--|

| Dimensior                | n Limits | MIN  | NOM              | MAX  |  |

| Contact Pitch            | E        |      | 1.27 BSC         | 0.60 |  |

| Contact Pad Spacing      | С        |      | 9.40             |      |  |

| Contact Pad Width (X28)  | X        |      |                  | 0.60 |  |

| Contact Pad Length (X28) | Y        |      |                  | 2.00 |  |

| Distance Between Pads    | Gx       | 0.67 |                  |      |  |

| Distance Between Pads    | G        | 7.40 |                  |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: