Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga004-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

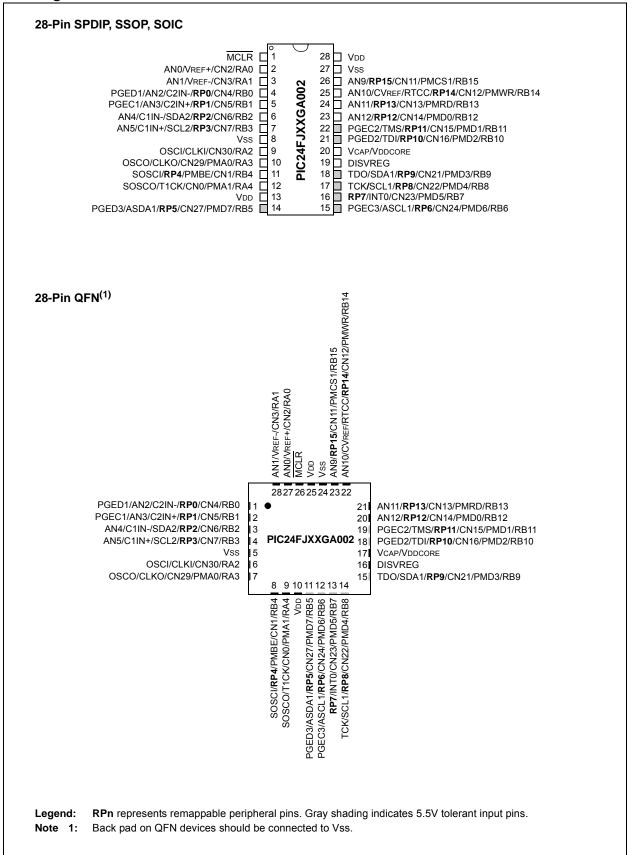

#### **Pin Diagrams**

| TABLE I-I. DEVICE FEATURE                           |                                                                                                                                                     |           | .41 0040   |             |         |          |            | 1       |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-------------|---------|----------|------------|---------|

| Features                                            | 16GA002                                                                                                                                             | 32GA002   | 48GA002    | 64GA002     | 16GA004 | 32GA004  | 48GA004    | 64GA004 |

| Operating Frequency                                 |                                                                                                                                                     | •         | •          | DC – 3      | 2 MHz   |          | •          |         |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 32K       | 48K        | 64K         | 16K     | 32K      | 48K        | 64K     |

| Program Memory (instructions)                       | 5,504                                                                                                                                               | 11,008    | 16,512     | 22,016      | 5,504   | 11,008   | 16,512     | 22,016  |

| Data Memory (bytes)                                 | 4096                                                                                                                                                |           | 8192       |             | 4096    |          | 8192       |         |

| Interrupt Sources<br>(soft vectors/NMI traps)       |                                                                                                                                                     |           |            | 4<br>(39    |         | •        |            |         |

| I/O Ports                                           |                                                                                                                                                     | Ports     | ; А, В     |             |         | Ports /  | A, B, C    |         |

| Total I/O Pins                                      |                                                                                                                                                     | 2         | 1          |             |         | 3        | 5          |         |

| Timers:                                             |                                                                                                                                                     |           |            |             |         |          |            |         |

| Total Number (16-bit)                               |                                                                                                                                                     |           |            | 5(          | 1)      |          |            |         |

| 32-Bit (from paired 16-bit timers)                  |                                                                                                                                                     |           |            | 2           |         |          |            |         |

| Input Capture Channels                              |                                                                                                                                                     |           |            | 5(          | 1)      |          |            |         |

| Output Compare/PWM Channels                         |                                                                                                                                                     |           |            | 5(          | 1)      |          |            |         |

| Input Change Notification Interrupt                 |                                                                                                                                                     | 2         | 1          |             | 30      |          |            |         |

| Serial Communications:                              |                                                                                                                                                     |           |            |             |         |          |            |         |

| UART                                                |                                                                                                                                                     |           |            | 2(          | 1)      |          |            |         |

| SPI (3-wire/4-wire)                                 | 2 <sup>(1)</sup>                                                                                                                                    |           |            |             |         |          |            |         |

| I <sup>2</sup> C™                                   | 2                                                                                                                                                   |           |            |             |         |          |            |         |

| Parallel Communications (PMP/PSP)                   |                                                                                                                                                     |           |            | Ye          | es      |          |            |         |

| JTAG Boundary Scan                                  |                                                                                                                                                     |           |            | Ye          | es      |          |            |         |

| 10-Bit Analog-to-Digital Module<br>(input channels) |                                                                                                                                                     | 10        |            |             | 13      |          |            |         |

| Analog Comparators                                  | 2                                                                                                                                                   |           |            |             |         |          |            |         |

| Remappable Pins                                     |                                                                                                                                                     | 1         | 6          |             |         | 2        | 6          |         |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |           |            |             |         |          |            |         |

| Instruction Set                                     |                                                                                                                                                     | 76 Base I | nstruction | s, Multiple | Address | ing Mode | Variations |         |

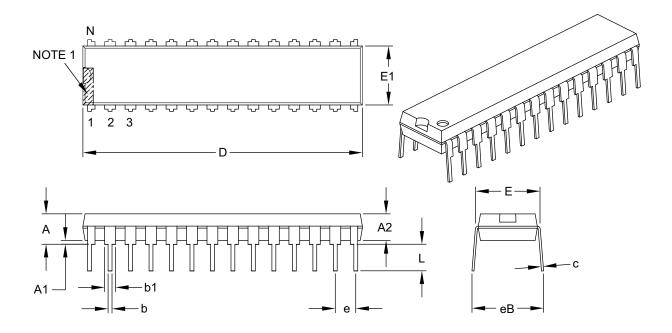

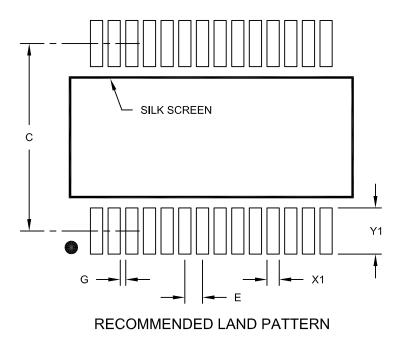

| Packages                                            | 28-Pin                                                                                                                                              | SPDIP/S   | SOP/SOI    | C/QFN       |         | 44-Pin Q | FN/TQFP    |         |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ64GA004 FAMILY

**Note 1:** Peripherals are accessible through remappable pins.

### TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          | I                             | Pin Number                                        |                    |     |                 |                                                                      |  |  |

|----------|-------------------------------|---------------------------------------------------|--------------------|-----|-----------------|----------------------------------------------------------------------|--|--|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN                                     | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                          |  |  |

| T1CK     | 12                            | 9                                                 | 34                 | Ι   | ST              | Timer1 Clock.                                                        |  |  |

| TCK      | 17                            | 14                                                | 13                 | -   | ST              | JTAG Test Clock Input.                                               |  |  |

| TDI      | 21                            | 18                                                | 35                 | -   | ST              | JTAG Test Data Input.                                                |  |  |

| TDO      | 18                            | 15                                                | 32                 | 0   | _               | JTAG Test Data Output.                                               |  |  |

| TMS      | 22                            | 19                                                | 12                 | -   | ST              | JTAG Test Mode Select Input.                                         |  |  |

| Vdd      | 13, 28                        | 10, 25                                            | 28, 40             | Р   | _               | Positive Supply for Peripheral Digital Logic and I/O Pins.           |  |  |

| VDDCAP   | 20                            | 17                                                | 7                  | Р   | _               | External Filter Capacitor Connection (regulator enabled).            |  |  |

| VDDCORE  | 20                            | 17                                                | 7                  | Р   | —               | Positive Supply for Microcontroller Core Logic (regulator disabled). |  |  |

| VREF-    | 3                             | 28                                                | 20                 | -   | ANA             | A/D and Comparator Reference Voltage (low) Input.                    |  |  |

| VREF+    | 2                             | 27                                                | 19                 | I   | ANA             | A/D and Comparator Reference Voltage (high) Input.                   |  |  |

| Vss      | 8, 27                         | 5, 24                                             | 29, 39             | Р   | —               | Ground Reference for Logic and I/O Pins.                             |  |  |

| Legend:  | TTL = TTL inp                 | TL input buffer ST = Schmitt Trigger input buffer |                    |     |                 |                                                                      |  |  |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffe  $I^2C^{TM} = I^2C/SMBus$  input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

## 3.2 CPU Control Registers

### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                  | U-0                                                                                                                                                                                                      | U-0                                                                                                                                                                     | U-0             | U-0               | U-0                | U-0               | R/W-0           |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|--------------------|-------------------|-----------------|--|--|--|--|--|

| —                    | _                                                                                                                                                                                                        | _                                                                                                                                                                       | —               | _                 |                    | _                 | DC              |  |  |  |  |  |

| bit 15               |                                                                                                                                                                                                          |                                                                                                                                                                         |                 |                   |                    |                   | bit 8           |  |  |  |  |  |

|                      |                                                                                                                                                                                                          |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                                                                                                                     | R/W-0 <sup>(1)</sup>                                                                                                                                                    | R-0             | R/W-0             | R/W-0              | R/W-0             | R/W-0           |  |  |  |  |  |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>                                                                                                                                                                                      | IPL0 <sup>(2)</sup>                                                                                                                                                     | RA              | N                 | OV                 | Z                 | С               |  |  |  |  |  |

| bit 7                |                                                                                                                                                                                                          |                                                                                                                                                                         |                 |                   |                    |                   | bit (           |  |  |  |  |  |

| Legend:              |                                                                                                                                                                                                          |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

| R = Readat           | ole bit                                                                                                                                                                                                  | W = Writable                                                                                                                                                            | oit             | U = Unimplem      | nented bit, read   | d as '0'          |                 |  |  |  |  |  |

| -n = Value a         | at POR                                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                        |                 | '0' = Bit is clea |                    | x = Bit is unki   | nown            |  |  |  |  |  |

|                      |                                                                                                                                                                                                          |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

| bit 15-9             | -                                                                                                                                                                                                        | ted: Read as '0                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

| bit 8                |                                                                                                                                                                                                          | f Carry/Borrow I                                                                                                                                                        |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          |                                                                                                                                                                         | low-order bit ( | for byte-sized da | ata) or 8th low-   | order bit (for we | ord-sized data  |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | of the result occurred<br>0 = No carry-out from the 4th or 8th low-order bit of the result has occurred                                                                 |                 |                   |                    |                   |                 |  |  |  |  |  |

| bit 7-5              | IPL<2:0>: CF                                                                                                                                                                                             | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                        |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                                                                                              |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | 110 = CPU Interrupt Priority Level is 6 (14)                                                                                                                            |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                                                                                                             |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      | 100 = CPU Interrupt Priority Level is 3 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)                                                                                                             |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      | 010 = CPU Interrupt Priority Level is 2 (10)                                                                                                                                                             |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | nterrupt Priority<br>nterrupt Priority                                                                                                                                  |                 |                   |                    |                   |                 |  |  |  |  |  |

| bit 4                |                                                                                                                                                                                                          | Loop Active bit                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | = REPEAT LOOP IN progress                                                                                                                                               |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      | 0 = REPEAT loop not in progress                                                                                                                                                                          |                                                                                                                                                                         |                 |                   |                    |                   |                 |  |  |  |  |  |

| bit 3                | N: ALU Nega                                                                                                                                                                                              | itive bit                                                                                                                                                               |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      | 1 = Result wa                                                                                                                                                                                            |                                                                                                                                                                         | , .             | <i></i> 、         |                    |                   |                 |  |  |  |  |  |

| 1.11.0               |                                                                                                                                                                                                          | as non-negative                                                                                                                                                         | (zero or posi   | tive)             |                    |                   |                 |  |  |  |  |  |

| bit 2                |                                                                                                                                                                                                          | <b>OV:</b> ALU Overflow bit                                                                                                                                             |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | <ul> <li>1 = Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation</li> <li>0 = No overflow has occurred</li> </ul>                     |                 |                   |                    |                   |                 |  |  |  |  |  |

| bit 1                | Z: ALU Zero                                                                                                                                                                                              | ALU Zero bit                                                                                                                                                            |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      | <ul> <li>1 = An operation which effects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which effects the Z bit has cleared it (i.e., a non-zero result)</li> </ul> |                                                                                                                                                                         |                 |                   |                    |                   | sult)           |  |  |  |  |  |

| bit 0                | C: ALU Carry                                                                                                                                                                                             | //Borrow bit                                                                                                                                                            |                 |                   |                    |                   |                 |  |  |  |  |  |

|                      |                                                                                                                                                                                                          | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |                 |                   |                    |                   |                 |  |  |  |  |  |

| Note 1: 7            | The IPL Status bi                                                                                                                                                                                        | its are read-only                                                                                                                                                       | when NSTD       | IS (INTCON1<1     | <b>5&gt;) =</b> 1. |                   |                 |  |  |  |  |  |

|                      | The IPL Status bi                                                                                                                                                                                        | -                                                                                                                                                                       |                 |                   |                    | n the CPU Inte    | errupt Priority |  |  |  |  |  |

| 1                    | aval (IDL) Thay                                                                                                                                                                                          | value in parenth                                                                                                                                                        | oooo indiaata   | a tha IDI when    |                    |                   | -               |  |  |  |  |  |

2: The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0               | U-0                                                                                                                                  | U-0                                                                                                                                                               | U-0   | U-0               | U-0              | U-0             | R/W-0 |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|------------------|-----------------|-------|--|

| _                 | —                                                                                                                                    | —                                                                                                                                                                 |       | —                 | —                |                 | LVDIF |  |

| bit 15            |                                                                                                                                      |                                                                                                                                                                   |       |                   |                  |                 | bit 8 |  |

|                   |                                                                                                                                      |                                                                                                                                                                   |       |                   |                  |                 |       |  |

| U-0               | U-0                                                                                                                                  | U-0                                                                                                                                                               | U-0   | R/W-0             | R/W-0            | R/W-0           | U-0   |  |

|                   |                                                                                                                                      | —                                                                                                                                                                 |       | CRCIF             | U2ERIF           | U1ERIF          |       |  |

| bit 7             |                                                                                                                                      |                                                                                                                                                                   |       |                   |                  |                 | bit C |  |

|                   |                                                                                                                                      |                                                                                                                                                                   |       |                   |                  |                 |       |  |

| Legend:           |                                                                                                                                      |                                                                                                                                                                   |       |                   |                  |                 |       |  |

| R = Readal        | ble bit                                                                                                                              | W = Writable b                                                                                                                                                    | bit   | U = Unimplem      | nented bit, read | d as '0'        |       |  |

| -n = Value a      | at POR                                                                                                                               | '1' = Bit is set                                                                                                                                                  |       | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |

| bit 15-9<br>bit 8 | LVDIF: Low-V<br>1 = Interrupt i<br>0 = Interrupt i                                                                                   | Unimplemented: Read as '0'<br>LVDIF: Low-Voltage Detect Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |       |                   |                  |                 |       |  |

| bit 7-4           | Unimplemen                                                                                                                           | ted: Read as '0                                                                                                                                                   | 3     |                   |                  |                 |       |  |

| bit 3             | 1 = Interrupt i                                                                                                                      | CRCIF: CRC Generator Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                    |       |                   |                  |                 |       |  |

| bit 2             | <b>U2ERIF:</b> UART2 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |                                                                                                                                                                   |       |                   |                  |                 |       |  |

| bit 1             | 1 = Interrupt                                                                                                                        | RT1 Error Interru<br>request has occ<br>request has not                                                                                                           | urred | ıs bit            |                  |                 |       |  |

| bit 0             | Unimplemen                                                                                                                           | ted: Read as '0                                                                                                                                                   | ,     |                   |                  |                 |       |  |

|                   |                                                                                                                                      |                                                                                                                                                                   |       |                   |                  |                 |       |  |

| U-0                                                     | U-0                                                        | U-0                                                        | U-0     | U-0              | U-0              | U-0                | U-0     |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|---------|------------------|------------------|--------------------|---------|--|--|--|--|

|                                                         | —                                                          | _                                                          | _       |                  |                  | _                  |         |  |  |  |  |

| oit 15                                                  |                                                            |                                                            |         |                  |                  |                    | bit 8   |  |  |  |  |

|                                                         |                                                            |                                                            |         |                  |                  |                    |         |  |  |  |  |

| U-0                                                     | R/W-1                                                      | R/W-0                                                      | R/W-0   | U-0              | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |

| —                                                       | SPI2IP2                                                    | SPI2IP1                                                    | SPI2IP0 | —                | SPF2IP2          | SPF2IP1            | SPF2IP0 |  |  |  |  |

| oit 7                                                   |                                                            |                                                            |         |                  |                  |                    | bit 0   |  |  |  |  |

|                                                         |                                                            |                                                            |         |                  |                  |                    |         |  |  |  |  |

| _egend:                                                 |                                                            |                                                            |         |                  |                  |                    |         |  |  |  |  |

| R = Readab                                              | ole bit                                                    | W = Writable                                               | bit     | U = Unimple      | mented bit, read | d as '0'           |         |  |  |  |  |

| -n = Value a                                            | it POR                                                     | '1' = Bit is set                                           |         | '0' = Bit is cle | eared            | x = Bit is unknown |         |  |  |  |  |

|                                                         |                                                            | (ada Daadaa (                                              | o.'     |                  |                  |                    |         |  |  |  |  |

| bit 15-7                                                | •                                                          | ted: Read as '                                             |         |                  |                  |                    |         |  |  |  |  |

| bit 6-4                                                 |                                                            | SPI2 Event In                                              |         |                  |                  |                    |         |  |  |  |  |

|                                                         | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | •                                                          |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | •                                                          |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | 001 = Interru                                              |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | 000 = Interru                                              | ot source is dis                                           | abled   |                  |                  |                    |         |  |  |  |  |

| bit 3                                                   | Unimplemen                                                 | Unimplemented: Read as '0'                                 |         |                  |                  |                    |         |  |  |  |  |

| bit 2-0 SPF2IP<2:0>: SPI2 Fault Interrupt Priority bits |                                                            |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | 111 = Interru                                              | 111 = Interrupt is Priority 7 (highest priority interrupt) |         |                  |                  |                    |         |  |  |  |  |

|                                                         | •                                                          |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | •                                                          |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         |                                                            |                                                            |         |                  |                  |                    |         |  |  |  |  |

|                                                         | 001 = Interru                                              | ot is Priority 1                                           |         |                  |                  |                    |         |  |  |  |  |

#### REGISTER 7-23: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

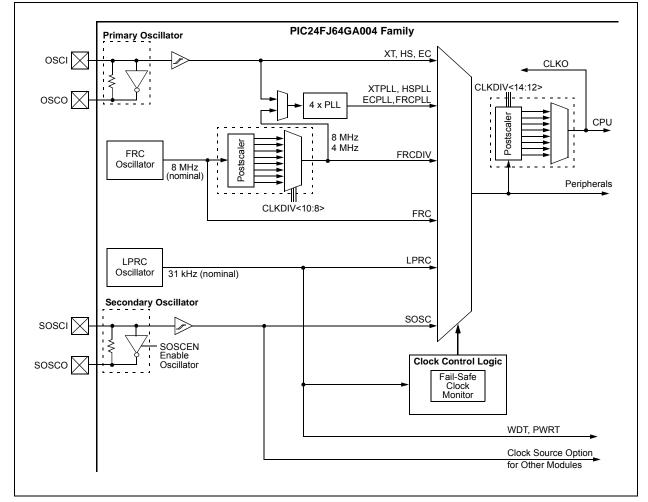

## 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | "Oscillator" (DS39700).                    |

The oscillator system for PIC24FJ64GA004 family devices has the following features:

- A total of four external and internal oscillator options as clock sources, providing 11 different clock modes

- On-chip 4x PLL to boost internal operating frequency on select internal and external oscillator sources

- Software-controllable switching between various clock sources

- Software-controllable postscaler for selective clocking of CPU for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

A simplified diagram of the oscillator system is shown in Figure 8-1.

## FIGURE 8-1: PIC24FJ64GA004 FAMILY CLOCK DIAGRAM

#### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

## 10.2 Configuring Analog Port Pins

The use of the AD1PCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 10.2.2 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages up to 5.5V, a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins are always to be avoided. Table 10-1 summarizes the input capabilities. Refer to **Section 27.1 "DC Characteristics"** for more details.

#### TABLE 10-1: INPUT VOLTAGE LEVELS

| Port or Pin    | Tolerated<br>Input | Description            |

|----------------|--------------------|------------------------|

| PORTA<4:0>     | Vdd                | Only VDD input levels  |

| PORTB<15:12>   |                    | are tolerated.         |

| PORTB<4:0>     |                    |                        |

| PORTC<2:0>(1)  |                    |                        |

| PORTA<10:7>(1) | 5.5V               | Tolerates input levels |

| PORTB<11:5>    |                    | above VDD, useful for  |

| PORTC<9:3>(1)  |                    | most standard logic.   |

Note 1: Unavailable on 28-pin devices.

## 10.3 Input Change Notification

The Input Change Notification function of the I/O ports allows the PIC24FJ64GA004 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 22 external signals that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

When the internal pull-up is selected, the pin pulls up to VDD - 0.7V (typical). Make sure that there is no external pull-up source when the internal pull-ups are enabled, as the voltage difference can cause a current path.

Note: Pull-ups on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

| EXAMPLE 10-1: | PORT WRITE/READ EXAMPLE |

|---------------|-------------------------|

|               |                         |

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; | Next Instruction                |

## 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Serial Peripheral Interface (SPI)"* (DS39699)

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the SPI and SIOP Motorola<sup>®</sup> interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 15-1 and Figure 15-2.

Depending on the pin count, PIC24FJ64GA004 family devices offer one or two SPI modules on a single device.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON1 or SPIxCON2 refers to the control register for the SPI1 or SPI2 module. To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit (SPIxCON1<9>).

- 5. If the CKE bit is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC             | R-0, HSC                                                                                           | U-0                                                                                                                                                  | U-0                     | U-0                          | R/C-0, HS          | R-0, HSC           | R-0, HSC        |  |

|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------|--------------------|--------------------|-----------------|--|

| ACKSTAT <sup>(</sup> | <sup>1)</sup> TRSTAT                                                                               | —                                                                                                                                                    | —                       | —                            | BCL                | GCSTAT             | ADD10           |  |

| bit 15               |                                                                                                    |                                                                                                                                                      |                         |                              |                    |                    | bit 8           |  |

|                      |                                                                                                    |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

| R/C-0, HS            | 8 R/C-0, HS                                                                                        | R-0, HSC                                                                                                                                             | R/C-0, HSC              | R/C-0, HSC                   | R-0, HSC           | R-0, HSC           | R-0, HSC        |  |

| IWCOL                | I2COV                                                                                              | D/A                                                                                                                                                  | Р                       | S                            | R/W                | RBF                | TBF             |  |

| bit 7                |                                                                                                    |                                                                                                                                                      | 1                       |                              |                    | •                  | bit 0           |  |

|                      |                                                                                                    |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

| Legend:              |                                                                                                    | C = Clearabl                                                                                                                                         | e bit                   | HS = Hardware                | e Settable bit     |                    |                 |  |

| R = Readal           | ole bit                                                                                            | W = Writable                                                                                                                                         | bit                     | U = Unimpleme                | ented bit, read a  | s '0'              |                 |  |

| -n = Value a         | at POR                                                                                             | '1' = Bit is se                                                                                                                                      | t                       | '0' = Bit is clear           | red                | x = Bit is unkr    | nown            |  |

| HSC = Har            | dware Settable/C                                                                                   | learable bit                                                                                                                                         |                         |                              |                    |                    |                 |  |

|                      |                                                                                                    |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

| bit 15               | ACKSTAT: Ad                                                                                        | cknowledge St                                                                                                                                        | atus bit <sup>(1)</sup> |                              |                    |                    |                 |  |

|                      |                                                                                                    | s detected las                                                                                                                                       |                         |                              |                    |                    |                 |  |

|                      | 0 = ACK was                                                                                        |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

|                      | Hardware is s                                                                                      |                                                                                                                                                      |                         | -                            |                    |                    |                 |  |

| bit 14               |                                                                                                    |                                                                                                                                                      |                         | ting as l <sup>2</sup> C™ ma | ister, applicable  | to master trans    | smit operation) |  |

|                      |                                                                                                    | ansmit is in pro                                                                                                                                     | <b>U</b>                | + ACK)                       |                    |                    |                 |  |

|                      |                                                                                                    | 0 = Master transmit is not in progress<br>Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge |                         |                              |                    |                    |                 |  |

| bit 13-11            |                                                                                                    | Unimplemented: Read as '0'                                                                                                                           |                         |                              |                    |                    |                 |  |

| bit 10               | BCL: Master                                                                                        |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

|                      |                                                                                                    |                                                                                                                                                      |                         | ing a master op              | eration            |                    |                 |  |

|                      | 0 = No collisio                                                                                    | on                                                                                                                                                   |                         |                              |                    |                    |                 |  |

|                      | Hardware is s                                                                                      | et at the dete                                                                                                                                       | ction of bus co         | ollision.                    |                    |                    |                 |  |

| bit 9                | GCSTAT: Ger                                                                                        |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

|                      |                                                                                                    | all address wa                                                                                                                                       |                         | 4                            |                    |                    |                 |  |

|                      |                                                                                                    | all address wa<br>et when an ad                                                                                                                      |                         | u<br>s the general call      | address. Hardw     | vare is clear at s | Stop detection. |  |

| bit 8                | ADD10: 10-B                                                                                        |                                                                                                                                                      |                         | stre general eau             |                    |                    |                 |  |

|                      |                                                                                                    | lress was mat                                                                                                                                        |                         |                              |                    |                    |                 |  |

|                      |                                                                                                    | lress was not                                                                                                                                        |                         |                              |                    |                    |                 |  |

|                      | Hardware is se                                                                                     | et at the match                                                                                                                                      | of the 2nd byte         | e of matched 10-b            | oit address. Hard  | ware is clear at   | Stop detection. |  |

| bit 7                | IWCOL: I2Cx Write Collision Detect bit                                                             |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

|                      | 1 = An attempt to write to the I2CxTRN register failed because the I <sup>2</sup> C module is busy |                                                                                                                                                      |                         |                              |                    |                    |                 |  |

|                      | 0 = No collisio<br>Hardware is s                                                                   |                                                                                                                                                      | rrence of a wr          | ite to I2CxTRN               | while busy (clea   | red by software    | e)              |  |

| bit 6                | 12COV: 12Cx 1                                                                                      |                                                                                                                                                      |                         |                              |                    | . ca sy convar     |                 |  |

| 211.0                |                                                                                                    |                                                                                                                                                      | -                       | CV register is sti           | Il holdina the pro | evious bvte        |                 |  |

|                      | 0 = No overflo                                                                                     |                                                                                                                                                      |                         |                              | 3 P.               |                    |                 |  |

|                      | Hardware is s                                                                                      | et at an attem                                                                                                                                       | pt to transfer          | 2CxRSR to 12C                | xRCV (cleared      | by software).      |                 |  |

| Note 1:              | n both Master an                                                                                   | d Slave mode                                                                                                                                         | s, the ACKST            | AT bit is only up            | dated when tran    | ismitting data r   | esultina in the |  |

| r                    | reception of an A<br>data, either as a s                                                           | CK or NACK f                                                                                                                                         | rom another d           | evice. Do not ch             | neck the state of  | ACKSTAT who        | en receiving    |  |

| REGISTER 17-2: | UxSTA: UARTx STATUS AND CONTROL REGISTER |

|----------------|------------------------------------------|

|----------------|------------------------------------------|

| REGISTER 1        | 17-2: UxST                                                                                                                     | A: UARTx ST                                                                         | ATUS AND                                                                | CONTROL R                                                                            | EGISTER              |                    |                   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|--------------------|-------------------|

| R/W-0             | R/W-0                                                                                                                          | R/W-0                                                                               | U-0                                                                     | R/W-0, HC                                                                            | R/W-0                | R-0                | R-1               |

| UTXISEL1          | UTXINV                                                                                                                         | UTXISEL0                                                                            | _                                                                       | UTXBRK                                                                               | UTXEN <sup>(1)</sup> | UTXBF              | TRMT              |

| bit 15            |                                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                               |                                                                         |                                                                                      |                      |                    | bit 8             |