# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A9                                                         |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.0GHz                                                                  |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                  |

| RAM Controllers                 | LPDDR2, DDR3L, DDR3                                                     |

| Graphics Acceleration           | Yes                                                                     |

| Display & Interface Controllers | HDMI, Keypad, LCD, LVDS, MIPI/DSI, Parallel                             |

| Ethernet                        | 10/100/1000Mbps (1)                                                     |

| SATA                            | SATA 3Gbps (1)                                                          |

| USB                             | USB 2.0 + PHY (3), USB 2.0 OTG + PHY (1)                                |

| Voltage - I/O                   | 1.8V, 2.5V, 2.8V, 3.3V                                                  |

| Operating Temperature           | -20°C ~ 105°C (TJ)                                                      |

| Security Features               | ARM TZ, A-HAB, CAAM, CSU, SJC, SNVS                                     |

| Package / Case                  | 624-LFBGA, FCBGA                                                        |

| Supplier Device Package         | 624-FCPBGA (21x21)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6dp5eym1aa |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. i.MX 6DualPlus/6QuadPlus Modules List ( | continued) |

|--------------------------------------------------|------------|

|--------------------------------------------------|------------|

| Block<br>Mnemonic                | Block Name                    | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|-------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRE1<br>PRE2<br>PRE3<br>PRE4     | Prefetch/Resolve<br>Engine    | Multimedia<br>Peripherals     | <ul> <li>The PRE includes the Resolve engine, Prefetch engine, and Store engine 3 blocks. The PRE key features are:</li> <li>The Resolve engine supports: <ul> <li>GPU 32bpp 4x4 standard tile, 4x4 split tile, 4x4 super tile, 4x4 super split tile format.</li> <li>GPU 16bpp 8x4 standard tile, 8x4 split tile, 8x4 super tile, 8x4 super split format.</li> <li>32/16x4 block mode and scan mode.</li> </ul> </li> <li>The prefetch engine supports: <ul> <li>Transfer of non-interleaved YUV422(NI422), non-interleaved YUV420(NI420), partial interleaved YUV422(PI422), and partial interleaved YUV420(PI420), inputs to interleaved YUV422.</li> <li>Vertical flip function both in block mode and scan mode. In block mode, vertical flip function should complete with TPR module enable.</li> <li>8bpp, 16bpp, 32bpp and 64bpp data format as generic data.</li> <li>Transfer of non-interleaved YUV444(NI444), input to interleaved YUV444 output.</li> </ul> </li> <li>The store Engine supports: 4/8/16 lines handshake modes with PRG.</li> </ul> |

| PRG1<br>PRG2                     | Prefetch/Resolve<br>Gasket    | Multimedia<br>Peripherals     | The PRG is a digital core function which works as a gasket interface<br>between the fabric and the IPU system. The primary function is to re-map<br>the ARADDR from a frame-based address to a band-based address<br>depending on the different ARIDs. The PRG also implements the<br>handshake logic with the Prefetch Resolve Engine (PRE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PMU                              | Power-Management<br>Functions | Data Path                     | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals   | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a $4x16$ data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RAM<br>512 KB                    | Internal RAM                  | Internal<br>Memory            | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ROM<br>96 KB                     | Boot ROM                      | Internal<br>Memory            | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SATA                             | Serial ATA                    | Connectivity<br>Peripherals   | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

<sup>10</sup> All digital I/O supplies (NVCC\_xxxx) must be powered under normal conditions whether the associated I/O pins are in use or not, and associated I/O pins need to have a pull-up or pull-down resistor applied to limit any floating gate current.

<sup>11</sup> This supply also powers the pre-drivers of the DDR I/O pins; therefore, it must always be provided, even when LVDS is not used.

## 4.1.4 External Clock Sources

Each i.MX 6DualPlus/6QuadPlus processor has two external input system clocks: a low frequency (RTC\_XTALI) and a high frequency (XTALI).

The RTC\_XTALI is used for low-frequency functions. It supplies the clock for wake-up circuit, power-down real time clock operation, and slow system and watchdog counters. The clock input can be connected to either an external oscillator or a crystal using the internal oscillator amplifier. Additionally, there is an internal ring oscillator, that can be used instead of RTC\_XTALI when accuracy is not important.

The system clock input XTALI is used to generate the main system clock. It supplies the PLLs and other peripherals. The system clock input can be connected to either an external oscillator or a crystal using the internal oscillator amplifier.

#### NOTE

The internal RTC oscillator does not provide an accurate frequency and is affected by process, voltage and temperature variations. Freescale strongly recommends using an external crystal as the RTC\_XTALI reference. If the internal oscillator is used instead, careful consideration should be given to the timing implications on all of the SoC modules dependent on this clock.

Table 7 shows the interface frequency requirements.

| Parameter Description               | Symbol            | Min | Тур                       | Мах | Unit |

|-------------------------------------|-------------------|-----|---------------------------|-----|------|

| RTC_XTALI Oscillator <sup>1,2</sup> | f <sub>ckil</sub> | _   | 32.768 <sup>3</sup> /32.0 | _   | kHz  |

| XTALI Oscillator <sup>4,2</sup>     | f <sub>xtal</sub> | _   | 24                        |     | MHz  |

<sup>1</sup> External oscillator or a crystal with internal oscillator amplifier.

<sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see the Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>3</sup> Recommended nominal frequency 32.768 kHz.

<sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 7 are required for use with Freescale BSPs to ensure precise time keeping and USB operation. For RTC\_XTALI operation, two clock sources are available:

- On-chip 40 kHz ring oscillator: This clock source has the following characteristics:

- Approximately 25  $\mu$ A more Idd than crystal oscillator

- Approximately  $\pm 50\%$  tolerance

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit

# 4.2 **Power Supplies Requirements and Restrictions**

The system design must comply with power-up sequence, power-down sequence, and steady state guidelines as described in this section to ensure the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the processor

# 4.2.1 Power-Up Sequence

For power-up sequence, the restrictions are as follows:

- VDD\_SNVS\_IN supply must be turned ON before any other power supply. It may be connected (shorted) with VDD\_HIGH\_IN supply.

- If a coin cell is used to power VDD\_SNVS\_IN, then ensure that it is connected before any other supply is switched on.

- If the external SRC\_POR\_B signal is used to control the processor POR, then SRC\_POR\_B must be immediately asserted at power-up and remain asserted until the VDD\_ARM\_CAP, VDD\_SOC\_CAP, and VDD\_PU\_CAP supplies are stable. VDD\_ARM\_IN and VDD\_SOC\_IN may be applied in either order with no restrictions. In the absence of an external reset feeding the SRC\_POR\_B input, the internal POR module takes control. See the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM) for further details and to ensure that all necessary requirements are being met.

- If the external SRC\_POR\_B signal is not used (always held high or left unconnected), the processor defaults to the internal POR function (where the PMU controls generation of the POR based on the power supplies). If the internal POR function is used, the following power supply requirements must be met:

- VDD\_ARM\_IN and VDD\_SOC\_IN may be supplied from the same source, or

- VDD\_SOC\_IN can be supplied before VDD\_ARM\_IN with a maximum delay of 1 ms.

### NOTE

Ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

### NOTE

USB\_OTG\_VBUS and USB\_H1\_VBUS are not part of the power supply sequence and can be powered at any time.

# 4.2.2 Power-Down Sequence

No special restrictions for i.MX 6DualPlus/6QuadPlus SoC.

# 4.2.3 Power Supplies Usage

- All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Group" column of Table 100, "21 x 21 mm Functional Contact Assignments," on page 149.

- When the SATA interface is not used, the SATA\_VP and SATA\_VPH supplies should be grounded. The input and output supplies for rest of the ports (SATA\_REXT, SATA\_PHY\_RX\_N, SATA\_PHY\_RX\_P, and SATA\_PHY\_TX\_N) can be left floating. It is recommended not to turn OFF the SATA\_VPH supply while the SATA\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, SATA\_VP and SATA\_VPH must remain powered.

- When the PCIE interface is not used, the PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX supplies should be grounded. The input and output supplies for rest of the ports (PCIE\_REXT, PCIE\_RX\_N, PCIE\_RX\_P, PCIE\_TX\_N, and PCIE\_TX\_P) can be left floating. It is recommended not to turn the PCIE\_VPH supply OFF while the PCIE\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX must remain powered.

# 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM) for details on the power tree scheme recommended operation.

### NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of their input supply ripple rejection and their on die trimming. This translates into more voltage for the die producing higher operating frequencies. These regulators have three basic modes.

- Bypass. The regulation FET is switched fully on passing the external voltage, DCDC\_LOW, to the load unaltered. The analog part of the regulator is powered down in this state, removing any loss other than the IR drop through the power grid and FET.

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

# 4.5 On-Chip Oscillators

# 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDD\_HIGH\_IN such as the oscillator consumes power from VDD\_HIGH\_IN when that supply is available and transitions to the back up battery when VDD\_HIGH\_IN is lost.

In addition, if the clock monitor determines that the OSC32K is not present, then the source of the 32 kHz clock will automatically switch to the internal ring oscillator.

### CAUTION

The internal RTC oscillator does not provide an accurate frequency and is affected by process, voltage, and temperature variations. Freescale strongly recommends using an external crystal as the RTC\_XTALI reference. If the internal oscillator is used instead, careful consideration must be given to the timing implications on all of the SoC modules dependent on this clock.

The OSC32k runs from VDD\_SNVS\_CAP, which comes from the VDD\_HIGH\_IN/VDD\_SNVS\_IN power mux. The target battery is a ~3 V coin cell. Proper choice of coin cell type is necessary for chosen VDD\_HIGH\_IN range. Appropriate series resistor (Rs) must be used when connecting the coin cell. Rs depends on the charge current limit that depends on the chosen coin cell. For example, for Panasonic ML621:

- Average Discharge Voltage is 2.5 V

- Maximum Charge Current is 0.6 mA

For a charge voltage of 3.2 V, Rs = (3.2-2.5)/0.6 m = 1.17 k

### NOTE

Always refer to the chosen coin cell manufacturer's data sheet for the latest information.

# 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 35 shows DDR I/O output buffer impedance of i.MX 6DualPlus/6QuadPlus processors.

|                            |        |                                                                                | Тур                                              |                                                  |      |

|----------------------------|--------|--------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|

| Parameter                  | Symbol | Test Conditions                                                                | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11          | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10        | Unit |

| Output Driver<br>Impedance | Rdrv   | Drive Strength (DSE) =<br>000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Ω    |

Table 35. DDR I/O Output Buffer Impedance

#### Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

2. Calibration is done against 240 W external reference resistor.

3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

# 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

# 4.8.4 MLB 6-Pin I/O Differential Output Impedance

Table 36 shows MLB 6-pin I/O differential output impedance of i.MX 6DualPlus/6QuadPlus processors.

Table 36. MLB 6-Pin I/O Differential Output Impedance

| Parameter                     | Symbol | Test Conditions | Min | Тур | Мах | Unit |

|-------------------------------|--------|-----------------|-----|-----|-----|------|

| Differential Output Impedance | ZO     | _               | 1.6 |     | _   | kΩ   |

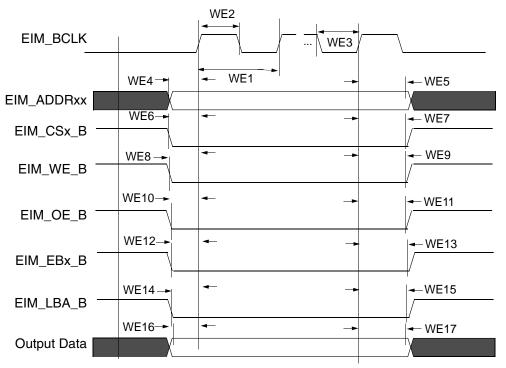

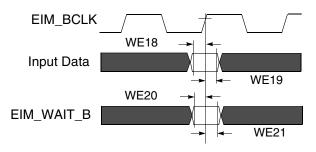

# 4.9.3.2 General EIM Timing-Synchronous Mode

Figure 12, Figure 13, and Table 40 specify the timings related to the EIM module. All EIM output control signals may be asserted and deasserted by an internal clock synchronized to the EIM\_BCLK rising edge according to corresponding assertion/negation control fields.

Figure 12. EIM Output Timing Diagram

Figure 13. EIM Input Timing Diagram

### 4.9.3.3 Examples of EIM Synchronous Accesses

Table 40. EIM Bus Timing Parameters

| ID  | Parameter                        | Min <sup>1</sup>            | Max <sup>1</sup> | Unit |

|-----|----------------------------------|-----------------------------|------------------|------|

| WE1 | EIM_BCLK cycle time <sup>2</sup> | t × (k+1)                   | —                | ns   |

| WE2 | EIM_BCLK high level width        | $0.4 \times t \times (k+1)$ | —                | ns   |

| WE3 | EIM_BCLK low level width         | $0.4 \times t \times (k+1)$ | _                | ns   |

| ID  | Parameter <sup>1,2</sup>             | Symbol | CK = 400 MHz |      | Unit |

|-----|--------------------------------------|--------|--------------|------|------|

|     |                                      |        | Min          | Мах  | Onit |

| LP1 | DRAM_SDCLKx_P clock high-level width | tсн    | 0.45         | 0.55 | tск  |

| LP2 | DRAM_SDCLKx_P clock low-level width  | tc∟    | 0.45         | 0.55 | tск  |

| LP3 | DRAM_CSx_B, DRAM_ADDRxx setup time   | tis    | 390          | —    | ps   |

| LP4 | DRAM_CSx_B, DRAM_ADDRxx hold time    | tıн    | 390          | —    | ps   |

| LP3 | DRAM_ADDRxx setup time               | tis    | 390          | —    | ps   |

| LP4 | DRAM_ADDRxx hold time                | tıн    | 390          | —    | ps   |

<sup>1</sup> All measurements are in reference to Vref level.

$^2\,$  Measurements were completed using balanced load and a 25  $\Omega$  resistor from outputs to DRAM\_VREF.

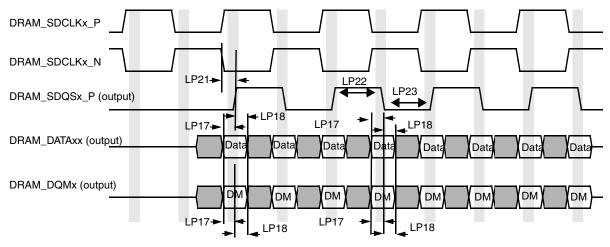

Figure 28 shows the LPDDR2 write timing diagram. The timing parameters for this diagram appear in Table 46.

Figure 28. LPDDR2 Write Cycle

#### Table 46. LPDDR2 Write Cycle

| ID   | Parameter <sup>1,2,3</sup>                                                   |        | CK = 400 MHz |      | Unit |

|------|------------------------------------------------------------------------------|--------|--------------|------|------|

|      | Farameter                                                                    | Symbol | Min          | Max  | onn  |

| LP17 | DRAM_DATAxx and DRAM_DQMx setup time to DRAM_SDQSx_P (differential strobe)   | tDS    | 370          | _    | ps   |

| LP18 | DRAM_DATAxx and DRAM_DQMx hold time to DRAM_SDQSx_P<br>(differential strobe) | tDH    | 370          | _    | ps   |

| LP21 | DRAM_SDQSx_P latching rising transitions to associated clock edges           | tDQSS  | 0.75         | 1.25 | tCK  |

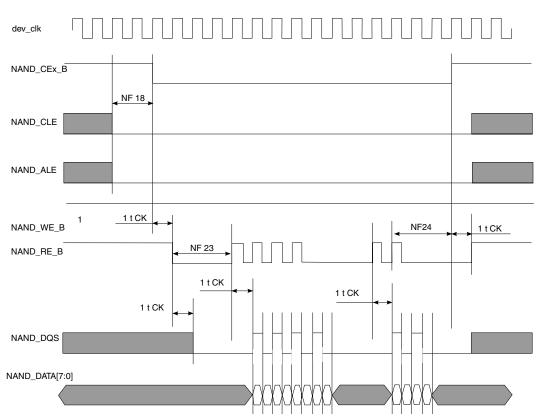

Figure 40. Samsung Toggle Mode Data Read Timing

| Table 50. Samsung Toggle Mode Timing Parameters <sup>1</sup> |                                        |        |                                                   |                       |      |  |

|--------------------------------------------------------------|----------------------------------------|--------|---------------------------------------------------|-----------------------|------|--|

| ID                                                           | Parameter                              | Symbol | Timing<br>T = GPMI Clock Cycle                    |                       | Unit |  |

|                                                              |                                        |        | Min                                               | Мах                   |      |  |

| NF1                                                          | NAND_CLE setup time                    | tCLS   | (AS + DS) × T - 0.12                              | [see <sup>2,3</sup> ] | —    |  |

| NF2                                                          | NAND_CLE hold time                     | tCLH   | DH × T - 0.72 [se                                 | e <sup>2</sup> ]      | —    |  |

| NF3                                                          | NAND_CEx_B setup time                  | tCS    | $(AS + DS) \times T - 0.58$ [see <sup>3,2</sup> ] |                       | —    |  |

| NF4                                                          | NAND_CEx_B hold time                   | tCH    | DH × T - 1 [see <sup>2</sup> ]                    |                       | —    |  |

| NF5                                                          | NAND_WE_B pulse width                  | tWP    | $DS \times T$ [see <sup>2</sup> ]                 |                       | —    |  |

| NF6                                                          | NAND_ALE setup time                    | tALS   | (AS + DS) × T - 0.49 [see <sup>3,2</sup> ]        |                       | —    |  |

| NF7                                                          | NAND_ALE hold time                     | tALH   | DH × T - 0.42 [see <sup>2</sup> ]                 |                       | —    |  |

| NF8                                                          | Command/address NAND_DATAxx setup time | tCAS   | DS × T - 0.26 [see <sup>2</sup> ]                 |                       | —    |  |

| NF9                                                          | Command/address NAND_DATAxx hold time  | tCAH   | DH × T - 1.37 [see <sup>2</sup> ]                 |                       | —    |  |

| NF18                                                         | NAND_CEx_B access time                 | tCE    | CE_DELAY × T [see <sup>4,2</sup> ]                | —                     | ns   |  |

| NF22                                                         | clock period                           | tCK    | _                                                 | _                     | ns   |  |

| NF23                                                         | preamble delay                         | tPRE   | PRE_DELAY × T [see <sup>5,2</sup> ]               | _                     | ns   |  |

| NF24                                                         | postamble delay                        | tPOST  | POST_DELAY × T +0.43 [see <sup>2</sup> ]          | _                     | ns   |  |

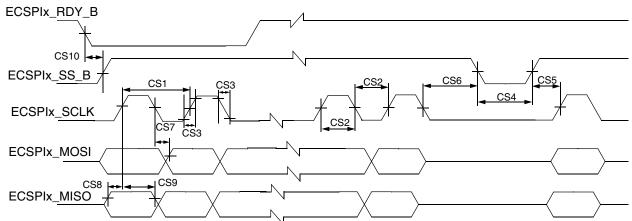

## 4.11.2.1 ECSPI Master Mode Timing

Figure 41 depicts the timing of ECSPI in master mode and Table 51 lists the ECSPI master mode timing characteristics.

Note: ECSPIx\_MOSI is always driven (not tri-stated) between actual data transmissions. This limits the ECSPI to be connected between a single master and a single slave.

#### Figure 41. ECSPI Master Mode Timing Diagram

| ID   | Parameter                                                                                                                         | Symbol                 | Min                         | Max | Unit |

|------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|-----|------|

| CS1  | ECSPIx_SCLK Cycle Time-Read<br>• Slow group <sup>1</sup><br>• Fast group <sup>2</sup><br>ECSPIx_SCLK Cycle Time-Write             | t <sub>clk</sub>       | 55<br>40<br>15              |     | ns   |

| CS2  | ECSPIx_SCLK High or Low Time-Read<br>• Slow group <sup>1</sup><br>• Fast group <sup>2</sup><br>ECSPIx_SCLK High or Low Time-Write | t <sub>SW</sub>        | 26<br>20<br>7               |     | ns   |

| CS3  | ECSPIx_SCLK Rise or Fall <sup>3</sup>                                                                                             | t <sub>RISE/FALL</sub> | _                           | _   | ns   |

| CS4  | ECSPIx_SSx pulse width                                                                                                            | t <sub>CSLH</sub>      | Half ECSPIx_SCLK period     | _   | ns   |

| CS5  | ECSPIx_SSx Lead Time (CS setup time)                                                                                              | t <sub>SCS</sub>       | Half ECSPIx_SCLK period - 4 | _   | ns   |

| CS6  | ECSPIx_SSx Lag Time (CS hold time)                                                                                                | t <sub>HCS</sub>       | Half ECSPIx_SCLK period - 2 | —   | ns   |

| CS7  | ECSPIx_MOSI Propagation Delay (C <sub>LOAD</sub> = 20 pF)                                                                         | t <sub>PDmosi</sub>    | -1                          | 1   | ns   |

| CS8  | ECSPIx_MISO Setup Time<br>• Slow group <sup>1</sup><br>• Fast group <sup>2</sup>                                                  | t <sub>Smiso</sub>     | 21.5<br>16                  |     | ns   |

| CS9  | ECSPIx_MISO Hold Time                                                                                                             | t <sub>Hmiso</sub>     | 0                           | —   | ns   |

| CS10 | ECSPIx_RDY to ECSPIx_SSx Time <sup>4</sup>                                                                                        | t <sub>SDRY</sub>      | 5                           | —   | ns   |

#### Table 51. ECSPI Master Mode Timing Parameters

<sup>1</sup> ECSPI slow includes:

ECSPI1/DISP0\_DAT22, ECSPI1/KEY\_COL1, ECSPI1/CSI0\_DAT6, ECSPI2/EIM\_OE, ECSPI2/ECSPI2/CSI0\_DAT10, ECSPI3/DISP0\_DAT2

<sup>2</sup> ECSPI fast includes:

ECSPI1/EIM\_D17, ECSPI4/EIM\_D22, ECSPI5/SD2\_DAT0, ECSPI5/SD1\_DAT0

<sup>3</sup> See specific I/O AC parameters Section 4.7, "I/O AC Parameters."

<sup>4</sup> ECSPI\_RDY is sampled internally by ipg\_clk and is asynchronous to all other CSPI signals.

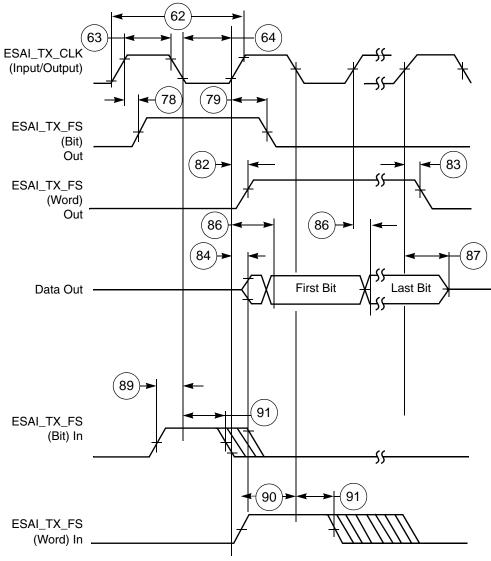

Figure 43. ESAI Transmitter Timing

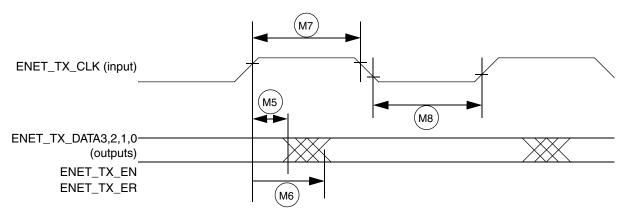

### 4.11.5.1.2 MII Transmit Signal Timing (ENET\_TX\_DATA3,2,1,0, ENET\_TX\_EN, ENET\_TX\_ER, and ENET\_TX\_CLK)

The transmitter functions correctly up to an ENET\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_TX\_CLK frequency.

Figure 49 shows MII transmit signal timings. Table 58 describes the timing parameters (M5–M8) shown in the figure.

Figure 49. MII Transmit Signal Timing Diagram

| Table 58. M | II Transmit | Signal | Timing |

|-------------|-------------|--------|--------|

|-------------|-------------|--------|--------|

| ID | Characteristic <sup>1</sup>                                           | Min | Max | Unit               |

|----|-----------------------------------------------------------------------|-----|-----|--------------------|

| M5 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER invalid | 5   | _   | ns                 |

| M6 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER valid   | _   | 20  | ns                 |

| M7 | ENET_TX_CLK pulse width high                                          | 35% | 65% | ENET_TX_CLK period |

| M8 | ENET_TX_CLK pulse width low                                           | 35% | 65% | ENET_TX_CLK period |

<sup>1</sup> ENET\_TX\_EN, ENET\_TX\_CLK, and ENET0\_TXD0 have the same timing in 10-Mbps 7-wire interface mode.

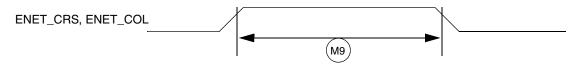

# 4.11.5.1.3 MII Asynchronous Inputs Signal Timing (ENET\_CRS and ENET\_COL)

Figure 50 shows MII asynchronous input timings. Table 59 describes the timing parameter (M9) shown in the figure.

Figure 50. MII Async Inputs Timing Diagram

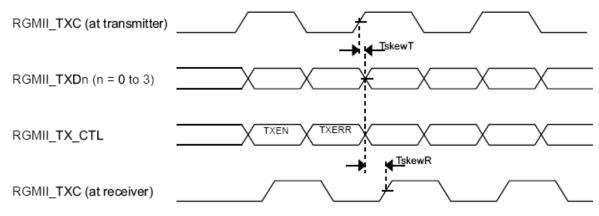

# 4.11.5.3 RGMII Signal Switching Specifications

The following timing specifications meet the requirements for RGMII interfaces for a range of transceiver devices.

| Symbol                          | Description                              | Min  | Мах  | Unit |

|---------------------------------|------------------------------------------|------|------|------|

| T <sub>cyc</sub> <sup>2</sup>   | Clock cycle duration                     | 7.2  | 8.8  | ns   |

| T <sub>skewT</sub> <sup>3</sup> | Data to clock output skew at transmitter | -100 | 900  | ps   |

| T <sub>skewR</sub> <sup>3</sup> | Data to clock input skew at receiver     | 1    | 2.6  | ns   |

| Duty_G <sup>4</sup>             | Duty cycle for Gigabit                   | 45   | 55   | %    |

| Duty_T <sup>4</sup>             | Duty cycle for 10/100T                   | 40   | 60   | %    |

| Tr/Tf                           | Rise/fall time (20–80%)                  | _    | 0.75 | ns   |

| Table 62. RGMII Signal Switching | Specifications <sup>1</sup> |

|----------------------------------|-----------------------------|

|----------------------------------|-----------------------------|

<sup>1</sup> The timings assume the following configuration: DDR\_SEL = (11)b

DSE (drive-strength) = (111)b

$^2~$  For 10 Mbps and 100 Mbps,  $T_{cyc}$  will scale to 400 ns ±40 ns and 40 ns ±4 ns respectively.

<sup>3</sup> For all versions of RGMII prior to 2.0; This implies that PC board design will require clocks to be routed such that an additional delay of greater than 1.2 ns and less than 1.7 ns will be added to the associated clock signal. For 10/100, the max value is unspecified.

<sup>4</sup> Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domain as long as minimum duty cycle is not violated and stretching occurs for no more than three Tcyc of the lowest speed transitioned between.

Figure 53. RGMII Transmit Signal Timing Diagram Original

**Electrical Characteristics**

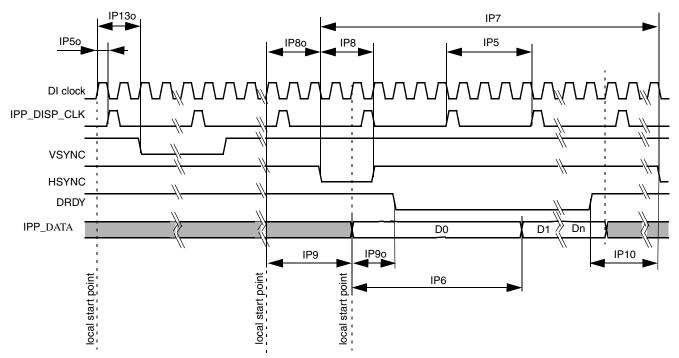

Figure 69. TFT Panels Timing Diagram—Horizontal Sync Pulse

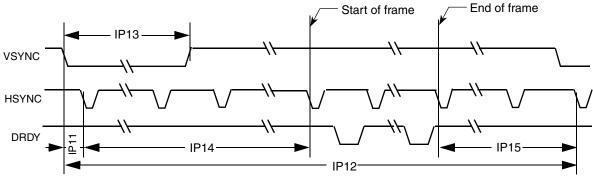

Figure 70 depicts the vertical timing (timing of one frame). All parameters shown in the figure are programmable.

Figure 70. TFT Panels Timing Diagram—Vertical Sync Pulse

| Symbol                   | Parameters                                                                    | Test Conditions               | Min | Тур | Мах  | Unit     |

|--------------------------|-------------------------------------------------------------------------------|-------------------------------|-----|-----|------|----------|

|                          | HS L                                                                          | ine Drivers DC Specifications |     |     |      | <u> </u> |

| IV <sub>OD</sub> I       | HS Transmit Differential output voltage magnitude                             | 80 Ω<= RL< = 125 Ω            | 140 | 200 | 270  | mV       |

| $\Delta  V_{OD} $        | Change in Differential output<br>voltage magnitude between<br>logic states    | 80 Ω<= RL< = 125 Ω            | _   |     | 10   | mV       |

| V <sub>CMTX</sub>        | Steady-state common-mode output voltage.                                      | 80 Ω<= RL< = 125 Ω            | 150 | 200 | 250  | mV       |

| ΔV <sub>CMTX</sub> (1,0) | Changes in steady-state<br>common-mode output voltage<br>between logic states | 80 Ω<= RL< = 125 Ω            | _   |     | 5    | mV       |

| V <sub>OHHS</sub>        | HS output high voltage                                                        | 80 Ω<= RL< = 125 Ω            | —   |     | 360  | mV       |

| Z <sub>OS</sub>          | Single-ended output impedance.                                                | _                             | 40  | 50  | 62.5 | Ω        |

| $\Delta Z_{OS}$          | Single-ended output impedance mismatch.                                       | _                             | _   |     | 10   | %        |

|                          | LPL                                                                           | ine Drivers DC Specifications |     |     |      |          |

| V <sub>OL</sub>          | Output low-level SE voltage                                                   |                               | -50 |     | 50   | mV       |

| V <sub>OH</sub>          | Output high-level SE voltage                                                  | _                             | 1.1 | 1.2 | 1.3  | V        |

| Z <sub>OLP</sub>         | Single-ended output impedance.                                                | _                             | 110 |     |      | Ω        |

| ΔZ <sub>OLP(01-10)</sub> | Single-ended output<br>impedance mismatch driving<br>opposite level           | _                             | _   | _   | 20   | %        |

| $\Delta Z_{OLP(0-11)}$   | Single-ended output<br>impedance mismatch driving<br>same level               | _                             | _   | _   | 5    | %        |

|                          | HS Li                                                                         | ne Receiver DC Specifications |     |     |      |          |

| V <sub>IDTH</sub>        | Differential input high voltage threshold                                     | _                             | —   | _   | 70   | mV       |

| V <sub>IDTL</sub>        | Differential input low voltage threshold                                      | _                             | -70 | -   | —    | mV       |

| V <sub>IHHS</sub>        | Single ended input high voltage                                               | _                             | —   | —   | 460  | mV       |

| V <sub>ILHS</sub>        | Single ended input low voltage                                                | _                             | -40 | _   | —    | mV       |

| V <sub>CMRXDC</sub>      | Input common mode voltage                                                     | _                             | 70  | —   | 330  | mV       |

| Z <sub>ID</sub>          | Differential input impedance                                                  | _                             | 80  | —   | 125  | Ω        |

### Table 72. Electrical and Timing Information (continued)

| Symbol         | Parameters                             | Test Conditions | Min | Тур | Max  | Unit |

|----------------|----------------------------------------|-----------------|-----|-----|------|------|

| L <sub>S</sub> | Equivalent wire bond series inductance | _               |     | _   | 1.5  | nH   |

| R <sub>S</sub> | Equivalent wire bond series resistance | _               |     | _   | 0.15 | Ω    |

| RL             | Load Resistance                        | _               | 80  | 100 | 125  | Ω    |

Table 73. Electrical and Timing Information (continued)

### 4.11.12.6 High-Speed Clock Timing

### 4.11.12.7 Forward High-Speed Data Transmission Timing

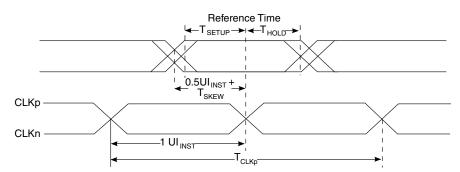

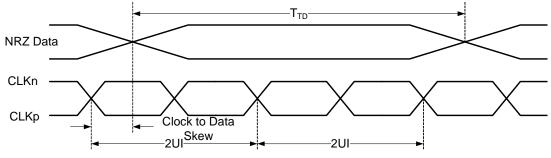

The timing relationship of the DDR Clock differential signal to the Data differential signal is shown in Figure 76:

Figure 76. Data to Clock Timing Definitions

### 4.11.12.8 Reverse High-Speed Data Transmission Timing

Figure 77. Reverse High-Speed Data Transmission Timing at Slave Side

| ID   | Parameter                      | Min   | Мах | Unit |

|------|--------------------------------|-------|-----|------|

|      | Oversampling Clock Oper        | ation |     |      |

| SS47 | Oversampling clock period      | 15.04 | _   | ns   |

| SS48 | Oversampling clock high period | 6.0   | _   | ns   |

| SS49 | Oversampling clock rise time   | —     | 3.0 | ns   |

| SS50 | Oversampling clock low period  | 6.0   |     | ns   |

| SS51 | Oversampling clock fall time   | _     | 3.0 | ns   |

#### Table 87. SSI Receiver Timing with Internal Clock (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- AUDx\_TXC and AUDx\_RXC refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

#### Package Information and Contact Assignments

|           |      |             |           |                                    | Out of Reset Co                   | ondition <sup>1</sup> |                    |

|-----------|------|-------------|-----------|------------------------------------|-----------------------------------|-----------------------|--------------------|

| Ball Name | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function<br>(Signal Name) | Input/Output          | Value <sup>2</sup> |

| EIM_A19   | G25  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_ADDR19                        | Output                | 0                  |

| EIM_A20   | H22  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_ADDR20                        | Output                | 0                  |

| EIM_A21   | H23  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_ADDR21                        | Output                | 0                  |

| EIM_A22   | F24  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_ADDR22                        | Output                | 0                  |

| EIM_A23   | J21  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_ADDR23                        | Output                | 0                  |

| EIM_A24   | F25  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_ADDR24                        | Output                | 0                  |

| EIM_A25   | H19  | NVCC_EIM0   | GPIO      | ALT0                               | EIM_ADDR25                        | Output                | 0                  |

| EIM_BCLK  | N22  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_BCLK                          | Output                | 0                  |

| EIM_CS0   | H24  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_CS0_B                         | Output                | 1                  |

| EIM_CS1   | J23  | NVCC_EIM1   | GPIO      | ALT0                               | EIM_CS1_B                         | Output                | 1                  |

| EIM_D16   | C25  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO16                        | Input                 | PU (100K)          |

| EIM_D17   | F21  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_I017                        | Input                 | PU (100K)          |

| EIM_D18   | D24  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO18                        | Input                 | PU (100K)          |

| EIM_D19   | G21  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_I019                        | Input                 | PU (100K)          |

| EIM_D20   | G20  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO20                        | Input                 | PU (100K)          |

| EIM_D21   | H20  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO21                        | Input                 | PU (100K)          |

| EIM_D22   | E23  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO22                        | Input                 | PD (100K)          |

| EIM_D23   | D25  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO23                        | Input                 | PU (100K)          |

| EIM_D24   | F22  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO24                        | Input                 | PU (100K)          |

| EIM_D25   | G22  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO25                        | Input                 | PU (100K)          |

| EIM_D26   | E24  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO26                        | Input                 | PU (100K)          |

| EIM_D27   | E25  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_I027                        | Input                 | PU (100K)          |

| EIM_D28   | G23  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO28                        | Input                 | PU (100K)          |

| EIM_D29   | J19  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO29                        | Input                 | PU (100K)          |

| EIM_D30   | J20  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO30                        | Input                 | PU (100K)          |

| EIM_D31   | H21  | NVCC_EIM0   | GPIO      | ALT5                               | GPIO3_IO31                        | Input                 | PD (100K)          |

| EIM_DA0   | L20  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD00                          | Input                 | PU (100K)          |

| EIM_DA1   | J25  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD01                          | Input                 | PU (100K)          |

| EIM_DA2   | L21  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD02                          | Input                 | PU (100K)          |

| EIM_DA3   | K24  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD03                          | Input                 | PU (100K)          |

| EIM_DA4   | L22  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD04                          | Input                 | PU (100K)          |

| EIM_DA5   | L23  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD05                          | Input                 | PU (100K)          |

| EIM_DA6   | K25  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD06                          | Input                 | PU (100K)          |

| EIM_DA7   | L25  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD07                          | Input                 | PU (100K)          |

| EIM_DA8   | L24  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD08                          | Input                 | PU (100K)          |

| EIM_DA9   | M21  | NVCC_EIM2   | GPIO      | ALT0                               | EIM_AD09                          | Input                 | PU (100K)          |

Table 100. 21 x 21 mm Functional Contact Assignments (continued)

#### Package Information and Contact Assignments

|             |      |               |           |                                    | Out of Reset Co                   | ondition <sup>1</sup> |                    |

|-------------|------|---------------|-----------|------------------------------------|-----------------------------------|-----------------------|--------------------|

| Ball Name   | Ball | Power Group   | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function<br>(Signal Name) | Input/Output          | Value <sup>2</sup> |

| LVDS0_TX3_P | W1   | NVCC_LVDS_2P5 | LVDS      | ALT0                               | LVDS0_TX3_P                       | Input                 | Keeper             |

| LVDS1_CLK_N | Y3   | NVCC_LVDS_2P5 | LVDS      | —                                  | LVDS1_CLK_N                       | _                     | —                  |

| LVDS1_CLK_P | Y4   | NVCC_LVDS_2P5 | LVDS      | ALT0                               | LVDS1_CLK_P                       | Input                 | Keeper             |

| LVDS1_TX0_N | Y1   | NVCC_LVDS_2P5 | LVDS      | —                                  | LVDS1_TX0_N                       | _                     | —                  |

| LVDS1_TX0_P | Y2   | NVCC_LVDS_2P5 | LVDS      | ALT0                               | LVDS1_TX0_P                       | Input                 | Keeper             |

| LVDS1_TX1_N | AA2  | NVCC_LVDS_2P5 | LVDS      | —                                  | LVDS1_TX1_N                       | _                     | —                  |

| LVDS1_TX1_P | AA1  | NVCC_LVDS_2P5 | LVDS      | ALT0                               | LVDS1_TX1_P                       | Input                 | Keeper             |

| LVDS1_TX2_N | AB1  | NVCC_LVDS_2P5 | LVDS      | _                                  | LVDS1_TX2_N                       | _                     | _                  |

| LVDS1_TX2_P | AB2  | NVCC_LVDS_2P5 | LVDS      | ALT0                               | LVDS1_TX2_P                       | Input                 | Keeper             |

| LVDS1_TX3_N | AA3  | NVCC_LVDS_2P5 | LVDS      | _                                  | LVDS1_TX3_N                       | —                     | _                  |

| LVDS1_TX3_P | AA4  | NVCC_LVDS_2P5 | LVDS      | ALT0                               | LVDS1_TX3_P                       | Input                 | Keeper             |

| MLB_CN      | A11  | VDD_HIGH_CAP  | LVDS      | _                                  | MLB_CLK_N                         | —                     | _                  |

| MLB_CP      | B11  | VDD_HIGH_CAP  | LVDS      | _                                  | MLB_CLK_P                         | _                     | _                  |

| MLB_DN      | B10  | VDD_HIGH_CAP  | LVDS      | _                                  | MLB_DATA_N                        | _                     | _                  |

| MLB_DP      | A10  | VDD_HIGH_CAP  | LVDS      | _                                  | MLB_DATA_P                        | _                     | _                  |

| MLB_SN      | A9   | VDD_HIGH_CAP  | LVDS      | _                                  | MLB_SIG_N                         | —                     | _                  |

| MLB_SP      | B9   | VDD_HIGH_CAP  | LVDS      | _                                  | MLB_SIG_P                         | _                     | _                  |

| NANDF_ALE   | A16  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_I008                        | Input                 | PU (100K)          |

| NANDF_CLE   | C15  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_IO07                        | Input                 | PU (100K)          |

| NANDF_CS0   | F15  | NVCC_NANDF    | GPIO      | ALT5                               | GPI06_I011                        | Input                 | PU (100K)          |

| NANDF_CS1   | C16  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_IO14                        | Input                 | PU (100K)          |

| NANDF_CS2   | A17  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_IO15                        | Input                 | PU (100K)          |

| NANDF_CS3   | D16  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_IO16                        | Input                 | PU (100K)          |

| NANDF_D0    | A18  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO00                        | Input                 | PU (100K)          |

| NANDF_D1    | C17  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO01                        | Input                 | PU (100K)          |

| NANDF_D2    | F16  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO02                        | Input                 | PU (100K)          |

| NANDF_D3    | D17  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO03                        | Input                 | PU (100K)          |

| NANDF_D4    | A19  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO04                        | Input                 | PU (100K)          |

| NANDF_D5    | B18  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO05                        | Input                 | PU (100K)          |

| NANDF_D6    | E17  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO06                        | Input                 | PU (100K)          |

| NANDF_D7    | C18  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO2_IO07                        | Input                 | PU (100K)          |

| NANDF_RB0   | B16  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_IO10                        | Input                 | PU (100K)          |

| NANDF_WP_B  | E15  | NVCC_NANDF    | GPIO      | ALT5                               | GPIO6_IO09                        | Input                 | PU (100K)          |

| ONOFF       | D12  | VDD_SNVS_IN   | GPIO      | —                                  | SRC_ONOFF                         | Input                 | PU (100K)          |

| PCIE_RXM    | B1   | PCIE_VPH      | _         |                                    | PCIE_RX_N                         | _                     | —                  |

| PCIE_RXP    | B2   | PCIE_VPH      | —         |                                    | PCIE_RX_P                         | —                     | —                  |

Table 100. 21 x 21 mm Functional Contact Assignments (continued)

#### Package Information and Contact Assignments

<sup>3</sup> ENET\_REF\_CLK is used as a clock source for MII and RGMII modes only. RMII mode uses either GPIO\_16 or RGMII\_TX\_CTL as a clock source. For more information on these clocks, see your specific device reference manual and the *Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors* (IMX6DQ6SDLHDG).

For most of the signals, the state during reset is same as the state after reset, given in Out of Reset Condition column of Table 100. However, there are few signals for which the state during reset is different from the state after reset. These signals along with their state during reset are given in Table 101.

| Ball Name | Before Reset State |           |  |  |  |

|-----------|--------------------|-----------|--|--|--|

|           | Input/Output       | Value     |  |  |  |

| EIM_A16   | Input              | PD (100K) |  |  |  |

| EIM_A17   | Input              | PD (100K) |  |  |  |

| EIM_A18   | Input              | PD (100K) |  |  |  |

| EIM_A19   | Input              | PD (100K) |  |  |  |

| EIM_A20   | Input              | PD (100K) |  |  |  |

| EIM_A21   | Input              | PD (100K) |  |  |  |

| EIM_A22   | Input              | PD (100K) |  |  |  |

| EIM_A23   | Input              | PD (100K) |  |  |  |

| EIM_A24   | Input              | PD (100K) |  |  |  |

| EIM_A25   | Input              | PD (100K) |  |  |  |

| EIM_DA0   | Input              | PD (100K) |  |  |  |

| EIM_DA1   | Input              | PD (100K) |  |  |  |

| EIM_DA2   | Input              | PD (100K) |  |  |  |

| EIM_DA3   | Input              | PD (100K) |  |  |  |

| EIM_DA4   | Input              | PD (100K) |  |  |  |

| EIM_DA5   | Input              | PD (100K) |  |  |  |

| EIM_DA6   | Input              | PD (100K) |  |  |  |

| EIM_DA7   | Input              | PD (100K) |  |  |  |

| EIM_DA8   | Input              | PD (100K) |  |  |  |

| EIM_DA9   | Input              | PD (100K) |  |  |  |

| EIM_DA10  | Input              | PD (100K) |  |  |  |

| EIM_DA11  | Input              | PD (100K) |  |  |  |

| EIM_DA12  | Input              | PD (100K) |  |  |  |

| EIM_DA13  | Input              | PD (100K) |  |  |  |

| EIM_DA14  | Input              | PD (100K) |  |  |  |

| EIM_DA15  | Input              | PD (100K) |  |  |  |

Table 101. Signals with Differing Before Reset and After Reset States