# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A9                                                         |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                                          |

| Speed                           | 1.0GHz                                                                  |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                  |

| RAM Controllers                 | LPDDR2, DDR3L, DDR3                                                     |

| Graphics Acceleration           | Yes                                                                     |

| Display & Interface Controllers | HDMI, Keypad, LCD, LVDS, MIPI/DSI, Parallel                             |

| Ethernet                        | 10/100/1000Mbps (1)                                                     |

| SATA                            | SATA 3Gbps (1)                                                          |

| USB                             | USB 2.0 + PHY (3), USB 2.0 OTG + PHY (1)                                |

| Voltage - I/O                   | 1.8V, 2.5V, 2.8V, 3.3V                                                  |

| Operating Temperature           | -40°C ~ 125°C (TJ)                                                      |

| Security Features               | ARM TZ, A-HAB, CAAM, CSU, SJC, SNVS                                     |

| Package / Case                  | 624-FBGA, FCBGA                                                         |

| Supplier Device Package         | 624-FCBGA (21x21)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6qp6avt1aa |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Ordering Information

Table 1 shows examples of orderable part numbers covered by this data sheet. This table does not include all possible orderable part numbers. The latest part numbers are available on freescale.com/imx6series. If your desired part number is not listed in the table, or you have questions about available parts, see freescale.com/imx6series or contact your Freescale representative.

| Part Number     | Quad/Dual      | CPU Options           | Speed <sup>1</sup> | Temperature Grade | Package                                         |

|-----------------|----------------|-----------------------|--------------------|-------------------|-------------------------------------------------|

| MCIMX6DP4AVT8AA | i.MX 6DualPlus | no VPU                | 852 MHz            | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6DP6AVT8AA | i.MX 6DualPlus | Full Featured Product | 852 MHz            | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6DP4AVT1AA | i.MX 6DualPlus | no VPU                | 1 GHz              | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6DP6AVT1AA | i.MX 6DualPlus | Full Featured Product | 1 GHz              | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6QP4AVT8AA | i.MX 6QuadPlus | no VPU                | 852 MHz            | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6QP6AVT8AA | i.MX 6QuadPlus | Full Featured Product | 852 MHz            | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6QP4AVT1AA | i.MX 6QuadPlus | no VPU                | 1 GHz              | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6QP6AVT1AA | i.MX 6QuadPlus | Full Featured Product | 1 GHz              | Automotive        | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

Table 1. Example Orderable Part Numbers

<sup>1</sup> If a 24 MHz input clock is used (required for USB), the maximum speed is limited to 996 MHz.

Figure 1 describes the part number nomenclature to identify the characteristics of the specific part number you have (for example, cores, frequency, temperature grade, fuse options, silicon revision). Figure 1 applies to the i.MX 6DualPlus/6QuadPlus.

The two characteristics that identify which data sheet a specific part applies to are the part number series field and the temperature grade (junction) field:

- The i.MX 6DualPlus/6QuadPlus Automotive Applications Processors data sheet (IMX6DQPAEC) covers parts listed for the "Plus" series and with "A" indicating automotive temperature.

- The i.MX 6DualPlus/6QuadPlus Applications Processors for Consumer Products data sheet (IMX6DQPCEC) covers parts listed with "D (Commercial temp)" or "E (Extended Commercial temp)"

- The i.MX 6DualPlus/6QuadPlus Applications Processors for Industrial Products data sheet (IMX6DQPIEC) covers parts listed with "C (Industrial temp)"

Ensure that you have the right data sheet for your specific part by checking the fields: Part # Series (DP/QP), temperature grade (junction) (A), and Frequency (8).

| Block<br>Mnemonic                                              | Block Name                                    | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------|-----------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPU2Dv3                                                        | Graphics Processing<br>Unit-2D, ver. 3        | Multimedia<br>Peripherals        | The GPU2Dv3 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPU3Dv6                                                        | Graphics Processing<br>Unit-3D, ver. 6        | Multimedia<br>Peripherals        | The GPU2Dv6 provides hardware acceleration for 3D graphics algorithms with sufficient processor power to run desktop quality interactive graphics applications on displays up to HD1080 resolution. The GPU3D provides OpenGL ES 3.0, including extensions, OpenGL ES 2.0, OpenGL ES 1.1, and OpenVG 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GPUVGv2                                                        | Vector Graphics<br>Processing Unit,<br>ver. 2 | Multimedia<br>Peripherals        | OpenVG graphics accelerator provides OpenVG 1.1 support as well as<br>other accelerations, including Real-time hardware curve tesselation of<br>lines, quadratic and cubic Bezier curves, 16x Line Anti-aliasing, and<br>various Vector Drawing functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HDMI Tx                                                        | HDMI Tx interface                             | Multimedia<br>Peripherals        | The HDMI module provides HDMI standard interface port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HSI                                                            | MIPI HSI interface                            | Connectivity<br>Peripherals      | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| l <sup>2</sup> C-1<br>l <sup>2</sup> C-2<br>l <sup>2</sup> C-3 | I <sup>2</sup> C Interface                    | Connectivity<br>Peripherals      | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IOMUXC                                                         | IOMUX Control                                 | System<br>Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IPUv3H-1<br>IPUv3H-2                                           | Image Processing<br>Unit, ver. 3H             | Multimedia<br>Peripherals        | <ul> <li>IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation.</li> <li>The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces:</li> <li>Parallel Interfaces for both display and camera</li> <li>Single/dual channel LVDS display interface</li> <li>HDMI transmitter</li> <li>MIPI/DSI transmitter</li> <li>MIPI/CSI-2 receiver</li> <li>The processing includes:</li> <li>Image conversions: resizing, rotation, inversion, and color space conversion</li> <li>A high-quality de-interlacing filter</li> <li>Video/graphics combining</li> <li>Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement</li> <li>Support for display backlight reduction</li> </ul> |

| KPP                                                            | Key Pad Port                                  | Connectivity<br>Peripherals      | <ul> <li>KPP Supports 8 x 8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 8. Maxim | um Supply Currents | s (continued) |

|----------------|--------------------|---------------|

|----------------|--------------------|---------------|

| Dower Comple | Conditions | Maximum C                                                                                                                                          | 11       |      |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--|

| Power Supply | Conditions | Power Virus                                                                                                                                        | CoreMark | Unit |  |

| NVCC_LVDS2P5 | _          | NVCC_LVDS2P5 is connected to<br>VDD_HIGH_CAP at the board<br>level. VDD_HIGH_CAP is capable<br>of handing the current required by<br>NVCC_LVDS2P5. |          |      |  |

|              | MISC       |                                                                                                                                                    |          |      |  |

| DRAM_VREF    | —          | 1                                                                                                                                                  |          | mA   |  |

<sup>1</sup> i.MX 6DualPlus numbers assume VDD\_ARM23\_IN and VDD\_ARM23\_CAP are connected to ground.

<sup>2</sup> The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI, PCIe, and SATA VPH supplies).

<sup>3</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown Table 8. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

<sup>4</sup> This is the maximum current per active USB physical interface.

- <sup>5</sup> The DRAM power consumption is dependent on several factors such as external signal termination. DRAM power calculators are typically available from memory vendors which take into account factors such as signal termination. See the *i.MX 6Dual/6Quad Power Consumption Measurement Application Note* (AN4509) for examples of DRAM power consumption during specific use case scenarios.

- <sup>6</sup> General equation for estimated, maximum power consumption of an IO power supply: Imax = N x C x V x (0.5 x F)

Where:

N—Number of IO pins supplied by the power line

C-Equivalent external capacitive load

V—IO voltage

(0.5 xF)-Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

## 4.1.6 Low Power Mode Supply Currents

Table 9 shows the current core consumption (not including I/O) of the i.MX 6DualPlus/6QuadPlus processors in selected low power modes.

| Mode                      | Test Conditions                                                                                                                                                                                                 | Supply              | Typical <sup>1</sup> | Unit |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|

| WAIT                      | <ul> <li>WAIT</li> <li>ARM, SoC, and PU LDOs are set to 1.225 V</li> <li>HIGH LDO set to 2.5 V</li> <li>Clocks are gated</li> <li>DDR is in self refresh</li> <li>PLLs are active in bypass (24 MHz)</li> </ul> | VDD_ARM_IN (1.4 V)  | 6                    | mA   |

|                           |                                                                                                                                                                                                                 | VDD_SOC_IN (1.4 V)  | 23                   | mA   |

|                           |                                                                                                                                                                                                                 | VDD_HIGH_IN (3.0 V) | 3.7                  | mA   |

| Supply voltages remain ON | Total                                                                                                                                                                                                           | 52                  | mW                   |      |

#### Table 9. Stop Mode Current and Power Consumption

## 4.4.3 Ethernet PLL

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 500 MHz                 |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

#### Table 16. Ethernet PLL Electrical Parameters

### 4.4.4 480 MHz PLL

#### Table 17. 480 MHz PLL Electrical Parameters

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

### 4.4.5 MLB PLL

The MediaLB PLL is necessary in the MediaLB 6-Pin implementation to phase align the internal and external clock edges, effectively tuning out the delay of the differential clock receiver and is also responsible for generating the higher speed internal clock, when the internal-to-external clock ratio is not 1:1.

#### Table 18. MLB PLL Electrical Parameters

| Parameter | Value   |

|-----------|---------|

| Lock time | <1.5 ms |

## 4.4.6 ARM PLL

#### Table 19. ARM PLL Electrical Parameters

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 650 MHz~1.3 GHz        |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

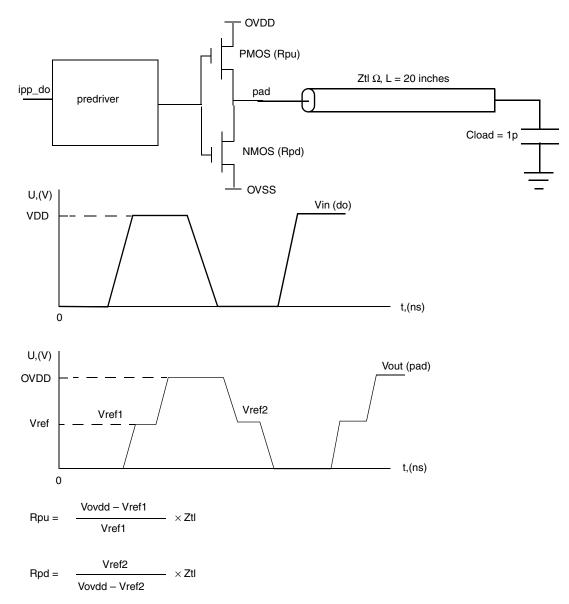

Figure 9. Impedance Matching Load for Measurement

| ID   | Parameter <sup>1,2,3</sup>    | Symbol        | CK = 400 MHz |     | Unit |

|------|-------------------------------|---------------|--------------|-----|------|

|      |                               |               | Min          | Max | Unit |

| LP22 | DRAM_SDQSx_P high level width | <b>t</b> DQSH | 0.4          |     | tCK  |

| LP23 | DRAM_SDQSx_P low level width  | tDQSL         | 0.4          | _   | tCK  |

#### Table 46. LPDDR2 Write Cycle (continued)

<sup>1</sup> To receive the reported setup and hold values, the write calibration must be performed to locate the DRAM\_SDQSx\_P in the middle of DRAM\_DATAxx window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3$  Measurements were completed using balanced load and a 25  $\Omega$  resistor from outputs to DRAM\_VREF.

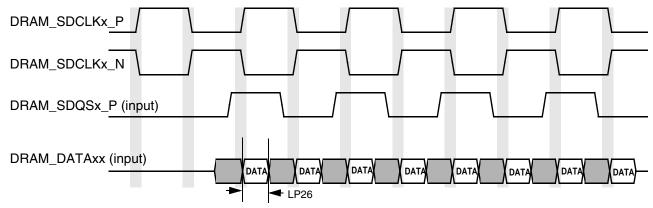

Figure 29 shows the LPDDR2 read timing diagram. The timing parameters for this diagram appear in Table 47.

Figure 29. LPDDR2 Read Cycle

#### Table 47. LPDDR2 Read Cycle

| ID   | Parameter <sup>1,2,3</sup>                                 | Symbol | CK = 40 | Unit |      |

|------|------------------------------------------------------------|--------|---------|------|------|

|      | i di dificici                                              | Cymbol | Min     | Max  | Onit |

| LP26 | Minimum required DRAM_DATAxx valid window width for LPDDR2 |        | 330     |      | ps   |

<sup>1</sup> To receive the reported setup and hold values, read calibration must be performed to locate the DRAM\_SDQSx\_P in the middle of DRAM\_DATAxx window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3$  Measurements were completed using balanced load and a 25  $\Omega$  resistor from outputs to DRAM\_VREF.

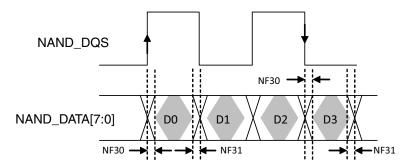

## 4.10 General-Purpose Media Interface (GPMI) Timing

The i.MX 6DualPlus/6QuadPlus GPMI controller is a flexible interface NAND Flash controller with 8-bit data width, up to 200 MB/s I/O speed and individual chip select. It supports Asynchronous timing mode, Source Synchronous timing mode, and Samsung Toggle timing mode separately described in the following subsections.

## 4.10.1 Asynchronous Mode AC Timing (ONFI 1.0 Compatible)

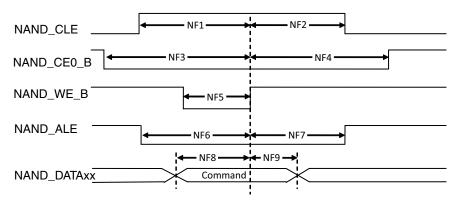

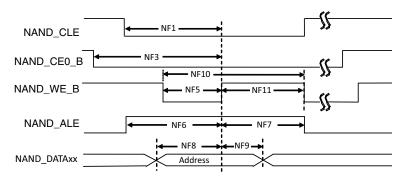

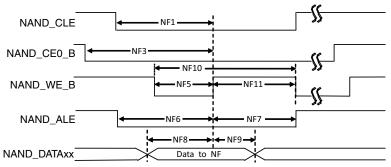

Asynchronous mode AC timings are provided as multiplications of the clock cycle and fixed delay. The Maximum I/O speed of GPMI in Asynchronous mode is about 50 MB/s. Figure 30 through Figure 33 depict the relative timing between GPMI signals at the module level for different operations under Asynchronous mode. Table 48 describes the timing parameters (NF1–NF17) that are shown in the figures.

Figure 30. Command Latch Cycle Timing Diagram

Figure 31. Address Latch Cycle Timing Diagram

| ID   | Parameter          | Symbol | Timing<br>T = GPMI Clock Cycle   |                                                   | Unit |

|------|--------------------|--------|----------------------------------|---------------------------------------------------|------|

|      |                    |        | Min                              | Мах                                               |      |

| NF16 | Data setup on read | tDSR   | _                                | (DS $\times\text{T}$ -0.67)/18.38 [see $^{5,6}$ ] | ns   |

| NF17 | Data hold on read  | tDHR   | 0.82/11.83 [see <sup>5,6</sup> ] | _                                                 | ns   |

#### Table 48. Asynchronous Mode Timing Parameters<sup>1</sup> (continued)

The GPMI asynchronous mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = GPMI clock period -0.075ns (half of maximum p-p jitter).

<sup>4</sup> NF12 is met automatically by the design.

<sup>5</sup> Non-EDO mode.

1

<sup>6</sup> EDO mode, GPMI clock ≈ 100 MHz (AS=DS=DH=1, GPMI\_CTL1 [RDN\_DELAY] = 8, GPMI\_CTL1 [HALF\_PERIOD] = 0).

In EDO mode (Figure 34), NF16/NF17 are different from the definition in non-EDO mode (Figure 33). They are called tREA/tRHOH (NAND\_RE\_B access time/NAND\_RE\_B HIGH to output hold). The typical value for them are 16 ns (max for tREA)/15 ns (min for tRHOH) at 50 MB/s EDO mode. In EDO mode, GPMI will sample NAND\_DATAxx at rising edge of delayed NAND\_RE\_B provided by an internal DPLL. The delay value can be controlled by GPMI\_CTRL1.RDN\_DELAY (see the GPMI chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM)). The typical value of this control register is 0x8 at 50 MT/s EDO mode. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

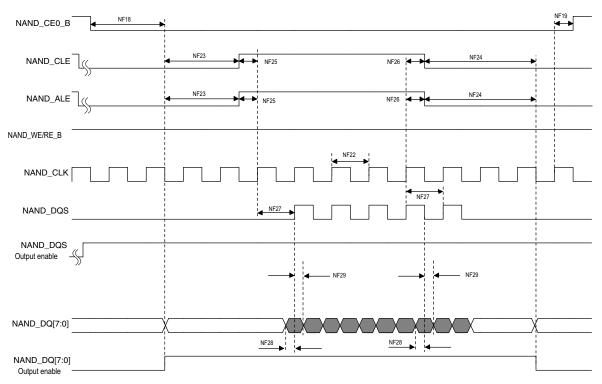

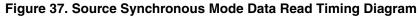

Figure 38. NAND\_DQS/NAND\_DQ Read Valid Window

| ID   | D Parameter                                    |       | Timin<br>T = GPMI Clo                          | Unit                       |    |

|------|------------------------------------------------|-------|------------------------------------------------|----------------------------|----|

|      |                                                |       | Min                                            | Max                        |    |

| NF18 | NAND_CEx_B access time                         | tCE   | CE_DELAY × T - 0.79 [see <sup>2</sup> ]        |                            | ns |

| NF19 | NAND_CEx_B hold time                           | tCH   | 0.5 × tCK - 0.6                                | 63 [see <sup>2</sup> ]     | ns |

| NF20 | Command/address NAND_DATAxx setup time         | tCAS  | 0.5 	imes tCK ·                                | 0.05                       | ns |

| NF21 | Command/address NAND_DATAxx hold time          | tCAH  | 0.5 × tCK - 1.23                               |                            | ns |

| NF22 | clock period                                   | tCK   | —                                              |                            | ns |

| NF23 | preamble delay                                 | tPRE  | PRE_DELAY $	imes$ T - 0.29 [see <sup>2</sup> ] |                            | ns |

| NF24 | postamble delay                                | tPOST | $POST_DELAY \times T$                          | - 0.78 [see <sup>2</sup> ] | ns |

| NF25 | NAND_CLE and NAND_ALE setup time               | tCALS | 0.5 	imes tCK ·                                | 0.86                       | ns |

| NF26 | NAND_CLE and NAND_ALE hold time                | tCALH | 0.5 	imes tCK ·                                | 0.37                       | ns |

| NF27 | NAND_CLK to first NAND_DQS latching transition | tDQSS | T - 0.41 [see <sup>2</sup> ]                   |                            | ns |

| NF28 | Data write setup                               | tDS   | 0.25 × tCK - 0.35                              |                            | —  |

| NF29 | Data write hold                                |       | 0.25 × tCK - 0.85                              |                            | —  |

| NF30 | NAND_DQS/NAND_DQ read setup skew               | tDQSQ | — 2.06                                         |                            | —  |

| NF31 | NAND_DQS/NAND_DQ read hold skew                | tQHS  | _                                              | 1.95                       | —  |

Table 49. Source Synchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> The GPMI source synchronous mode output timing can be controlled by the module's internal registers GPMI\_TIMING2\_CE\_DELAY, GPMI\_TIMING\_PREAMBLE\_DELAY, GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers settings. In the table, CE\_DELAY/PRE\_DELAY/POST\_DELAY represents each of these settings.

<sup>2</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

Figure 38 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. For Source Synchronous mode, the typical value of tDQSQ is 0.85 ns (max) and 1 ns (max) for tQHS at 200MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of a delayed NAND\_DQS signal, which can be provided by an internal DPLL. The delay value can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM)). Generally, the typical delay value of this register is equal to 0x7 which means 1/4 clock cycle delay expected. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

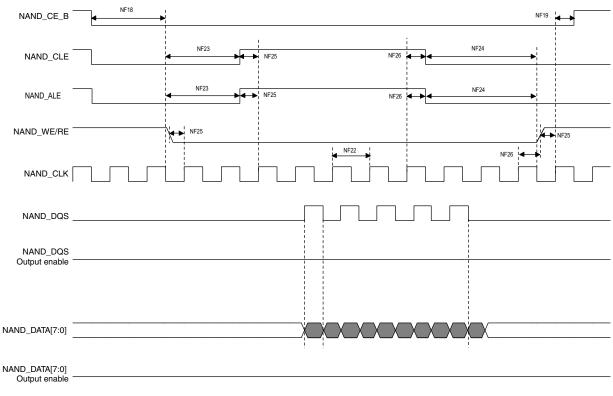

Figure 40. Samsung Toggle Mode Data Read Timing

| Table 50. Samsung Toggle Mode Timing Parameters <sup>1</sup> |                                        |       |                                          |                       |      |  |  |  |

|--------------------------------------------------------------|----------------------------------------|-------|------------------------------------------|-----------------------|------|--|--|--|

| ID                                                           | Parameter                              |       | Timing<br>T = GPMI Clock C               | Cycle                 | Unit |  |  |  |

|                                                              |                                        |       | Min                                      | Мах                   |      |  |  |  |

| NF1                                                          | NAND_CLE setup time                    | tCLS  | (AS + DS) × T - 0.12                     | [see <sup>2,3</sup> ] | —    |  |  |  |

| NF2                                                          | NAND_CLE hold time                     | tCLH  | DH × T - 0.72 [se                        | e <sup>2</sup> ]      | —    |  |  |  |

| NF3                                                          | NAND_CEx_B setup time                  | tCS   | (AS + DS) × T - 0.58                     | [see <sup>3,2</sup> ] | —    |  |  |  |

| NF4                                                          | NAND_CEx_B hold time                   | tCH   | DH × T - 1 [see                          | 2]                    | —    |  |  |  |

| NF5                                                          | NAND_WE_B pulse width                  | tWP   | DS × T [see <sup>2</sup> ]               |                       | —    |  |  |  |

| NF6                                                          | NAND_ALE setup time                    | tALS  | (AS + DS) × T - 0.49                     | [see <sup>3,2</sup> ] | —    |  |  |  |

| NF7                                                          | NAND_ALE hold time                     | tALH  | DH × T - 0.42 [se                        | e <sup>2</sup> ]      | —    |  |  |  |

| NF8                                                          | Command/address NAND_DATAxx setup time | tCAS  | DS × T - 0.26 [se                        | e <sup>2</sup> ]      | —    |  |  |  |

| NF9                                                          | Command/address NAND_DATAxx hold time  | tCAH  | DH × T - 1.37 [se                        | e <sup>2</sup> ]      | —    |  |  |  |

| NF18                                                         | NAND_CEx_B access time                 | tCE   | CE_DELAY × T [see <sup>4,2</sup> ]       | —                     | ns   |  |  |  |

| NF22                                                         | clock period                           | tCK   | _                                        | _                     | ns   |  |  |  |

| NF23                                                         | preamble delay                         | tPRE  | PRE_DELAY × T [see <sup>5,2</sup> ]      | _                     | ns   |  |  |  |

| NF24                                                         | postamble delay                        | tPOST | POST_DELAY × T +0.43 [see <sup>2</sup> ] | _                     | ns   |  |  |  |

| ID   | Parameter                        |                    | Timing<br>T = GPMI Clock C | Cycle | Unit |

|------|----------------------------------|--------------------|----------------------------|-------|------|

|      |                                  |                    | Min                        | Max   |      |

| NF28 | Data write setup                 | tDS <sup>6</sup>   | 0.25 × tCK - 0.32          | —     | ns   |

| NF29 | Data write hold                  | tDH <sup>6</sup>   | 0.25 × tCK - 0.79          | —     | ns   |

| NF30 | NAND_DQS/NAND_DQ read setup skew | tDQSQ <sup>7</sup> | —                          | 3.18  | —    |

| NF31 | NAND_DQS/NAND_DQ read hold skew  | tQHS <sup>7</sup>  | —                          | 3.27  | —    |

#### Table 50. Samsung Toggle Mode Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> The GPMI toggle mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

<sup>4</sup> CE\_DELAY represents HW\_GPMI\_TIMING2[CE\_DELAY]. NF18 is met automatically by the design. Read/Write operation is started with enough time of ALE/CLE assertion to low level.

<sup>5</sup> PRE\_DELAY+1)  $\geq$  (AS+DS)

<sup>6</sup> Shown in Figure 36.

<sup>7</sup> Shown in Figure 37.

Figure 38 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. For DDR Toggle mode, the typical value of tDQSQ is 1.4 ns (max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of a delayed NAND\_DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM)). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

## 4.11 External Peripheral Interface Parameters

The following subsections provide information on external peripheral interfaces.

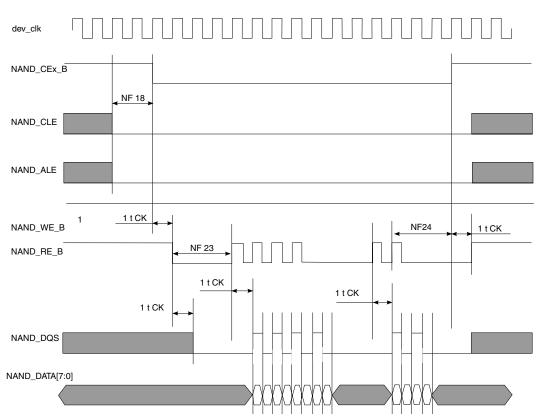

## 4.11.1 AUDMUX Timing Parameters

The AUDMUX provides a programmable interconnect logic for voice, audio, and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is governed by the SSI module. For more information, see the respective SSI electrical specifications found within this document.

## 4.11.2 ECSPI Timing Parameters

This section describes the timing parameters of the ECSPI block. The ECSPI has separate timing parameters for master and slave modes.

Figure 43. ESAI Transmitter Timing

## 4.11.6 Flexible Controller Area Network (FlexCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM) to see which pins expose Tx and Rx pins; these ports are named FLEXCAN\_TX and FLEXCAN\_RX, respectively.

## 4.11.7 HDMI Module Timing Parameters

### 4.11.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

| Symbol             | Parameter                                                                                                                                                                                                                                                                                                                                                              | Condition                                                                                                                                                                           | Min                  | Тур   | Мах                  | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|----------------------|------|

| R <sub>T</sub>     | Termination resistance                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                   | 45                   | 50    | 55                   | Ω    |

|                    | Т                                                                                                                                                                                                                                                                                                                                                                      | MDS drivers DC specifications                                                                                                                                                       |                      |       |                      |      |

| $V_{OFF}$          | Single-ended standby voltage                                                                                                                                                                                                                                                                                                                                           | $RT = 50 \Omega$                                                                                                                                                                    |                      |       |                      | mV   |

| V <sub>SWING</sub> | Single-ended output swing voltage                                                                                                                                                                                                                                                                                                                                      | For measurement conditions and<br>definitions, see the first two figures<br>above.<br>Compliance point TP1 as defined in<br>the HDMI specification, version 1.3a,<br>section 4.2.4. | 400                  | _     | 600                  | mV   |

| V <sub>H</sub>     | Single-ended output high voltage<br>For definition, see the second                                                                                                                                                                                                                                                                                                     | If attached sink supports TMDSCLK < or = 165 MHz                                                                                                                                    | avddti               | mds ± | 10 mV                | mV   |

|                    | figure above.                                                                                                                                                                                                                                                                                                                                                          | If attached sink supports TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>– 200 mV | —     | avddtmds<br>+ 10 mV  | mV   |

| VL                 | Single-ended output low voltage<br>For definition, see the second                                                                                                                                                                                                                                                                                                      | If attached sink supports TMDSCLK < or = 165 MHz                                                                                                                                    | avddtmds<br>– 600 mV | —     | avddtmds<br>- 400mV  | mV   |

|                    | figure above.                                                                                                                                                                                                                                                                                                                                                          | If attached sink supports TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>– 700 mV | —     | avddtmds<br>- 400 mV | mV   |

| R <sub>term</sub>  | Differential source termination load<br>(inside HDMI 3D Tx PHY)<br>Although the HDMI 3D Tx PHY<br>includes differential source<br>termination, the user-defined value<br>is set for each single line (for<br>illustration, see the third figure<br>above).<br><b>Note:</b> R <sub>TERM</sub> can also be<br>configured to be open and not<br>present on TMDS channels. |                                                                                                                                                                                     | 50                   |       | 200                  | Ω    |

|                    |                                                                                                                                                                                                                                                                                                                                                                        | Hot plug detect specifications                                                                                                                                                      |                      |       |                      |      |

| HPD <sup>VH</sup>  | Hot plug detect high range                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                   | 2.0                  |       | 5.3                  | V    |

|                    | Hot plug detect low range                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                   | 0                    |       | 0.8                  | V    |

| HPD                | Hot plug detect input impedance                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     | 10                   | _     |                      | kΩ   |

| HPD<br>t           | Hot plug detect time delay                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                   | —                    | —     | 100                  | μs   |

#### Table 63. Electrical Characteristics (continued)

## 4.11.8 Switching Characteristics

Table 64 describes switching characteristics for the HDMI 3D Tx PHY. Figure 59 to Figure 63 illustrate various parameters specified in table.

#### NOTE

All dynamic parameters related to the TMDS line drivers' performance imply the use of assembly guidelines.

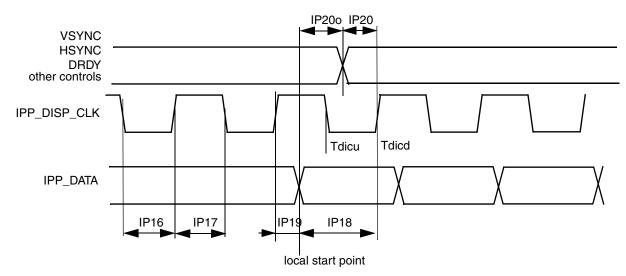

Figure 71 depicts the synchronous display interface timing for access level. The DISP\_CLK\_DOWN and DISP\_CLK\_UP parameters are register-controlled. Table 70 lists the synchronous display interface timing characteristics.

Figure 71. Synchronous Display Interface Timing Diagram—Access Level

| ID    | Parameter                                                                          | Symbol | Min                    | Typ <sup>1</sup>                       | Мах                   | Unit |

|-------|------------------------------------------------------------------------------------|--------|------------------------|----------------------------------------|-----------------------|------|

| IP16  | Display interface clock low time                                                   | Tckl   | Tdicd-Tdicu-1.24       | Tdicd <sup>2</sup> -Tdicu <sup>3</sup> | Tdicd-Tdicu+1.24      | ns   |

| IP17  | Display interface clock<br>high time                                               | Tckh   | Tdicp-Tdicd+Tdicu-1.24 | Tdicp-Tdicd+Tdicu                      | Tdicp-Tdicd+Tdicu+1.2 | ns   |

| IP18  | Data setup time                                                                    | Tdsu   | Tdicd-1.24             | Tdicu                                  | —                     | ns   |

| IP19  | Data holdup time                                                                   | Tdhd   | Tdicp-Tdicd-1.24       | Tdicp-Tdicu                            | —                     | ns   |

| IP20o | Control signals offset<br>times (defined for each<br>pin)                          | Tocsu  | Tocsu-1.24             | Tocsu                                  | Tocsu+1.24            | ns   |

| IP20  | Control signals setup time<br>to display interface clock<br>(defined for each pin) | Tcsu   | Tdicd-1.24-Tocsu%Tdicp | Tdicu                                  | _                     | ns   |

Table 70. Synchronous Display Interface Timing Characteristics (Access Level)

<sup>1</sup>The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be chip specific.

<sup>2</sup> Display interface clock down time

$$Tdicd = \frac{1}{2} \left( T_{diclk} \times ceil \left[ \frac{2 \times DISP_CLK_DOWN}{DI_CLK_PERIOD} \right] \right)$$

<sup>3</sup> Display interface clock up time where CEIL(X) rounds the elements of X to the nearest integers towards infinity.

$$Tdicu = \frac{1}{2} \left( T_{diclk} \times ceil \left[ \frac{2 \times DISP\_CLK\_UP}{DI\_CLK\_PERIOD} \right] \right)$$

| Table 77. MLB 256/512 Fs Timing Parameters (contin | ued) |

|----------------------------------------------------|------|

|----------------------------------------------------|------|

| Parameter                                                                              | Symbol            | Min | Мах   | Unit | Comment |

|----------------------------------------------------------------------------------------|-------------------|-----|-------|------|---------|

| Bus Hold from MLB_CLK low                                                              | t <sub>mdzh</sub> | 4   | —     | ns   | —       |

| Transmitter MLBSIG (MLBDAT)<br>output valid from transition of<br>MLBCLK (low-to-high) | Tdelay            | _   | 10.75 | _    | ns      |

<sup>1</sup> The controller can shut off MLB\_CLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLB\_CLK.

<sup>2</sup> MLB\_CLK low/high time includes the pulse width variation.

<sup>3</sup> The MediaLB driver can release the MLB\_DATA/MLB\_SIG line as soon as MLB\_CLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Ground = 0.0 V; load capacitance = 40 pF; MediaLB speed = 1024 Fs; Fs = 48 kHz; all timing parameters specified from the valid voltage threshold as listed in Table 78; unless otherwise noted.

| Parameter                                                                        | Symbol             | Min               | Мах               | Unit | Comment                                    |

|----------------------------------------------------------------------------------|--------------------|-------------------|-------------------|------|--------------------------------------------|

| MLB_CLK Operating Frequency <sup>1</sup>                                         | f <sub>mck</sub>   | 45.056            | 51.2              | MHz  | 1024xfs at 44.0 kHz<br>1024xfs at 50.0 kHz |

| MLB_CLK rise time                                                                | t <sub>mckr</sub>  | —                 | 1                 | ns   | V <sub>IL</sub> TO V <sub>IH</sub>         |

| MLB_CLK fall time                                                                | t <sub>mckf</sub>  | —                 | 1                 | ns   | V <sub>IH</sub> TO V <sub>IL</sub>         |

| MLB_CLK low time                                                                 | t <sub>mckl</sub>  | 6.1               | —                 | ns   | (see <sup>2</sup> )                        |

| MLB_CLK high time                                                                | t <sub>mckh</sub>  | 9.3               | —                 | ns   | —                                          |

| MLB_SIG/MLB_DATA receiver input valid to MLB_CLK falling                         | t <sub>dsmcf</sub> | 1                 | —                 | ns   | _                                          |

| MLB_SIG/MLB_DATA receiver input hold<br>from MLB_CLK low                         | t <sub>dhmcf</sub> | t <sub>mdzh</sub> | —                 | ns   | _                                          |

| MLB_SIG/MLB_DATA output high<br>impedance from MLB_CLK low                       | t <sub>mcfdz</sub> | 0                 | t <sub>mckl</sub> | ns   | (see <sup>3</sup> )                        |

| Bus Hold from MLB_CLK low                                                        | t <sub>mdzh</sub>  | 2                 | —                 | ns   | —                                          |

| Transmitter MLBSIG (MLBDAT) output valid from transition of MLBCLK (low-to-high) | Tdelay             | _                 | 6                 | ns   | _                                          |

Table 78. MLB 1024 Fs Timing Parameters

<sup>1</sup> The controller can shut off MLB\_CLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLB\_CLK.

<sup>2</sup> MLB\_CLK low/high time includes the pulse width variation.

<sup>3</sup> The MediaLB driver can release the MLB\_DATA/MLB\_SIG line as soon as MLB\_CLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Table 79 lists the MediaLB 6-pin interface timing characteristics, and Figure 88 shows the MLB 6-pin delay, setup, and hold times.

## 4.11.21.2 UART RS-232 Serial Mode Timing

The following sections describe the electrical information of the UART module in the RS-232 mode.

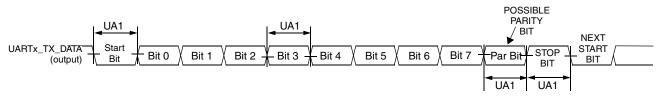

### 4.11.21.2.1 UART Transmitter

Figure 100 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 91 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 100. UART RS-232 Serial Mode Transmit Timing Diagram

Table 91. RS-232 Serial Mode Transmit Timing Parameters

| ID  | Parameter         | Symbol            | Min                                 | Мах                                             | Unit |

|-----|-------------------|-------------------|-------------------------------------|-------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | $1/F_{baud_rate}^1 - T_{ref_clk}^2$ | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub> | —    |

<sup>1</sup>  $F_{baud\_rate}$ : Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

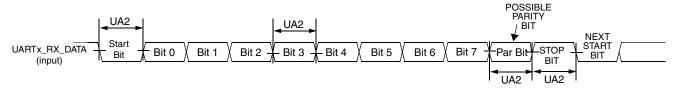

### 4.11.21.2.2 UART Receiver

Figure 101 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 92 lists serial mode receive timing characteristics.

Figure 101. UART RS-232 Serial Mode Receive Timing Diagram

Table 92.

RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> −<br>1/(16 × F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 × F <sub>baud_rate</sub> ) | —    |

The UART receiver can tolerate  $1/(16 \times F_{baud\_rate})$  tolerance in each bit. But accumulation tolerance in one frame must not exceed  $3/(16 \times F_{baud\_rate})$ .

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

## 4.11.22 USB HSIC Timings

This section describes the electrical information of the USB HSIC port.

#### NOTE

HSIC is a DDR signal. The following timing specification is for both rising and falling edges.

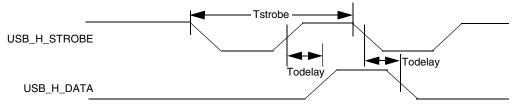

### 4.11.22.1 Transmit Timing

Figure 104. USB HSIC Transmit Waveform

#### Table 95. USB HSIC Transmit Parameters

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |  |

|---------|---------------------------------|-------|-------|------|--------------------------------|--|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   | _                              |  |

| Todelay | data output delay time          | 550   | 1350  | ps   | Measured at 50% point          |  |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |  |

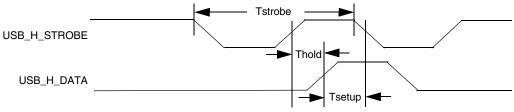

## 4.11.22.2 Receive Timing

Figure 105. USB HSIC Receive Waveform

#### Table 96. USB HSIC Receive Parameters<sup>1</sup>

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |  |

|---------|---------------------------------|-------|-------|------|--------------------------------|--|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   | _                              |  |

| Thold   | data hold time                  | 300   | _     | ps   | Measured at 50% point          |  |

| Tsetup  | data setup time                 | 365   | —     | ps   | Measured at 50% point          |  |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |  |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

#### Package Information and Contact Assignments

|                |      | Power Group | Ball Type | Out of Reset Condition <sup>1</sup> |                                   |              |                    |  |

|----------------|------|-------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|--|

| Ball Name      | Ball |             |           | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |  |

| DRAM_SDBA1     | Y15  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_SDBA1                        | Output       | 0                  |  |

| DRAM_SDBA2     | AB12 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_SDBA2                        | Output       | 0                  |  |

| DRAM_SDCKE0    | Y11  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_SDCKE0                       | Output       | 0                  |  |

| DRAM_SDCKE1    | AA11 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_SDCKE1                       | Output       | 0                  |  |

| DRAM_SDCLK_0   | AD15 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDCLK0_P                     | Input        | Hi-Z               |  |

| DRAM_SDCLK_0_B | AE15 | NVCC_DRAM   | DDRCLK    | —                                   | DRAM_SDCLK0_N                     | —            | _                  |  |

| DRAM_SDCLK_1   | AD14 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDCLK1_P                     | Input        | Hi-Z               |  |

| DRAM_SDCLK_1_B | AE14 | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDCLK1_N                     | - 1          |                    |  |

| DRAM_SDODT0    | AC16 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ODT0                         | Output       | 0                  |  |

| DRAM_SDODT1    | AB17 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ODT1                         | Output       | 0                  |  |

| DRAM_SDQS0     | AE3  | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS0_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS0_B   | AD3  | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS0_N                      |              |                    |  |

| DRAM_SDQS1     | AD6  | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS1_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS1_B   | AE6  | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS1_N                      |              |                    |  |

| DRAM_SDQS2     | AD8  | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS2_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS2_B   | AE8  | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS2_N                      |              |                    |  |

| DRAM_SDQS3     | AC10 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS3_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS3_B   | AB10 | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS3_N                      | - 1          |                    |  |

| DRAM_SDQS4     | AD18 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS4_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS4_B   | AE18 | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS4_N                      | - 1          |                    |  |

| DRAM_SDQS5     | AD20 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS5_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS5_B   | AE20 | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS5_N                      | - 1          |                    |  |

| DRAM_SDQS6     | AD23 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS6_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS6_B   | AE23 | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS6_N                      | - 1          |                    |  |

| DRAM_SDQS7     | AA25 | NVCC_DRAM   | DDRCLK    | ALT0                                | DRAM_SDQS7_P                      | Input        | Hi-Z               |  |

| DRAM_SDQS7_B   | AA24 | NVCC_DRAM   | DDRCLK    | _                                   | DRAM_SDQS7_N                      | - 1          |                    |  |

| DRAM_SDWE      | AB16 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_SDWE_B                       | Output       | 0                  |  |

| DSI_CLK0M      | H3   | NVCC_MIPI   | —         | —                                   | DSI_CLK_N                         | —            | _                  |  |

| DSI_CLK0P      | H4   | NVCC_MIPI   | —         | —                                   | DSI_CLK_P                         | —            | _                  |  |

| DSI_D0M        | G2   | NVCC_MIPI   | —         |                                     | DSI_DATA0_N                       | —            |                    |  |

| DSI_D0P        | G1   | NVCC_MIPI   |           | _                                   | DSI_DATA0_P                       | _            |                    |  |

| DSI_D1M        | H2   | NVCC_MIPI   | —         |                                     | DSI_DATA1_N                       | _            |                    |  |

| DSI_D1P        | H1   | NVCC_MIPI   | —         |                                     | DSI_DATA1_P                       | _            |                    |  |

| EIM_A16        | H25  | NVCC_EIM1   | GPIO      | ALT0                                | EIM_ADDR16                        | Output       | 0                  |  |

| EIM_A17        | G24  | NVCC_EIM1   | GPIO      | ALT0                                | EIM_ADDR17                        | Output       | 0                  |  |

| EIM_A18        | J22  | NVCC_EIM1   | GPIO      | ALT0                                | EIM_ADDR18                        | Output       | 0                  |  |

Table 100. 21 x 21 mm Functional Contact Assignments (continued)