Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | Coldfire V2                                                           |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 166.67MHz                                                             |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                            |

| Peripherals                | DMA, WDT                                                              |

| Number of I/O              | 30                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K × 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.4V ~ 3.6V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LBGA                                                              |

| Supplier Device Package    | 144-MAPBGA (13x13)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf5207cvm166 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MCF5207/8 Device Configurations

# **1 MCF5207/8 Device Configurations**

The following table compares the two devices described in this document:

#### Table 1. MCF5207 & MCF5208 Configurations

| Module                                                                   | MCF5207                | MCF5208               |  |

|--------------------------------------------------------------------------|------------------------|-----------------------|--|

| Version 2 ColdFire Core with EMAC<br>(Enhanced Multiply-Accumulate Unit) | •                      | •                     |  |

| Core (System) Clock                                                      | up to 166              | 6.67 MHz              |  |

| Peripheral and External Bus Clock<br>(Core clock ÷ 2)                    | up to 83.33 MHz        |                       |  |

| Performance (Dhrystone/2.1 MIPS)                                         | up to                  | 0 159                 |  |

| Instruction/Data Cache                                                   | 8 Kb                   | oytes                 |  |

| Static RAM (SRAM)                                                        | 16 K                   | bytes                 |  |

| SDR/DDR SDRAM Controller                                                 | •                      | •                     |  |

| Fast Ethernet Controller (FEC)                                           | —                      | •                     |  |

| Low-Power Management Module                                              | •                      | •                     |  |

| UARTs                                                                    | 3                      | 3                     |  |

| I <sup>2</sup> C                                                         | •                      | •                     |  |

| QSPI                                                                     | •                      | •                     |  |

| 32-bit DMA Timers                                                        | 4                      | 4                     |  |

| Watchdog Timer (WDT)                                                     | •                      | •                     |  |

| Periodic Interrupt Timers (PIT)                                          | 4                      | 4                     |  |

| Edge Port Module (EPORT)                                                 | •                      | •                     |  |

| Interrupt Controllers (INTC)                                             | 1                      | 1                     |  |

| 16-channel Direct Memory Access (DMA)                                    | •                      | •                     |  |

| FlexBus External Interface                                               | •                      | •                     |  |

| General Purpose I/O Module (GPIO)                                        | •                      | •                     |  |

| JTAG - IEEE <sup>®</sup> 1149.1 Test Access Port                         | •                      | •                     |  |

| Package                                                                  | 144 LQFP<br>144 MAPBGA | 160 QFP<br>196 MAPBGA |  |

# 2 Ordering Information

#### **Table 2. Orderable Part Numbers**

| Freescale Part<br>Number | Description                             | Speed      | Temperature                      |

|--------------------------|-----------------------------------------|------------|----------------------------------|

| MCF5207CAG166            | MCF5207 RISC Microprocessor, 144 LQFP   | 166.67 MHz | $-40^{\circ}$ to $+85^{\circ}$ C |

| MCF5207CVM166            | MCF5207 RISC Microprocessor, 144 MAPBGA | 166.67 MHz | $-40^{\circ}$ to $+85^{\circ}$ C |

| MCF5208CAB166            | MCF5208 RISC Microprocessor, 160 QFP    | 166.67 MHz | $-40^{\circ}$ to $+85^{\circ}$ C |

| MCF5208CVM166            | MCF5208 RISC Microprocessor, 196 MAPBGA | 166.67 MHz | $-40^{\circ}$ to $+85^{\circ}$ C |

**Signal Descriptions**

| Table 3. MCF5207/8 Signal | Information and Muxing | (continued) |

|---------------------------|------------------------|-------------|

|---------------------------|------------------------|-------------|

| Signal Name                                                   | GPIO                  | Alternate 1                          | Alternate 2   | Dir. <sup>1</sup> | Voltage<br>Domain | MCF5207<br>144<br>LQFP | MCF5207<br>144<br>MAPBGA | MCF5208<br>160<br>QFP | MCF5208<br>196<br>MAPBGA |  |  |

|---------------------------------------------------------------|-----------------------|--------------------------------------|---------------|-------------------|-------------------|------------------------|--------------------------|-----------------------|--------------------------|--|--|

| External Interrupts Port <sup>5</sup>                         |                       |                                      |               |                   |                   |                        |                          |                       |                          |  |  |

| IRQ7 <sup>2</sup>                                             | PIRQ7 <sup>2</sup>    |                                      |               | Ι                 | EVDD              | 134                    | A5                       | 142                   | C7                       |  |  |

| IRQ4 <sup>2</sup>                                             | PIRQ4 <sup>2</sup>    | DREQ0 <sup>2</sup>                   | —             | I                 | EVDD              | 133                    | C6                       | 141                   | D7                       |  |  |

| IRQ1 <sup>2</sup>                                             | PIRQ1 <sup>2</sup>    |                                      |               | Ι                 | EVDD              | 132                    | B6                       | 140                   | D8                       |  |  |

| FEC                                                           |                       |                                      |               |                   |                   |                        |                          |                       |                          |  |  |

| FEC_MDC PFECI2C3 I2C_SCL <sup>2</sup> U2TXD O EVDD — — 148 D6 |                       |                                      |               |                   |                   |                        |                          |                       |                          |  |  |

| FEC_MDIO                                                      | PFECI2C2              | I2C_SDA <sup>2</sup>                 | U2RXD         | I/O               | EVDD              | _                      | _                        | 147                   | C6                       |  |  |

| FEC_TXCLK                                                     | PFECH7                |                                      |               | I                 | EVDD              |                        |                          | 157                   | B3                       |  |  |

| _                                                             | PFECH6                |                                      | U1RTS         | 0                 | EVDD              | 142                    | A2                       | —                     | —                        |  |  |

| FEC_TXEN                                                      | PFECH6                |                                      | U1RTS         | 0                 | EVDD              |                        |                          | 158                   | A2                       |  |  |

| FEC_TXD0                                                      | PFECH5                |                                      | —             | 0                 | EVDD              |                        |                          | 3                     | B1                       |  |  |

| FEC_COL                                                       | PFECH4                |                                      | —             | Ι                 | EVDD              | _                      | —                        | 7                     | D3                       |  |  |

| FEC_RXCLK                                                     | PFECH3                |                                      | —             | Ι                 | EVDD              | _                      | —                        | 154                   | B4                       |  |  |

| FEC_RXDV                                                      | PFECH2                |                                      | —             | Ι                 | EVDD              | —                      | —                        | 153                   | A4                       |  |  |

| FEC_RXD0                                                      | PFECH1                | _                                    | —             | I                 | EVDD              | _                      | —                        | 152                   | D5                       |  |  |

| FEC_CRS                                                       | PFECH0                | _                                    | —             | Ι                 | EVDD              | _                      | —                        | 8                     | D2                       |  |  |

| FEC_TXD[3:1]                                                  | PFECL[7:5]            | —                                    | —             | 0                 | EVDD              | _                      | —                        | 6–4                   | C1, C2, B2               |  |  |

| —                                                             | PFECL4                | _                                    | UORTS         | 0                 | EVDD              | 141                    | D5                       | _                     | _                        |  |  |

| FEC_TXER                                                      | PFECL4                | _                                    | UORTS         | 0                 | EVDD              | _                      | —                        | 156                   | A3                       |  |  |

| FEC_RXD[3:2]                                                  | PFECL[3:2]            | —                                    | —             | Ι                 | EVDD              | _                      | —                        | 149–150               | A5, B5                   |  |  |

| —                                                             | PFECL1                | _                                    | U1CTS         | I                 | EVDD              | 139                    | B4                       | —                     | _                        |  |  |

| FEC_RXD1                                                      | PFECL1                | _                                    | U1CTS         | Ι                 | EVDD              | _                      | —                        | 151                   | C5                       |  |  |

| _                                                             | PFECL0                | _                                    | UOCTS         | I                 | EVDD              | 140                    | E4                       | _                     | —                        |  |  |

| FEC_RXER                                                      | PFECL0                | _                                    | UOCTS         | I                 | EVDD              | _                      | —                        | 155                   | C4                       |  |  |

|                                                               |                       | ontain an FEC mo<br>opriate FEC GPI0 |               |                   | UART0 a           | nd UART1 cor           | htrol signals (as        | s well as their (     | GPIO signals             |  |  |

| I2C_SDA <sup>2</sup>                                          | PFECI2C0 <sup>2</sup> | U2RXD <sup>2</sup>                   | _             | I/O               | EVDD              | —                      | —                        | —                     | D1                       |  |  |

| I2C_SCL <sup>2</sup>                                          | PFECI2C1 <sup>2</sup> | U2TXD <sup>2</sup>                   | —             | I/O               | EVDD              |                        |                          |                       | E4                       |  |  |

| Ī                                                             | DACK0 and DRE         | EQO do not have<br>TS and QSPI       | a dedicated b | DMA<br>ond pa     | ads. Plea         | se refer to the        | following pins           | for muxing:           |                          |  |  |

**Mechanicals and Pinouts**

## 4 Mechanicals and Pinouts

Drawings in this section show the pinout and the packaging and mechanical characteristics of the MCF5207 and MCF5208 devices.

#### NOTE

The mechanical drawings are the latest revisions at the time of publication of this document. The most up-to-date mechanical drawings can be found at the product summary page located at http://www.freescale.com/coldfire.

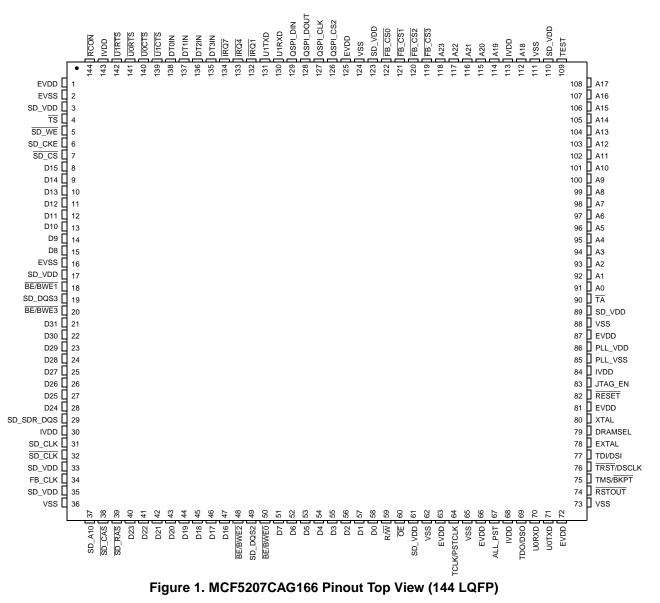

## 4.1 Pinout—144 LQFP

Figure 1 shows a pinout of the MCF5207CAG166 device.

**Mechanicals and Pinouts**

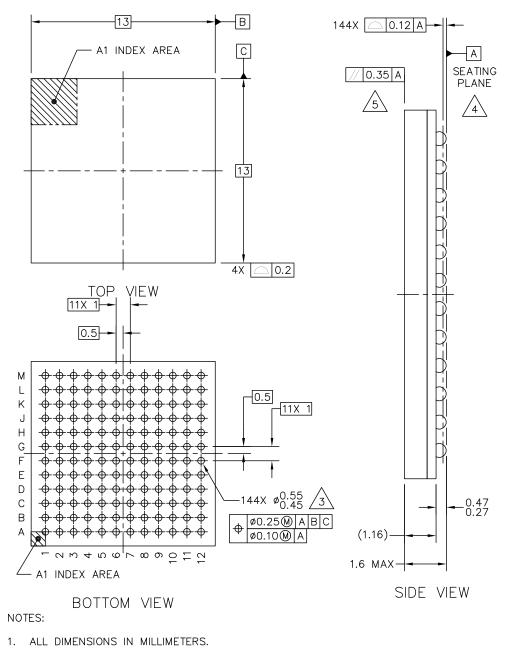

## 4.4 Package Dimensions—144 MAPBGA

Figure 5 shows the MCF5207CAB166 package dimensions.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3 MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

$\overline{4}$  datum a, the seating plane, is determined by the spherical crowns of the solder balls.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

Figure 5. MCF5207CAB166 Package Dimensions (144 MAPBGA)

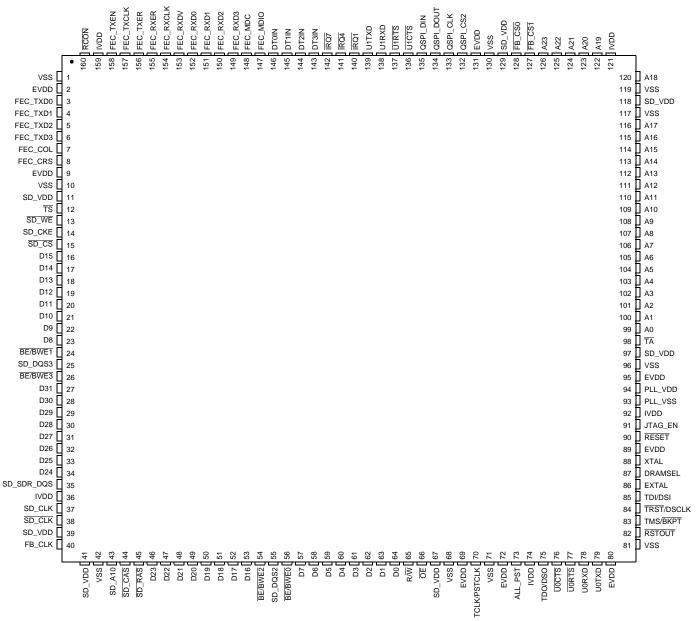

## 4.5 Pinout—160 QFP

Figure 6 shows a pinout of the MCF5208CAB166 device.

Figure 6. MCF5208CAB166 Pinout Top View (160 QFP)

| Operating Temperature Range (Packaged) | T <sub>A</sub><br>(T <sub>L</sub> - T <sub>H</sub> ) | – 40 to 85  | °C |

|----------------------------------------|------------------------------------------------------|-------------|----|

| Storage Temperature Range              | T <sub>stg</sub>                                     | – 55 to 150 | °C |

| Table 4. Absolute Maximum Ratings <sup>1, 2</sup> (continued) |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

NOTES:

Functional operating conditions are given in Section 5.4, "DC Electrical Specifications". Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Continued operation at these levels may affect device reliability or cause permanent damage to the device.

<sup>2</sup> This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (V<sub>SS</sub> or EV<sub>DD</sub>).

<sup>3</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

<sup>4</sup> All functional non-supply pins are internally clamped to V<sub>SS</sub> and EV<sub>DD</sub>.

<sup>5</sup> Power supply must maintain regulation within operating  $EV_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > EV_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $EV_{DD}$  and could result in external power supply going out of regulation. Ensure external  $EV_{DD}$  load shunts current greater than maximum injection current. This is the greatest risk when the MCU is not consuming power (ex; no clock). Power supply must maintain regulation within operating  $EV_{DD}$  range during instantaneous and operating maximum current conditions.

## 5.2 Thermal Characteristics

Table 5 lists thermal resistance values

| Characteristic                          |                            | Symbol          | 196MBGA           | 144MBGA           | 160QFP            | 144LQFP           | Unit |

|-----------------------------------------|----------------------------|-----------------|-------------------|-------------------|-------------------|-------------------|------|

| Junction to ambient, natural convection | Four layer board (2s2p)    | $\theta_{JMA}$  | 47 <sup>1,2</sup> | 47 <sup>1,2</sup> | 49 <sup>1,2</sup> | 65 <sup>1,2</sup> | °C/W |

| Junction to ambient (@200 ft/min)       | Four layer board<br>(2s2p) | $\theta_{JMA}$  | 43 <sup>1,2</sup> | 43 <sup>1,2</sup> | 44 <sup>1,2</sup> | 58 <sup>1,2</sup> | °C/W |

| Junction to board                       |                            | $\theta_{JB}$   | 36 <sup>3</sup>   | 36 <sup>3</sup>   | 40 <sup>3</sup>   | 50 <sup>3</sup>   | °C/W |

| Junction to case                        |                            | $\theta_{JC}$   | 22 <sup>4</sup>   | 22 <sup>4</sup>   | 39 <sup>4</sup>   | 19 <sup>4</sup>   | °C/W |

| Junction to top of package              |                            | Ψ <sub>jt</sub> | 6 <sup>1,5</sup>  | 6 <sup>1,5</sup>  | 12 <sup>1,6</sup> | 5 <sup>1,7</sup>  | °C/W |

| Maximum operating junction temperature  |                            | Тj              | 105               | 105               | 105               | 105               | °C   |

**Table 5. Thermal Characteristics**

NOTES:

$\theta_{JMA}$  and  $\Psi_{jt}$  parameters are simulated in conformance with EIA/JESD Standard 51-2 for natural convection. Freescale recommends the use of  $\theta_{JmA}$  and power dissipation specifications in the system design to prevent device junction temperatures from exceeding the rated specification. System designers should be aware that device junction temperatures can be significantly influenced by board layout and surrounding devices. Conformance to the device junction temperature specification can be verified by physical measurement in the customer's system using the  $\Psi_{jt}$  parameter, the device power dissipation, and the method described in EIA/JESD Standard 51-2.

<sup>2</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>2</sup> A device is defined as a failure if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete DC parametric and functional testing is performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

## 5.4 DC Electrical Specifications

#### **Table 7. DC Electrical Specifications**

| Characteristic                                                                                                                                                                                                               | Symbol             | Min                                                                     | Max                                                                                                                         | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| Core Supply Voltage                                                                                                                                                                                                          | IV <sub>DD</sub>   | 1.4                                                                     | 1.6                                                                                                                         | V    |

| PLL Supply Voltage                                                                                                                                                                                                           | PLLV <sub>DD</sub> | 1.4                                                                     | 1.6                                                                                                                         | V    |

| CMOS Pad Supply Voltage                                                                                                                                                                                                      | EV <sub>DD</sub>   | 3.0                                                                     | 3.6                                                                                                                         | V    |

| SDRAM and FlexBus Supply Voltage<br>Mobile DDR/Bus Pad Supply Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)                                               | SDV <sub>DD</sub>  | 1.70<br>2.25<br>3.0                                                     | 1.95<br>2.75<br>3.6                                                                                                         | V    |

| CMOS Input High Voltage                                                                                                                                                                                                      | EVIH               | 2                                                                       | EV <sub>DD</sub> + 0.3                                                                                                      | V    |

| CMOS Input Low Voltage                                                                                                                                                                                                       | EVIL               | V <sub>SS</sub> - 0.3                                                   | 0.8                                                                                                                         | V    |

| CMOS Output High Voltage<br>$I_{OH} = -5.0 \text{ mA}$                                                                                                                                                                       | EV <sub>OH</sub>   | EV <sub>DD</sub> - 0.4                                                  | _                                                                                                                           | V    |

| CMOS Output Low Voltage<br>I <sub>OL</sub> = 5.0 mA                                                                                                                                                                          | EV <sub>OL</sub>   | _                                                                       | 0.4                                                                                                                         | V    |

| SDRAM and FlexBus Input High Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)                                           | SDV <sub>IH</sub>  | 1.35<br>1.7<br>2                                                        | $\begin{array}{l} \text{SDV}_{\text{DD}} + 0.3 \\ \text{SDV}_{\text{DD}} + 0.3 \\ \text{SDV}_{\text{DD}} + 0.3 \end{array}$ | V    |

| SDRAM and FlexBus Input Low Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)                                            | SDV <sub>IL</sub>  | V <sub>SS</sub> - 0.3<br>V <sub>SS</sub> - 0.3<br>V <sub>SS</sub> - 0.3 | 0.45<br>0.8<br>0.8                                                                                                          | V    |

| SDRAM and FlexBus Output High Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)<br>$I_{OH} = -5.0$ mA for all modes      | SDV <sub>OH</sub>  | SDV <sub>DD</sub> - 0.35<br>2.1<br>2.4                                  |                                                                                                                             | V    |

| SDRAM and FlexBus Output Low Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)<br>I <sub>OL</sub> = 5.0 mA for all modes | SDV <sub>OL</sub>  |                                                                         | 0.3<br>0.3<br>0.5                                                                                                           | V    |

| Input Leakage Current $V_{in} = IV_{DD}$ or $V_{SS}$ , Input-only pins                                                                                                                                                       | l <sub>in</sub>    | -1.0                                                                    | 1.0                                                                                                                         | μΑ   |

| Characteristic                                                                               | Symbol           | Min | Мах    | Unit |

|----------------------------------------------------------------------------------------------|------------------|-----|--------|------|

| Weak Internal Pull Up Device Current, tested at $V_{IL}$ Max. <sup>1</sup>                   | I <sub>APU</sub> | -10 | - 130  | μA   |

| Input Capacitance <sup>2</sup><br>All input-only pins<br>All input/output (three-state) pins | C <sub>in</sub>  |     | 7<br>7 | pF   |

| Table 7. DC Electrical | Specifications | (continued) |

|------------------------|----------------|-------------|

|------------------------|----------------|-------------|

NOTES:

<sup>1</sup> Refer to the signals section for pins having weak internal pull-up devices.

<sup>2</sup> This parameter is characterized before qualification rather than 100% tested.

## 5.4.1 PLL Power Filtering

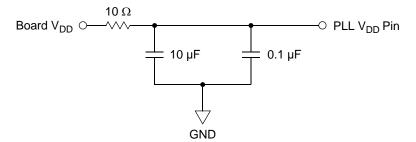

To further enhance noise isolation, an external filter is strongly recommended for PLL analog  $V_{DD}$  pins. The filter shown in Figure 11 should be connected between the board  $V_{DD}$  and the PLLV<sub>DD</sub> pins. The resistor and capacitors should be placed as close to the dedicated PLLV<sub>DD</sub> pin as possible.

Figure 11. System PLL V<sub>DD</sub> Power Filter

## 5.4.2 Supply Voltage Sequencing and Separation Cautions

The relationship between  $SDV_{DD}$  and  $EV_{DD}$  is non-critical during power-up and power-down sequences.  $SDV_{DD}$  (2.5V or 3.3V) and  $EV_{DD}$  are specified relative to  $IV_{DD}$ .

#### 5.4.2.1 Power Up Sequence

If  $EV_{DD}/SDV_{DD}$  are powered up with  $IV_{DD}$  at 0 V, the sense circuits in the I/O pads cause all pad output drivers connected to the  $EV_{DD}/SDV_{DD}$  to be in a high impedance state. There is no limit on how long after  $EV_{DD}/SDV_{DD}$  powers up before  $IV_{DD}$  must power up.  $IV_{DD}$  should not lead the  $EV_{DD}$ ,  $SDV_{DD}$ , or  $PLLV_{DD}$  by more than 0.4 V during power ramp-up or there will be high current in the internal ESD protection diodes. The rise times on the power supplies should be slower than 500 us to avoid turning on the internal ESD protection clamp diodes.

#### 5.4.2.2 Power Down Sequence

If  $IV_{DD}$ /PLLV<sub>DD</sub> are powered down first, sense circuits in the I/O pads cause all output drivers to be in a high impedance state. There is no limit on how long after  $IV_{DD}$  and  $PLLV_{DD}$  power down before  $EV_{DD}$  or  $SDV_{DD}$  must power down.  $IV_{DD}$  should not lag  $EV_{DD}$ ,  $SDV_{DD}$ , or  $PLLV_{DD}$  going low by more than

<sup>5</sup> See the description of the low-power control register (LCPR) in the MCF5208 Reference Manual for more information on stop modes 0–3.

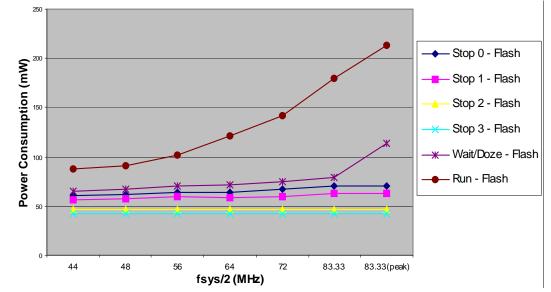

The figure below illustrates the power consumption in a graphical format.

| f <sub>sys/2</sub> Frequency | Voltage | Typical <sup>2</sup> A | ctive (mA) | Peak <sup>3</sup> Active |

|------------------------------|---------|------------------------|------------|--------------------------|

| sys/2 requency               | (V)     | SRAM                   | Flash      | (mA)                     |

|                              | 3.3     | 2.04                   | 2.12       | 2.28                     |

| 1 MHz                        | 2.5     | 15.24                  | 15.32      | 15.24                    |

|                              | 1.5     | 1.30                   | 1.41       | 1.49                     |

|                              | 3.3     | 2.23                   | 2.40       | 3.57                     |

| 2 MHz                        | 2.5     | 15.26                  | 15.42      | 15.26                    |

|                              | 1.5     | 1.71                   | 1.92       | 2.09                     |

| 4 MHz                        | 3.3     | 2.60                   | 2.95       | 3.58                     |

|                              | 2.5     | 15.30                  | 15.61      | 15.30                    |

|                              | 1.5     | 2.49                   | 2.95       | 3.29                     |

|                              | 3.3     | 7.61                   | 17.67      | 25.34                    |

| 44 MHz                       | 2.5     | 16.13                  | 19.49      | 16.95                    |

|                              | 1.5     | 24.04                  | 28.72      | 39.02                    |

|                              | 3.3     | 8.16                   | 26.21      | 34.45                    |

| 48 MHz                       | 2.5     | 16.28                  | 20.06      | 17.17                    |

|                              | 1.5     | 26.05                  | 31.13      | 42.30                    |

#### Table 9. Typical Active Current Consumption Specifications<sup>1</sup>

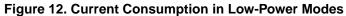

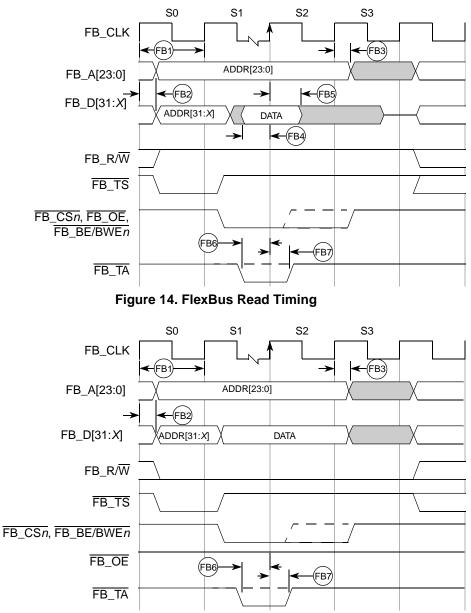

All other timing relationships can be derived from these values. Timings listed in Table 11 are shown in Figure 14 and Figure 15.

\* The timings are also valid for inputs sampled on the negative clock edge.

### 5.7.1 FlexBus

FlexBus is a multi-function external bus interface provided to interface to slave-only devices up to a maximum bus frequency of 83.33 MHz. It can be directly connected to asynchronous or synchronous devices such as external boot ROMs, flash memories, gate-array logic, or other simple target (slave) devices with little or no additional circuitry. For asynchronous devices, a simple chip-select based interface can be used. The FlexBus interface has six general purpose chip-selects ( $\overline{FB}_CS[5:0]$ ) that can be configured to be distributed between the FlexBus or SDRAM memory interfaces. Chip-select  $\overline{FB}_CS[0]$  can be dedicated to boot ROM access and can be programmed to be byte (8 bits), word (16 bits), or longword (32 bits) wide. Control signal timing is compatible with common ROM/flash memories.

Figure 15. Flexbus Write Timing

## 5.8 SDRAM Bus

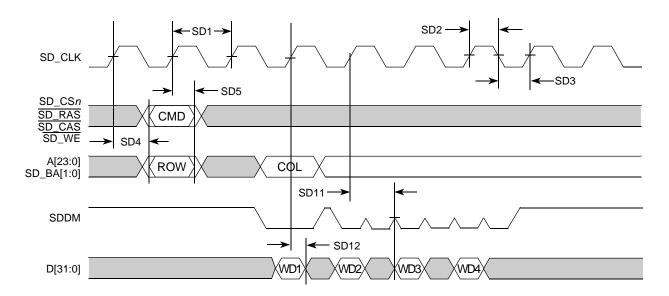

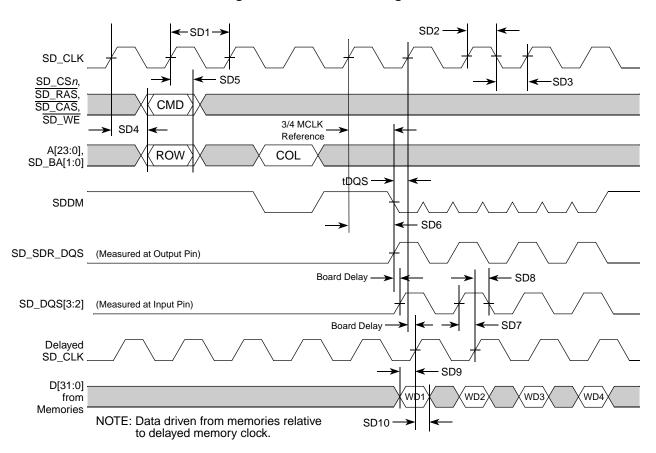

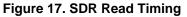

The SDRAM controller supports accesses to main SDRAM memory from any internal master. It supports standard SDRAM or double data rate (DDR) SDRAM, but it does not support both at the same time. The SDRAM controller uses SSTL2 and SSTL3 I/O drivers. Both SSTL drive modes are programmable for Class I or Class II drive strength.

Figure 16. SDR Write Timing

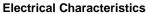

## 5.8.2 DDR SDRAM AC Timing Characteristics

When using the SDRAM controller in DDR mode, the following timing numbers must be followed to properly latch or drive data onto the memory bus. All timing numbers are relative to the four DQS byte lanes. The following timing numbers are subject to change at anytime, and are only provided to aid in early board design. Please contact your local Freescale representative if questions develop.

| Num  | Characteristic                                                               | Symbol               | Min                      | Мах                   | Unit   | Notes  |

|------|------------------------------------------------------------------------------|----------------------|--------------------------|-----------------------|--------|--------|

| _    | Frequency of Operation                                                       | _                    | 60                       | 83.33                 | Mhz    | 1      |

| DD1  | Clock Period (SD_CLK)                                                        | t <sub>DDCK</sub>    | 12                       | 16.67                 | ns     | 2      |

| DD2  | Pulse Width High                                                             | t <sub>DDCKH</sub>   | 0.45                     | 0.55                  | SD_CLK | 3      |

| DD3  | Pulse Width Low                                                              | t <sub>DDCKL</sub>   | 0.45                     | 0.55                  | SD_CLK | 3      |

| DD4  | Address, SD_CKE, SD_CAS, SD_RAS, SD_WE,<br>SD_CS[1:0] - Output Valid         | t <sub>SDCHACV</sub> | —                        | 0.5 × SD_CLK<br>+ 1.0 | ns     | 4      |

| DD5  | Address, SD_CKE, SD_CAS, SD_RAS, SD_WE,<br>SD_CS[1:0] - Output Hold          | t <sub>SDCHACI</sub> | 2.0                      | _                     | ns     | —      |

| DD6  | Write Command to first DQS Latching Transition                               | t <sub>CMDVDQ</sub>  |                          | 1.25                  | SD_CLK | —      |

| DD7  | Data and Data Mask Output Setup (DQ>DQS)<br>Relative to DQS (DDR Write Mode) | t <sub>DQDMV</sub>   | 1.5                      | _                     | ns     | 5<br>6 |

| DD8  | Data and Data Mask Output Hold (DQS>DQ)<br>Relative to DQS (DDR Write Mode)  | t <sub>DQDMI</sub>   | 1.0                      | _                     | ns     | 7      |

| DD9  | Input Data Skew Relative to DQS (Input Setup)                                | t <sub>DVDQ</sub>    | —                        | 1                     | ns     | 8      |

| DD10 | Input Data Hold Relative to DQS.                                             | t <sub>DIDQ</sub>    | 0.25 × SD_CLK<br>+ 0.5ns | _                     | ns     | 9      |

| DD11 | DQS falling edge from SDCLK rising (output hold time)                        | t <sub>DQLSDCH</sub> | 0.5                      | —                     | ns     | —      |

| DD12 | DQS input read preamble width (t <sub>RPRE</sub> )                           | t <sub>DQRPRE</sub>  | 0.9                      | 1.1                   | SD_CLK | —      |

| DD13 | DQS input read postamble width (t <sub>RPST</sub> )                          | t <sub>DQRPST</sub>  | 0.4                      | 0.6                   | SD_CLK | —      |

| DD14 | DQS output write preamble width (t <sub>WPRE</sub> )                         | t <sub>DQWPRE</sub>  | 0.25                     | —                     | SD_CLK | —      |

| DD15 | DQS output write postamble width (t <sub>WPST</sub> )                        | t <sub>DQWPST</sub>  | 0.4                      | 0.6                   | SD_CLK | —      |

#### Table 13. DDR Timing Specifications

NOTES:

<sup>1</sup> The frequency of operation is 2x or 4x the FB\_CLK frequency of operation. FlexBus and SDRAM clock operate at the same frequency as the internal bus clock.

<sup>2</sup> SD\_CLK is one SDRAM clock in (ns).

<sup>3</sup> Pulse width high plus pulse width low cannot exceed min and max clock period.

<sup>4</sup> Command output valid should be 1/2 the memory bus clock (SD\_CLK) plus some minor adjustments for process, temperature, and voltage variations.

<sup>5</sup> This specification relates to the required input setup time of today's DDR memories. The device's output setup should be larger than the input setup of the DDR memories. If it is not larger, the input setup on the memory is in violation. MEM\_DATA[31:24] is relative to MEM\_DQS[3], MEM\_DATA[23:16] is relative to MEM\_DQS[2], MEM\_DATA[15:8] is relative to MEM\_DQS[1], and MEM\_[7:0] is relative MEM\_DQS[0].

<sup>6</sup> The first data beat is valid before the first rising edge of DQS and after the DQS write preamble. The remaining data beats are valid for each subsequent DQS edge.

D[31:24]/D[23:16] WD1 WD2 WD3 WD4

Figure 19. DDR Read Timing

#### **General Purpose I/O Timing** 5.9

#### Table 14. GPIO Timing<sup>1</sup>

| Num | Characteristic                                                | Symbol             | Min | Мах | Unit |

|-----|---------------------------------------------------------------|--------------------|-----|-----|------|

| G1  | FB_CLK High to GPIO Output Valid                              | t <sub>CHPOV</sub> |     | 8   | ns   |

| G2  | FB_CLK High to GPIO Output Invalid     t <sub>CHPOI</sub> 1.5 |                    |     |     | ns   |

| G3  | GPIO Input Valid to FB_CLK High t <sub>PVCH</sub> 8 -         |                    | _   | ns  |      |

| G4  | FB_CLK High to GPIO Input Invalid                             | t <sub>CHPI</sub>  | 1.5 |     | ns   |

NOTES:

GPIO spec cover: IRQn, UART and Timer pins.

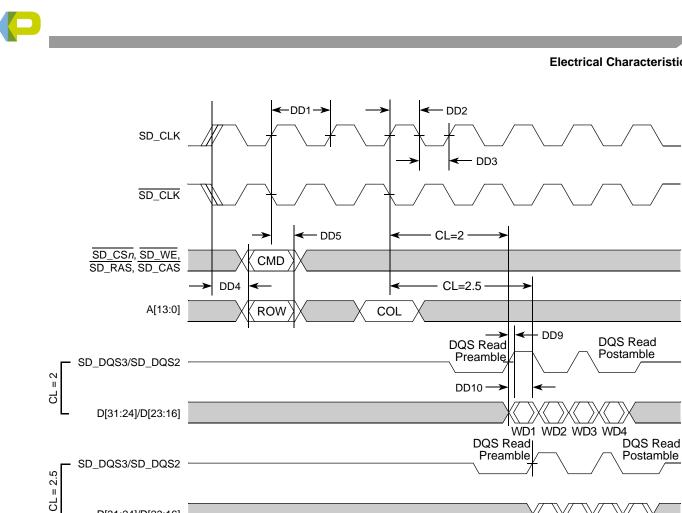

Figure 22. I<sup>2</sup>C Input/Output Timings

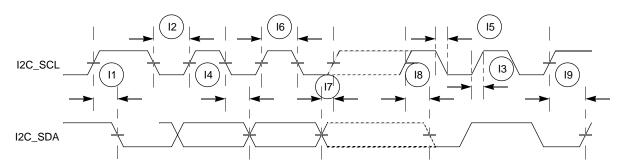

## 5.12 Fast Ethernet AC Timing Specifications

MII signals use TTL signal levels compatible with devices operating at 5.0 V or 3.3 V.

# 5.12.1 MII Receive Signal Timing (FEC\_RXD[3:0], FEC\_RXDV, FEC\_RXER, and FEC\_RXCLK)

The receiver functions correctly up to a FEC\_RXCLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed twice the FEC\_RXCLK frequency.

Table 18 lists MII receive channel timings.

| Table 18. MI | Receive | Signal | Timing |

|--------------|---------|--------|--------|

|--------------|---------|--------|--------|

| Num | Characteristic                                      | Min | Max | Unit             |

|-----|-----------------------------------------------------|-----|-----|------------------|

| M1  | FEC_RXD[3:0], FEC_RXDV, FEC_RXER to FEC_RXCLK setup | 5   | _   | ns               |

| M2  | FEC_RXCLK to FEC_RXD[3:0], FEC_RXDV, FEC_RXER hold  | 5   | _   | ns               |

| M3  | FEC_RXCLK pulse width high                          | 35% | 65% | FEC_RXCLK period |

| M4  | FEC_RXCLK pulse width low                           | 35% | 65% | FEC_RXCLK period |

Figure 23 shows MII receive signal timings listed in Table 18.

Figure 23. MII Receive Signal Timing Diagram

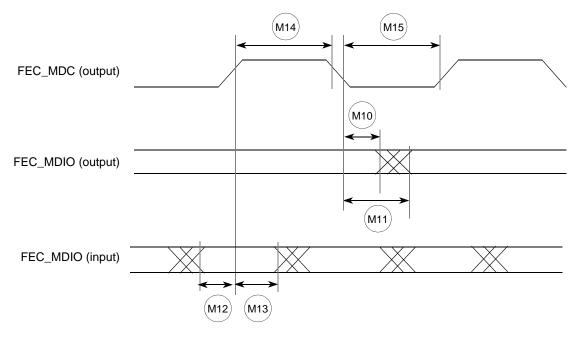

# 5.12.4 MII Serial Management Channel Timing (FEC\_MDIO and FEC\_MDC)

Table 21 lists MII serial management channel timings. The FEC functions correctly with a maximum MDC frequency of 2.5 MHz.

| Num | Characteristic                                                              | Min | Max | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | FEC_MDC falling edge to FEC_MDIO output invalid (minimum propagation delay) | 0   | —   | ns             |

| M11 | FEC_MDC falling edge to FEC_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | FEC_MDIO (input) to FEC_MDC rising edge setup                               | 10  | _   | ns             |

| M13 | FEC_MDIO (input) to FEC_MDC rising edge hold                                | 0   | _   | ns             |

| M14 | FEC_MDC pulse width high                                                    | 40% | 60% | FEC_MDC period |

| M15 | FEC_MDC pulse width low                                                     | 40% | 60% | FEC_MDC period |

Figure 26 shows MII serial management channel timings listed in Table 21.

Figure 26. MII Serial Management Channel Timing Diagram

## 5.13 32-Bit Timer Module AC Timing Specifications

Table 22 lists timer module AC timings.

#### Table 22. Timer Module AC Timing Specifications

| Name | Characteristic                            |   | Unit |                  |  |

|------|-------------------------------------------|---|------|------------------|--|

| Name |                                           |   | Max  | Onit             |  |

| T1   | DT0IN / DT1IN / DT2IN / DT3IN cycle time  |   | _    | t <sub>CYC</sub> |  |

| T2   | DT0IN / DT1IN / DT2IN / DT3IN pulse width | 1 | —    | t <sub>CYC</sub> |  |

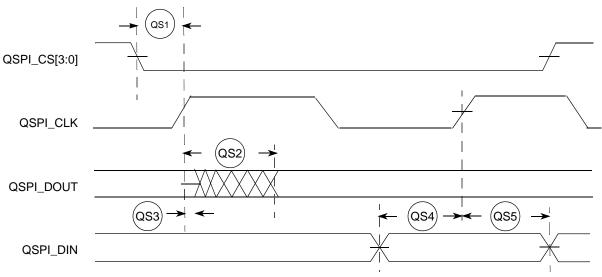

## 5.14 **QSPI Electrical Specifications**

Table 23 lists QSPI timings.

| Name | Characteristic                                    | Min | Max | Unit |

|------|---------------------------------------------------|-----|-----|------|

| QS1  | QSPI_CS[3:0] to QSPI_CLK                          | 1   | 510 | tcyc |

| QS2  | QSPI_CLK high to QSPI_DOUT valid.                 | _   | 10  | ns   |

| QS3  | QSPI_CLK high to QSPI_DOUT invalid. (Output hold) | 1.5 | —   | ns   |

| QS4  | QSPI_DIN to QSPI_CLK (Input setup) 9              |     | —   | ns   |

| QS5  | QSPI_DIN to QSPI_CLK (Input hold)                 | 9   | —   | ns   |

The values in Table 23 correspond to Figure 27.

#### Figure 27. QSPI Timing

## 6 Revision History

#### Table 26. Revision History

| Revision<br>Number | Date      | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | 5/23/2005 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.1                | 6/16/2005 | <ul> <li>Corrected 144QFP pinout in Figure 1. Pins 139-142 incorrectly showed FEC functionality, which are actually UART 0/1 clear-to-send and request-to-send signals.</li> <li>Changed maximum core frequency in Table 10, spec #2, from 240MHz to 166.67MHz. Also, changed symbols in table: f<sub>core</sub> -&gt; f<sub>sys</sub> and f<sub>sys</sub> -&gt; f<sub>sys/2</sub> for consistency throughout document and reference manual.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0.2                | 8/26/2005 | <ul> <li>Changed ball M9 from SD_VDD to EVDD in Figure 9.</li> <li>Table 3: Pin 33 for 144 LQFP package should be EVDD instead of SD_VDD. BE/BWE[3:0] for 144 LQFP should be "20, 48, 18, 50" instead of "18, 20, 48, 50"</li> <li>Cleaned up various electrical specifications:</li> <li>Table 4: Added DDR/Memory pad supply voltage spec, changed "clock synthesizer supply voltage" to "PLL supply voltage", changed min PLLV<sub>DD</sub> from -0.5 to -0.3, changed max V<sub>IN</sub> from 4.0 to 3.6, changed minimum T<sub>stg</sub> from -65 to -55,</li> <li>Table 5: Changed TBD values in T<sub>j</sub> entry to 105°C.</li> <li>Table 5: Changed TBD values in T<sub>j</sub> entry to 105°C.</li> <li>Table 7: Changed minimum core supply voltage from 1.35 to 1.4 and maximum from 1.65 to 1.6, added PLL supply voltage entry, added pad supply entries for mobile-DDR, DDR, and SDR, changed minimum input high voltage from 0.7xEV<sub>DD</sub> to 2 and maximum from 3.65 to EV<sub>DD</sub>+0.05, changed minimum input low voltage from VSS-0.3 to -0.05 and maximum from 0.35xEV<sub>DD</sub>to 0.8, added input high/low voltage entries for DDR and mobile-DDR, removed high impedance leakage current entry, changed minimum output high voltage from EV<sub>DD</sub>-0.5 to EV<sub>DD</sub>-0.4, added DDR/bus output high/low voltage entries.</li> <li>Added filtering circuits and voltage sequencing sections: Section 5.4.1, "PLL Power Filtering," and Section 5.4.2, "Supply Voltage Sequencing and Separation Cautions."</li> <li>Removed "Operating Conditions" table from Section 5.6, "Oscillator and PLL Electrical Characteristics," because it is redundant with Table 7.</li> <li>Table 11: Changed minimum core frequency to TBD, removed external reference and on-chip PLL frequency specs to have only a CLKOUT frequency spec of TBD to 83.33MHz, removed loss of reference frequency and self-clocked mode frequency entries, in EXTAL input high/low voltage entries, removed power-up to lock time entry, removed last 5 entries (frequency un-lock range, frequency lock range, CLKOUT period jitter, frequency modulation range limit, and ICO frequency)</li> </ul> |

| 0.3                | 9/07/2005 | <ul> <li>Corrected DRAMSEL footnote #3 in Table 3.</li> <li>Updated Table 3 with 144MAPBGA pin locations.</li> <li>Added 144MAPBGA ballmap to Section 4.3, "Pinout—144 MAPBGA."</li> <li>Changed J12 from PLL_VDD to IVDD in Figure 9.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**Revision History**

| Revision<br>Number | Date       | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.4                | 10/10/2005 | <ul> <li>Figure 1 and Table 3: Changed pin 33 from EVDD to SD_VDD</li> <li>Figure 4 and Table 3: Changed ball D10 from TEST to VSS</li> <li>Figure 6 and Table 3: Changed pin 39 from EVDD to SD_VDD and pin 117 from TEST to VSS</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.5                | 3/29/2006  | <ul> <li>Added "top view" and "bottom view" labels where appropriate to mechanical drawings and pinouts.</li> <li>Updated mechanical drawings to latest available, and added note to Section 4, "Mechanicals and Pinouts."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.6                | 7/21/2006  | <ul> <li>Corrected cross-reference to Figure 9 in Section 4.7, "Pinout—196 MAPBGA."</li> <li>Corrected L3 label in Figure 9 from SD_DR_DQS to SD_SDR_DQS.</li> <li>Corrected L6 label in Figure 9 from SD_DQS0 to SD_DQS2 and H3 from SD_DQS1 to SD_DQS3.</li> <li>Removed second sentence from Section 5.12.2, "MII Transmit Signal Timing (FEC_TXD[3:0], FEC_TXEN, FEC_TXER, FEC_TXCLK)," regarding no minimum frequency requirement for TXCLK.</li> <li>Removed third and fourth paragraphs from Section 5.12.2, "MII Transmit Signal Timing (FEC_TXD[3:0], FEC_TXEN, FEC_TXEN, FEC_TXER, FEC_TXCLK)," as this feature is not supported on this device.</li> </ul> |

| 1                  | 3/28/2007  | <ul> <li>Removed preliminary designation from Section 5, "Electrical<br/>Characteristics."</li> <li>Updated Section 5.2, "Thermal Characteristics."</li> <li>Updated Section 5.4, "DC Electrical Specifications."</li> <li>Added Section 5.5, "Current Consumption."</li> <li>Updated Section 5.6, "Oscillator and PLL Electrical Characteristics."</li> <li>Made some corrections to the drawings in Section 5.8, "SDRAM Bus."</li> <li>Edited for grammar, punctuation, spelling, style, and format JD</li> </ul>                                                                                                                                                   |

| 2                  | 12/4/2008  | <ul> <li>Updated FlexBus read and write timing diagrams in Figure 14 and Figure 15.</li> <li>Changed the following specs in Table 12 and Table 13:</li> <li>Minimum frequency of operation from TBD to 60MHz</li> <li>Maximum clock period from TBD to 16.67 ns</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                  | 9/1/2009   | Changed doc type from Advance Information to Technical Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**Revision History**