#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C                                                               |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90ls8535-4ac |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

sponding interrupt of External Interrupt Request 0 is executed from program memory address \$001. See also "External Interrupts."

#### Bits 5.0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and always read as zero.

#### **General Interrupt Flag Register – GIFR**

| Bit           | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |      |

|---------------|-------|-------|---|---|---|---|---|---|------|

| \$3A (\$5A)   | INTF1 | INTF0 | - | - | - | - | - | - | GIFR |

| Read/Write    | R/W   | R/W   | R | R | R | R | R | R | -    |

| Initial Value | 0     | 0     | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### Bit 7 – INTF1: External Interrupt Flag1

When an edge or logical change on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). This flag is always cleared (0) when the pin is configured for lowlevel interrupts, as the state of a low-level interrupt can be determined by reading the PIN register.

If the I-bit in SREG and the INT1 bit in GIMSK are set (one), the MCU will jump to the interrupt address \$002. For edge and logic change interrupts, this flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical "1" to it.

#### Bit 6 – INTF0: External Interrupt Flag0

When an edge or logical change on the INTO pin triggers an interrupt request, INTFO becomes set (one). This flag is always cleared (0) when the pin is configured for lowlevel interrupts, as the state of a low-level interrupt can be determined by reading the PIN register.

If the I-bit in SREG and the INT0 bit in GIMSK are set (one), the MCU will jump to the interrupt address \$001. For edge and logic change interrupts, this flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical "1" to it.

#### Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and always read as zero.

# **Timer/Counter Interrupt Mask**

**Register – TIMSK**

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1 | 0     | _     |

|---------------|-------|-------|--------|--------|--------|-------|---|-------|-------|

| \$39 (\$59)   | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | - | TOIE0 | TIMSK |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R | R/W   | -     |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0 | 0     |       |

#### Bit 7 – OCIE2: Timer/Counter2 Output Compare Match Interrupt Enable

When the OCIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match interrupt is enabled. The corresponding interrupt (at vector \$003) is executed if a compare match in Timer/Counter2 occurs (i.e., when the OCF2 bit is set in the Timer/Counter Interrupt Flag Register [TIFR]).

#### • Bit 6 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt (at vector \$004) is executed if an overflow in Timer/Counter2 occurs (i.e., when the TOV2 bit is set in the Timer/Counter Interrupt Flag Register [TIFR]).

| Table 8. | Interrupt 1 | Sense Control |

|----------|-------------|---------------|

|----------|-------------|---------------|

| ISC11 | ISC10 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT1 generates an interrupt request. |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.  |

The value on the INT pin is sampled before detecting edges. If edge interrupt is selected, pulses that last longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level-triggered interrupt will generate an interrupt request as long as the pin is held low.

#### • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bits 1 and 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask is set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 9.

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

Table 9. Interrupt 0 Sense Control

The value on the INT pin is sampled before detecting edges. If edge interrupt is selected, pulses that last longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level-triggered interrupt will generate an interrupt request as long as the pin is held low.

| To enter any of the three sleep modes, the SE bit in MCUCR must be set (one) and a |

|------------------------------------------------------------------------------------|

| SLEEP instruction must be executed. The SM0 and SM1 bits in the MCUCR register     |

| select which sleep mode (Idle, Power-down or Power Save) will be activated by the  |

| SLEEP instruction. See Table 7.                                                    |

|                                                                                    |

If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up, executes the interrupt routine and resumes execution from the instruction following SLEEP. The contents of the register file, SRAM and I/O memory are unaltered. If a reset occurs during Sleep Mode, the MCU wakes up and executes from the Reset vector.

Idle Mode When the SM1/SM0 bits are set to 00, the SLEEP instruction makes the MCU enter the Idle Mode, stopping the CPU but allowing SPI, UARTs, Analog Comparator, ADC, Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and UART Receive Complete interrupts. If wake-up from the Analog

Comparator Interrupt is not required, the Analog Comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status Register (ACSR). This will reduce power consumption in Idle Mode. When the MCU wakes up from Idle Mode, the CPU starts program execution immediately.

Power-down Mode When the SM1/SM0 bits are set to 10, the SLEEP instruction makes the MCU enter the Power-down mode. In this mode, the external oscillator is stopped while the external interrupts and the Watchdog (if enabled) continue operating. Only an external reset, a Watchdog reset (if enabled) or an external level interrupt can wake up the MCU.

Note that when a level-triggered interrupt is used for wake-up from power-down, the low level must be held for a time longer than the reset delay Time-out period  $t_{TOUT}$ .

When waking up from Power-down mode, a delay from the wake-up condition occurs until the wake-up becomes effective. This allows the clock to restart and become stable after having been stopped. The wake-up period is equal to the reset period, as shown in Table 3 on page 22.

If the wake-up condition disappears before the MCU wakes up and starts to execute, e.g., a low-level on is not held long enough, the interrupt causing the wake-up will not be executed.

Power Save Mode When the SM1/SM0 bits are 11, the SLEEP instruction makes the MCU enter the Power Save Mode. This mode is identical to Power-down, with one exception: If Timer/Counter2 is clocked asynchronously, i.e., the AS2 bit in ASSR is set, Timer/Counter2 will run during sleep. In addition to the power-down wake-up sources, the device can also wake up from either a Timer Overflow or Output Compare event from Timer/Counter2 if the corresponding Timer/Counter2 interrupt enable bits are set in TIMSK and the global interrupt enable bit in SREG is set.

When waking up from Power Save Mode by an external interrupt, two instruction cycles are executed before the interrupt flags are updated. When waking up by the asynchronous timer, three instruction cycles are executed before the flags are updated. During these cycles, the processor executes instructions, but the interrupt condition is not readable and the interrupt routine has not started yet.

When waking up from Power Save Mode by an asynchronous timer interrupt, the part will wake up even if global interrupts are disabled. To ensure that the part executes the interrupt routine when waking up, also set the global interrupt enable bit in SREG.

If the asynchronous timer is not clocked asynchronously, Power-down mode is recommended instead of Power Save Mode because the contents of the registers in the asynchronous timer should be considered undefined after wake-up in Power Save Mode, even if AS2 is 0.

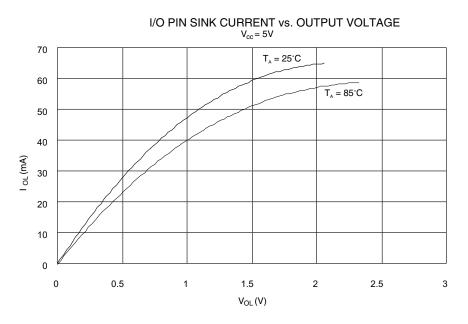

#### Timer/Counter0 Control Register – TCCR0

• Bits 7..3 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and always read zero.

• Bits 2, 1, 0 – CS02, CS01, CS00: Clock Select0, Bits 2, 1 and 0

The Clock Select0 bits 2,1 and 0 define the prescaling source of Timer/Counter0.

| Table 10. | Clock 0 | Prescale | Select |

|-----------|---------|----------|--------|

|-----------|---------|----------|--------|

| CS02 | CS01 | CS00 | Description                      |

|------|------|------|----------------------------------|

| 0    | 0    | 0    | Stop, Timer/Counter0 is stopped. |

| 0    | 0    | 1    | СК                               |

| 0    | 1    | 0    | СК/8                             |

| 0    | 1    | 1    | CK/64                            |

| 1    | 0    | 0    | CK/256                           |

| 1    | 0    | 1    | CK/1024                          |

| 1    | 1    | 0    | External Pin T0, falling edge    |

| 1    | 1    | 1    | External Pin T0, rising edge     |

The Stop condition provides a Timer Enable/Disable function. The prescaled CK modes are scaled directly from the CK oscillator clock. If the external pin modes are used, the corresponding setup must be performed in the actual Data Direction Control Register (cleared to zero gives an input pin).

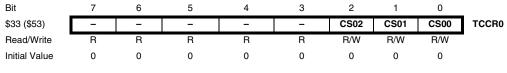

#### Timer Counter 0 – TCNT0

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the clock cycle following the write operation.

TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

- TCNT1 Timer/Counter1 Write: When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP register, and all 16 bits are written to the TCNT1 Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

- TCNT1 Timer/Counter1 Read: When the CPU reads the low byte TCNT1L, the data of the low byte TCNT1L is sent to the CPU and the data of the high byte TCNT1H is placed in the TEMP register. When the CPU reads the data in the high byte TCNT1H, the CPU receives the data in the TEMP register. Consequently, the low byte TCNT1L must be accessed first for a full 16-bit register read operation.

The Timer/Counter1 is realized as an up or up/down (in PWM mode) counter with read and write access. If Timer/Counter1 is written to and a clock source is selected, the Timer/Counter1 continues counting in the timer clock cycle after it is preset with the written value.

| Compare Register – OCR1AH | Bit           | 15      | 14       | 13       | 12         | 11         | 10        | 9   | 8   |        |

|---------------------------|---------------|---------|----------|----------|------------|------------|-----------|-----|-----|--------|

| AND OCR1AL                | \$2B (\$4B)   | MSB     |          |          |            |            |           |     |     | OCR1AH |

|                           | \$2A (\$4A)   |         |          |          |            |            |           |     | LSB | OCR1AL |

|                           | ·             | 7       | 6        | 5        | 4          | 3          | 2         | 1   | 0   | -      |

|                           | Read/Write    | R/W     | R/W      | R/W      | R/W        | R/W        | R/W       | R/W | R/W |        |

|                           |               | R/W     | R/W      | R/W      | R/W        | R/W        | R/W       | R/W | R/W |        |

|                           | Initial Value | 0       | 0        | 0        | 0          | 0          | 0         | 0   | 0   |        |

|                           |               | 0       | 0        | 0        | 0          | 0          | 0         | 0   | 0   |        |

|                           |               |         |          |          |            |            |           |     |     |        |

| Timer/Counter1 Output     |               |         |          |          |            |            |           |     |     |        |

| Compare Register – OCR1BH | Bit           | 15      | 14       | 13       | 12         | 11         | 10        | 9   | 8   |        |

| AND OCR1BL                | \$29 (\$49)   | MSB     |          |          |            |            |           |     |     | OCR1BH |

|                           | \$28 (\$48)   |         |          |          |            |            |           |     | LSB | OCR1BL |

|                           | ·             | 7       | 6        | 5        | 4          | 3          | 2         | 1   | 0   |        |

|                           | Read/Write    | R/W     | R/W      | R/W      | R/W        | R/W        | R/W       | R/W | R/W |        |

|                           |               | R/W     | R/W      | R/W      | R/W        | R/W        | R/W       | R/W | R/W |        |

|                           | Initial Value | 0       | 0        | 0        | 0          | 0          | 0         | 0   | 0   |        |

|                           |               | 0       | 0        | 0        | 0          | 0          | 0         | 0   | 0   |        |

|                           | The output of | compare | register | s are 16 | 6-bit read | d/write re | egisters. |     |     |        |

The Timer/Counter1 Output Compare registers contain the data to be continuously compared with Timer/Counter1. Actions on compare matches are specified in the Timer/Counter1 Control and Status registers. A compare match only occurs if Timer/Counter1 counts to the OCR value. A software write that sets TCNT1 and OCR1A or OCR1B to the same value does not generate a compare match.

A compare match will set the compare interrupt flag in the CPU clock cycle following the compare event.

Since the Output Compare Registers (OCR1A and OCR1B) are 16-bit registers, a temporary register (TEMP) is used when OCR1A/B are written to ensure that both bytes are updated simultaneously. When the CPU writes the high byte, OCR1AH or OCR1BH, the data is temporarily stored in the TEMP register. When the CPU writes the low byte,

**Timer/Counter1 Output**

# Asynchronous Operation of Timer/Counter2

When Timer/Counter2 operates asynchronously, some considerations must be taken.

- Warning: When switching between asynchronous and synchronous clocking of Timer/Counter2, the timer registers TCNT2, OCR2 and TCCR2 might get corrupted. A safe procedure for switching clock source is:

- 1. Disable the Timer/Counter2 interrupts OCIE2 and TOIE2.

- 2. Select clock source by setting AS2 as appropriate.

- 3. Write new values to TCNT2, OCR2 and TCCR2.

- 4. To switch to asynchronous operation: Wait for TCN2UB, OCR2UB and TCR2UB.

- 5. Clear the Timer/Counter2 interrupt flags.

- 6. Clear the TOV2 and OCF2 flags in TIFR.

- 7. Enable interrupts, if needed.

- When writing to one of the registers TCNT2, OCR2 or TCCR2, the value is transferred to a temporary register and latched after two positive edges on TOSC1. The user should not write a new value before the contents of the temporary register have been transferred to their destination. Each of the three mentioned registers have their individual temporary register. For example, writing to TCNT2 does not disturb an OCR2 write in progress. To detect that a transfer to the destination register has taken place, an Asynchronous Status Register (ASSR) has been implemented.

- When entering a Power Save Mode after having written to TCNT2, OCR2 or TCCR2, the user must wait until the written register has been updated if Timer/Counter2 is used to wake up the device. Otherwise, the MCU will go to sleep before the changes have had any effect. This is extremely important if the Output Compare2 interrupt is used to wake up the device; Output Compare is disabled during write to OCR2 or TCNT2. If the write cycle is not finished (i.e., the user goes to sleep before the OCR2UB bit returns to zero), the device will never get a compare match and the MCU will not wake up.

- If Timer/Counter2 is used to wake up the device from Power Save Mode, precautions must be taken if the user wants to re-enter Power Save Mode: The interrupt logic needs one TOSC1 cycle to be reset. If the time between wake up and re-entering Power Save Mode is less than one TOSC1 cycle, the interrupt will not occur and the device will fail to wake up. If the user is in doubt whether the time before re-entering Power Save is sufficient, the following algorithm can be used to ensure that one TOSC1 cycle has elapsed:

- 1. Write a value to TCCR2, TCNT2 or OCR2.

- 2. Wait until the corresponding Update Busy flag in ASSR returns to zero.

- 3. Enter Power Save Mode.

- When the asynchronous operation is selected, the 32 kHz oscillator for Timer/Counter2 is always running, except in Power-down mode. After a power-up reset or wake-up from power-down, the user should be aware of the fact that this oscillator might take as long as one second to stabilize. The user is advised to wait for at least one second before using Timer/Counter2 after power-up or wake-up from power-down. The content of all Timer/Counter2 registers must be considered lost after a wake-up from power-down due to the unstable clock signal upon start-up, regardless of whether the oscillator is in use or a clock signal is applied to the TOSC pin.

- Description of wake-up from Power Save Mode when the timer is clocked asynchronously: When the interrupt condition is met, the wake-up process is started on the following cycle of the timer clock, that is, the timer is always advanced by at

## EEPROM Read/Write Access

**te** The EEPROM access registers are accessible in the I/O space.

The write access time is in the range of 2.5 - 4 ms, depending on the V<sub>CC</sub> voltages. A self-timing function lets the user software detect when the next byte can be written. A special EEPROM Ready interrupt can be set to trigger when the EEPROM is ready to accept new data.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

#### EEPROM Address Register – EEARH and EEARL

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |       |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$1F (\$3F)   | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| \$1E (\$3E)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | х     |       |

|               | х     | Х     | Х     | Х     | х     | Х     | Х     | Х     |       |

The EEPROM address registers (EEARH and EEARL) specify the EEPROM address in the 512-byte EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 511.

#### EEPROM Data Register – EEDR

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$1D (\$3D)   | MSB |     |     |     |     |     |     | LSB | EEDR |

| Read/Write    | R/W | -    |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### • Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR register contains the data to be written to the EEPROM in the address given by the EEAR register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

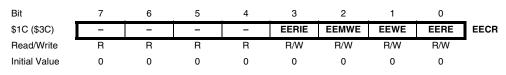

# EEPROM Control Register – EECR

#### • Bit 7..4 - Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

#### • Bit 3 – EERIE: EEPROM Ready Interrupt Enable

When the I-bit in SREG and EERIE are set (one), the EEPROM Ready Interrupt is enabled. When cleared (zero), the interrupt is disabled. The EEPROM Ready Interrupt generates a constant interrupt when EEWE is cleared (zero).

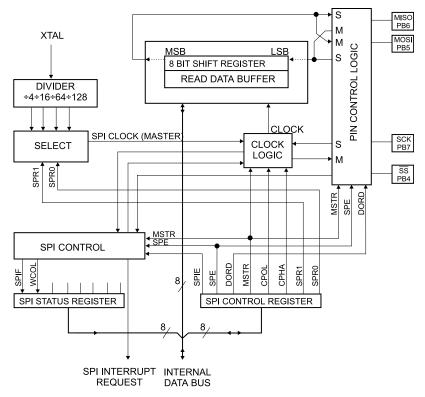

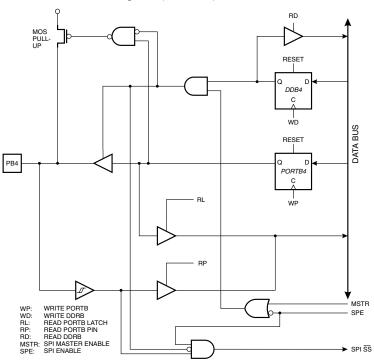

## Serial Peripheral Interface – SPI

The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the AT90S8535 and peripheral devices or between several AVR devices. The AT90S8535 SPI features include the following:

- Full-duplex, 3-wire Synchronous Data Transfer

- Master or Slave Operation

- LSB First or MSB First Data Transfer

- Four Programmable Bit Rates

- End-of-transmission Interrupt Flag

- Write Collision Flag Protection

- Wake-up from Idle Mode

Figure 37. SPI Block Diagram

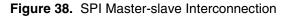

The interconnection between master and slave CPUs with SPI is shown in Figure 38. The PB7(SCK) pin is the clock output in the Master Mode and is the clock input in the Slave Mode. Writing to the SPI Data Register of the master CPU starts the SPI clock generator and the data written shifts out of the PB5(MOSI) pin and into the PB5(MOSI) pin of the slave CPU. After shifting one byte, the SPI clock generator stops, setting the end-of-transmission flag (SPIF). If the SPI interrupt enable bit (SPIE) in the SPCR register is set, an interrupt is requested. The Slave Select input, PB4(SS), is set low to select an individual slave SPI device. The two shift registers in the master and the slave can be considered as one distributed 16-bit circular shift register. This is shown in Figure 38. When data is shifted from the master to the slave, data is also shifted in the opposite direction, simultaneously. During one shift cycle, data in the master and the slave is interchanged.

The system is single-buffered in the transmit direction and double-buffered in the receive direction. This means that bytes to be transmitted cannot be written to the SPI Data Register before the entire shift cycle is completed. When receiving data, however, a received byte must be read from the SPI Data Register before the next byte has been completely shifted in. Otherwise, the first byte is lost.

When the SPI is enabled, the data direction of the MOSI, MISO, SCK and  $\overline{SS}$  pins is overridden according to Table 22.

Table 22. SPI Pin Overrides

| Pin  | Direction, Master SPI | Direction, Slave SPI |  |  |

|------|-----------------------|----------------------|--|--|

| MOSI | User Defined          | Input                |  |  |

| MISO | Input                 | User Defined         |  |  |

| SCK  | User Defined          | Input                |  |  |

| SS   | User Defined          | Input                |  |  |

Note: See "Alternate Functions of Port B" on page 79 for a detailed description of how to define the direction of the user-defined SPI pins.

The FE bit is cleared when the stop bit of received data is one.

#### • Bit 3 – OR: OverRun

This bit is set if an Overrun condition is detected, i.e., when a character already present in the UDR register is not read before the next character has been shifted into the Receiver Shift register. The OR bit is buffered, which means that it will be set once the valid data still in UDR is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

#### • Bits 2..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

#### **UART Control Register – UCR**

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    | _   |

|---------------|-------|-------|-------|------|------|------|------|------|-----|

| \$0A (\$2A)   | RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 | UCR |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R    | W    | •   |

| Initial Value | 0     | 0     | 0     | 0    | 0    | 0    | 1    | 0    |     |

#### Bit 7 – RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in USR will cause the Receive Complete Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 6 – TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in USR will cause the Transmit Complete Interrupt routine to be executed provided that global interrupts are enabled.

#### Bit 5 – UDRIE: UART Data Register Empty Interrupt Enable

When this bit is set (one), a setting of the UDRE bit in USR will cause the UART Data Register Empty Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 4 – RXEN: Receiver Enable

This bit enables the UART receiver when set (one). When the receiver is disabled, the RXC, OR and FE status flags cannot become set. If these flags are set, turning off RXEN does not cause them to be cleared.

#### • Bit 3 – TXEN: Transmitter Enable

This bit enables the UART transmitter when set (one). When disabling the transmitter while transmitting a character, the transmitter is not disabled before the character in the shift register plus any following character in UDR has been completely transmitted.

#### • Bit 2 – CHR9: 9 Bit Characters

When this bit is set (one), transmitted and received characters are 9 bits long, plus start and stop bits. The ninth bit is read and written by using the RXB8 and TXB8 bits in UCR, respectively. The ninth data bit can be used as an extra stop bit or a parity bit.

#### Bit 1 – RXB8: Receive Data Bit 8

When CHR9 is set (one), RXB8 is the ninth data bit of the received character.

#### • Bit 0 – TXB8: Transmit Data Bit 8

When CHR9 is set (one), TXB8 is the ninth data bit in the character to be transmitted.

# AT90S/LS8535

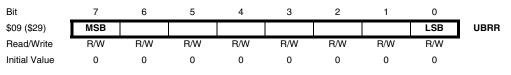

# UART Baud Rate Register – UBRR

The UBRR register is an 8-bit read/write register that specifies the UART Baud Rate according to the equation on the previous page.

## **Analog Comparator**

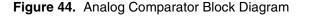

The Analog Comparator compares the input values on the positive input PB2 (AIN0) and negative input PB3 (AIN1). When the voltage on the positive input PB2 (AIN0) is higher than the voltage on the negative input PB3 (AIN1), the Analog Comparator Output (ACO) is set (one). The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 44.

#### • Bit 7 – ACD: Analog Comparator Disable

When this bit is set (one), the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. When changing the ACD bit, the Analog Comparator interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

#### • Bit 6 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8535 and will always read as zero.

#### • Bit 5 – ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

#### • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logical "1" to the flag.

#### • Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is set (one) and the I-bit in the Status Register is set (one), the Analog Comparator interrupt is activated. When cleared (zero), the interrupt is disabled.

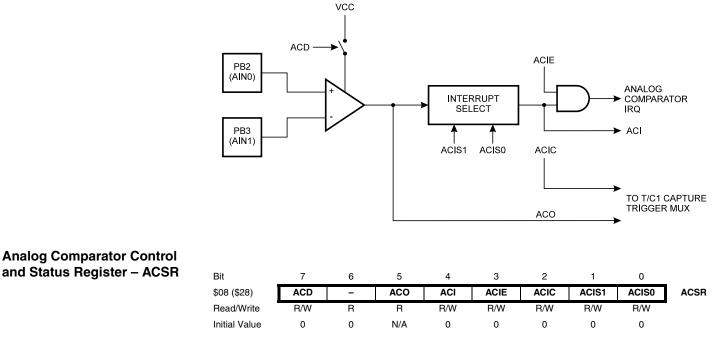

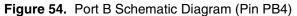

#### Port B As General Digital I/O

Alternate Functions of Port B

All eight pins in Port B have equal functionality when used as digital I/O pins.

PBn, general I/O pin: The DDBn bit in the DDRB register selects the direction of this pin. If DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin is configured as an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, the PORTBn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.

| DDBn | PORTBn | I/O       | Pull-up | Comment                                    |  |  |

|------|--------|-----------|---------|--------------------------------------------|--|--|

| 0    | 0      | Input     | No      | Tri-state (high-Z)                         |  |  |

| 0    | 1      | Input Yes |         | PBn will source current if ext. pulled low |  |  |

| 1    | 0      | Output    | No      | Push-pull Zero Output                      |  |  |

| 1    | 1      | Output    | No      | Push-pull One Output                       |  |  |

Table 31. DDBn Effects on Port B Pins

Note: n: 7,6...0, pin number.

The alternate pin configuration is as follows:

#### • SCK – Port B, Bit 7

SCK: Master clock output, slave clock input pin for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB7. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB7. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB7 bit. See the description of the SPI port for further details.

#### • MISO - Port B, Bit 6

MISO: Master data input, slave data output pin for SPI channel. When the SPI is enabled as a master, this pin is configured as an input regardless of the setting of DDB6. When the SPI is enabled as a slave, the data direction of this pin is controlled by DDB6. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB6 bit. See the description of the SPI port for further details.

#### • MOSI – Port B, Bit 5

MOSI: SPI Master data output, slave data input for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB5 bit. See the description of the SPI port for further details.

#### • SS – Port B, Bit 4

$\overline{SS}$ : Slave port select input. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB4. As a slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB4. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB4 bit. See the description of the SPI port for further details.

#### • AIN1 – Port B, Bit 3

AIN1, Analog Comparator Negative Input. When configured as an input (DDB3 is cleared [zero]) and with the internal MOS pull-up resistor switched off (PB3 is cleared [zero]), this pin also serves as the negative input of the on-chip Analog Comparator. During Power-down mode, the Schmitt trigger of the digital input is disconnected. This

Figure 53. Port B Schematic Diagram (Pins PB2 and PB3)

Table 37. Pin Name Mapping

| Signal Name in<br>Programming Mode | Pin Name | I/O | Function                                                            |

|------------------------------------|----------|-----|---------------------------------------------------------------------|

| RDY/BSY                            | PD1      | 0   | 0: Device is busy programming, 1: Device is ready for new command   |

| ŌĒ                                 | PD2      | I   | Output Enable (Active low)                                          |

| WR PD3                             |          | I   | Write Pulse (Active low)                                            |

| BS                                 | PD4      | I   | Byte Select ("0" selects low byte, "1" selects high byte)           |

| XA0                                | PD5      | Ι   | XTAL Action Bit 0                                                   |

| XA1                                | PD6      | Ι   | XTAL Action Bit 1                                                   |

| DATA                               | PB7 - 0  | I/O | Bi-directional Data Bus (Output when $\overline{\text{OE}}$ is low) |

Table 38. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                              |

|-----|-----|--------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (high or low address byte determined by BS) |

| 0   | 1   | Load Data (High or low data byte for Flash determined by BS)             |

| 1   | 0   | Load Command                                                             |

| 1   | 1   | No Action, Idle                                                          |

#### Table 39. Command Byte Bit Coding

| Command Byte | Command Executed        |

|--------------|-------------------------|

| 1000 0000    | Chip Erase              |

| 0100 0000    | Write Fuse Bits         |

| 0010 0000    | Write Lock Bits         |

| 0001 0000    | Write Flash             |

| 0001 0001    | Write EEPROM            |

| 0000 1000    | Read Signature Bytes    |

| 0000 0100    | Read Lock and Fuse Bits |

| 0000 0010    | Read Flash              |

| 0000 0011    | Read EEPROM             |

#### Enter Programming Mode

The following algorithm puts the device in Parallel Programming Mode:

- 1. Apply supply voltage according to Table 36, between  $V_{\text{CC}}$  and GND.

- 2. Set the  $\overline{\text{RESET}}$  and BS pin to "0" and wait at least 100 ns.

- 3. Apply 11.5 12.5V to RESET. Any activity on BS within 100 ns after +12V has been applied to RESET, will cause the device to fail entering programming mode.

- If a Chip Erase is performed (must be done to erase the Flash), wait t<sub>WD\_ERASE</sub> after the instruction, give RESET a positive pulse and start over from step 2. See Table 44 for t<sub>WD ERASE</sub> value.

- 5. The Flash or EEPROM array is programmed one byte at a time by supplying the address and data together with the appropriate Write instruction. An EEPROM memory location is first automatically erased before new data is written. Use Data Polling to detect when the next byte in the Flash or EEPROM can be written. If polling is not used, wait t<sub>WD\_PROG</sub> before transmitting the next instruction. See Table 45 for t<sub>WD\_PROG</sub> value. In an erased device, no \$FFs in the data file(s) needs to be programmed.

- 6. Any memory location can be verified by using the Read instruction that returns the content at the selected address at the serial output MISO (PB6) pin.

- 7. At the end of the programming session, **RESET** can be set high to commence normal operation.

- 8. Power-off sequence (if needed):

Set XTAL1 to "0" (if a crystal is not used). Set  $\overline{\text{RESET}}$  to "1".

Turn V<sub>CC</sub> power off.

# Data Polling EEPROMWhen a byte is being programmed into the EEPROM, reading the address location<br/>being programmed will give the value P1 until the auto-erase is finished and then the<br/>value P2. See Table 41 for P1 and P2 values.

At the time the device is ready for a new EEPROM byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the values P1 and P2, so when programming these values, the user will have to wait for at least the prescribed time  $t_{WD_PROG}$  before programming the next byte. See Table 45 for  $t_{WD_PROG}$  value. As a chip-erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF can be skipped. This does not apply if the EEPROM is reprogrammed without first chip-erasing the device.

#### Table 41. Read Back Value during EEPROM Polling

| Part         | P1   | P2   |  |

|--------------|------|------|--|

| AT90S/LS8535 | \$00 | \$FF |  |

#### **Data Polling Flash**

When a byte is being programmed into the Flash, reading the address location being programmed will give the value FF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value FF, so when programming this value, the user will have to wait for at least  $t_{WD_PROG}$  before programming the next byte. As a chiperased device contains FF in all locations, programming of addresses that are meant to contain FF can be skipped.

#### Figure 72. Serial Programming Waveforms

# **Electrical Characteristics**

## **Absolute Maximum Ratings\***

| Operating Temperature40°C to +105°C                                                     |

|-----------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                       |

| Voltage on Any Pin except RESET<br>with Respect to Ground1.0V to V <sub>CC</sub> + 0.5V |

| Voltage on RESET with Respect to Ground1.0V to +13.0V                                   |

| Maximum Operating Voltage 6.6V                                                          |

| I/O Pin Maximum Current 40.0 mA                                                         |

| Maximum Current V <sub>CC</sub><br>and GND (PDIP package)                               |

| Maximum Current V <sub>CC</sub><br>and GND (TQFP, PLCC package) 400.0 mA                |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Characteristics**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ ,  $V_{CC} = 2.7V$  to 6.0V (unless otherwise noted)

| Symbol              | Parameter                                                | Condition                                                                        | Min                                | Тур | Max                                | Units  |

|---------------------|----------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------|-----|------------------------------------|--------|

| V <sub>IL</sub>     | Input Low Voltage                                        |                                                                                  | -0.5                               |     | 0.3V <sub>CC</sub> <sup>(1)</sup>  | V      |

| V <sub>IL1</sub>    | Input Low Voltage                                        | XTAL                                                                             | -0.5                               |     | 0.2 V <sub>CC</sub> <sup>(1)</sup> | V      |

| V <sub>IH</sub>     | Input High Voltage                                       | Except (XTAL, RESET)                                                             | 0.6 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> + 0.5              | V      |

| V <sub>IH1</sub>    | Input High Voltage                                       | XTAL                                                                             | 0.8 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> + 0.5              | V      |

| V <sub>IH2</sub>    | Input High Voltage                                       | RESET                                                                            | 0.9 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> + 0.5              | V      |

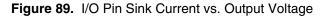

| V <sub>OL</sub>     | Output Low Voltage <sup>(3)</sup><br>(Ports A, B, C, D)  | $I_{OL} = 20 \text{ mA}, V_{CC} = 5V$<br>$I_{OL} = 10 \text{ mA}, V_{CC} = 3V$   |                                    |     | 0.6<br>0.5                         | V<br>V |

| V <sub>OH</sub>     | Output High Voltage <sup>(4)</sup><br>(Ports A, B, C, D) | $I_{OH} = -3 \text{ mA}, V_{CC} = 5V$<br>$I_{OH} = -1.5 \text{ mA}, V_{CC} = 3V$ | 4.2<br>2.3                         |     |                                    | V<br>V |

| I <sub>IL</sub>     | Input Leakage<br>Current I/O Pin                         | V <sub>CC</sub> = 6V, Vin = 0.45V<br>(absolute value)                            |                                    |     | 8.0                                | μA     |

| I <sub>IH</sub>     | Input Leakage<br>Current I/O Pin                         | V <sub>CC</sub> = 6V, Vin = 6.0V<br>(absolute value)                             |                                    |     | 8.0                                | μA     |

| RRST                | Reset Pull-up                                            |                                                                                  | 100.0                              |     | 500.0                              | kΩ     |

| R <sub>I/O</sub>    | I/O Pin Pull-up Resistor                                 |                                                                                  | 35.0                               |     | 120.0                              | kΩ     |

|                     |                                                          | Active 4 MHz, $V_{CC} = 3V$                                                      |                                    |     | 5.0                                | mA     |

|                     |                                                          | Idle 4 MHz, $V_{CC} = 3V$                                                        |                                    |     | 3.0                                | mA     |

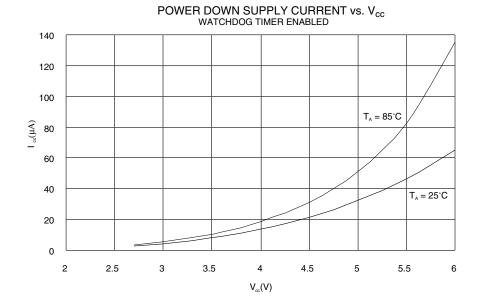

| I <sub>CC</sub> Pow |                                                          | Power-down, $V_{CC} = 3V$<br>WDT enabled <sup>(5)</sup>                          |                                    |     | 15.0                               | μA     |

|                     | Power Supply Current                                     | Power-down, $V_{CC} = 3V$<br>WDT disabled <sup>(5)</sup>                         |                                    |     | 5.0                                | μA     |

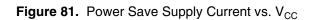

|                     |                                                          | Power Save, $V_{CC} = 3V$<br>WDT disabled <sup>(5)</sup>                         |                                    |     | 15.0                               | μA     |

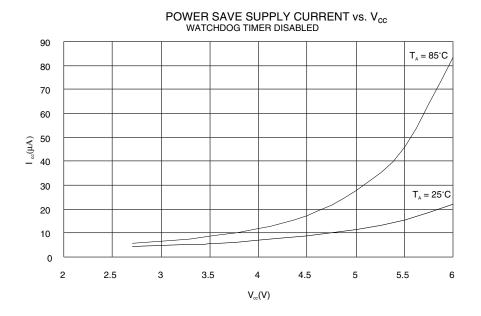

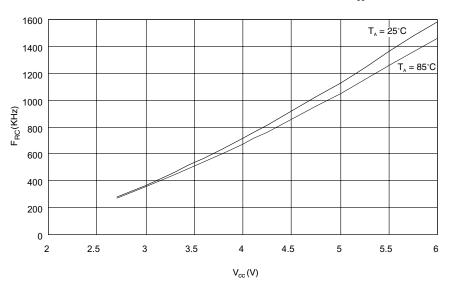

WATCHDOG OSCILLATOR FREQUENCY vs. Vcc

Note: Sink and source capabilities of I/O ports are measured on one pin at a time.

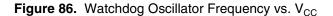

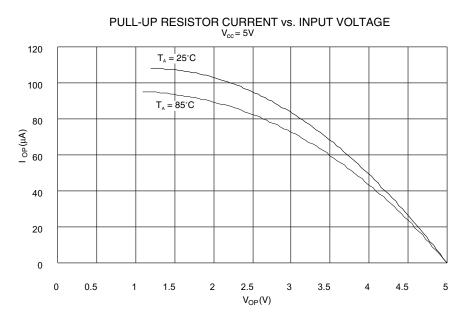

Figure 87. Pull-up Resistor Current vs. Input Voltage

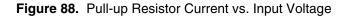

PULL-UP RESISTOR CURRENT vs. INPUT VOLTAGE  $V_{cc}$  = 2.7V