Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C                                                              |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8535-8jc |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

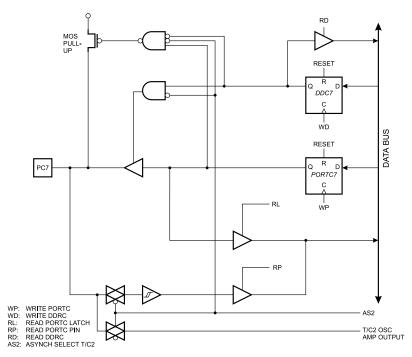

|                 | current if the pull-up resistors are activated. Two Port C pins can alternatively be used as oscillator for Timer/Counter2.                                                                                                                               |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                   |

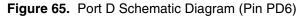

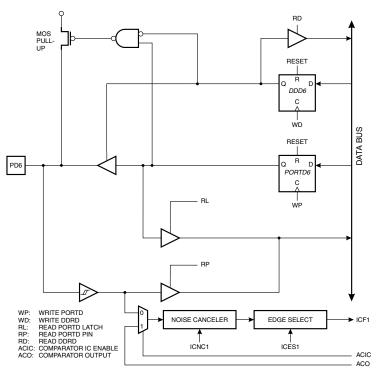

| Port D (PD7PD0) | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated.                   |

|                 | Port D also serves the functions of various special features of the AT90S8535 as listed on page 86.                                                                                                                                                       |

|                 | The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                   |

| RESET           | Reset input. An external reset is generated by a low level on the $\overrightarrow{\text{RESET}}$ pin. Reset pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.     |

| XTAL1           | Input to the inverting oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                            |

| XTAL2           | Output from the inverting oscillator amplifier.                                                                                                                                                                                                           |

| AVCC            | AVCC is the supply voltage pin for Port A and the A/D Converter. If the ADC is not used, this pin must be connected to VCC. If the ADC is used, this pin must be connected to VCC via a low-pass filter. See page 68 for details on operation of the ADC. |

| AREF            | AREF is the analog reference input for the A/D Converter. For ADC operations, a voltage in the range 2V to $AV_{CC}$ must be applied to this pin.                                                                                                         |

| AGND            | Analog ground. If the board has a separate analog ground plane, this pin should be con-<br>nected to this ground plane. Otherwise, connect to GND.                                                                                                        |

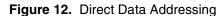

#### **Data Direct**

A 16-bit data address is contained in the 16 LSBs of a 2-word instruction. Rd/Rr specify the destination or source register.

0

0

а

Data Space

\$0000

025F

10

Y OR Z - REGISTER

n

65

15

15

OP

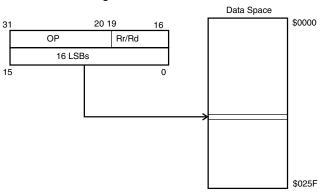

Operand address is the result of the Y- or Z-register contents added to the address contained in six bits of the instruction word.

+

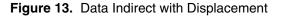

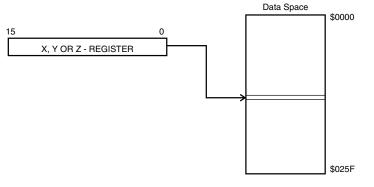

**Data Indirect**

Figure 14. Data Indirect Addressing

Operand address is the contents of the X-, Y-, or the Z-register.

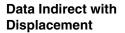

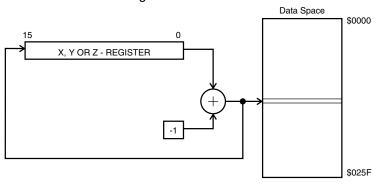

Figure 15. Data Indirect Addressing with Pre-decrement

The X-, Y-, or the Z-register is decremented before the operation. Operand address is the decremented contents of the X-, Y-, or the Z-register.

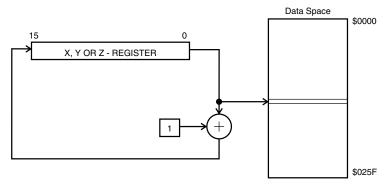

Figure 16. Data Indirect Addressing with Post-increment

The X-, Y-, or the Z-register is incremented after the operation. Operand address is the content of the X-, Y-, or the Z-register prior to incrementing.

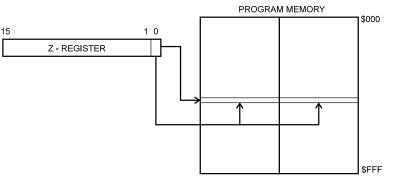

# Constant Addressing Using the LPM Instruction

Figure 17. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 4K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

#### Data Indirect with Predecrement

**Data Indirect with Post-**

increment

sponding interrupt of External Interrupt Request 0 is executed from program memory address \$001. See also "External Interrupts."

#### Bits 5.0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and always read as zero.

#### **General Interrupt Flag Register – GIFR**

| Bit           | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |      |

|---------------|-------|-------|---|---|---|---|---|---|------|

| \$3A (\$5A)   | INTF1 | INTF0 | - | - | - | - | - | - | GIFR |

| Read/Write    | R/W   | R/W   | R | R | R | R | R | R | -    |

| Initial Value | 0     | 0     | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### Bit 7 – INTF1: External Interrupt Flag1

When an edge or logical change on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). This flag is always cleared (0) when the pin is configured for lowlevel interrupts, as the state of a low-level interrupt can be determined by reading the PIN register.

If the I-bit in SREG and the INT1 bit in GIMSK are set (one), the MCU will jump to the interrupt address \$002. For edge and logic change interrupts, this flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical "1" to it.

#### Bit 6 – INTF0: External Interrupt Flag0

When an edge or logical change on the INTO pin triggers an interrupt request, INTFO becomes set (one). This flag is always cleared (0) when the pin is configured for lowlevel interrupts, as the state of a low-level interrupt can be determined by reading the PIN register.

If the I-bit in SREG and the INT0 bit in GIMSK are set (one), the MCU will jump to the interrupt address \$001. For edge and logic change interrupts, this flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical "1" to it.

#### Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and always read as zero.

## **Timer/Counter Interrupt Mask**

**Register – TIMSK**

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1 | 0     | _     |

|---------------|-------|-------|--------|--------|--------|-------|---|-------|-------|

| \$39 (\$59)   | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | - | TOIE0 | TIMSK |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R | R/W   | -     |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0 | 0     |       |

#### Bit 7 – OCIE2: Timer/Counter2 Output Compare Match Interrupt Enable

When the OCIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match interrupt is enabled. The corresponding interrupt (at vector \$003) is executed if a compare match in Timer/Counter2 occurs (i.e., when the OCF2 bit is set in the Timer/Counter Interrupt Flag Register [TIFR]).

### • Bit 6 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt (at vector \$004) is executed if an overflow in Timer/Counter2 occurs (i.e., when the TOV2 bit is set in the Timer/Counter Interrupt Flag Register [TIFR]).

| Table 8. | Interrupt 1 | Sense Control |

|----------|-------------|---------------|

|----------|-------------|---------------|

| ISC11 | ISC10 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT1 generates an interrupt request. |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.  |

The value on the INT pin is sampled before detecting edges. If edge interrupt is selected, pulses that last longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level-triggered interrupt will generate an interrupt request as long as the pin is held low.

#### • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bits 1 and 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask is set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 9.

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

Table 9. Interrupt 0 Sense Control

The value on the INT pin is sampled before detecting edges. If edge interrupt is selected, pulses that last longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level-triggered interrupt will generate an interrupt request as long as the pin is held low.

| To enter any of the three sleep modes, the SE bit in MCUCR must be set (one) and a |

|------------------------------------------------------------------------------------|

| SLEEP instruction must be executed. The SM0 and SM1 bits in the MCUCR register     |

| select which sleep mode (Idle, Power-down or Power Save) will be activated by the  |

| SLEEP instruction. See Table 7.                                                    |

|                                                                                    |

If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up, executes the interrupt routine and resumes execution from the instruction following SLEEP. The contents of the register file, SRAM and I/O memory are unaltered. If a reset occurs during Sleep Mode, the MCU wakes up and executes from the Reset vector.

Idle Mode When the SM1/SM0 bits are set to 00, the SLEEP instruction makes the MCU enter the Idle Mode, stopping the CPU but allowing SPI, UARTs, Analog Comparator, ADC, Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and UART Receive Complete interrupts. If wake-up from the Analog

## **Timer/Counters**

The AT90S8535 provides three general-purpose Timer/Counters – two 8-bit T/Cs and one 16-bit T/C. Timer/Counter2 can optionally be asynchronously clocked from an external oscillator. This oscillator is optimized for use with a 32.768 kHz watch crystal, enabling use of Timer/Counter2 as a Real-time Clock (RTC). Timer/Counters 0 and 1 have individual prescaling selection from the same 10-bit prescaling timer. Timer/Counter2 has its own prescaler. These Timer/Counters can either be used as a timer with an internal clock time base or as a counter with an external pin connection that triggers the counting.

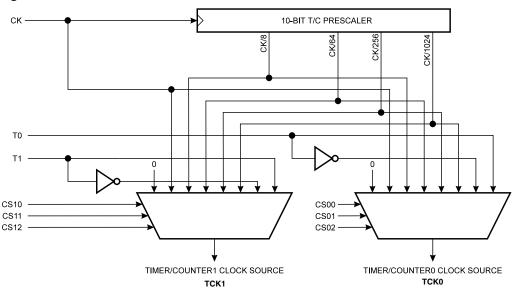

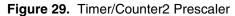

### Timer/Counter Prescalers

Figure 28. Prescaler for Timer/Counter0 and 1

For Timer/Counters 0 and 1, the four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024, where CK is the oscillator clock. For the two Timer/Counters 0 and 1, CK, external source and stop can also be selected as clock sources.

The clock source for Timer/Counter2 prescaler is named PCK2. PCK2 is by default connected to the main system clock (CK). By setting the AS2 bit in ASSR, Timer/Counter2 prescaler is asynchronously clocked from the PC6(TOSC1) pin. This enables use of Timer/Counter2 as a Real-time Clock (RTC). When AS2 is set, pins PC6(TOSC1) and PC7(TOSC2) are disconnected from Port C. A crystal can then be connected between the PC6(TOSC1) and PC7(TOSC2) pins to serve as an independent clock source for Timer/Counter2. The oscillator is optimized for use with a 32.768 kHz crystal. Applying an external clock source to TOSC1 is not recommended.

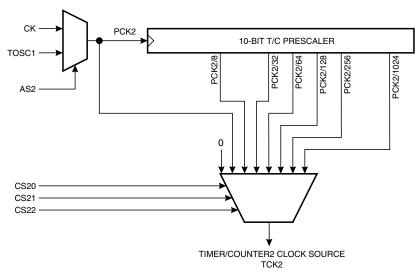

#### 8-bit Timer/Counter0 Figure 30 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK or an external pin. In addition, it can be stopped as described in the specification for the Timer/Counter0 Control Register (TCCR0). The overflow status flag is found in the Timer/Counter Interrupt Flag Register (TIFR). Control signals are found in the Timer/Counter0 Control Register (TCCR0). The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register (TIMSK).

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

#### Figure 30. Timer/Counter0 Block Diagram

up-counting and down-counting values are reached simultaneously. When the prescaler is in use (CS12..CS10  $\neq$  001 or 000), the PWM output goes active when the counter reaches TOP value, but the down-counting compare match is not interpreted to be reached before the next time the counter reaches the TOP value, making a one-period PWM pulse.

| COM1X1 | COM1X0 | Effect on OCX1                                                                                 |

|--------|--------|------------------------------------------------------------------------------------------------|

| 0      | 0      | Not connected                                                                                  |

| 0      | 1      | Not connected                                                                                  |

| 1      | 0      | Cleared on compare match, up-counting. Set on compare match, down-counting (non-inverted PWM). |

| 1      | 1      | Cleared on compare match, down-counting. Set on compare match, up-counting (inverted PWM).     |

Table 15. Compare1 Mode Select in PWM Mode

Note: X = A or B

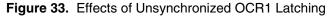

Note that in the PWM mode, the 10 least significant OCR1A/OCR1B bits, when written, are transferred to a temporary location. They are latched when Timer/Counter1 reaches the value TOP. This prevents the occurrence of odd-length PWM pulses (glitches) in the event of an unsynchronized OCR1A/OCR1B write. See Figure 33 for an example.

Note: X = A or B

During the time between the write and the latch operations, a read from OCR1A or OCR1B will read the contents of the temporary location. This means that the most recently written value always will read out of OCR1A/B.

When the OCR1A/OCR1B contains \$0000 or TOP, the output OC1A/OC1B is updated to low or high on the next compare match according to the settings of COM1A1/COM1A0 or COM1B1/COM1B0. This is shown in Table 16.

Table 16. PWM Outputs OCR1X = \$0000 or TOP

| COM1X1 | COM1X0 | OCR1X  | Output OC1X |

|--------|--------|--------|-------------|

| 1      | 0      | \$0000 | L           |

## EEPROM Read/Write Access

**te** The EEPROM access registers are accessible in the I/O space.

The write access time is in the range of 2.5 - 4 ms, depending on the V<sub>CC</sub> voltages. A self-timing function lets the user software detect when the next byte can be written. A special EEPROM Ready interrupt can be set to trigger when the EEPROM is ready to accept new data.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

#### EEPROM Address Register – EEARH and EEARL

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |       |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$1F (\$3F)   | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| \$1E (\$3E)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | х     |       |

|               | х     | Х     | Х     | Х     | х     | Х     | Х     | Х     |       |

The EEPROM address registers (EEARH and EEARL) specify the EEPROM address in the 512-byte EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 511.

### EEPROM Data Register – EEDR

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$1D (\$3D)   | MSB |     |     |     |     |     |     | LSB | EEDR |

| Read/Write    | R/W | -    |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### • Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR register contains the data to be written to the EEPROM in the address given by the EEAR register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

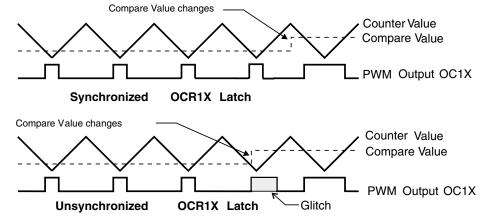

# EEPROM Control Register – EECR

#### • Bit 7..4 - Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

### • Bit 3 – EERIE: EEPROM Ready Interrupt Enable

When the I-bit in SREG and EERIE are set (one), the EEPROM Ready Interrupt is enabled. When cleared (zero), the interrupt is disabled. The EEPROM Ready Interrupt generates a constant interrupt when EEWE is cleared (zero).

#### • Bits 1,0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the oscillator clock frequency  $f_{cl}$  is shown in Table 23.

Table 23. Relationship between SCK and the Oscillator Frequency

| SPR1 | SPR0 | SCK Frequency        |

|------|------|----------------------|

| 0    | 0    | f <sub>cl</sub> /4   |

| 0    | 1    | f <sub>cl</sub> /16  |

| 1    | 0    | f <sub>cl</sub> /64  |

| 1    | 1    | f <sub>cl</sub> /128 |

#### SPI Status Register – SPSR

| Bit           | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 | _    |

|---------------|------|------|---|---|---|---|---|---|------|

| \$0E (\$2E)   | SPIF | WCOL | - | - | - | - | - | - | SPSR |

| Read/Write    | R    | R    | R | R | R | R | R | R | -    |

| Initial Value | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### Bit 7 – SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF bit is set (one) and an interrupt is generated if SPIE in SPCR is set (one) and global interrupts are enabled. If  $\overline{SS}$  is an input and is driven low when the SPI is in Master Mode, this will also set the SPIF flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI Status Register with SPIF set (one), then accessing the SPI Data Register (SPDR).

#### • Bit 6 – WCOL: Write Collision flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared (zero) by first reading the SPI Status Register with WCOL set (one) and then accessing the SPI Data Register.

#### • Bit 5..0 - Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

The SPI interface on the AT90S8535 is also used for program memory and EEPROM downloading or uploading. See page 99 for serial programming and verification.

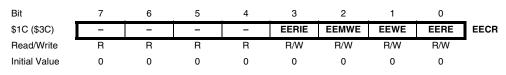

#### SPI Data Register – SPDR

The SPI Data Register is a read/write register used for data transfer between the register file and the SPI Shift Register. Writing to the register initiates data transmission. Reading the register causes the Shift Register Receive buffer to be read.

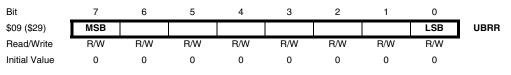

# UART Baud Rate Register – UBRR

The UBRR register is an 8-bit read/write register that specifies the UART Baud Rate according to the equation on the previous page.

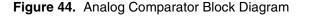

## **Analog Comparator**

The Analog Comparator compares the input values on the positive input PB2 (AIN0) and negative input PB3 (AIN1). When the voltage on the positive input PB2 (AIN0) is higher than the voltage on the negative input PB3 (AIN1), the Analog Comparator Output (ACO) is set (one). The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 44.

#### • Bit 7 – ACD: Analog Comparator Disable

When this bit is set (one), the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. When changing the ACD bit, the Analog Comparator interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

#### • Bit 6 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8535 and will always read as zero.

#### • Bit 5 – ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

#### • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logical "1" to the flag.

#### • Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is set (one) and the I-bit in the Status Register is set (one), the Analog Comparator interrupt is activated. When cleared (zero), the interrupt is disabled.

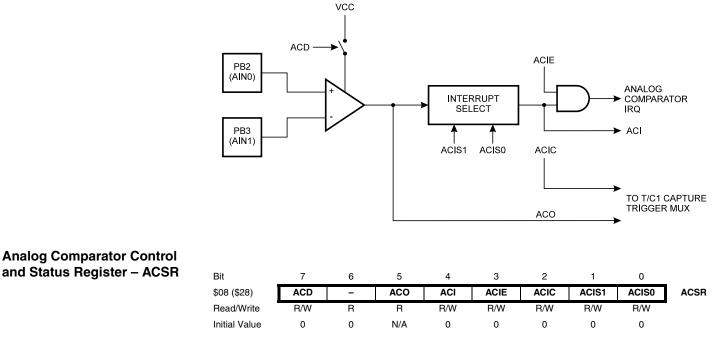

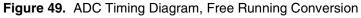

#### Table 26. ADC Conversion Time

| Condition           | Sample and Hold (Cycles from Start of Conversion) | Conversion<br>Time (Cycles) | Conversion<br>Time (µs) |

|---------------------|---------------------------------------------------|-----------------------------|-------------------------|

| Extended Conversion | 14                                                | 25                          | 125 - 500               |

| Normal Conversion   | 14                                                | 26                          | 130 - 520               |

# ADC Noise Canceler Function

The ADC features a noise canceler that enables conversion during Idle Mode to reduce noise induced from the CPU core. To make use of this feature, the following procedure should be used:

- 1. Make sure that the ADC is enabled and is not busy converting. Single Conversion Mode must be selected and the ADC conversion complete interrupt must be enabled.

- ADEN = 1ADSC = 0

- ADFR = 0

- ADIE = 1

| I/O Ports | All AVR ports have true read-modify-write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintention-<br>ally changing the direction of any other pin with the SBI and CBI instructions. The same applies for changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port A    | Port A is an 8-bit bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                   |

|           | Three I/O memory address locations are allocated for Port A, one each for the Data Register – PORTA, \$1B(\$3B), Data Direction Register – DDRA, \$1A(\$3A) and the Port A Input Pins – PINA, \$19(\$39). The Port A Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.                                                                                 |

|           | All port pins have individually selectable pull-up resistors. The Port A output buffers can sink 20 mA and thus drive LED displays directly. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.                                                                                                                 |

|           | Port A has an alternate function as analog inputs for the ADC. If some Port A pins are configured as outputs, it is essential that these do not switch when a conversion is in progress. This might corrupt the result of the conversion.                                                                                                                                                                     |

|           | During Power-down mode, the Schmitt trigger of the digital input is disconnected. This allows analog signals that are close to $V_{\rm CC}/2$ to be present during power-down without causing excessive power consumption.                                                                                                                                                                                    |

|           |                                                                                                                                                                                                                                                                                                                                                                                                               |

### Port A Data Register – PORTA

|                                | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|--------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                | \$1B (\$3B)   | PORTA7 | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | PORTA |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port A Data Direction Register |               |        |        |        |        |        |        |        |        |       |

| – DDRA                         | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$1A (\$3A)   | DDA7   | DDA6   | DDA5   | DDA4   | DDA3   | DDA2   | DDA1   | DDA0   | DDRA  |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port A Input Pins Address –    |               |        |        |        |        |        |        |        |        |       |

| PINA                           | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$19 (\$39)   | PINA7  | PINA6  | PINA5  | PINA4  | PINA3  | PINA2  | PINA1  | PINA0  | PINA  |

|                                | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      |       |

|                                | Initial Value | N/A    |       |

The Port A Input Pins address (PINA) is not a register; this address enables access to the physical value on each Port A pin. When reading PORTA, the Port A Data Latch is read and when reading PINA, the logical values present on the pins are read.

Port D

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for Port D, one each for the Data Register – PORTD, \$12(\$32), Data Direction Register – DDRD, \$11(\$31) and the Port D Input Pins – PIND, \$10(\$30). The Port D Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. Some Port D pins have alternate functions as shown in Table 33.

| Port Pin | Alternate Function                                 |

|----------|----------------------------------------------------|

| PD0      | RXD (UART Input line)                              |

| PD1      | TXD (UART Output line)                             |

| PD2      | INT0 (External interrupt 0 input)                  |

| PD3      | INT1 (External interrupt 1 input)                  |

| PD4      | OC1B (Timer/Counter1 output compareB match output) |

| PD5      | OC1A (Timer/Counter1 output compareA match output) |

| PD6      | ICP (Timer/Counter1 input capture pin)             |

| PD7      | OC2 (Timer/Counter2 output compare match output)   |

Table 33. Port D Pin Alternate Functions

Figure 66. Port D Schematic Diagram (Pin PD7)

## Memory Programming

### **Program and Data** Memory Lock Bits

The AT90S8535 MCU provides two Lock bits that can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 35. The Lock bits can only be erased with the Chip Erase command.

#### Table 35. Lock Bit Protection Modes

|                                  | Memory Lock Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              | Bits     |                                                                                                                                                                             |  |  |  |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                  | Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LB1                                                                                                                                                          | LB2      | Protection Type                                                                                                                                                             |  |  |  |  |  |  |

|                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                            | 1        | No memory lock features enabled.                                                                                                                                            |  |  |  |  |  |  |

|                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                            | 1        | Further programming of the Flash and EEPROM is disabled. <sup>(1)</sup>                                                                                                     |  |  |  |  |  |  |

|                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                            | 0        | Same as mode 2 and verify is also disabled.                                                                                                                                 |  |  |  |  |  |  |

|                                  | Note:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                              |          | ode, further programming of the Fuse bits is also disabled. Program the fore programming the Lock bits.                                                                     |  |  |  |  |  |  |

| Fuse Bits                        | The AT9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0S8535                                                                                                                                                       | 5 has tv | vo Fuse bits, SPIEN and FSTRT.                                                                                                                                              |  |  |  |  |  |  |

|                                  | is er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nabled.                                                                                                                                                      | Default  | use is programmed ("0"), Serial Program and Data Downloading value is programmed ("0"). The SPIEN Fuse is not accessible in g Mode.                                         |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |          | Fuse is programmed ("0"), the short start-up time is selected. programmed ("1").                                                                                            |  |  |  |  |  |  |

|                                  | The stat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | us of th                                                                                                                                                     | e Fuse   | bits is not affected by Chip Erase.                                                                                                                                         |  |  |  |  |  |  |

| Signature Bytes                  | All Atmel microcontrollers have a three-byte signature code that identifies the device.<br>This code can be read in both Serial and Parallel modes. The three bytes reside in a<br>separate address space.                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |          |                                                                                                                                                                             |  |  |  |  |  |  |

|                                  | 1. \$000: \$1E (indicates manufactured by Atmel)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |          |                                                                                                                                                                             |  |  |  |  |  |  |

|                                  | 2. \$00-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1: \$93 (i                                                                                                                                                   | indicate | es 8K bytes Flash memory)                                                                                                                                                   |  |  |  |  |  |  |

|                                  | 3. \$002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2: <b>\$</b> 03 (i                                                                                                                                           | indicate | es AT90S8535 device when signature byte \$001 is \$93)                                                                                                                      |  |  |  |  |  |  |

|                                  | Note:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | te: 1. When both Lock bits are programmed (lock mode 3), the signature bytes read in Serial Mode. Reading the signature bytes will return: \$00, \$01 and \$ |          |                                                                                                                                                                             |  |  |  |  |  |  |

| Programming the Flash and EEPROM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |          | fers 8K bytes of in-system reprogrammable Flash program mem-<br>EPROM data memory.                                                                                          |  |  |  |  |  |  |

|                                  | The AT90S8535 is shipped with the On-chip Flash program and EEPROM data memory arrays in the erased state (i.e., contents = \$FF) and ready to be programmed. This device supports a high-voltage (12V) Parallel Programming Mode and a low-voltage Serial Programming Mode. The +12V is used for programming enable only and no current of significance is drawn by this pin. The Serial Programming Mode provides a convenient way to download program and data into the AT90S8535 inside the user's system. |                                                                                                                                                              |          |                                                                                                                                                                             |  |  |  |  |  |  |

|                                  | in either                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | progra                                                                                                                                                       | mming    | a memory arrays on the AT90S8535 are programmed byte-by-byte<br>g mode. For the EEPROM, an auto-erase cycle is provided within<br>struction in the Serial Programming Mode. |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |          |                                                                                                                                                                             |  |  |  |  |  |  |

During programming, the supply voltage must be in accordance with Table 36.

Table 37. Pin Name Mapping

| Signal Name in<br>Programming Mode | Pin Name | I/O | Function                                                            |

|------------------------------------|----------|-----|---------------------------------------------------------------------|

| RDY/BSY                            | PD1      | 0   | 0: Device is busy programming, 1: Device is ready for new command   |

| ŌĒ                                 | PD2      | I   | Output Enable (Active low)                                          |

| WR                                 | PD3      | I   | Write Pulse (Active low)                                            |

| BS                                 | PD4      | I   | Byte Select ("0" selects low byte, "1" selects high byte)           |

| XA0                                | PD5      | Ι   | XTAL Action Bit 0                                                   |

| XA1                                | PD6      | Ι   | XTAL Action Bit 1                                                   |

| DATA                               | PB7 - 0  | I/O | Bi-directional Data Bus (Output when $\overline{\text{OE}}$ is low) |

Table 38. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                              |

|-----|-----|--------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (high or low address byte determined by BS) |

| 0   | 1   | Load Data (High or low data byte for Flash determined by BS)             |

| 1   | 0   | Load Command                                                             |

| 1   | 1   | No Action, Idle                                                          |

### Table 39. Command Byte Bit Coding

| Command Byte | Command Executed        |

|--------------|-------------------------|

| 1000 0000    | Chip Erase              |

| 0100 0000    | Write Fuse Bits         |

| 0010 0000    | Write Lock Bits         |

| 0001 0000    | Write Flash             |

| 0001 0001    | Write EEPROM            |

| 0000 1000    | Read Signature Bytes    |

| 0000 0100    | Read Lock and Fuse Bits |

| 0000 0010    | Read Flash              |

| 0000 0011    | Read EEPROM             |

### Enter Programming Mode

The following algorithm puts the device in Parallel Programming Mode:

- 1. Apply supply voltage according to Table 36, between  $V_{\text{CC}}$  and GND.

- 2. Set the  $\overline{\text{RESET}}$  and BS pin to "0" and wait at least 100 ns.

- 3. Apply 11.5 12.5V to RESET. Any activity on BS within 100 ns after +12V has been applied to RESET, will cause the device to fail entering programming mode.

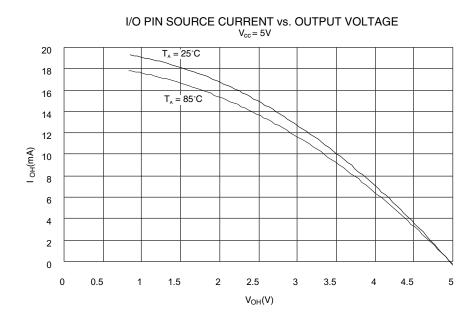

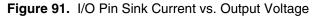

Figure 90. I/O Pin Source Current vs. Output Voltage

- Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.