Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C                                                              |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8535-8pc |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | The AVR core combines a rich instruction set with 32 general-purpose working regis-<br>ters. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU),<br>allowing two independent registers to be accessed in one single instruction executed in<br>one clock cycle. The resulting architecture is more code efficient while achieving<br>throughputs up to ten times faster than conventional CISC microcontrollers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | The AT90S8535 provides the following features: 8K bytes of In-System Programmable<br>Flash, 512 bytes EEPROM, 512 bytes SRAM, 32 general-purpose I/O lines, 32 general-<br>purpose working registers, Real-time Clock (RTC), three flexible timer/counters with<br>compare modes, internal and external interrupts, a programmable serial UART, 8-chan-<br>nel, 10-bit ADC, programmable Watchdog Timer with internal oscillator, an SPI serial<br>port and three software-selectable power-saving modes. The Idle Mode stops the CPU<br>while allowing the SRAM, timer/counters, SPI port and interrupt system to continue<br>functioning. The Power-down mode saves the register contents but freezes the oscilla-<br>tor, disabling all other chip functions until the next interrupt or hardware reset. In Power<br>Save Mode, the timer oscillator continues to run, allowing the user to maintain a timer<br>base while the rest of the device is sleeping. |

|                  | The device is manufactured using Atmel's high-density nonvolatile memory technology.<br>The On-chip ISP Flash allows the program memory to be reprogrammed in-system<br>through an SPI serial interface or by a conventional nonvolatile memory programmer.<br>By combining an 8-bit RISC CPU with In-System Programmable Flash on a monolithic<br>chip, the Atmel AT90S8535 is a powerful microcontroller that provides a highly flexible<br>and cost effective solution to many embedded control applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  | The AT90S8535 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators and evaluation kits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin Descriptions |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VCC              | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND              | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Port A (PA7PA0)  | Port A is an 8-bit bi-directional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers can sink 20 mA and can drive LED displays directly. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  | Port A also serves as the analog inputs to the A/D Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

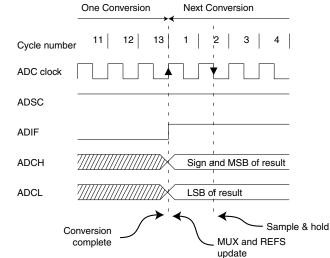

| Port B (PB7PB0)  | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. Port B also serves the functions of various special features of the AT90S8535 as listed on page 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  | The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Port C (PC7PC0)  | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors. The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally pulled low will source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

X-register low byte X-register high byte Y-register low byte Y-register high byte Z-register low byte Z-register high byte

memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

#### General-purpose Register File

Figure 6 shows the structure of the 32 general-purpose working registers in the CPU.

Figure 6. AVR CPU General-purpose Working Registers

General Purpose Working Registers

| 7   | 0 | Addr. |

|-----|---|-------|

| R0  |   | \$00  |

| R1  |   | \$01  |

| R2  |   | \$02  |

|     |   |       |

| R13 |   | \$0D  |

| R14 |   | \$0E  |

| R15 |   | \$0F  |

| R16 |   | \$10  |

| R17 |   | \$11  |

|     |   |       |

| R26 |   | \$1A  |

| R27 |   | \$1B  |

| R28 |   | \$1C  |

| R29 |   | \$1D  |

| R30 |   | \$1E  |

| R31 |   | \$1F  |

|     |   | -     |

All the register operating instructions in the instruction set have direct and single-cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI and ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file (R16..R31). The general SBC, SUB, CP, AND, and OR and all other operations between two registers or on a single register apply to the entire register file.

As shown in Figure 6, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y-, and Z-registers can be set to index any register in the file.

## AT90S/LS8535

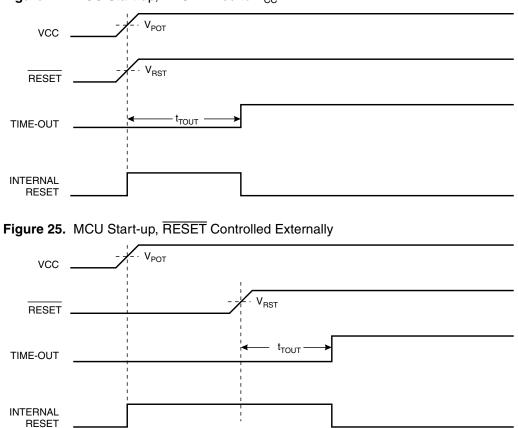

#### Figure 24. MCU Start-up, RESET Tied to V<sub>CC</sub>.

#### **External Reset**

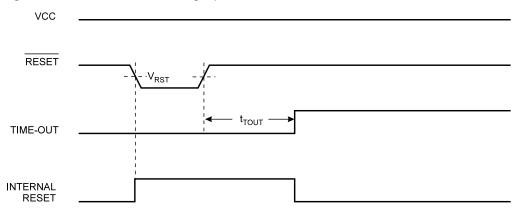

An external reset is generated by a low level on the  $\overrightarrow{\text{RESET}}$  pin. Reset pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage (V<sub>RST</sub>) on its positive edge, the delay timer starts the MCU after the Time-out period t<sub>TOUT</sub> has expired.

#### • Bit 5 – ICF1: Input Capture Flag 1

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the Input Capture Register (ICR1). ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logical "1" to the flag. When the SREG I-bit and TICIE1 (Timer/Counter1 Input Capture Interrupt Enable) and ICF1 are set (one), the Timer/Counter1 Capture Interrupt is executed.

#### • Bit 4 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1A (Output Compare Register 1A). OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logical "1" to the flag. When the I-bit in SREG and OCIE1A (Timer/Counter1 Compare Match InterruptA Enable) and the OCF1A are set (one), the Timer/Counter1 Compare A Match Interrupt is executed.

#### • Bit 3 – OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1B (Output Compare Register 1B). OCF1B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logical "1" to the flag. When the I-bit in SREG and OCIE1B (Timer/Counter1 Compare Match InterruptB Enable) and the OCF1B are set (one), the Timer/Counter1 Compare Match B Interrupt is executed.

#### • Bit 2 – TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV1 is cleared by writing a logical "1" to the flag. When the I-bit in SREG and TOIE1 (Timer/Counter1 Overflow Interrupt Enable) and TOV1 are set (one), the Timer/Counter1 Overflow Interrupt is executed. In up/down PWM mode, this bit is set when Timer/Counter1 advances from \$0000.

#### • Bit 1 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8535 and always reads zero.

#### • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logical "1" to the flag. When the SREG I-bit and TOIE0 (Timer/Counter0 Overflow Interrupt Enable) and TOV0 are set (one), the Timer/Counter0 Overflow Interrupt is executed. In up/down PWM mode, this bit is set when Timer/Counter1 advances from \$0000.

#### **External Interrupts**

The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register (MCUCR). When the external interrupt is enabled and is configured as level-triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register (MCUCR).

the counter on compareA match and actions on the Output Compare pins on both compare matches.

Timer/Counter1 can also be used as an 8-, 9- or 10-bit Pulse Width Modulator. In this mode the counter and the OCR1A/OCR1B registers serve as a dual glitch-free standalone PWM with centered pulses. Refer to page 40 for a detailed description of this function.

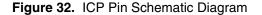

The Input Capture function of Timer/Counter1 provides a capture of the Timer/Counter1 contents to the Input Capture Register (ICR1), triggered by an external event on the Input Capture Pin (ICP). The actual capture event settings are defined by the Timer/Counter1 Control Register (TCCR1B). In addition, the Analog Comparator can be set to trigger the input capture. Refer to "Analog Comparator" on page 66 for details on this. The ICP pin logic is shown in Figure 32.

ACIC: COMPARATOR IC ENABLE ACO: COMPARATOR OUTPUT

If the Noise Canceler function is enabled, the actual trigger condition for the capture event is monitored over four samples and all four must be equal to activate the capture flag. The input pin signal is sampled at XTAL clock frequency.

#### Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     | _      |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

| \$2F (\$4F)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

#### • Bits 7, 6 - COM1A1, COM1A0: Compare Output Mode1A, Bits 1 and 0

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1A (Output CompareA pin 1). This is an alternative function to an I/O port and the corresponding direction control bit must be set (one) to control an output pin. The control configuration is shown in Table 11.

#### • Bits 5, 4 – COM1B1, COM1B0: Compare Output Mode1B, Bits 1 and 0

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1B (Output CompareB). This is an alternative function to an I/O port and the corresponding direction control bit must be set (one) to control an output pin. The control configuration is given in Table 11.

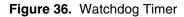

### Watchdog Timer

The Watchdog Timer is clocked from a separate On-chip oscillator. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted as shown in Table 21. See characterization data for typical values at other  $V_{CC}$  levels. The WDR (Watchdog Reset) instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S8535 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 22.

To prevent unintentional disabling of the Watchdog, a special turn-off sequence must be followed when the Watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

#### Watchdog Timer Control Register – WDTCR

| Bit           | 7 | 6 | 5 | 4     | 3   | 2    | 1    | 0    | _     |

|---------------|---|---|---|-------|-----|------|------|------|-------|

| \$21 (\$41)   | - | - | - | WDTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write    | R | R | R | R/W   | R/W | R/W  | R/W  | R/W  |       |

| Initial Value | 0 | 0 | 0 | 0     | 0   | 0    | 0    | 0    |       |

#### • Bits 7..5 - Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

#### • Bit 4 – WDTOE: Watchdog Turn-off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the Watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a Watchdog disable procedure.

#### • Bit 3 – WDE: Watchdog Enable

When the WDE is set (one) the Watchdog Timer is enabled and if the WDE is cleared (zero) the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE bit is set (one). To disable an enabled Watchdog Timer, the following procedure must be followed:

#### Prevent EEPROM Corruption

During periods of low V<sub>CC</sub>, the EEPROM data can be corrupted because the supply voltage is too low for the CPU and the EEPROM to operate properly. These issues are the same as for board level systems using the EEPROM and the same design solutions should be applied.

An EEPROM data corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage for executing instructions is too low.

EEPROM data corruption can easily be avoided by following these design recommendations (one is sufficient):

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This is best done by an external low V<sub>CC</sub> Reset Protection circuit, often referred to as a Brown-out Detector (BOD). Please refer to application note AVR 180 for design considerations regarding power-on reset and low-voltage detection.

- Keep the AVR core in Power-down Sleep Mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the EEPROM registers from unintentional writes.

- 3. Store constants in Flash memory if the ability to change memory contents from software is not required. Flash memory cannot be updated by the CPU and will not be subject to corruption.

The FE bit is cleared when the stop bit of received data is one.

#### • Bit 3 – OR: OverRun

This bit is set if an Overrun condition is detected, i.e., when a character already present in the UDR register is not read before the next character has been shifted into the Receiver Shift register. The OR bit is buffered, which means that it will be set once the valid data still in UDR is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

#### • Bits 2..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

#### **UART Control Register – UCR**

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    | _   |

|---------------|-------|-------|-------|------|------|------|------|------|-----|

| \$0A (\$2A)   | RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 | UCR |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R    | W    | -   |

| Initial Value | 0     | 0     | 0     | 0    | 0    | 0    | 1    | 0    |     |

#### Bit 7 – RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in USR will cause the Receive Complete Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 6 – TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in USR will cause the Transmit Complete Interrupt routine to be executed provided that global interrupts are enabled.

#### Bit 5 – UDRIE: UART Data Register Empty Interrupt Enable

When this bit is set (one), a setting of the UDRE bit in USR will cause the UART Data Register Empty Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 4 – RXEN: Receiver Enable

This bit enables the UART receiver when set (one). When the receiver is disabled, the RXC, OR and FE status flags cannot become set. If these flags are set, turning off RXEN does not cause them to be cleared.

#### • Bit 3 – TXEN: Transmitter Enable

This bit enables the UART transmitter when set (one). When disabling the transmitter while transmitting a character, the transmitter is not disabled before the character in the shift register plus any following character in UDR has been completely transmitted.

#### • Bit 2 – CHR9: 9 Bit Characters

When this bit is set (one), transmitted and received characters are 9 bits long, plus start and stop bits. The ninth bit is read and written by using the RXB8 and TXB8 bits in UCR, respectively. The ninth data bit can be used as an extra stop bit or a parity bit.

#### Bit 1 – RXB8: Receive Data Bit 8

When CHR9 is set (one), RXB8 is the ninth data bit of the received character.

#### • Bit 0 – TXB8: Transmit Data Bit 8

When CHR9 is set (one), TXB8 is the ninth data bit in the character to be transmitted.

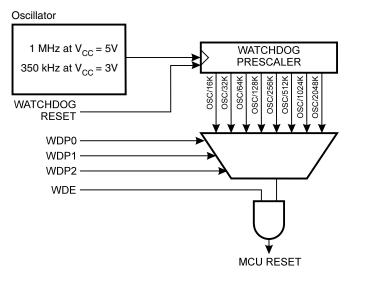

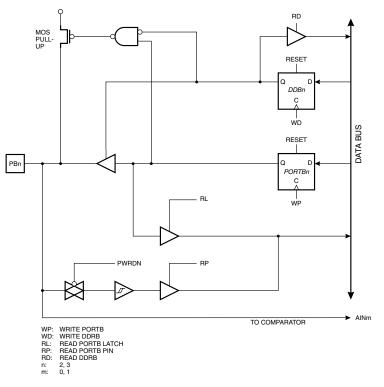

### **Analog Comparator**

The Analog Comparator compares the input values on the positive input PB2 (AIN0) and negative input PB3 (AIN1). When the voltage on the positive input PB2 (AIN0) is higher than the voltage on the negative input PB3 (AIN1), the Analog Comparator Output (ACO) is set (one). The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 44.

#### • Bit 7 – ACD: Analog Comparator Disable

When this bit is set (one), the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. When changing the ACD bit, the Analog Comparator interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

#### • Bit 6 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8535 and will always read as zero.

#### • Bit 5 – ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

#### • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logical "1" to the flag.

#### • Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is set (one) and the I-bit in the Status Register is set (one), the Analog Comparator interrupt is activated. When cleared (zero), the interrupt is disabled.

#### • Bit 2 – ACIC: Analog Comparator Input Capture Enable

When set (one), this bit enables the Input Capture function in Timer/Counter1 to be triggered by the Analog Comparator. The comparator output is in this case directly connected to the Input Capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When cleared (zero), no connection between the Analog Comparator and the Input Capture function is given. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the TICIE1 bit in the Timer Interrupt Mask Register (TIMSK) must be set (one).

#### • Bits 1,0 – ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events trigger the Analog Comparator interrupt. The different settings are shown in Table 25.

| ACIS1 | ACIS0 | Interrupt Mode                              |

|-------|-------|---------------------------------------------|

| 0     | 0     | Comparator Interrupt on Output Toggle       |

| 0     | 1     | Reserved                                    |

| 1     | 0     | Comparator Interrupt on Falling Output Edge |

| 1     | 1     | Comparator Interrupt on Rising Output Edge  |

Table 25.

ACIS1/ACIS0 Settings

Note: When changing the ACIS1/ACIS0 bits, the Analog Comparator interrupt must be disabled by clearing its interrupt enable bit in the ACSR register. Otherwise an interrupt can occur when the bits are changed.

**Caution**: Using the SBI or CBI instruction on bits other than ACI in this register will write a "1" back into ACI if it is read as set, thus clearing the flag.

### Analog-to-Digital Converter

Feature list

- 10-bit Resolution

- 0.5 LSB Integral Non-linearity

- ±2 LSB Absolute Accuracy

- 65 260 µs Conversion Time

- Up to 15 kSPS at Maximum Resolution

- 8 Multiplexed Input Channels

- Rail-to-Rail Input Range

- Free Running or Single Conversion Mode

- Interrupt on ADC Conversion Complete

- Sleep Mode Noise Canceler

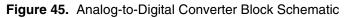

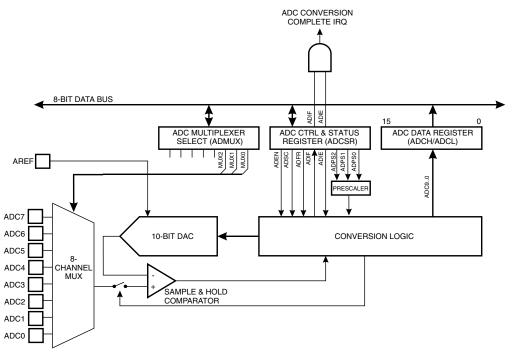

The AT90S8535 features a 10-bit successive approximation ADC. The ADC is connected to an 8-channel Analog Multiplexer that allows each pin of Port A to be used as an input for the ADC. The ADC contains a Sample and Hold Amplifier that ensures that the input voltage to the ADC is held at a constant level during conversion. A block diagram of the ADC is shown in Figure 45.

The ADC has two separate analog supply voltage pins, AVCC and AGND. AGND must be connected to GND and the voltage on  $AV_{CC}$  must not differ more than ±0.3V from  $V_{CC}$ . See "ADC Noise Canceling Techniques" on page 74 on how to connect these pins.

An external reference voltage must be applied to the AREF pin. This voltage must be in the range 2V - AV $_{\rm CC}$ .

# AT90S/LS8535

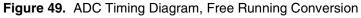

#### Table 26. ADC Conversion Time

| Condition           | Sample and Hold (Cycles from Start of Conversion) | Conversion<br>Time (Cycles) | Conversion<br>Time (µs) |

|---------------------|---------------------------------------------------|-----------------------------|-------------------------|

| Extended Conversion | 14                                                | 25                          | 125 - 500               |

| Normal Conversion   | 14                                                | 26                          | 130 - 520               |

# ADC Noise Canceler Function

The ADC features a noise canceler that enables conversion during Idle Mode to reduce noise induced from the CPU core. To make use of this feature, the following procedure should be used:

- 1. Make sure that the ADC is enabled and is not busy converting. Single Conversion Mode must be selected and the ADC conversion complete interrupt must be enabled.

- ADEN = 1ADSC = 0

- ADFR = 0

- ADIE = 1

- 2. Enter Idle Mode. The ADC will start a conversion once the CPU has been halted.

- 3. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the MCU and execute the ADC Conversion Complete Interrupt routine.

#### ADC Multiplexer Select Register – ADMUX

| Bit           | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    | _     |

|---------------|---|---|---|---|---|------|------|------|-------|

| \$07 (\$27)   | - | - | - | - | - | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write    | R | R | R | R | R | R/W  | R/W  | R/W  | •     |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

#### • Bits 7..3 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and always read as zero.

#### • Bits 2..0 – MUX2..MUX0: Analog Channel Select Bits 2-0

The value of these three bits selects which analog input ADC7..0 is connected to the ADC. See Table 27 for details.

If these bits are changed during a conversion, the change will not go into effect until this conversion is complete (ADIF in ADCSR is set).

| Table 27 | . Inp  | out Ch | nannel | Selections  |

|----------|--------|--------|--------|-------------|

|          | • •••• |        |        | 00100110110 |

| MUX2.0 | Single-ended Input |

|--------|--------------------|

| 000    | ADC0               |

| 001    | ADC1               |

| 010    | ADC2               |

| 011    | ADC3               |

| 100    | ADC4               |

| 101    | ADC5               |

| 110    | ADC6               |

| 111    | ADC7               |

#### ADC Control and Status Register – ADCSR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2     | 1     | 0     |       |

|---------------|------|------|------|------|------|-------|-------|-------|-------|

| \$06 (\$26)   | ADEN | ADSC | ADFR | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSR |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   |       |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     |       |

#### • Bit 7 – ADEN: ADC Enable

Writing a logical "1" to this bit enables the ADC. By clearing this bit to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress will terminate this conversion.

#### • Bit 6 – ADSC: ADC Start Conversion

In Single Conversion Mode, a logical "1" must be written to this bit to start each conversion. In Free Running Mode, a logical "1" must be written to this bit to start the first conversion. The first time ADSC has been written after the ADC has been enabled or if ADSC is written at the same time as the ADC is enabled, an extended conversion will precede the initiated conversion. This extended conversion performs initialization of the ADC.

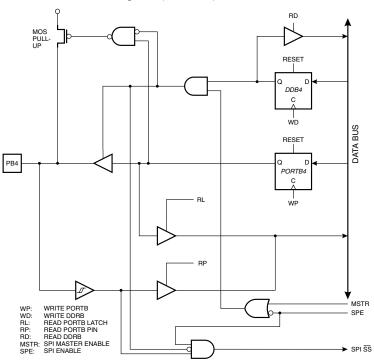

Figure 53. Port B Schematic Diagram (Pins PB2 and PB3)

| Table 36. | Supply | Voltage | durina | Programming | 1 |

|-----------|--------|---------|--------|-------------|---|

| 14010 001 | Cappij | ·onago  | aannig |             | , |

| Part       | Serial Programming | Parallel Programming |

|------------|--------------------|----------------------|

| AT90S8535  | 4.0 - 6.0V         | 4.5 - 5.5V           |

| AT90LS8535 | 2.7 - 6.0V         | 4.5 - 5.5V           |

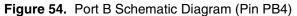

**Parallel Programming** This section describes how to parallel program and verify Flash program memory, EEPROM data memory, Lock bits and Fuse bits in the AT90S8535.

**Signal Names**

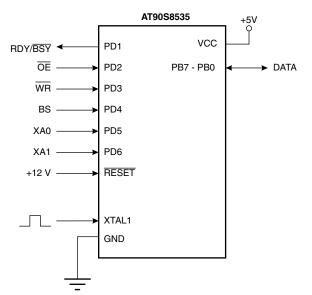

In this section, some pins of the AT90S8535 are referenced by signal names describing their function during parallel programming. See Figure 67 and Table 37. Pins not described in Table 37 are referenced by pin name.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding are shown in Table 38.

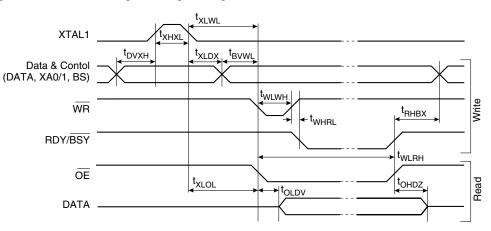

When pulsing  $\overline{WR}$  or  $\overline{OE}$ , the command loaded determines the action executed. The command is a byte where the different bits are assigned functions as shown in Table 39.

Figure 67. Parallel Programming

# AT90S/LS8535

#### Parallel Programming Characteristics

| Table 40. | Parallel | Programming | Characteristics, | T <sub>A</sub> = 25°C ± | 10%, $V_{CC} = 5V$ | ′ ± 10% |

|-----------|----------|-------------|------------------|-------------------------|--------------------|---------|

|-----------|----------|-------------|------------------|-------------------------|--------------------|---------|

| Symbol                | Parameter                                        | Min  | Тур  | Max   | Units |  |

|-----------------------|--------------------------------------------------|------|------|-------|-------|--|

| V <sub>PP</sub>       | Programming Enable Voltage                       | 11.5 |      | 12.5  | V     |  |

| I <sub>PP</sub>       | Programming Enable Current                       |      |      | 250.0 | μA    |  |

| t <sub>DVXH</sub>     | Data and Control Setup before XTAL1 High         | 67.0 |      |       | ns    |  |

| t <sub>xHxL</sub>     | XTAL1 Pulse Width High                           | 67.0 |      |       | ns    |  |

| t <sub>xLDX</sub>     | Data and Control Hold after XTAL1 Low            | 67.0 |      |       | ns    |  |

| t <sub>XLWL</sub>     | XTAL1 Low to WR Low                              | 67.0 |      |       | ns    |  |

| t <sub>BVWL</sub>     | BS Valid to WR Low                               | 67.0 |      |       | ns    |  |

| t <sub>RHBX</sub>     | BS Hold after RDY/BSY High                       | 67.0 |      |       | ns    |  |

| t <sub>wLWH</sub>     | WR Pulse Width Low <sup>(1)</sup>                | 67.0 |      |       | ns    |  |

| t <sub>WHRL</sub>     | WR High to RDY/BSY Low <sup>(2)</sup>            |      | 20.0 |       | ns    |  |

| t <sub>wLRH</sub>     | WR Low to RDY/BSY High <sup>(2)</sup>            | 0.5  | 0.7  | 0.9   | ms    |  |

| t <sub>XLOL</sub>     | XTAL1 Low to OE Low                              | 67.0 |      |       | ns    |  |

| t <sub>OLDV</sub>     | OE Low to DATA Valid                             |      | 20.0 |       | ns    |  |

| t <sub>OHDZ</sub>     | OE High to DATA Tri-stated                       |      |      | 20.0  | ns    |  |

| t <sub>WLWH_CE</sub>  | WR Pulse Width Low for Chip Erase                | 5.0  | 10.0 | 15.0  | ms    |  |

| t <sub>wlwh_PFB</sub> | WR Pulse Width Low for Programming the Fuse Bits | 1.0  | 1.5  | 1.8   | ms    |  |

Notes: 1. Use t<sub>WLWH CE</sub> for Chip Erase and t<sub>WLWH PEB</sub> for programming the Fuse bits.

2. If t<sub>WLWH</sub> is held longer than t<sub>WLBH</sub>, no RDY/BSY pulse will be seen.

#### **Serial Downloading**

Both the Flash and EEPROM memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output), see Figure 71. After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase operations can be executed.

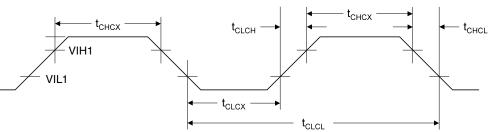

# External Clock Drive Waveforms

Figure 74. External Clock

#### Table 46. External Clock Drive

|                     |                      | V <sub>CC</sub> = 2.7V to 6.0V |     | V <sub>CC</sub> = 4.0V to 6.0V |     |       |

|---------------------|----------------------|--------------------------------|-----|--------------------------------|-----|-------|

| Symbol              | Parameter            | Min                            | Max | Min                            | Max | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                              | 4   | 0                              | 8.0 | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 250.0                          |     | 125.0                          |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 100.0                          |     | 50.0                           |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 100.0                          |     | 50.0                           |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                | 1.6 |                                | 0.5 | μs    |

| t <sub>CHCL</sub>   | Fall Time            |                                | 1.6 |                                | 0.5 | μs    |

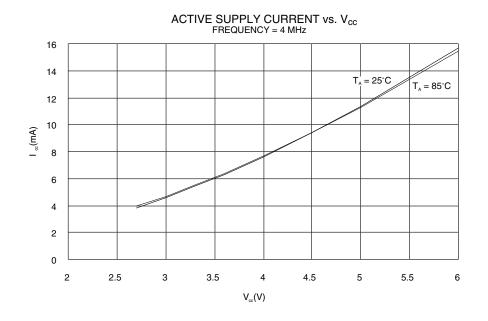

Figure 76. Active Supply Current vs. V<sub>CC</sub>

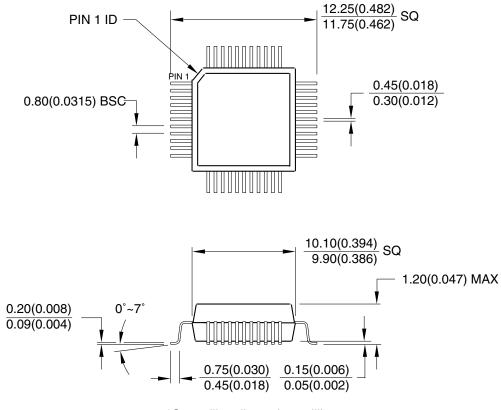

## **Packaging Information**

44A

44-lead, Thin (1.0mm) Plastic Quad Flat Package (TQFP), 10x10mm body, 2.0mm footprint, 0.8mm pitch. Dimension in Millimeters and (Inches)\* JEDEC STANDARD MS-026 ACB

\*Controlling dimension: millimetter

REV. A 04/11/2001

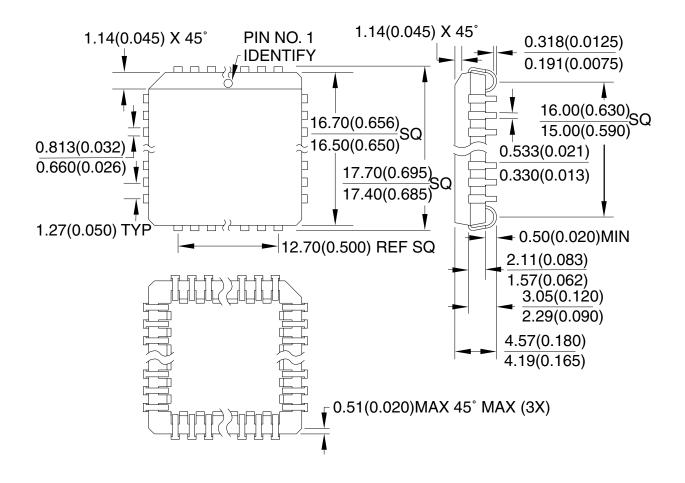

44J

44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC) Dimensions in Milimeters and (Inches)\* JEDEC STANDARD MS-018 AC

\*Controlling dimensions: Inches