Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | SCI                                                       |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 192 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 4x8b                                                  |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 16-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908kx2cdwe |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC908KX8 MC68HC908KX2 MC68HC08KX8

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.freescale.com

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

MC68HC908KX8 • MC68HC908KX2 • MC68HC08KX8 Data Sheet, Rev. 2.1

Freescale Semiconductor

**Random-Access Memory (RAM)**

# 2.4 Random-Access Memory (RAM)

Addresses \$0040–\$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

### NOTE

For correct operation, the stack pointer must point only to RAM locations.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

## NOTE

For M6805, M146805 and M68HC05compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

NOTE

Be careful when using nested subroutines. The CPU could overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

# 2.5 FLASH Memory (FLASH)

The FLASH memory is an array of 7,680 bytes with an additional 36 bytes of user vectors and one byte used for block protection.

### NOTE

An erased bit reads as 1 and a programmed bit reads as 0.

The program and erase operations are facilitated through control bits in the FLASH control register (FLCR). See 2.6 FLASH Control Register.

The FLASH is organized internally as an 8192-word by 8-bit complementary metal-oxide semiconductor (CMOS) page erase, byte (8-bit) program embedded FLASH memory. Each page consists of 64 bytes. The page erase operation erases all words within a page. A page is composed of two adjacent rows.

A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

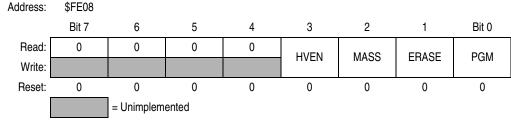

## 2.6 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

1. No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

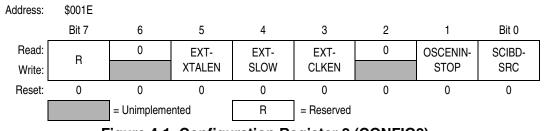

# Chapter 4 Configuration Register (CONFIG)

# 4.1 Introduction

This section describes the configuration registers, CONFIG1 and CONFIG2. The configuration registers control these options:

- Stop mode recovery time, 32 CGMXCLK cycles or 4096 CGMXCLK cycles

- Computer operating properly (COP) timeout period, 2<sup>18</sup>–2<sup>4</sup> or 2<sup>13</sup>–2<sup>4</sup> CGMXCLK cycles

- STOP instruction

- Computer operating properly (COP) module

- Low-voltage inhibit (LVI) module control and voltage trip point selection

- Enable/disable the oscillator (OSC) during stop mode

- Serial communications interface (SCI) clock source selection

- External clock/crystal source control

- Enable/disable for the FLASH charge-pump regulator

# 4.2 Functional Description

The configuration registers are used in the initialization of various options and can be written once after each reset. All of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU), it is recommended that these registers be written immediately after reset. The configuration registers are located at \$001E and \$001F. For compatibility, a write to a read-only memory (ROM) version of the MCU at this location will have no effect. The configuration register may be read at anytime.

#### NOTE

The CONFIG module is known as an MOR (mask option register) on a ROM device. On a ROM device, the options are fixed at the time of device fabrication and are neither writable nor changeable by the user.

On a FLASH device, the CONFIG registers are special registers containing one-time writable latches after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 4-1 and Figure 4-2.

**Central Processor Unit (CPU)**

| Source                                                                                        | Operation                                                         | Description                                                                                                                                                                                                                               | Effect<br>on CCF |   |   |   |   |   | Address<br>Mode                                     | Opcode                                           | Operand                                   | es                              |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|---|---|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|---------------------------------|

| Form                                                                                          | opolation                                                         | Becomption                                                                                                                                                                                                                                | v                | Η | I | Ν | z | С | Add<br>Mod                                          | Opc                                              | Ope                                       | Cycles                          |

| PULA                                                                                          | Pull A from Stack                                                 | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                                        | -                | - | - | - | - | - | INH                                                 | 86                                               |                                           | 2                               |

| PULH                                                                                          | Pull H from Stack                                                 | $SP \leftarrow (SP + 1); Pull (H)$                                                                                                                                                                                                        | -                | - | - | - | - | - | INH                                                 | 8A                                               |                                           | 2                               |

| PULX                                                                                          | Pull X from Stack                                                 | $SP \leftarrow (SP + 1); Pull (X)$                                                                                                                                                                                                        | -                | - | - | - | - | - | INH                                                 | 88                                               |                                           | 2                               |

| ROL <i>opr</i><br>ROLA<br>ROLX<br>ROL <i>opr</i> ,X<br>ROL ,X<br>ROL <i>opr</i> ,SP           | Rotate Left through Carry                                         | C←←<br>b7 b0                                                                                                                                                                                                                              | t                | _ | _ | ţ | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                            | 4<br>1<br>4<br>3<br>5           |

| ROR <i>opr</i><br>RORA<br>RORX<br>ROR <i>opr</i> ,X<br>ROR ,X<br>ROR <i>opr</i> ,SP           | Rotate Right through Carry                                        | b7 b0                                                                                                                                                                                                                                     | ţ                | _ | _ | ţ | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                            | 4<br>1<br>4<br>3<br>5           |

| RSP                                                                                           | Reset Stack Pointer                                               | $SP \leftarrow \$FF$                                                                                                                                                                                                                      | -                | - |   | - | Ι | - | INH                                                 | 9C                                               |                                           | 1                               |

| RTI                                                                                           | Return from Interrupt                                             | $\begin{array}{l} SP \leftarrow (SP) + 1;  Pull \; (CCR) \\ SP \leftarrow (SP) + 1;  Pull \; (A) \\ SP \leftarrow (SP) + 1;  Pull \; (X) \\ SP \leftarrow (SP) + 1;  Pull \; (PCH) \\ SP \leftarrow (SP) + 1;  Pull \; (PCL) \end{array}$ | t                | ţ | ţ | ţ | ţ | ţ | INH                                                 | 80                                               |                                           | 7                               |

| RTS                                                                                           | Return from Subroutine                                            | $\begin{array}{l} SP \leftarrow SP + 1; Pull \ (PCH) \\ SP \leftarrow SP + 1; Pull \ (PCL) \end{array}$                                                                                                                                   | _                | - | _ | - | _ | - | INH                                                 | 81                                               |                                           | 4                               |

| SBC #opr<br>SBC opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC,X<br>SBC opr,SP<br>SBC opr,SP | Subtract with Carry                                               | $A \gets (A) - (M) - (C)$                                                                                                                                                                                                                 | t                | - | _ | ţ | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 |                                           | 23443245                        |

| SEC                                                                                           | Set Carry Bit                                                     | C ← 1                                                                                                                                                                                                                                     | -                | - | - | - | - | 1 | INH                                                 | 99                                               |                                           | 1                               |

| SEI                                                                                           | Set Interrupt Mask                                                | l ← 1                                                                                                                                                                                                                                     | -                | - | 1 | - | - | - | INH                                                 | 9B                                               |                                           | 2                               |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X<br>STA opr,SP<br>STA opr,SP            | Store A in M                                                      | M ← (A)                                                                                                                                                                                                                                   | 0                | _ | _ | ţ | ţ | - | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | 87<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 3443245                         |

| STHX opr                                                                                      | Store H:X in M                                                    | $(M{:}M+1) \leftarrow (H{:}X)$                                                                                                                                                                                                            | 0                | - | - | 1 | 1 | - | DIR                                                 | 35                                               | dd                                        | 4                               |

| STOP                                                                                          | Enable Interrupts, Stop Processing,<br>Refer to MCU Documentation | $I \leftarrow 0$ ; Stop Processing                                                                                                                                                                                                        | -                | - | 0 | - | _ | - | INH                                                 | 8E                                               |                                           | 1                               |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX ,X<br>STX opr,SP<br>STX opr,SP            | Store X in M                                                      | $M \gets (X)$                                                                                                                                                                                                                             | 0                | _ | _ | ţ | ţ | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       |                                           | 3<br>4<br>4<br>3<br>2<br>4<br>5 |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB opr,SP<br>SUB opr,SP          | Subtract                                                          | $A \gets (A) - (M)$                                                                                                                                                                                                                       | t                | _ | _ | ţ | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 |                                           | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

## Table 6-1. Instruction Set Summary (Sheet 5 of 6)

#### Internal Clock Generator Module (ICG)

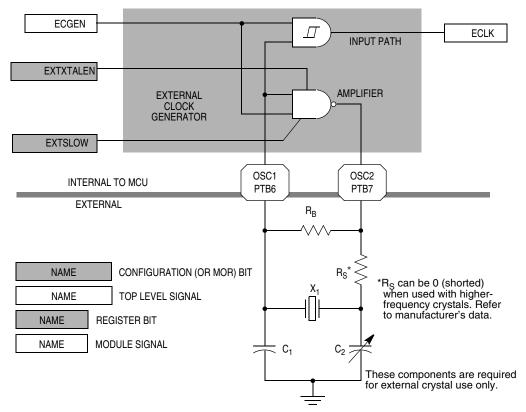

Figure 7-3. External Clock Generator Block Diagram

The amplifier is enabled when the external clock generator enable (ECGEN) signal is set and when the external crystal enable (EXTXTALEN) bit in the CONFIG (or MOR) register is set. ECGEN is controlled by the clock enable circuit (see 7.3.1 Clock Enable Circuit), and indicates that the external clock function is desired. When enabled, the amplifier will be connected between the PTB6/(OSC1) and PTB7/(OSC2)/RST pins. Otherwise, the PTB7/(OSC2)/RST pin reverts to its port function. In its typical configuration, the external oscillator requires five external components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the crystal manufacturer's data for more information.)

## 7.3.3.2 External Clock Input Path

The external clock input path is the means by which the microcontroller uses an external clock source. The input to the path is the PTB6/(OSC1) pin and the output is the external clock (ECLK). The path, which contains input buffering, is enabled when the external clock generator enable signal (ECGEN) is set. When not enabled, the PTB6/(OSC1) pin reverts to its port function.

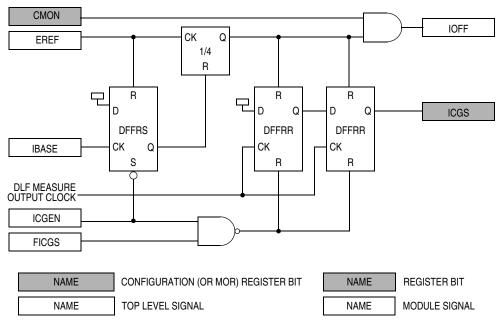

## 7.3.4.2 Internal Clock Activity Detector

The internal clock activity detector, shown in Figure 7-5, looks for at least one falling edge on the low-frequency base clock (IBASE) every time the external reference (EREF) is low. Since EREF is less than half the frequency of IBASE, this should occur every time. If it does not occur two consecutive times, the internal clock inactivity indicator (IOFF) is set. IOFF will be cleared the next time there is a falling edge of IBASE while EREF is low.

The internal clock stable bit (ICGS) is also generated in the internal clock activity detector. ICGS is set when the internal clock generator's filter stable signal (FICGS) indicates that IBASE is within about 15% of the target 307.2 kHz  $\pm$  25% for two consecutive measurements. ICGS is cleared when FICGS is clear, the internal clock generator is turned off or in STOP (ICGEN is clear), or when IOFF is set.

Figure 7-5. Internal Clock Activity Detector

## 7.3.4.3 External Clock Activity Detector

The external clock activity detector, shown in Figure 7-6, looks for at least one falling edge on the external clock (ECLK) every time the internal reference (IREF) is low. Since IREF is less than half the frequency of ECLK, this should occur every time. If it does not occur two consecutive times, the external clock inactivity indicator (EOFF) is set. EOFF will be cleared the next time there is a falling edge of ECLK while IREF is low.

The external clock stable bit (ECGS) is also generated in the external clock activity detector. ECGS is set on a falling edge of the external stabilization clock (ESTBCLK). This will be 4096 ECLK cycles after the external clock generator on bit is set or the MCU exits STOP (ECGEN = 1) if the external crystal enable (EXTXTALEN) in the CONFIG (or MOR) register is set, or 16 cycles when EXTXTALEN is clear. ECGS is cleared when the external clock generator is turned off or in STOP (ECGEN is clear) or when EOFF is set.

#### Internal Clock Generator Module (ICG)

### ICGON — Internal Clock Generator On Bit

This read/write bit enables the internal clock generator. ICGON can be cleared when the CS bit has been set and the CMON bit has been clear for at least one bus cycle. ICGON is forced set when the CMON bit is set, the CS bit is clear, or during reset.

- 1 = Internal clock generator enabled

- 0 = Internal clock generator disabled

### ICGS — Internal Clock Generator Stable Bit

This read-only bit indicates when the internal clock generator has determined that the internal clock (ICLK) is within about 15% of the desired value. This bit is forced clear when the clock monitor determines the ICLK is inactive, when ICGON is clear, when the ICG multiplier register (ICGMR) is written, when the ICG trim register (ICGTR) is written, during STOP with OSCENINSTOP low, or during reset.

- 1 = Internal clock is within 15% of the desired value

- 0 = Internal clock may not be within 15% of the desired value

## ECGON — External Clock Generator On Bit

This read/write bit enables the external clock generator. ECGON can be cleared when the CS and CMON bits have been clear for at least one bus cycle. ECGON is forced set when the CMON bit or the CS bit is set. ECGON is forced clear during reset.

- 1 = External clock generator enabled

- 0 = External clock generator disabled

### ECGS — External Clock Generator Stable Bit

This read-only bit indicates when at least 4096 external clock (ECLK) cycles have elapsed since the external clock generator was enabled. This is not an assurance of the stability of ECLK but is meant to provide a start-up delay. This bit is forced clear when the clock monitor determines ECLK is inactive, when ECGON is clear, during STOP with OSCENINSTOP low, or during reset.

- 1 = 4096 ECLK cycles have elapsed since ECGON was set

- 0 = External clock is unstable, inactive, or disabled

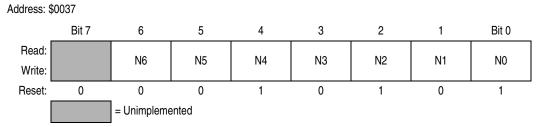

## 7.7.2 ICG Multiplier Register

Figure 7-12. ICG Multiplier Register (ICGMR)

#### N6:N0 — ICG Multiplier Factor Bits

These read/write bits change the multiplier used by the internal clock generator. The internal clock (ICLK) will be (307.2 kHz  $\pm$  25%) \* N. A value of \$00 in this register is interpreted the same as a value of \$01. This register cannot be written when the CMON bit is set. Reset sets this factor to \$15 (decimal 21) for default frequency of 6.45 MHz  $\pm$  25% (1.613 MHz  $\pm$  25% bus).

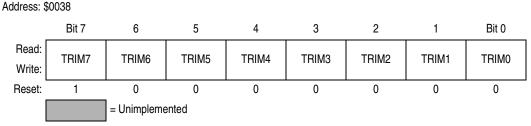

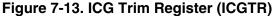

## 7.7.3 ICG Trim Register

## TRIM7:TRIM0 — ICG Trim Factor Bits

These read/write bits change the size of the internal capacitor used by the internal clock generator. By testing the frequency of the internal clock and incrementing or decrementing this factor accordingly, the accuracy of the internal clock can be improved to  $\pm 2\%$ . Incrementing this register by one decreases the frequency by 0.195% of the unadjusted value. Decrementing this register by one increases the frequency by 0.195%. This register cannot be written when the CMON bit is set. Reset sets these bits to \$80, centering the range of possible adjustment.

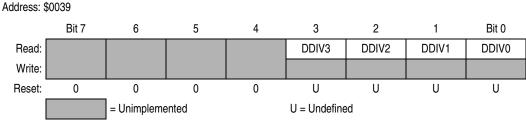

## 7.7.4 ICG DCO Divider Register

## DDIV3:DDIV0 — ICG DCO Divider Control Bits

These bits indicate the number of divide-by-twos (DDIV) that follow the digitally controlled oscillator. When ICGON is set, DDIV is controlled by the digital loop filter. The range of valid values for DDIV is from \$0 to \$9. Values of \$A-\$F are interpreted the same as \$9. Since the DCO is active during reset, reset has no effect on DSTG and the value may vary.

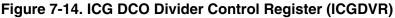

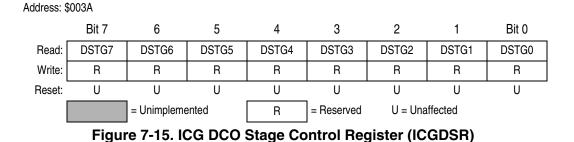

## 7.7.5 ICG DCO Stage Register

MC68HC908KX8 • MC68HC908KX2 • MC68HC08KX8 Data Sheet, Rev. 2.1

#### External Interrupt (IRQ)

The vector fetch or software clear and the return of the  $\overline{IRQ1}$  pin to logic 1 can occur in any order. The interrupt request remains pending as long as the  $\overline{IRQ1}$  pin is at logic 0. A reset will clear the latch and the MODE1 control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE1 bit is clear, the IRQ1 pin is falling-edge sensitive only. With MODE1 clear, a vector fetch or software clear immediately clears the IRQ1 latch.

The IRQF1 bit in the ISCR can be used to check for pending interrupts. The IRQF1 bit is not affected by the IMASK1 bit, which makes it useful in applications where polling is preferred.

Use the branch if interrupt pin is high (BIH) or branch if interrupt pin is low (BIL) instruction to read the logic level on the IRQ1 pin.

### NOTE

When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

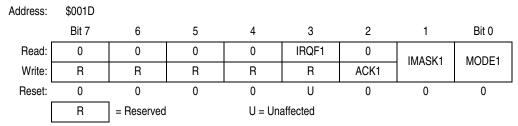

## 8.5 IRQ Status and Control Register

The IRQ status and control register (ISCR) controls and monitors operation of the IRQ module. The ISCR has these functions:

- Shows the state of the IRQ1 interrupt flag

- Clears the IRQ1 interrupt latch

- Masks IRQ1 interrupt request

- Controls triggering sensitivity of the IRQ1 interrupt pin

## Figure 8-3. IRQ Status and Control Register (ISCR)

## IRQF1 — IRQ1 Flag Bit

This read-only status bit is high when the IRQ1 interrupt is pending.

1 = IRQ1 interrupt pending

0 = IRQ1 interrupt not pending

## ACK1 — IRQ1 Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ1 latch. ACK1 always reads as 0. Reset clears ACK1.

## IMASK1 — IRQ1 Interrupt Mask Bit

Writing a 1 to this read/write bit disables IRQ1 interrupt requests. Reset clears IMASK1.

- 1 = IRQ1 interrupt requests disabled

- 0 = IRQ1 interrupt requests enabled

## MODE1 — IRQ1 Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ1 pin. Reset clears MODE1.

- 1 = IRQ1 interrupt requests on falling edges and low levels

- 0 = IRQ1 interrupt requests on falling edges only

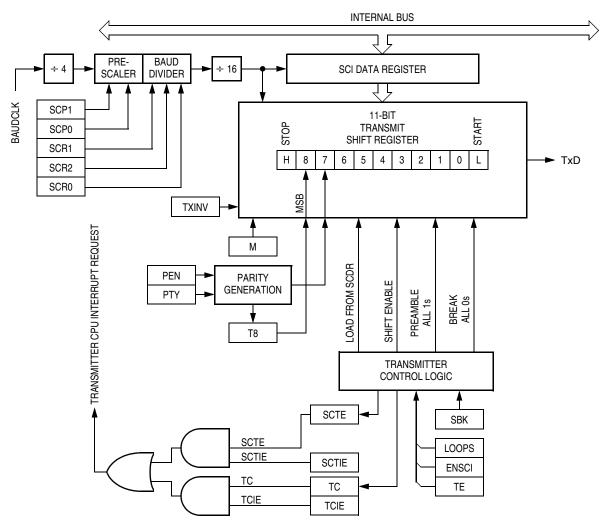

Serial Communications Interface Module (SCI)

Figure 12-5. SCI Transmitter Break Characters

At the start of a transmission, transmitter control logic automatically loads the transmit shift register with a preamble of logic 1s. After the preamble shifts out, control logic transfers the SCDR data into the transmit shift register. A logic 0 start bit automatically goes into the least significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit position.

The SCI transmitter empty bit, SCTE, in SCS1 becomes set when the SCDR transfers a byte to the transmit shift register. The SCTE bit indicates that the SCDR can accept new data from the internal data bus. If the SCI transmit interrupt enable bit, SCTIE, in SCC2 is also set, the SCTE bit generates a transmitter CPU interrupt request.

When the transmit shift register is not transmitting a character, the TxD pin goes to the idle condition, logic 1. If at any time software clears the ENSCI bit in SCI control register 1 (SCC1), the transmitter and receiver relinquish control of the port B pins.

Writing a 1 to the send break bit, SBK, in SCC2 loads the transmit shift register with a break character. A break character contains all logic 0s and has no start, stop, or parity bit. Break character length depends on the M bit in SCC1. As long as SBK is at 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last

#### Serial Communications Interface Module (SCI)

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7.

Table 12-2 summarizes the results of the start bit verification samples.

| RT3, RT5,<br>and RT7 Samples | Start Bit<br>Verification | Noise Flag |

|------------------------------|---------------------------|------------|

| 000                          | Yes                       | 0          |

| 001                          | Yes                       | 1          |

| 010                          | Yes                       | 1          |

| 011                          | No                        | 0          |

| 100                          | Yes                       | 1          |

| 101                          | No                        | 0          |

| 110                          | No                        | 0          |

| 111                          | No                        | 0          |

| Table 12 | 2-2. Starl | t Bit Ver | rification |

|----------|------------|-----------|------------|

|          |            |           | mouton     |

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 12-3 summarizes the results of the data bit samples.

| RT8, RT9,<br>and RT10 Samples | Data Bit<br>Determination | Noise Flag |

|-------------------------------|---------------------------|------------|

| 000                           | 0                         | 0          |

| 001                           | 0                         | 1          |

| 010                           | 0                         | 1          |

| 011                           | 1                         | 1          |

| 100                           | 0                         | 1          |

| 101                           | 1                         | 1          |

| 110                           | 1                         | 1          |

| 111                           | 1                         | 0          |

## Table 12-3. Data Bit Recovery

#### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is

$$\frac{170 - 176}{170} \times 100 = 3.53\%.$$

## 12.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

Depending on the state of the WAKE bit in SCC1, either of two conditions on the RxD pin can bring the receiver out of the standby state:

- 1. Address mark An address mark is a 1 in the most significant bit position of a received character. When the WAKE bit is set, an address mark wakes the receiver from the standby state by clearing the RWU bit. The address mark also sets the SCI receiver full bit, SCRF. Software can then compare the character containing the address mark to the user-defined address of the receiver. If they are the same, the receiver remains awake and processes the characters that follow. If they are not the same, software can set the RWU bit and put the receiver back into the standby state.

- 2. Idle input line condition When the WAKE bit is clear, an idle character on the RxD pin wakes the receiver from the standby state by clearing the RWU bit. The idle character that wakes the receiver does not set the receiver idle bit, IDLE, or the SCI receiver full bit, SCRF. The idle line type bit, ILTY, determines whether the receiver begins counting 1s as idle character bits after the start bit or after the stop bit.

### NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle may cause the receiver to wake up immediately.

#### 12.4.3.7 Receiver Interrupts

These sources can generate CPU interrupt requests from the SCI receiver:

- SCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has transferred a character to the SCDR. SCRF can generate a receiver CPU interrupt request. Setting the SCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver CPU interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate CPU interrupt requests.

## 12.4.3.8 Error Interrupts

These receiver error flags in SCS1 can generate CPU interrupt requests:

Receiver overrun (OR) — The OR bit indicates that the receive shift register shifted in a new character before the previous character was read from the SCDR. The previous character remains in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3 enables OR to generate SCI error CPU interrupt requests.

#### Serial Communications Interface Module (SCI)

## SCRIE — SCI Receive Interrupt Enable Bit

This read/write bit enables the SCRF bit to generate SCI receiver CPU interrupt requests. Setting the SCRIE bit in SCC3 enables the SCRF bit to generate CPU interrupt requests. Reset clears the SCRIE bit.

1 = SCRF enabled to generate CPU interrupt

0 = SCRF not enabled to generate CPU interrupt

## ILIE — Idle Line Interrupt Enable Bit

This read/write bit enables the IDLE bit to generate SCI receiver CPU interrupt requests. Reset clears the ILIE bit.

1 = IDLE enabled to generate CPU interrupt requests

0 = IDLE not enabled to generate CPU interrupt requests

### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (logic 1). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

1 = Transmitter enabled

0 = Transmitter disabled

## NOTE

Writing to the TE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

### **RE** — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

1 = Receiver enabled

0 = Receiver disabled

#### NOTE

Writing to the RE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

#### RWU — Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

1 = Standby state

0 = Normal operation

## SBK — Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a 1. The 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no 1s between them. Reset clears the SBK bit.

1 = Transmit break characters

0 = No break characters being transmitted

#### NOTE

Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the SCI to send a break character instead of a preamble.

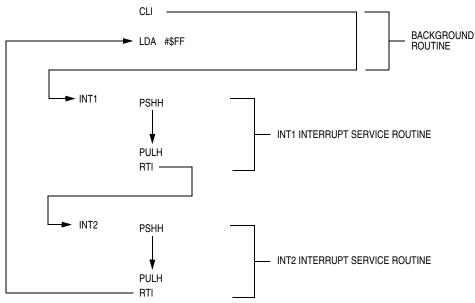

Serial Communications Interface Module (SCI)

is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the load-accumulator- from-memory (LDA) instruction is executed.

The LDA opcode is prefetched by both the INT1 and INT2 RTI instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

**NOTE** To maintain compatibility with the M68HC05, M6805, and M146805 Families the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

Figure 13-10. Interrupt Recognition Example

## 13.5.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

#### NOTE

A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC - 1, as a hardware interrupt does.

## 13.5.2 Reset

All reset sources always have higher priority than interrupts and cannot be arbitrated.

## 13.6 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur. Low-power modes are exited via an interrupt or reset.

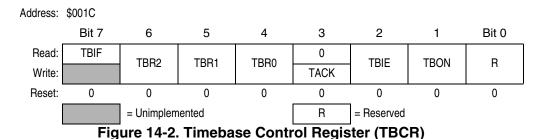

Timebase Module (TBM)

# 14.7 Timebase Control Register

The timebase has one register, the timebase control register (TBCR), which is used to enable the timebase interrupts and set the rate.

### TBIF — Timebase Interrupt Flag

This read-only flag bit is set when the timebase counter has rolled over.

- 1 = Timebase interrupt pending

- 0 = Timebase interrupt not pending

## TBR2–TBR0 — Timebase Divider Selection Bits

These read/write bits select the tap in the counter to be used for timebase interrupts as shown in Table 14-1.

### NOTE

Do not change TBR2–TBR0 bits while the timebase is enabled (TBON = 1).

### TACK— Timebase ACKnowledge Bit

The TACK bit is a write-only bit and always reads as 0. Writing a 1 to this bit clears TBIF, the timebase interrupt flag bit. Writing a 0 to this bit has no effect.

1 = Clear timebase interrupt flag

0 = No effect

## **TBIE** — Timebase Interrupt Enabled Bit

This read/write bit enables the timebase interrupt when the TBIF bit becomes set. Reset clears the TBIE bit.

1 = Timebase interrupt is enabled.

0 = Timebase interrupt is disabled.

### **TBON** — Timebase Enabled Bit

This read/write bit enables the timebase. Timebase may be turned off to reduce power consumption when its function is not necessary. The counter can be initialized by clearing and then setting this bit. Reset clears the TBON bit.

1 = Timebase is enabled.

0 = Timebase is disabled and the counter initialized to 0s.

Timer Interface Module (TIM)

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H and TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSCR0) controls and monitors the PWM signal from the linked channels.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0 percent duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100 percent duty cycle output. See 15.8.4 TIM Channel Status and Control Registers.

## 15.5 Interrupts

These TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The timer overflow flag (TOF) bit is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow interrupt requests. TOF and TOIE are in the TIM status and control registers.

- TIM channel flags (CH1F and CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE = 1. CHxF and CHxIE are in the TIM channel x status and control register.

## **15.6 Low-Power Modes**

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 15.6.1 Wait Mode

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 15.6.2 Stop Mode

The TIM is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

## 15.7 I/O Signals

Port A shares two of its pins with the TIM, PTA3/KBD3/TCH1 and PTA2/KBD2/TCH0. Each channel input/output (I/O) pin is programmable independently as an input capture pin or an output compare pin. TCH0 can be configured as buffered output compare or buffered PWM pins.

#### **Timer Interface Module (TIM)**

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as 0. Reset clears the TRST bit.

1 = Prescaler and TIM counter cleared

0 = No effect

#### NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

#### PS2–PS0 — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIM counter as Table 15-2 shows. Reset clears the PS2–PS0 bits.

| PS2-PS0 | TIM Clock Source        |  |  |  |

|---------|-------------------------|--|--|--|

| 000     | Internal bus clock ÷1   |  |  |  |

| 001     | Internal bus clock ÷ 2  |  |  |  |

| 010     | Internal bus clock ÷ 4  |  |  |  |

| 011     | Internal bus clock ÷ 8  |  |  |  |

| 100     | Internal bus clock ÷ 16 |  |  |  |

| 101     | Internal bus clock ÷ 32 |  |  |  |

| 110     | Internal bus clock ÷ 64 |  |  |  |

| 111     | Not available           |  |  |  |

| Table 15-2. Prescaler Selection | Table <sup>·</sup> | 15-2. | Prescaler | Selection |

|---------------------------------|--------------------|-------|-----------|-----------|

|---------------------------------|--------------------|-------|-----------|-----------|

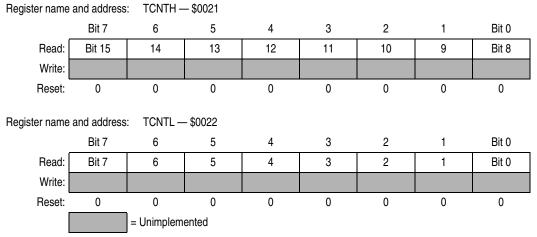

## 15.8.2 TIM Counter Registers

The two read-only TIM counter registers (TCNTH and TCNTL) contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005. All rights reserved.

MC68HC908KX8 Rev. 2.1, 07/2005