Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2011110                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | SCI                                                       |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 192 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 4x8b                                                  |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

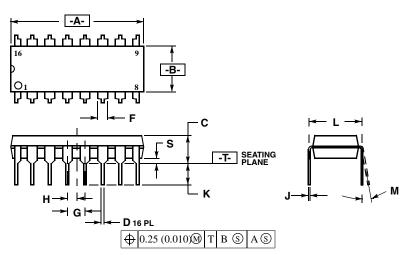

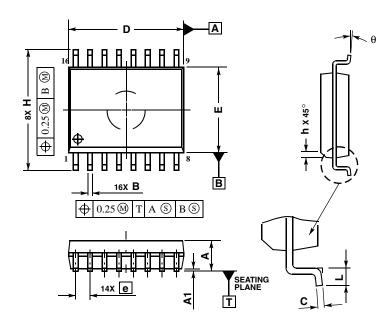

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 16-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908kx8mdwe |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| 6.3.4 | Program Counter             | 57 |

|-------|-----------------------------|----|

| 6.3.5 | Condition Code Register     | 58 |

| 6.4   | Arithmetic/Logic Unit (ALU) | 59 |

| 6.5   | Low-Power Modes             | 59 |

| 6.5.1 | Wait Mode                   | 59 |

| 6.5.2 | Stop Mode                   | 59 |

| 6.6   | CPU During Break Interrupts | 59 |

| 6.7   | Instruction Set Summary     | 60 |

| 6.8   | Opcode Map                  | 65 |

# Chapter 7 Internal Clock Generator Module (ICG)

| 7.1     | Introduction                                       | 37 |

|---------|----------------------------------------------------|----|

| 7.2     | Features                                           | 37 |

| 7.3     | Functional Description                             | 37 |

| 7.3.1   | Clock Enable Circuit                               | 69 |

| 7.3.2   | Internal Clock Generator                           | 39 |

| 7.3.2.1 | Digitally Controlled Oscillator 7                  | 70 |

| 7.3.2.2 | Modulo "N" Divider                                 | 70 |

| 7.3.2.3 | Frequency Comparator                               | 70 |

| 7.3.2.4 | Digital Loop Filter                                | 71 |

| 7.3.3   | External Clock Generator                           | 71 |

| 7.3.3.1 | External Oscillator Amplifier                      | 71 |

| 7.3.3.2 |                                                    |    |

| 7.3.4   | Clock Monitor Circuit                              | 73 |

| 7.3.4.1 | Clock Monitor Reference Generator                  | 73 |

| 7.3.4.2 | Internal Clock Activity Detector                   | 75 |

| 7.3.4.3 | External Clock Activity Detector                   | 75 |

| 7.3.5   | Clock Selection Circuit                            |    |

| 7.3.5.1 | Clock Selection Switches                           | 77 |

| 7.3.5.2 | Clock Switching Circuit                            | 77 |

| 7.4     | Usage Notes                                        | 77 |

| 7.4.1   | Switching Clock Sources                            | 78 |

| 7.4.2   | Enabling the Clock Monitor                         | 78 |

| 7.4.3   | Using Clock Monitor Interrupts                     | 79 |

| 7.4.4   | Quantization Error in DCO Output 8                 | 30 |

| 7.4.4.1 | Digitally Controlled Oscillator 8                  | 30 |

| 7.4.4.2 | Binary Weighted Divider                            | 30 |

| 7.4.4.3 | Variable-Delay Ring Oscillator 8                   | 31 |

| 7.4.4.4 | Ring Oscillator Fine-Adjust Circuit 8              | 31 |

| 7.4.5   | Switching Internal Clock Frequencies 8             | 31 |

| 7.4.6   | Nominal Frequency Settling Time                    | 31 |

| 7.4.6.1 | Settling To Within 15%                             | 32 |

| 7.4.6.2 | Total Settling Time                                | 32 |

| 7.4.7   | Trimming Frequency on the Internal Clock Generator | 33 |

#### **Monitor ROM**

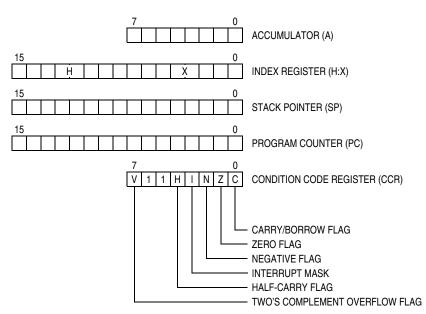

| Interrupt Status Register 2<br>(INT2)   Read:<br>(INT2)   IF14   IF13   IF12   IF11   IF10   IF9   IF8   IF7     SFE05   (INT2)<br>(INT2)   Write:<br>(INT3)   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Addr.                                   | Register Name                   |        | Bit 7   | 6    | 5    | 4           | 3            | 2      | 1     | Bit 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------|--------|---------|------|------|-------------|--------------|--------|-------|-------|

| SFE05   (INT2)<br>See page 150   Write:   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | Interrupt Status Register 2     | Read:  | IF14    | IF13 | IF12 | IF11        | IF10         | IF9    | IF8   | IF7   |

| SFE06   Interrupt Status Register 3<br>(INT3)   Readt<br>(INT3)   IF22   IF21   IF20   IF19   IF18   IF17   IF16   IF15     SFE07   RASH Test Control<br>Register (FLCR)   Readt<br>Write:   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R <td>\$FE05</td> <td>(INT2)</td> <td>Write:</td> <td>R</td> <td>R</td> <td>R</td> <td>R</td> <td>R</td> <td>R</td> <td>R</td> <td>R</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$FE05                                  | (INT2)                          | Write: | R       | R    | R    | R           | R            | R      | R     | R     |

| SFE06   Interrupt Values Register 3<br>See page 150.   Write:<br>Reset:   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         | See page 150.                   | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| SFE06   (INT3)   Write   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | Interrupt Status Register 3     | Read:  | IF22    | IF21 | IF20 | IF19        | IF18         | IF17   | IF16  | IF15  |

| SFE07   FLASH Test Control<br>Register (FLTCR)   Read:<br>Write:<br>Reset:   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$FE06                                  | (INT3)                          | Write: | R       | R    | R    | R           | R            | R      | R     | R     |

| SFE07   FLASH Test Control<br>Register (FLTCH)<br>Register (FLTCH)   Write:<br>Reset:<br>Reset:   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | See page 150.                   | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| FLASH Control Register<br>(FLCR)   Read:<br>(FLCR)   0   0   0   0   HVEN   MARGIN   ERASE   PGM     SFE08   (FLCR)   (FLCR)   Write:<br>Reset:   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$FE07                                  |                                 |        | R       | R    | R    | R           | R            | R      | R     | R     |

| SFE08   (FLCR)   Write:   HVEN   MARGIN   ERASE   PGM     SFE08   (FLCR)   Reset:   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0 <td></td> <td></td> <td>Reset:</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |                                 | Reset: |         |      |      |             |              |        |       |       |

| SFE08   (FLCR)   Write:   Image: Constraint of the c                                                                     |                                         | FLASH Control Register          | Read:  | 0       | 0    | 0    | 0           |              | MARGIN | EBASE | PGM   |

| Break Address Register High<br>(BRKH)   Read:<br>(BRKH)   Bit 15   14   13   12   11   10   9   Bit 8     \$FE09   Break Address Register Low<br>(BRKL)   Read:<br>(BRKL)   Bit 15   14   13   12   11   10   9   Bit 8     \$FE04   Break Address Register Low<br>(BRKL)   Read:<br>(BRKL)   Bit 7   6   5   4   3   2   1   Bit 0     \$FE0A   Break Address Register Low<br>(BRKL)   Read:<br>(BRKL)   Bit 7   6   5   4   3   2   1   Bit 0     \$FE0A   Break Status and Control<br>Register (BRKSCR)<br>See page 171.   Read:   BRKE   BRKA   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \$FE08                                  | (FLCR)                          | Write: |         |      |      |             |              | WANGIN | LHAGE | F GIM |

| Break Address Register Hight   Write:   Bit 15   14   13   12   11   10   9   Bit 8     \$FE09   (BRKH)   See page 172.   Reset:   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | See page 31.                    | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| Break Address Register Low<br>(BRKL)   Read:<br>(BRKL)   Bit 7   6   5   4   3   2   1   Bit 0     SFE0A   (BRKL)   See page 172.   Read:   Bit 7   6   5   4   3   2   1   Bit 0     SFE0A   (BRKL)   See page 172.   Reset:   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$FE09                                  | (BRKH)                          |        | Bit 15  | 14   | 13   | 12          | 11           | 10     | 9     | Bit 8 |

| SFE0A   (BRKL)<br>(BRKL)<br>See page 172.   Write:<br>Reset:   Bit 7   6   5   4   3   2   1   Bit 0     SFE0A   (BRKL)<br>See page 172.   See page 172.   Reset:   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | See page 172.                   | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| Break Status and Control<br>Register (BRKSCR)<br>See page 171.   Read:<br>Write:   BRKE   BRKA   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$FE0A                                  | (BRKL)                          |        | Bit 7   | 6    | 5    | 4           | 3            | 2      | 1     | Bit 0 |

| SFEOB   Register (BRKSCR)<br>See page 171.   Write:<br>Reset:   BRKE   BRKA   Image: Constraints of the constra                                                                                             |                                         | See page 172.                   | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| \$FE0B   Register (BRKSCR)<br>See page 171.   Write:   Driver   Driver<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         | Break Status and Control        | Read:  | d: DDKE |      | 0    | 0           | 0            | 0      | 0     | 0     |

| SFEOC   LVI Status Register (LVISR)<br>See page 103.   Read:<br>Write:<br>Reset:   LVIOUT   0   0   0   0   0   0   0   Read:<br>Mrite:<br>Reset:   LVIOUT   0   0   0   0   0   0   Read:<br>Mrite:<br>Reset:   BPR7   BPR6   BPR5   BPR4   BPR3   BPR2   BPR1   BPR0     \$FF7E   See page 36.   See page 36.   Write:<br>Reset:   Unaffected by reset   Unaff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | \$FE0B                                  |                                 | Write: | BRKE    | ВККА |      |             |              |        |       |       |

| \$FEOC LVI Status Register (LVISR)<br>See page 103. Write:<br>Reset: Image: Constraint of the set in the se                                                                      |                                         | See page 171.                   | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| See page 103. Write: Reset: 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 <td></td> <td></td> <td>Read:</td> <td>LVIOUT</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>R</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |                                 | Read:  | LVIOUT  | 0    | 0    | 0           | 0            | 0      | 0     | R     |

| \$FF7E FLASH Block Protect<br>Register (FLBPR) <sup>(1)</sup><br>See page 36. Read:<br>Write:<br>Reset: 0 0 0 0 0 0 0 0 0   Image: See page 36. BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \$FE0C                                  |                                 | Write: |         |      |      |             |              |        |       |       |

| \$FF7E Register (FLBPR) <sup>(1)</sup> Write: BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0   See page 36. Reset: Unaffected by reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | dee page 100.                   | Reset: | 0       | 0    | 0    | 0           | 0            | 0      | 0     | 0     |

| line in the set. I for a set of a set o | \$FF7E                                  | Register (FLBPR) <sup>(1)</sup> |        | BPR7    | BPR6 | BPR5 | BPR4        | BPR3         | BPR2   | BPR1  | BPR0  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | See page 36. Reset: Unaffected by reset |                                 |        |         |      |      |             |              |        |       |       |

| 1. Non-volatile FLASH register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |                                 |        |         |      |      |             |              |        |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                 |        |         |      |      |             |              |        |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                 |        |         |      |      |             |              |        |       |       |

| COP Control Register Read: Low byte of reset vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | COP Control Register            | Read:  |         |      |      | Low byte of | reset vector |        |       |       |

|        | COP Control Register | Read:  |                 | Low byte of                            | reset vector |                |  |  |  |  |

|--------|----------------------|--------|-----------------|----------------------------------------|--------------|----------------|--|--|--|--|

| \$FFFF | (COPCTL)             | Write: |                 | Writing clears COP counter (any value) |              |                |  |  |  |  |

|        | See page 53.         | Reset: |                 | Unaffecte                              | ed by reset  |                |  |  |  |  |

|        |                      |        | = Unimplemented | R                                      | = Reserved   | U = Unaffected |  |  |  |  |

|        |                      | ~ ~ ~  |                 | <b>-</b>                               |              |                |  |  |  |  |

Memory

#### HVEN — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can be set only if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

1 = High voltage enabled to array and charge pump on

0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the 8-Kbyte FLASH array for mass erase operation.

1 = MASS erase operation selected

0 = MASS erase operation unselected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

1 = Erase operation selected

0 = Erase operation unselected

#### PGM — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

1 = Program operation selected

0 = Program operation unselected

# 2.7 FLASH Page Erase Operation

Use this step-by-step procedure to erase a page (64 bytes) of FLASH memory to read as 1:

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{RCV}$  (typical 1 µs), the memory can be accessed in read mode again.

#### NOTE

While these operations must be performed in the order shown, other unrelated operations may occur between the steps.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

Memory

# 2.9 FLASH Program/Read Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, and \$XXE0. Use this step-by-step procedure to program a row of FLASH memory (Figure 2-4 is a flowchart representation).

### NOTE

### Only bytes which are currently \$FF may be programmed.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range desired.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{PGS}$  (minimum 5  $\mu$ s).

- 7. Write data to the FLASH address being programmed<sup>(1)</sup>.

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM  $bit^{(1)}$ .

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1 µs), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed t<sub>PROG</sub> maximum. See 17.11 Memory Characteristics.

<sup>1.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

#### **Central Processor Unit (CPU)**

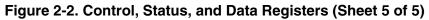

Figure 6-1. CPU Registers

### 6.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 6-2. Accumulator (A)

### 6.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 6-3. Index Register (H:X)

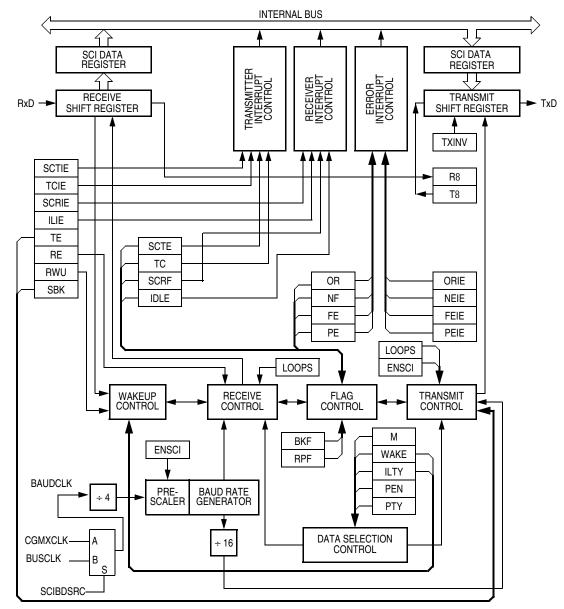

# Chapter 12 Serial Communications Interface Module (SCI)

# **12.1 Introduction**

The serial communications interface (SCI) allows asynchronous communications with peripheral devices and other microcontroller unit (MCU).

## 12.2 Features

The SCI module's features include:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Choice of baud rate clock source:

- Internal bus clock

- CGMXCLK

- 32 programmable baud rates

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter central processor unit (CPU) interrupt requests

- Programmable transmitter output polarity

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

#### Serial Communications Interface Module (SCI)

Figure 12-3. SCI Module Block Diagram

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is

$$\frac{170 - 176}{170} \times 100 = 3.53\%.$$

### 12.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

Depending on the state of the WAKE bit in SCC1, either of two conditions on the RxD pin can bring the receiver out of the standby state:

- 1. Address mark An address mark is a 1 in the most significant bit position of a received character. When the WAKE bit is set, an address mark wakes the receiver from the standby state by clearing the RWU bit. The address mark also sets the SCI receiver full bit, SCRF. Software can then compare the character containing the address mark to the user-defined address of the receiver. If they are the same, the receiver remains awake and processes the characters that follow. If they are not the same, software can set the RWU bit and put the receiver back into the standby state.

- 2. Idle input line condition When the WAKE bit is clear, an idle character on the RxD pin wakes the receiver from the standby state by clearing the RWU bit. The idle character that wakes the receiver does not set the receiver idle bit, IDLE, or the SCI receiver full bit, SCRF. The idle line type bit, ILTY, determines whether the receiver begins counting 1s as idle character bits after the start bit or after the stop bit.

#### NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle may cause the receiver to wake up immediately.

#### 12.4.3.7 Receiver Interrupts

These sources can generate CPU interrupt requests from the SCI receiver:

- SCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has transferred a character to the SCDR. SCRF can generate a receiver CPU interrupt request. Setting the SCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver CPU interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate CPU interrupt requests.

#### 12.4.3.8 Error Interrupts

These receiver error flags in SCS1 can generate CPU interrupt requests:

Receiver overrun (OR) — The OR bit indicates that the receive shift register shifted in a new character before the previous character was read from the SCDR. The previous character remains in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3 enables OR to generate SCI error CPU interrupt requests.

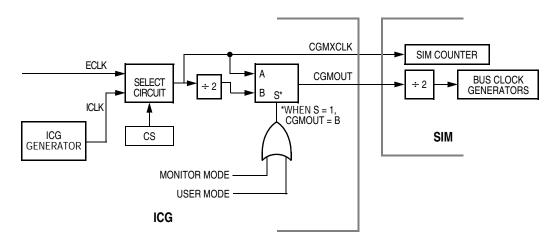

# 13.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 13-3. This clock originates from either an external oscillator or from the internal clock generator.

Figure 13-3. System Clock Signals

### 13.2.1 Bus Timing

In user mode, the internal bus frequency is the internal clock generator output (CGMXCLK) divided by four.

### 13.2.2 Clock Startup from POR or LVI Reset

When the power-on reset (POR) module or the low-voltage inhibit (LVI) module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after 4096 CGMXCLK cycles. The MCU is held in reset by the SIM during this entire period. The bus clocks start upon completion of the timeout.

### 13.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows CGMXCLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. Stop mode recovery timing is discussed in detail in 13.6.2 Stop Mode.

In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

#### System Integration Module (SIM)

# 13.7 SIM Registers

The SIM has four memory mapped registers described here.

- 1. SIM reset status register (SRSR)

- 2. Interrupt status register 1 (INT1)

- 3. Interrupt status register 2 (INT2)

- 4. Interrupt status register 2 (INT3)

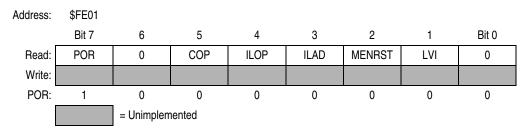

### 13.7.1 SIM Reset Status Register

This register contains five bits that show the source of the last reset. The status register will clear automatically after reading it. A power-on reset sets the POR bit and clears all other bits in the register.

#### Figure 13-16. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### COP — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

#### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

#### ILAD — Illegal Address Reset Bit (opcode fetches only)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

#### MENRST — Forced Monitor Mode Entry Reset Bit

- 1 = Last reset was caused by the MENRST circuit

- 0 = POR or read of SRSR

#### LVI — Low-Voltage Inhibit Reset Bit

- 1 = Last reset was caused by the LVI circuit

- 0 = POR or read of SRSR

#### System Integration Module (SIM)

#### IF6 — Interrupt Flag 6

Since the MC68HC908KX8 parts do not use this interrupt flag, this bit will always read 0.

Bit 0 and Bit 1 — Always read 0

#### 13.7.2.2 Interrupt Status Register 2

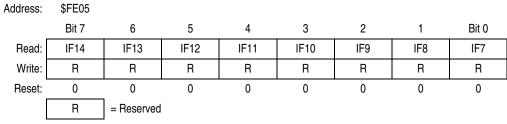

Figure 13-18. Interrupt Status Register 2 (INT2)

#### IF14–IF11 — Interrupt Flags 14–11

These flags indicate the presence of interrupt requests from the sources shown in Table 13-2.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### IF10–IF7 — Interrupt Flags 10–7

Since the MC68HC908KX8 parts do not use these interrupt flags, these bits will always read 0.

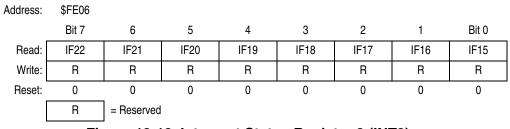

#### 13.7.2.3 Interrupt Status Register 3

Figure 13-19. Interrupt Status Register 3 (INT3)

#### IF22–IF17 — Interrupt Flags 22–17

Since the MC68HC908KX8 parts do not use these interrupt flags, these bits will always read 0.

#### IF16–IF15 — Interrupt Flags 16–15

These flags indicate the presence of interrupt requests from the sources shown in Table 13-2.

1 = Interrupt request present

0 = No interrupt request present

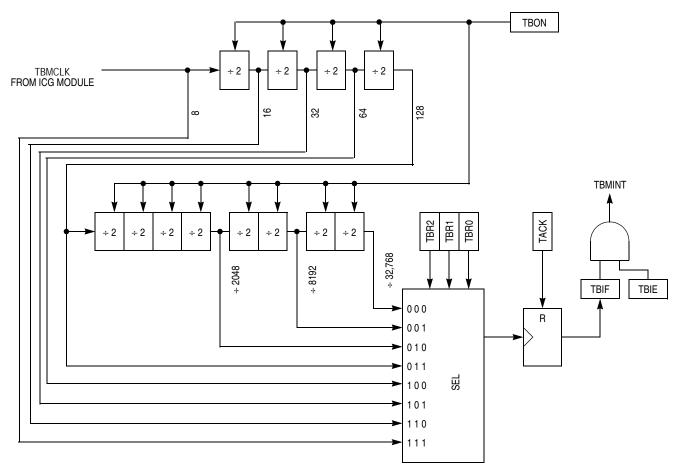

#### Timebase Module (TBM)

Figure 14-1. Timebase Block Diagram

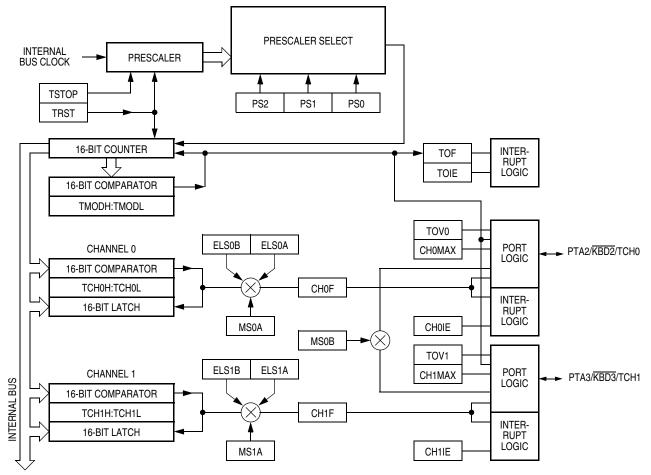

Figure 15-2. TIM Block Diagram

| Addr.  | Register Name                                 |                 | Bit 7  | 6          | 5      | 4    | 3  | 2    | 1   | Bit 0 |

|--------|-----------------------------------------------|-----------------|--------|------------|--------|------|----|------|-----|-------|

|        | Timer Status and Control                      | Read:           | TOF    | TOIE       | TSTOP  | 0    | 0  | PS2  | PS1 | PS0   |

| \$0020 | Register (TSC)                                | Write:          | 0      | IOIE       | 13105  | TRST |    | F 32 | FOI | F30   |

|        | See page 163.                                 | Reset:          | 0      | 0          | 1      | 0    | 0  | 0    | 0   | 0     |

|        | Timer Counter Register High                   | Read:           | Bit 15 | 14         | 13     | 12   | 11 | 10   | 9   | Bit 8 |

| \$0021 | (TCNTH)                                       | Write:          |        |            |        |      |    |      |     |       |

|        | See page 164.                                 | Reset:          | 0      | 0          | 0      | 0    | 0  | 0    | 0   | 0     |

|        | Timer Counter Register Low                    | Read:           | Bit 7  | 6          | 5      | 4    | 3  | 2    | 1   | Bit 0 |

| \$0022 | (TCNTL)                                       | Write:          |        |            |        |      |    |      |     |       |

|        | See page 164.                                 | Reset:          | 0      | 0          | 0      | 0    | 0  | 0    | 0   | 0     |

| \$0023 | Timer Counter Modulo<br>Register High (TMODH) | Read:<br>Write: | Bit 15 | 14         | 13     | 12   | 11 | 10   | 9   | Bit 8 |

|        | See page 165.                                 | Reset:          | 1      | 1          | 1      | 1    | 1  | 1    | 1   | 1     |

|        |                                               | [               |        | = Unimplem | nented |      |    |      |     |       |

Figure 15-3. TIM I/O Register Summary

#### Timer Interface Module (TIM)

| Addr.  | Register Name                                |                 | Bit 7  | 6                         | 5      | 4           | 3              | 2     | 1    | Bit 0   |

|--------|----------------------------------------------|-----------------|--------|---------------------------|--------|-------------|----------------|-------|------|---------|

| \$0024 | Timer Counter Modulo<br>Register Low (TMODL) | Read:<br>Write: | Bit 7  | 6                         | 5      | 4           | 3              | 2     | 1    | Bit 0   |

|        | See page 165.                                | Reset:          | 1      | 1                         | 1      | 1           | 1              | 1     | 1    | 1       |

|        | Timer Channel 0 Status and                   | Read:           | CH0F   | CHOIE                     | MS0B   | MS0A        | ELS0B          | ELS0A | TOV0 | CH0MAX  |

| \$0025 | Control Register (TSC0)                      | Write:          | 0      |                           | MOOD   | MOUA        | LLOUD          | LLOUA | 1000 |         |

|        | See page 165.                                | Reset:          | 0      | 0                         | 0      | 0           | 0              | 0     | 0    | 0       |

| \$0026 | Timer Channel 0 Register<br>High (TCH0H)     | Read:<br>Write: | Bit 15 | 14                        | 13     | 12          | 11             | 10    | 9    | Bit 8   |

|        | See page 168.                                | Reset:          |        |                           |        | Indetermina | te after reset |       |      |         |

| \$0027 | Timer Channel 0 Register<br>Low (TCH0L)      | Read:<br>Write: | Bit 7  | 6                         | 5      | 4           | 3              | 2     | 1    | Bit 0   |