# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART                             |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                       |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 15x16b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 36-XFBGA                                                              |

| Supplier Device Package    | 36-XFBGA (3.5x3.5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl17z32vda4r |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Configurable for short and long timeout values, the longest timeout is up to 262 seconds

- Support window mode

# 2.2 Peripheral features

The following sections describe the features of each peripherals of the chip.

# 2.2.1 BME

The Bit Manipulation Engine (BME) provides hardware support for atomic readmodify-write memory operations to the peripheral address space in Cortex-M0+ based microcontrollers. It reduces up to 30% of the code size and up to 9% of the cycles for bit-oriented operations to peripheral registers.

The BME supports unsigned bit field extract, load-and-set 1-bit, load-and-clear 1-bit, bit field insert, logical AND/OR/XOR operations with byte, halfword or word-sized data type.

# 2.2.2 DMA and DMAMUX

The DMA controller module enables fast transfers of data, which provides an efficient way to move blocks of data with minimal processor interaction. The DMA controller in this device implements four channels which can be routed from up to 63 DMA request sources through DMA MUX module. Some of the peripheral request sources have asynchronous DMA capability which can be used to wake MCU from Stop mode. The peripherals which have such capability include LPUART0, LPUART1, FlexIO, TPM0-TPM2, ADC0, CMP0, PORTA-PORTE. The DMA channel 0 and 1 can be periodically triggered by PIT via DMA MUX.

Main features are listed below:

- Dual-address transfers via 32-bit master connection to the system bus and data transfers in 8-, 16-, or 32-bit blocks

- Supports programmable source and destination address and transfer size, optional modulo addressing from 16 bytes to 256 KB

- Automatic updates of source and destination addresses

- Full-duplex or single-wire bidirectional mode

- Programmable transmit bit rate

- Double-buffered transmit and receive data register

- Serial clock phase and polarity options

- Slave select output

- Mode fault error flag with CPU interrupt capability

- Control of SPI operation during wait mode

- Selectable MSB-first or LSB-first shifting

- Programmable 8- or 16-bit data transmission length

- Receive data buffer hardware match feature

- 64-bit FIFO mode for high speed/large amounts of data transfers

- Support DMA

### 2.2.14 I2C

This device contains two I2C modules, which support up to 1 Mbits/s by dual buffer features, and address match to wake MCU from the low power mode.

I2C modules support DMA transfer, and the interrupt condition can trigger DMA request when DMA function is enabled.

The I2C modules have the following features:

- Support for system management bus (SMBus) Specification, version 2

- Software programmable for one of 64 different serial clock frequencies

- Software-selectable acknowledge bit

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation and detection

- Repeated START signal generation and detection

- Acknowledge bit generation and detection

- Bus busy detection

- General call recognition

- 10-bit address extension

- Programmable input glitch filter

- Low power mode wakeup on slave address match

- Range slave address support

- DMA support

- Double buffering support to achieve higher baud rate

| Chip signal name | Module signal<br>name | Description                                                                                                                                                                                     | I/O |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TPM_CLKIN[1:0]   | TPM_EXTCLK            | External clock. TPM external clock can be selected to increment the TPM counter on every rising edge synchronized to the counter clock.                                                         | -   |

| TPM1_CH[1:0]     | TPM_CHn               | TPM channel (n = 1 to 0). A TPM channel pin is configured as output when configured in an output compare or PWM mode and the TPM counter is enabled, otherwise the TPM channel pin is an input. | I/O |

#### Table 17. TPM1 signal descriptions

#### Table 18. TPM2 signal descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                                                                     | I/O |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TPM_CLKIN[1:0]   | TPM_EXTCLK            | External clock. TPM external clock can be selected to increment<br>the TPM counter on every rising edge synchronized to the counter<br>clock.                                                   | Ι   |

| TPM2_CH[1:0]     | TPM_CHn               | TPM channel (n = 1 to 0). A TPM channel pin is configured as output when configured in an output compare or PWM mode and the TPM counter is enabled, otherwise the TPM channel pin is an input. | I/O |

#### Table 19. LPTMR0 signal descriptions

| Chip signal name | Module signal<br>name | Description             | I/O |

|------------------|-----------------------|-------------------------|-----|

| LPTMR0_ALT[3:1]  | LPTMR0_ALTn           | Pulse Counter Input pin | I   |

#### Table 20. RTC signal descriptions

| Chip signal name        | Module signal<br>name | Description                         | I/O |

|-------------------------|-----------------------|-------------------------------------|-----|

| RTC_CLKOUT <sup>1</sup> | RTC_CLKOUT            | 1 Hz square-wave output or OSCERCLK | 0   |

1. RTC\_CLKOUT can also be driven with OSCERCLK via SIM control bit SIM\_SOPT[RCTCLKOUTSEL]

### 4.3.6 Communication interfaces

### Table 21. SPI0 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI0_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

Table continues on the next page...

NOTES:

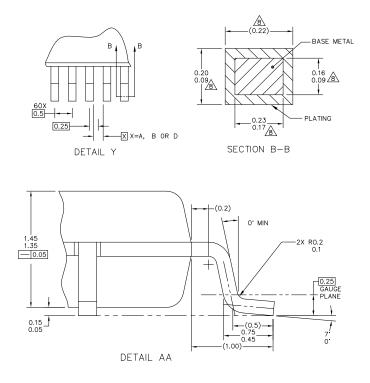

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- A DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- $\underline{\bigtriangleup}$  dimensions to be determined at seating plane c.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 MM AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 MM.

- THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

- $\triangle$  exact shape of each corner is optional.

### Figure 12. 64-pin LQFP package dimensions 2

| Symbol           | Description                                                               | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IO</sub>  | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

Table 33.

Voltage and current absolute operating ratings (continued)

### 5.2 General

### 5.2.1 AC electrical characteristics

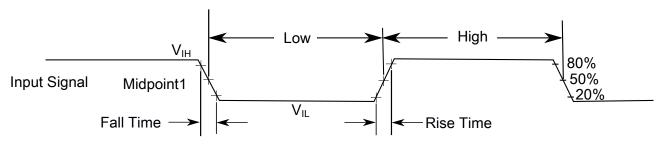

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  + ( $V_{IH}$  -  $V_{IL}$ ) / 2

### Figure 19. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30$  pF loads

- Slew rate disabled

- Normal drive strength

### 5.2.2 Nonswitching electrical specifications

| Symbol           | Description                                                                                                                                                                                                        |     | •   | Tempera | ature (°C | ;)  |     | Unit |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|------|

|                  |                                                                                                                                                                                                                    | -40 | 25  | 50      | 70        | 85  | 105 |      |

|                  |                                                                                                                                                                                                                    | 40  | 40  | 40      | 40        | 40  | 40  |      |

| I <sub>BG</sub>  | Bandgap adder when BGEN bit is set<br>and device is placed in VLPx or VLLSx<br>mode.                                                                                                                               | 45  | 45  | 45      | 45        | 45  | 45  | μA   |

| I <sub>ADC</sub> | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions. | 320 | 320 | 320     | 320       | 320 | 320 | μA   |

### Table 39. Low power mode peripheral adders — typical value (continued)

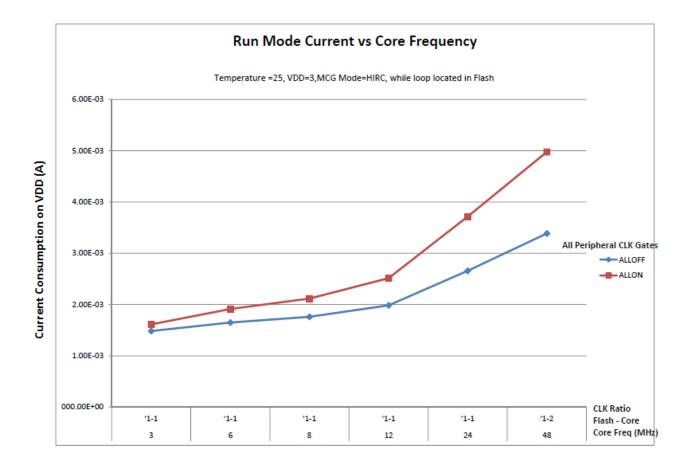

### 5.2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG-Lite in HIRC for run mode, and LIRC for VLPR mode

- No GPIOs toggled

- Code execution from flash

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

Figure 20. Run mode supply current vs. core frequency

### 5.2.3.2 General switching specifications

These general-purpose specifications apply to all signals configured for GPIO and UART signals.

| Description                                                                           | Min. | Max. | Unit                | Notes |

|---------------------------------------------------------------------------------------|------|------|---------------------|-------|

| GPIO pin interrupt pulse width (digital glitch filter disabled)<br>— Synchronous path | 1.5  | —    | Bus clock<br>cycles | 1     |

| External RESET and NMI pin interrupt pulse width — Asynchronous path                  | 100  | _    | ns                  | 2     |

| GPIO pin interrupt pulse width — Asynchronous path                                    | 16   | _    | ns                  | 2     |

| Port rise and fall time                                                               |      | 36   | ns                  | 3     |

#### Table 42. General switching specifications

1. The synchronous and asynchronous timing must be met.

2. This is the shortest pulse that is guaranteed to be recognized.

3. 75 pF load

### 5.2.4 Thermal specifications

#### 5.2.4.1 Thermal operating requirements Table 43. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed the maximum. The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\theta JA} \times chip$  power dissipation.

### 5.2.4.2 Thermal attributes

### NOTE

The 48 QFN and 64 MAPBGA packages for this product are not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/ KPYW for more details.

| Board type        | Symbol            | Description                                                                                              | 32 QFN | 36<br>XFBGA | 64 LQFP | Unit | Notes     |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|--------|-------------|---------|------|-----------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 101    | 81.5        | 71      | °C/W | 1, 2, 3   |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 33     | 54.7        | 53      | °C/W | 1, 2, 3,4 |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 84     | 71.3        | 60      | °C/W | 1, 4, 5   |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 28     | 50.0        | 47      | °C/W | 1, 4, 5   |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 13     | 58.0        | 35      | °C/W | 6         |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 1.7    | 45.3        | 21      | °C/W | 7         |

| —                 | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 3      | 1.2         | 5       | °C/W | 8         |

| _                 | Ψ <sub>JB</sub>   | Thermal characterization<br>parameter, junction to package<br>bottom (natural convection)                | -      | 44.5        | -       | °C/W | 9         |

### Table 44. Thermal attributes

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Per JEDEC JESD51-6 with the board horizontal.

- 5. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 6. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 7. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 8. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 9. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

# 5.3 Peripheral operating requirements and behaviors

### 5.3.1 Core modules

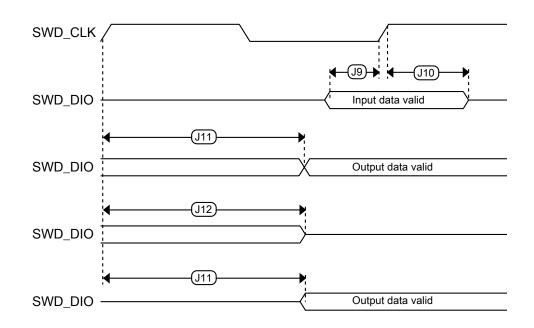

Figure 23. Serial wire data timing

### 5.3.2 System modules

There are no specifications necessary for the device's system modules.

### 5.3.3 Clock modules

#### 5.3.3.1 MCG-Lite specifications Table 46. IRC48M specifications

| Symbol                     | Description                                                                                     | Min. | Тур.  | Max.  | Unit                 | Notes |

|----------------------------|-------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| I <sub>DD48M</sub>         | Supply current                                                                                  | —    | 400   | 500   | μA                   |       |

| f <sub>irc48m</sub>        | Internal reference frequency                                                                    | _    | 48    |       | MHz                  |       |

| Δf <sub>irc48m_ol_lv</sub> | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over temperature | _    | ± 0.5 | ± 1.5 | %f <sub>irc48m</sub> |       |

| Δf <sub>irc48m_ol_hv</sub> | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over temperature | _    | ± 0.5 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

| J <sub>cyc_irc48m</sub>    | Period Jitter (RMS)                                                                             | _    | 35    | 150   | ps                   |       |

| t <sub>irc48mst</sub>      | Startup time                                                                                    | _    | 2     | 3     | μs                   | 2     |

- 1. The maximum value represents characterized results equivalent to the mean plus or minus three times the standard deviation (mean±3 sigma).

- 2. IRC48M startup time is defined as the time between clock enablement and clock availability for system use. Enable the clock by one of the following settings:

- MCG operating in an external clocking mode and MCG\_C7[OSCSEL]=10, or

- SIM\_SOPT2[PLLFLLSEL]=11

| Symbol                | Description                          | Min. | Тур. | Max. | Unit              | Notes |

|-----------------------|--------------------------------------|------|------|------|-------------------|-------|

| I <sub>DD_2M</sub>    | Supply current in 2 MHz mode         | —    | 14   | 17   | μA                | —     |

| I <sub>DD_8M</sub>    | Supply current in 8 MHz mode         | —    | 30   | 35   | μA                | —     |

| f <sub>IRC_2M</sub>   | f <sub>IRC_2M</sub> Output frequency |      | 2    | _    | MHz               | _     |

| f <sub>IRC_8M</sub>   | Output frequency                     | —    | 8    | _    | MHz               | —     |

| f <sub>IRC_T_2M</sub> | Output frequency range (trimmed)     | —    | —    | ±3   | %f <sub>IRC</sub> | —     |

| f <sub>IRC_T_8M</sub> | Output frequency range (trimmed)     | —    | —    | ±3   | %f <sub>IRC</sub> | —     |

| T <sub>su_2M</sub>    | T <sub>su_2M</sub> Startup time      |      | —    | 12.5 | μs                | —     |

| T <sub>su_8M</sub>    | Startup time                         | —    | _    | 12.5 | μs                | _     |

#### Table 47. IRC8M/2M specification

### 5.3.3.2 Oscillator electrical specifications

#### 5.3.3.2.1 Oscillator DC electrical specifications Table 48. Oscillator DC electrical specifications

| Symbol             | Description                             | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-----------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub>    | Supply voltage                          | 1.71 | —    | 3.6  | V    |       |

| I <sub>DDOSC</sub> | Supply current — low-power mode (HGO=0) |      |      |      |      | 1     |

|                    | • 32 kHz                                | _    | 500  | —    | nA   |       |

|                    | • 4 MHz                                 | _    | 200  | —    | μA   |       |

|                    | • 8 MHz (RANGE=01)                      | _    | 300  | _    | μA   |       |

|                    | • 16 MHz                                | _    | 950  | _    | μA   |       |

|                    | • 24 MHz                                | _    | 1.2  | _    | mA   |       |

|                    | • 32 MHz                                | _    | 1.5  | _    | mA   |       |

| IDDOSC             | Supply current — high gain mode (HGO=1) |      |      |      |      | 1     |

|                    | • 32 kHz                                | _    | 25   | _    | μA   |       |

|                    | • 4 MHz                                 | _    | 400  | _    | μA   |       |

|                    | • 8 MHz (RANGE=01)                      | _    | 500  | _    | μA   |       |

|                    | • 16 MHz                                | _    | 2.5  | _    | mA   |       |

|                    | • 24 MHz                                | _    | 3    | _    | mA   |       |

|                    | • 32 MHz                                | _    | 4    | _    | mA   |       |

Table continues on the next page ...

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| C <sub>x</sub>               | EXTAL load capacitance                                                                                 | _    | —               | —    |      | 2, 3  |

| Cy                           | XTAL load capacitance                                                                                  | _    | _               | —    |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              |      |                 |      | ΜΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | _    | 10              | _    | ΜΩ   |       |

|                              | Feedback resistor — high-frequency, low-<br>power mode (HGO=0)                                         | —    | _               |      | ΜΩ   |       |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | —    | 1               | _    | ΜΩ   | -     |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | _    | _               |      | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | _    | 200             |      | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               | _    | —               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

### Table 48. Oscillator DC electrical specifications (continued)

1. V<sub>DD</sub>=3.3 V, Temperature =25 °C

2. See crystal or resonator manufacturer's recommendation

3.  $C_x, C_y$  can be provided by using the integrated capacitors when the low frequency oscillator (RANGE = 00) is used. For all other cases external capacitors must be used.

4. When low power mode is selected,  $R_F$  is integrated and must not be attached externally.

5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

| Symbol                | Description                                                                                               | Min.                             | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                     | 32                               | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | hi_1 Oscillator crystal or resonator frequency —<br>high-frequency mode (low range)<br>(MCG_C2[RANGE]=01) |                                  | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | high frequency mode (high range)<br>(MCG_C2[RANGE]=1x)                                                    |                                  | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                               | ncy (external clock mode) — — 48 |      | MHz  | 1, 2 |       |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                              | 40                               | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                    | —                                | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                    | _                                | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)              | _                                | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)              | _                                | 1    | _    | ms   |       |

### 5.3.3.2.2 Oscillator frequency specifications Table 49. Oscillator frequency specifications

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

3. Proper PC board layout procedures must be followed to achieve specifications.

4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

### 5.3.4 Memories and memory interfaces

### 5.3.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

### 5.3.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                | Description                        | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>   | Longword Program high-voltage time |      | 7.5  | 18   | μs   | —     |

| t <sub>hversscr</sub> | Sector Erase high-voltage time     | —    | 13   | 113  | ms   | 1     |

| t <sub>hversall</sub> | Erase All high-voltage time        | —    | 52   | 452  | ms   | 1     |

#### Table 50. NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

#### 5.3.4.1.2 Flash timing specifications — commands Table 51. Flash command timing specifications

| Symbol                | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|------|-------|

| t <sub>rd1sec1k</sub> | Read 1s Section execution time (flash sector) | _    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | _    | _    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | _    | 65   | 145  | μs   |       |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | _    | —    | 0.9  | ms   | 1     |

| t <sub>rdonce</sub>   | Read Once execution time                      | _    | —    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | _    | 65   | —    | μs   | _     |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | _    | 70   | 575  | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | —    | —    | 30   | μs   | 1     |

| t <sub>ersallu</sub>  | Erase All Blocks Unsecure execution time      | _    | 70   | 575  | ms   | 2     |

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

### 5.3.4.1.3 Flash high voltage current behaviors Table 52. Flash high voltage current behaviors

| Symbol              | Symbol Description                                                    |   | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|---|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation |   | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       | _ | 1.5  | 4.0  | mA   |

# 5.3.4.1.4 Reliability specifications

### Table 53. NVM reliability specifications

| Symbol | Description   | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |  |

|--------|---------------|------|-------------------|------|------|-------|--|

|        | Program Flash |      |                   |      |      |       |  |

Table continues on the next page...

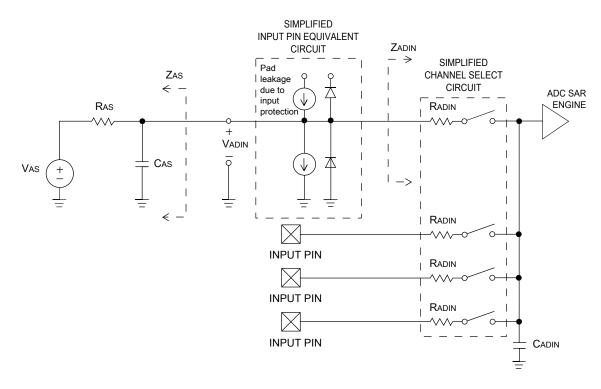

| Symbol            | Description                       | Conditions                                                                                                      | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|-------------------|---------|------|-------|

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | ≤ 13-bit mode                                                                                                   | 1.0    | —                 | 18.0    | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | 16-bit mode                                                                                                     | 2.0    |                   | 12.0    | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion<br>rate            | ≤ 13-bit modes<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time | 20.000 | _                 | 818.330 | ksps | 5     |

| C <sub>rate</sub> | ADC conversion<br>rate            | 16-bit mode<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time    | 37.037 | _                 | 461.467 | ksps | 5     |

| Table 54. | 16-bit ADC o | perating | conditions ( | (continued) |

|-----------|--------------|----------|--------------|-------------|

|-----------|--------------|----------|--------------|-------------|

- 1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

| Symbol              | Description                    | Conditions <sup>1</sup>                                     | Min. | Typ. <sup>2</sup>      | Max. | Unit  | Notes                                                                        |

|---------------------|--------------------------------|-------------------------------------------------------------|------|------------------------|------|-------|------------------------------------------------------------------------------|

|                     |                                | • Avg = 32                                                  |      |                        |      |       |                                                                              |

| SFDR                | Spurious free<br>dynamic range | <ul><li>16-bit differential mode</li><li>Avg = 32</li></ul> | 82   | 95                     | _    | dB    | 7                                                                            |

|                     |                                | <ul><li>16-bit single-ended mode</li><li>Avg = 32</li></ul> | 78   | 90                     | —    | dB    |                                                                              |

| EIL                 | Input leakage<br>error         |                                                             |      | $I_{ln} \times R_{AS}$ |      | mV    | I <sub>In</sub> =<br>leakage<br>current                                      |

|                     |                                |                                                             |      |                        |      |       | (refer to<br>the MCU's<br>voltage<br>and<br>current<br>operating<br>ratings) |

|                     | Temp sensor slope              | Across the full temperature range of the device             | 1.55 | 1.62                   | 1.69 | mV/°C | 8                                                                            |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage         | 25 °C                                                       | 706  | 716                    | 726  | mV    | 8                                                                            |

#### Table 55. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

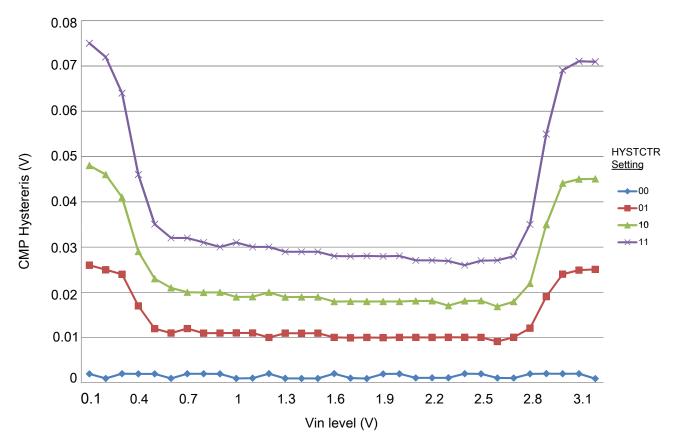

Figure 27. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | tSPSCK              | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | _                             | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x<br>t <sub>periph</sub> | ns                 | -    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        |                               | ns                 | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | _                             | ns                 | _    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 15                            | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | —                             | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25      | ns                 | _    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                               |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 25                            | ns                 | _    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                               |                    |      |

Table 60. SPI master mode timing on slew rate disabled pads

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

2.  $t_{periph} = 1/f_{periph}$

Table 61. SPI master mode timing on slew rate enabled pads

| Num. | Symbol              | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | —                             | t <sub>SPSCK</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x<br>t <sub>periph</sub> | ns                 | _    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 96                        | —                             | ns                 | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | —                             | ns                 | —    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 52                            | ns                 | —    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | —                             | ns                 | —    |

| 10   | t <sub>RI</sub>     | Rise time input                | —                         | t <sub>periph</sub> - 25      | ns                 | —    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                               |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 36                            | ns                 | —    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                               |                    |      |

1. For SPI0  $f_{periph}$  is the bus clock (f\_{BUS}). For SPI1  $f_{periph}$  is the system clock (f\_{SYS}).

2.  $t_{periph} = 1/f_{periph}$

86

Design considerations

# 6.1.4 Digital design

Ensure that all I/O pins cannot get pulled above VDD (Max I/O is VDD+0.3V).

## CAUTION

Do not provide power to I/O pins prior to VDD, especially the RESET\_b pin.

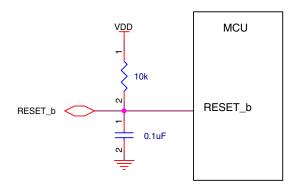

• RESET\_b pin

The RESET\_b pin is an open-drain I/O pin that has an internal pullup resistor. An external RC circuit is recommended to filter noise as shown in the following figure. The resistor value must be in the range of 4.7 k $\Omega$  to 10 k $\Omega$ ; the recommended capacitance value is 0.1  $\mu$ F. The RESET\_b pin also has a selectable digital filter to reject spurious noise.

Figure 36. Reset circuit

When an external supervisor chip is connected to the RESET\_b pin, a series resistor must be used to avoid damaging the supervisor chip or the RESET\_b pin, as shown in the following figure. The series resistor value (RS below) must be in the range of  $100 \Omega$  to  $1 \text{ k}\Omega$  depending on the external reset chip drive strength. The supervisor chip must have an active high, open-drain output.

For all other partner-developed software and tools, visit http://www.freescale.com/ partners.

# 7 Part identification

# 7.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 7.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

# 7.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                                                                                                                                                        |

|-------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                                                                                                                                    |

| KL##  | Kinetis family              | • KL17                                                                                                                                                                                                                        |

| A     | Key attribute               | • Z = Cortex-M0+                                                                                                                                                                                                              |

| FFF   | Program flash memory size   | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> </ul>                                                                                                                                                                            |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                                                                                           |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                                                                                                                              |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)<sup>1</sup></li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>MP = 64 MAPBGA (5 mm x 5 mm)<sup>1</sup></li> <li>DA = 36 XFBGA (3.5 mm x 3.5 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                                                                                                                                  |

Table 67. Part number fields description

Table continues on the next page...