Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART                            |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                      |

| Number of I/O              | 28                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 11x16b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-UFQFN Exposed Pad                                                 |

| Supplier Device Package    | 32-QFN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl17z32vfm4 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 Ord | lering info | ormation                              | 4  |

|-------|-------------|---------------------------------------|----|

| 2 Ove | erview      |                                       | 4  |

| 2.1   | System      | features                              | 5  |

|       | 2.1.1       | ARM Cortex-M0+ core                   | 5  |

|       | 2.1.2       | NVIC                                  | 6  |

|       | 2.1.3       | AWIC                                  | 6  |

|       | 2.1.4       | Memory                                | 7  |

|       | 2.1.5       | Reset and boot                        | 7  |

|       | 2.1.6       | Clock options                         | 9  |

|       | 2.1.7       | Security                              | 12 |

|       | 2.1.8       | Power management                      | 12 |

|       | 2.1.9       | LLWU                                  | 14 |

|       | 2.1.10      | Debug controller                      | 15 |

|       | 2.1.11      | COP                                   | 15 |

| 2.2   | Periphe     | ral features                          | 16 |

|       | 2.2.1       | BME                                   | 16 |

|       | 2.2.2       | DMA and DMAMUX                        | 16 |

|       | 2.2.3       | ТРМ                                   | 17 |

|       | 2.2.4       | ADC                                   | 17 |

|       | 2.2.5       | VREF                                  | 18 |

|       | 2.2.6       | CMP                                   | 19 |

|       | 2.2.7       | RTC                                   | 19 |

|       | 2.2.8       | PIT                                   | 20 |

|       | 2.2.9       | LPTMR                                 | 20 |

|       | 2.2.10      | CRC                                   | 21 |

|       | 2.2.11      | UART                                  | 21 |

|       | 2.2.12      | LPUART                                | 22 |

|       | 2.2.13      | SPI                                   | 22 |

|       | 2.2.14      | I2C                                   | 23 |

|       | 2.2.15      | FlexIO                                | 23 |

|       | 2.2.16      | Port control and GPIO                 | 24 |

| 3 Mei | mory ma     | 0                                     | 26 |

| 4 Pin | outs        |                                       | 27 |

| 4.1   | KL17 Si     | gnal Multiplexing and Pin Assignments | 27 |

| 4.2   | Pin prop    | perties                               | 30 |

| 4.3   | Module      | Signal Description Tables             | 33 |

|       | 4.3.1       | Core modules                          | 33 |

|       | 4.3.2       | System modules                        | 33 |

|       | 4.3.3       | Clock modules                         | 34 |

|       | 4.3.4       | Analog                                | 34 |

|       | 4.3.5       | Timer Modules                         | 35 |

|       | 4.3.6       | Communication interfaces              | 36 |

|       |             |                                       |    |

|   |      | 4.3.7      | Human-machine interfaces (HMI)                  | 38  |

|---|------|------------|-------------------------------------------------|-----|

|   | 4.4  | KL17 Fa    | mily Pinouts                                    | 38  |

|   | 4.5  | Package    | dimensions                                      | 43  |

| 5 | Elec | trical cha | aracteristics                                   | 51  |

|   | 5.1  | Ratings.   |                                                 | 51  |

|   |      | 5.1.1      | Thermal handling ratings                        | 51  |

|   |      | 5.1.2      | Moisture handling ratings                       | 52  |

|   |      | 5.1.3      | ESD handling ratings                            | 52  |

|   |      | 5.1.4      | Voltage and current absolute operating          |     |

|   |      |            | ratings                                         | 52  |

|   | 5.2  | General.   |                                                 | 53  |

|   |      | 5.2.1      | AC electrical characteristics                   | 53  |

|   |      | 5.2.2      | Nonswitching electrical specifications          | 53  |

|   |      | 5.2.3      | Switching specifications                        | 68  |

|   |      | 5.2.4      | Thermal specifications                          | 69  |

|   | 5.3  | Peripher   | al operating requirements and behaviors         | 70  |

|   |      | 5.3.1      | Core modules                                    | 70  |

|   |      | 5.3.2      | System modules                                  | 72  |

|   |      | 5.3.3      | Clock modules                                   | 72  |

|   |      | 5.3.4      | Memories and memory interfaces                  | 75  |

|   |      | 5.3.5      | Security and integrity modules                  | 77  |

|   |      | 5.3.6      | Analog                                          | 77  |

|   | 5.4  | Timers     |                                                 | 85  |

|   | 5.5  | Commu      | nication interfaces                             | 85  |

|   |      | 5.5.1      | SPI switching specifications                    | 85  |

|   |      | 5.5.2      | Inter-Integrated Circuit Interface (I2C) timing | 89  |

|   |      | 5.5.3      | UART                                            | 91  |

| 6 | Des  | ign consi  | derations                                       | 91  |

|   | 6.1  | Hardwar    | e design considerations                         | 91  |

|   |      | 6.1.1      | Printed circuit board recommendations           | 92  |

|   |      | 6.1.2      | Power delivery system                           | 92  |

|   |      | 6.1.3      | Analog design                                   | 93  |

|   |      | 6.1.4      | Digital design                                  | 93  |

|   |      | 6.1.5      | Crystal oscillator                              | 96  |

|   | 6.2  | Software   | e considerations                                | 98  |

| 7 | Part | identifica | ation                                           | 99  |

|   | 7.1  | Descript   | ion                                             | 99  |

|   | 7.2  | Format     |                                                 | 99  |

|   | 7.3  | Fields     |                                                 | 99  |

|   | 7.4  | Example    | )                                               | 100 |

| 8 | Rev  | ision hist | ory                                             | 100 |

3

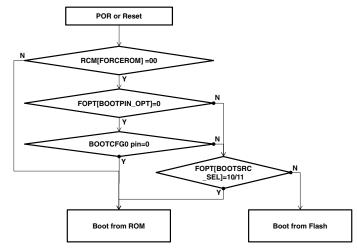

The Flash Option (FOPT) register in the Flash Memory module (FTFA\_FOPT) allows the user to customize the operation of the MCU at boot time. The register contains read-only bits that are loaded from the NVM's option byte in the flash configuration field. Below is boot flow chart for this device.

Figure 2. Boot flow chart

The blank chip is default to boot from ROM and remaps the vector table to ROM base address, otherwise, it remaps to flash address.

### 2.1.6 Clock options

This chip provides a wide range of sources to generate the internal clocks. These sources include internal resistor capacitor (IRC) oscillators, external oscillators, external clock sources, and ceramic resonators. These sources can be configured to provide the required performance and optimize the power consumption.

The IRC oscillators include the high-speed internal resister capacitor (HIRC) oscillator, the low-speed internal resister capacitor (LIRC) oscillator, and the low power oscillator (LPO).

The HIRC oscillator generates a 48 MHz clock.

The LIRC oscillator generates an 8 MHz or 2 MHz clock, and default to 8 MHz system clock on reset. The LIRC oscillator cannot be used in any VLLS modes.

The LPO generates a 1 kHz clock and cannot be used in VLLS0 mode.

9

| Core mode  | Device mode           | Descriptions                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deep sleep | Stop                  | In Stop mode, most peripheral clocks are disabled and placed in a static state. Stop mode retains all registers and SRAMs while maintaining Low Voltage Detection protection. In Stop mode, the ADC, CMP, LPTimer, RTC, and pin interrupts are operational. The NVIC is disabled, but the AWIC can be used to wake up from an interrupt.                                                                |

|            | Very Low Power Stop   | In VLPS mode, the contents of the SRAM are retained. The CMP (low speed), ADC, OSC, RTC, LPTMR, TPM, FlexIO, LPUART, and DMA are operational, LVD and NVIC are disabled, AWIC is used to wake up from interrupt.                                                                                                                                                                                        |

|            | Low Leakage Stop      | In LLS mode, the contents of the SRAM and the 32-byte system register file<br>are retained. The CMP (low speed), LLWU, LPTMR, and RTC are<br>operational. The ADC, CRC, DMA, FlexIO, I2C, LPUART, MCG-Lite, NVIC,<br>PIT, SPI, TPM, UART, and COP are static, but retain their programming. The<br>GPIO, and VREF are static, retain their programming, and continue to drive<br>their previous values. |

|            | Very Low Leakage Stop | In VLLS modes, most peripherals are powered off and will resume operation from their reset state when the device wakes up. The LLWU, LPTMR, and RTC are operational in all VLLS modes.                                                                                                                                                                                                                  |

|            |                       | In VLLS3, the contents of the SRAM and the 32-byte system register file are retained. The CMP (low speed), and PMC are operational. The GPIO, and VREF are not operational but continue driving.                                                                                                                                                                                                        |

|            |                       | In VLLS1, the contents of the 32-byte system register file are retained. The CMP (low speed), and PMC are operational. The GPIO, and VREF are not operational but continue driving.                                                                                                                                                                                                                     |

|            |                       | In VLLS0, the contents of the 32-byte system register file are retained. The PMC is operational. The GPIO is not operational but continues driving. The POR detection circuit can be enabled or disabled.                                                                                                                                                                                               |

#### Table 6. Peripherals states in different operational modes (continued)

### 2.1.9 LLWU

The LLWU module is used to wake MCU from low leakage power mode (LLS and VLLSx) and functional only on entry into a low-leakage power mode. After recovery from LLS, the LLWU is immediately disabled. After recovery from VLLSx, the LLWU continues to detect wake-up events until the user has acknowledged the wake-up event.

This device uses 8 external wakeup pin inputs and 4 internal modules as wakeup sources to the LLWU module.

The following is internal peripheral and external pin inputs as wakeup sources to the LLWU module.

## 2.2.6 CMP

The device contains one high-speed comparator and two 8-input multiplexers for both the inverting and non-inverting inputs of the comparator. Each CMP input channel connects to both muxes.

The CMP includes one 6-bit DAC, which provides a selectable voltage reference for various user application cases. Besides, the CMP also has several module-to-module interconnects in order to facilitate ADC triggering, TPM triggering, and interfaces.

The CMP has the following features:

- Inputs may range from rail to rail

- Programmable hysteresis control

- Selectable interrupt on rising-edge, falling-edge, or both rising or falling edges of the comparator output

- Selectable inversion on comparator output

- Capability to produce a wide range of outputs such as sampled, digitally filtered

- External hysteresis can be used at the same time that the output filter is used for internal functions

- Two software selectable performance levels: shorter propagation delay at the expense of higher power and Low power with longer propagation delay

- DMA transfer support

- Functional in all modes of operation except in VLLS0 mode

- The filter functions are not available in Stop, VLPS, LLS, or VLLSx modes

- Integrated 6-bit DAC with selectable supply reference source and can be power down to conserve power

- Two 8-to-1 channel mux

## 2.2.7 RTC

The RTC is an always powered-on block that remains active in all low power modes. The time counter within the RTC is clocked by a 32.768 kHz clock sourced from an external crystal using the oscillator or clock directly from RTC\_CLKIN pin.

RTC is reset on power-on reset, and a software reset bit in RTC can also initialize all RTC registers.

The RTC module has the following features

• 32-bit seconds counter with roll-over protection and 32-bit alarm

## 2.2.10 CRC

This device contains one cyclic redundancy check (CRC) module which can generate 16/32-bit CRC code for error detection.

The CRC module provides a programmable polynomial, WAS, and other parameters required to implement a 16-bit or 32-bit CRC standard.

The CRC module has the following features:

- Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift register

- Programmable initial seed value and polynomial

- Option to transpose input data or output data (the CRC result) bitwise or bytewise.

- Option for inversion of final CRC result

- 32-bit CPU register programming interface

### 2.2.11 UART

This device contains a basic universal asynchronous receiver/transmitter (UART) module with DMA function supported. Generally, this module is used in RS-232, RS-485, and other communications and supports LIN slave operation and ISO7816.

The UART module has the following features:

- Full-duplex operation

- 13-bit baud rate selection with /32 fractional divide, based on the module clock frequency

- Programmable 8-bit or 9-bit data format

- Programmable transmitter output polarity

- Programmable receive input polarity

- Up to 14-bit break character transmission.

- 11-bit break character detection option

- Two receiver wakeup methods with idle line or address mark wakeup

- Address match feature in the receiver to reduce address mark wakeup ISR overhead

- Ability to select MSB or LSB to be first bit on wire

- Support for ISO 7816 protocol to interface with SIM cards and smart cards

- Receiver framing error detection

- Hardware parity generation and checking

- Full-duplex or single-wire bidirectional mode

- Programmable transmit bit rate

- Double-buffered transmit and receive data register

- Serial clock phase and polarity options

- Slave select output

- Mode fault error flag with CPU interrupt capability

- Control of SPI operation during wait mode

- Selectable MSB-first or LSB-first shifting

- Programmable 8- or 16-bit data transmission length

- Receive data buffer hardware match feature

- 64-bit FIFO mode for high speed/large amounts of data transfers

- Support DMA

### 2.2.14 I2C

This device contains two I2C modules, which support up to 1 Mbits/s by dual buffer features, and address match to wake MCU from the low power mode.

I2C modules support DMA transfer, and the interrupt condition can trigger DMA request when DMA function is enabled.

The I2C modules have the following features:

- Support for system management bus (SMBus) Specification, version 2

- Software programmable for one of 64 different serial clock frequencies

- Software-selectable acknowledge bit

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation and detection

- Repeated START signal generation and detection

- Acknowledge bit generation and detection

- Bus busy detection

- General call recognition

- 10-bit address extension

- Programmable input glitch filter

- Low power mode wakeup on slave address match

- Range slave address support

- DMA support

- Double buffering support to achieve higher baud rate

| 64<br>LQFP | 36<br>XFB<br>GA | 32<br>QFN | 48<br>QFN | 64<br>Map<br>Bga | Pin Name                       | Default       | ALT0          | ALT1                           | ALT2      | ALT3            | ALT4           | ALT5      | ALT6     | ALT7 |

|------------|-----------------|-----------|-----------|------------------|--------------------------------|---------------|---------------|--------------------------------|-----------|-----------------|----------------|-----------|----------|------|

| 37         | _               | -         | 29        | E7               | PTB2                           | ADC0_<br>SE12 | ADC0_<br>SE12 | PTB2                           | I2C0_SCL  | TPM2_CH0        |                |           |          |      |

| 38         | —               |           | 30        | E8               | PTB3                           | ADC0_<br>SE13 | ADC0_<br>SE13 | PTB3                           | I2C0_SDA  | TPM2_CH1        |                |           |          |      |

| 39         | -               | -         | 31        | E6               | PTB16                          | DISABLED      |               | PTB16                          | SPI1_MOSI | LPUART0_<br>RX  | TPM_<br>CLKIN0 | SPI1_MISO |          |      |

| 40         | -               | _         | 32        | D7               | PTB17                          | DISABLED      |               | PTB17                          | SPI1_MISO | LPUART0_<br>TX  | TPM_<br>CLKIN1 | SPI1_MOSI |          |      |

| 41         | —               | —         | —         | D6               | PTB18                          | DISABLED      |               | PTB18                          |           | TPM2_CH0        |                |           |          |      |

| 42         | -               | -         | -         | C7               | PTB19                          | DISABLED      |               | PTB19                          |           | TPM2_CH1        |                |           |          |      |

| 43         | _               | _         | 33        | D8               | PTC0                           | ADC0_<br>SE14 | ADC0_<br>SE14 | PTC0                           |           | EXTRG_IN        |                | CMP0_OUT  |          |      |

| 44         | C5              | 22        | 34        | C6               | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | ADC0_<br>SE15 | ADC0_<br>SE15 | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | I2C1_SCL  |                 | TPM0_CH0       |           |          |      |

| 45         | B6              | 23        | 35        | B7               | PTC2                           | ADC0_<br>SE11 | ADC0_<br>SE11 | PTC2                           | I2C1_SDA  |                 | TPM0_CH1       |           |          |      |

| 46         | B5              | 24        | 36        | C8               | PTC3/<br>LLWU_P7               | DISABLED      |               | PTC3/<br>LLWU_P7               | SPI1_SCK  | LPUART1_<br>RX  | TPM0_CH2       | CLKOUT    |          |      |

| 47         | Ι               | _         | -         | E3               | VSS                            | VSS           | VSS           |                                |           |                 |                |           |          |      |

| 48         | Ι               | —         | -         | E4               | VDD                            | VDD           | VDD           |                                |           |                 |                |           |          |      |

| 49         | A6              | 25        | 37        | B8               | PTC4/<br>LLWU_P8               | DISABLED      |               | PTC4/<br>LLWU_P8               | SPI0_PCS0 | LPUART1_<br>TX  | TPM0_CH3       | SPI1_PCS0 |          |      |

| 50         | A5              | 26        | 38        | A8               | PTC5/<br>LLWU_P9               | DISABLED      |               | PTC5/<br>LLWU_P9               | SPI0_SCK  | LPTMR0_<br>ALT2 |                |           | CMP0_OUT |      |

| 51         | B4              | 27        | 39        | A7               | PTC6/<br>LLWU_P10              | CMP0_IN0      | CMP0_IN0      | PTC6/<br>LLWU_P10              | SPI0_MOSI | EXTRG_IN        |                | SPI0_MISO |          |      |

| 52         | A4              | 28        | 40        | B6               | PTC7                           | CMP0_IN1      | CMP0_IN1      | PTC7                           | SPI0_MISO |                 |                | SPI0_MOSI |          |      |

| 53         | -               | -         | -         | A6               | PTC8                           | CMP0_IN2      | CMP0_IN2      | PTC8                           | I2C0_SCL  | TPM0_CH4        |                |           |          |      |

| 54         | _               | -         | _         | B5               | PTC9                           | CMP0_IN3      | CMP0_IN3      | PTC9                           | I2C0_SDA  | TPM0_CH5        |                |           |          |      |

| 55         | _               | _         | -         | B4               | PTC10                          | DISABLED      |               | PTC10                          | I2C1_SCL  |                 |                |           |          |      |

| 56         | _               | _         | -         | A5               | PTC11                          | DISABLED      |               | PTC11                          | I2C1_SDA  |                 |                |           |          |      |

| 57         | _               | —         | 41        | C3               | PTD0                           | DISABLED      |               | PTD0                           | SPI0_PCS0 |                 | TPM0_CH0       |           | FXIO0_D0 |      |

| 58         | -               | -         | 42        | A4               | PTD1                           | ADC0_<br>SE5b | ADC0_<br>SE5b | PTD1                           | SPI0_SCK  |                 | TPM0_CH1       |           | FXIO0_D1 |      |

| 59         | _               | -         | 43        | C2               | PTD2                           | DISABLED      |               | PTD2                           | SPI0_MOSI | UART2_RX        | TPM0_CH2       | SPI0_MISO | FXIO0_D2 |      |

| 60         | _               | —         | 44        | B3               | PTD3                           | DISABLED      |               | PTD3                           | SPI0_MISO | UART2_TX        | TPM0_CH3       | SPI0_MOSI | FXIO0_D3 |      |

| 61         | A3              | 29        | 45        | A3               | PTD4/<br>LLWU_P14              | DISABLED      |               | PTD4/<br>LLWU_P14              | SPI1_PCS0 | UART2_RX        | TPM0_CH4       |           | FXIO0_D4 |      |

| 62         | B3              | 30        | 46        | C1               | PTD5                           | ADC0_<br>SE6b | ADC0_<br>SE6b | PTD5                           | SPI1_SCK  | UART2_TX        | TPM0_CH5       |           | FXIO0_D5 |      |

| 63         | B2              | 31        | 47        | B2               | PTD6/<br>LLWU_P15              | ADC0_<br>SE7b | ADC0_<br>SE7b | PTD6/<br>LLWU_P15              | SPI1_MOSI | LPUART0_<br>RX  | I2C1_SDA       | SPI1_MISO | FXIO0_D6 |      |

| Properties               | Abbreviation | Descriptions          |

|--------------------------|--------------|-----------------------|

|                          | н            | High level            |

|                          | L            | Low level             |

| Pullup/ pulldown setting | PD           | Pullup                |

| after POR                | PU           | Pulldown              |

| Slew rate after POR      | FS           | Fast slew rate        |

|                          | SS           | Slow slew rate        |

| Passive Pin Filter after | N            | Disabled              |

| POR                      | Y            | Enabled               |

| Open drain               | N            | Disabled <sup>1</sup> |

|                          | Y            | Enabled <sup>2</sup>  |

| Pin interrupt            | Y            | Yes                   |

1. When I2C module is enabled and a pin is functional for I2C, this pin is (pseudo-) open drain enabled. When UART or LPUART module is enabled and a pin is functional for UART or LPUART, this pin is (pseudo-) open drain configurable.

2. PTA20 is a true open drain pin that must never be pulled above VDD.

## 4.3 Module Signal Description Tables

The following sections correlate the chip-level signal name with the signal name used in the module's chapter. They also briefly describe the signal function and direction.

#### 4.3.1 Core modules

| Table 9. | SWD | signal | descriptions |

|----------|-----|--------|--------------|

|----------|-----|--------|--------------|

| Chip signal name | Module signal<br>name | Description                                                                                                               | I/O     |

|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|---------|

| SWD_DIO          | SWD_DIO               | Serial Wire Debug Data Input/Output                                                                                       | Input / |

|                  |                       | The SWD_DIO pin is used by an external debug tool for communication and device control. This pin is pulled up internally. | Output  |

| SWD_CLK          | SWD_CLK               | Serial Wire Clock                                                                                                         | Input   |

|                  |                       | This pin is the clock for debug logic when in the Serial Wire Debug mode. This pin is pulled down internally.             |         |

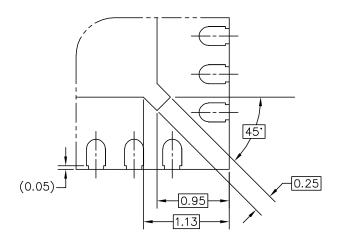

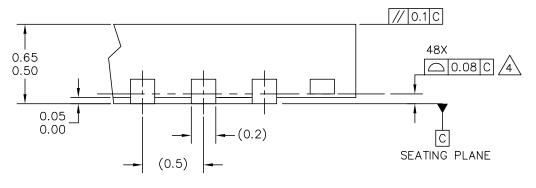

DETAIL F

DETAIL G VIEW ROTATED 90°CW

NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS A NON-JEDEC REGISTERED PACKAGE.

A. COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

#### Figure 15. 48-pin QFN package dimension 2

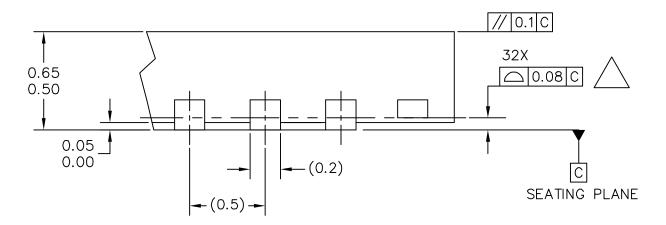

DETAIL G VIEW ROTATED 90°CW

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS A NON-JEDEC REGISTERED PACKAGE.

4 COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

#### Figure 18. 32-pin QFN package dimension 2

# **5** Electrical characteristics

## 5.1 Ratings

| Symbol           | Description                                                               | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IO</sub>  | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

Table 33.

Voltage and current absolute operating ratings (continued)

### 5.2 General

#### 5.2.1 AC electrical characteristics

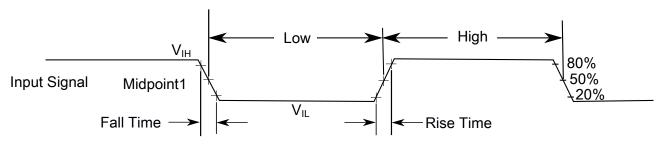

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  + ( $V_{IH}$  -  $V_{IL}$ ) / 2

#### Figure 19. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30$  pF loads

- Slew rate disabled

- Normal drive strength

#### 5.2.2 Nonswitching electrical specifications

| Symbol          | Description                                                       | Min. | Max.  | Unit | Notes |

|-----------------|-------------------------------------------------------------------|------|-------|------|-------|

| I <sub>IN</sub> | Input leakage current (per pin) for full temperature range        | _    | 1     | μΑ   | 2     |

| I <sub>IN</sub> | Input leakage current (per pin) at 25 °C                          | —    | 0.025 | μA   | 2     |

| I <sub>IN</sub> | Input leakage current (total all pins) for full temperature range | _    | 64    | μA   | 2     |

| I <sub>OZ</sub> | Hi-Z (off-state) leakage current (per pin)                        | —    | 1     | μA   |       |

| R <sub>PU</sub> | Internal pullup resistors                                         | 20   | 50    | kΩ   | 3     |

Table 36. Voltage and current operating behaviors (continued)

- 1. PTB0, PTB1, PTC3, PTC4, PTD6, and PTD7 I/O have both high drive and normal drive capability selected by the associated PTx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

- 2. Measured at  $V_{DD}$  = 3.6 V

3. Measured at  $V_{\text{DD}}$  supply voltage =  $V_{\text{DD}}$  min and Vinput =  $V_{\text{SS}}$

#### 5.2.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$  and VLLSx  $\rightarrow$  RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 48 MHz

- Bus and flash clock = 24 MHz

- HIRC clock mode

#### Table 37. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. | _    | —    | 300  | μs   |       |

|                  | <ul> <li>VLLS0 → RUN</li> </ul>                                                                                                                                   | _    | 152  | 166  | μs   |       |

|                  | • VLLS1 → RUN                                                                                                                                                     | _    | 152  | 166  | μs   |       |

|                  | VLLS3 → RUN                                                                                                                                                       |      | 93   | 104  | μs   |       |

|                  | • LLS → RUN                                                                                                                                                       |      | 7.5  | 8    | μs   |       |

|                  | <ul> <li>VLPS → RUN</li> </ul>                                                                                                                                    | _    | 7.5  | 8    | μs   |       |

|                  | • STOP → RUN                                                                                                                                                      |      | 7.5  | 8    | μs   |       |

| Symbol                 | Description                                                                                                                                                                                              | Min. | Тур.  | Max.   | Unit | Notes |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------|------|-------|

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current— 8 MHz<br>LIRC mode, While(1) loop in flash all peripheral<br>clock disable, 4 MHz core / 1 MHz flash, V <sub>DD</sub> =<br>3.0 V<br>• at 25 °C                          |      | 212   | 318    | μA   |       |

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current—8 MHz<br>LIRC mode, While(1) loop in flash all peripheral<br>clock enable, 4 MHz core / 1 MHz flash, V <sub>DD</sub> =<br>3.0 V<br>• at 25 °C                            | _    | 302   | 392.6  | μA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 48 MHz<br>system/24 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V<br>• at 25 °C | _    | 1.81  | 2.12   | mA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 24 MHz<br>system/12 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V<br>• at 25 °C | _    | 1.27  | 1.46   | mA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core<br>disabled, 4 MHz system/ 1 MHz bus and flash,<br>all peripheral clocks disabled, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                                          | _    | 156   | 193.2  | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core<br>disabled, 2 MHz system/ 0.5 MHz bus and<br>flash, all peripheral clocks disabled, V <sub>DD</sub> = 3.0<br>V<br>• at 25 °C                                     | _    | 63    | 100.8  | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core<br>disabled, 125 kHz system/ 31.25 kHz bus and<br>flash, all peripheral clocks disabled, V <sub>DD</sub> = 3.0<br>V<br>• at 25 °C                                 | _    | 32    | 48     | μA   |       |

| IDD_PSTOP2             | Partial Stop 2, core and system clock disabled,<br>12 MHz bus and flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                                                                                           |      | 1.68  | 2.05   | mA   |       |

| I <sub>DD_PSTOP2</sub> | Partial Stop 2, core and system clock disabled,<br>flash doze enabled, 12 MHz bus, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                                                                                 |      | 1.05  | 1.26   | mA   |       |

| I <sub>DD_STOP</sub>   | Stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                                                       |      | 158.1 | 175.81 |      |       |

|                        | • at 50 °C                                                                                                                                                                                               | _    | 171   | 180.24 |      |       |

|                        | • at 85 °C                                                                                                                                                                                               | —    | 203.8 | 228.64 | μA   |       |

| L                      | • at 105 °C                                                                                                                                                                                              |      | 251.7 | 300.06 |      |       |

| Table 38. Power consumption operating behaviors (contin |

|---------------------------------------------------------|

|---------------------------------------------------------|

Table continues on the next page...

**Electrical characteristics**

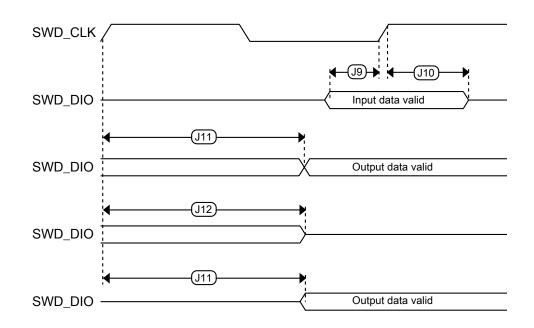

Figure 23. Serial wire data timing

### 5.3.2 System modules

There are no specifications necessary for the device's system modules.

### 5.3.3 Clock modules

#### 5.3.3.1 MCG-Lite specifications Table 46. IRC48M specifications

| Symbol                     | Description                                                                                     | Min. | Тур.  | Max.  | Unit                 | Notes |

|----------------------------|-------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| I <sub>DD48M</sub>         | Supply current                                                                                  | —    | 400   | 500   | μA                   |       |

| f <sub>irc48m</sub>        | Internal reference frequency                                                                    | _    | 48    | _     | MHz                  |       |

| Δf <sub>irc48m_ol_lv</sub> | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over temperature | _    | ± 0.5 | ± 1.5 | %f <sub>irc48m</sub> |       |

| Δf <sub>irc48m_ol_hv</sub> | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over temperature | _    | ± 0.5 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

| J <sub>cyc_irc48m</sub>    | Period Jitter (RMS)                                                                             | _    | 35    | 150   | ps                   |       |

| t <sub>irc48mst</sub>      | Startup time                                                                                    |      | 2     | 3     | μs                   | 2     |

#### 5.3.6.2 CMP and 6-bit DAC electrical specifications Table 59. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | _                     | _    | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      |                       |      | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | $V_{SS} - 0.3$        | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         |                       | _    | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | —                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | —                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | —                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      | _               | V                |

| V <sub>CMPOI</sub> | Output low                                          |                       | _    | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> |                       |      | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   |                       | 7    | —               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  |      | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  | _    | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to V\_{DD}-0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB = V<sub>reference</sub>/64

**Electrical characteristics**

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | —                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | _                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      | —                        | ns                  | —    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | —                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

#### Table 62. SPI slave mode timing on slew rate disabled pads (continued)

1. For SPI0  $f_{periph}$  is the bus clock (f\_{BUS}). For SPI1  $f_{periph}$  is the system clock (f\_{SYS}).

2.  $t_{periph} = 1/f_{periph}$

3. Time to data active from high-impedance state

4. Hold time to high-impedance state

#### Table 63. SPI slave mode timing on slew rate enabled pads

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | —                        | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> |      |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> |      |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | _                        | ns                  | _    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2                        | _                        | ns                  | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 7                        | _                        | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | _                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | _                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                        | 122                      | ns                  | _    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | _    |

| 12   | t <sub>RI</sub>     | Rise time input                | _                        | t <sub>periph</sub> - 25 | ns                  | _    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | _                        | 36                       | ns                  |      |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

2.  $t_{periph} = 1/f_{periph}$

88

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

## 6.1 Hardware design considerations

This device contains protective circuitry to guard against damage due to high static voltage or electric fields. However, take normal precautions to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit.

## 6.1.1 Printed circuit board recommendations

- Place connectors or cables on one edge of the board and do not place digital circuits between connectors.

- Drivers and filters for I/O functions must be placed as close to the connectors as possible. Connect TVS devices at the connector to a good ground. Connect filter capacitors at the connector to a good ground.

- Physically isolate analog circuits from digital circuits if possible.

- Place input filter capacitors as close to the MCU as possible.

- For best EMC performance, route signals as transmission lines; use a ground plane directly under LQFP packages; and solder the exposed pad (EP) to ground directly under QFN packages.

### 6.1.2 Power delivery system

Consider the following items in the power delivery system:

- Use a plane for ground.

- Use a plane for MCU VDD supply if possible.

- Always route ground first, as a plane or continuous surface, and never as sequential segments.

- Route power next, as a plane or traces that are parallel to ground traces.

- Place bulk capacitance,  $10 \,\mu\text{F}$  or more, at the entrance of the power plane.

- Place bypass capacitors for MCU power domain as close as possible to each VDD/VSS pair, including VDDA/VSSA and VREFH/VREFL.

- The minimum bypass requirement is to place  $0.1 \,\mu\text{F}$  capacitors positioned as near as possible to the package supply pins.

- Take special care to minimize noise levels on the VREFH/VREFL inputs. An option is to use the internal reference voltage (output 1.2 V typically) as the ADC reference.

#### NOTE

The internal reference voltage output (VREFO) is bonded to the VREFH pin on some packages and to PTE30 on other packages. When the VREFO output is used, a 0.1  $\mu$ F capacitor

is required as a filter. Do not connect any other supply voltage to the pin that has VREFO activated.

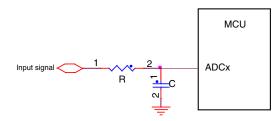

## 6.1.3 Analog design

Each ADC input must have an RC filter as shown in the following figure. The maximum value of R must be RAS max if fast sampling and high resolution are required. The value of C must be chosen to ensure that the RC time constant is very small compared to the sample period.

Figure 34. RC circuit for ADC input

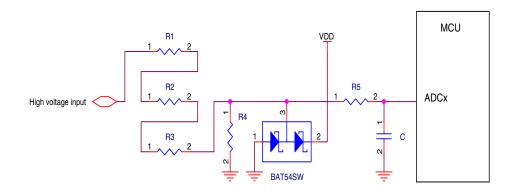

High voltage measurement circuits require voltage division, current limiting, and over-voltage protection as shown the following figure. The voltage divider formed by R1 - R4 must yield a voltage less than or equal to VREFH. The current must be limited to less than the injection current limit. Since the ADC pins do not have diodes to VDD, external clamp diodes must be included to protect against transient over-voltages.

Figure 35. High voltage measurement with an ADC input

Design considerations

## 6.1.4 Digital design

Ensure that all I/O pins cannot get pulled above VDD (Max I/O is VDD+0.3V).

## CAUTION

Do not provide power to I/O pins prior to VDD, especially the RESET\_b pin.

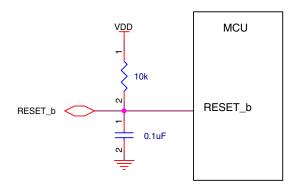

• RESET\_b pin

The RESET\_b pin is an open-drain I/O pin that has an internal pullup resistor. An external RC circuit is recommended to filter noise as shown in the following figure. The resistor value must be in the range of 4.7 k $\Omega$  to 10 k $\Omega$ ; the recommended capacitance value is 0.1  $\mu$ F. The RESET\_b pin also has a selectable digital filter to reject spurious noise.

Figure 36. Reset circuit

When an external supervisor chip is connected to the RESET\_b pin, a series resistor must be used to avoid damaging the supervisor chip or the RESET\_b pin, as shown in the following figure. The series resistor value (RS below) must be in the range of  $100 \Omega$  to  $1 \text{ k}\Omega$  depending on the external reset chip drive strength. The supervisor chip must have an active high, open-drain output.

| Field | Description    | Values                                                         |

|-------|----------------|----------------------------------------------------------------|

| Ν     | Packaging type | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul> |

#### Table 67. Part number fields description (continued)

1. This package for this product is not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

## 7.4 Example

This is an example part number:

MKL17Z64VLH4

# 8 Revision history

The following table provides a revision history for this document.

| Rev. No. | Date                | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 28 January/<br>2015 | <ul> <li>Initial public release</li> <li>Updated the features and completed the ordering information.</li> <li>Updated Table 9 - Power consumption operating behaviors with Max. values.</li> <li>Added a note before Table 9.</li> <li>Updated Table 17 - IRC48M specifications.</li> <li>Updated Table 28. VREF full-range (-40 – 105 °C) operating behaviors with Min., Max., and Typical values.</li> <li>Added Table 36 - I<sup>2</sup>C 1Mbit/s timing.</li> </ul>                                                                                                    |

| 4.1      | 2 February/<br>2015 | <ul><li>Moved the ordering information out of the front page to be a separate chapter.</li><li>Added Module signal description table and Package dimension sections.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                              |

| 5        | 21 April/2015       | <ul> <li>32-pin QFN package is now standard part, added Marking information and thermal attributes of this package</li> <li>Added Overview chapter</li> <li>Added Memory map chapter</li> <li>Added Pin properties</li> <li>Added a note to the t<sub>rd1all</sub> in Flash timing specifications — commands</li> <li>Added a note to the Maximum of f<sub>SCL</sub> in the fast mode in Inter-Integrated Circuit Interface (I2C) timing</li> <li>Added a footnote to the Δfirc48m_ol_hv in MCG-Lite specifications</li> <li>Added Design considerations chapter</li> </ul> |

Table 68. Revision history