#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART                            |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                      |

| Number of I/O              | 54                                                                   |

| Program Memory Size        | 64KB (64K × 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | - ·                                                                  |

| RAM Size                   | 16K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

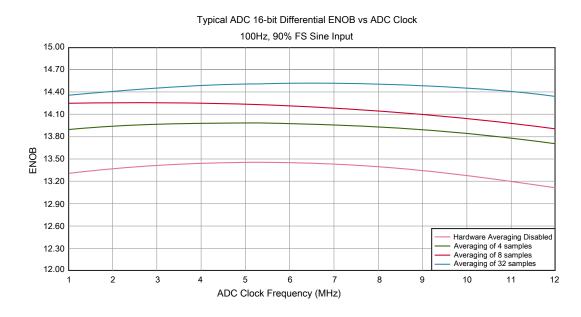

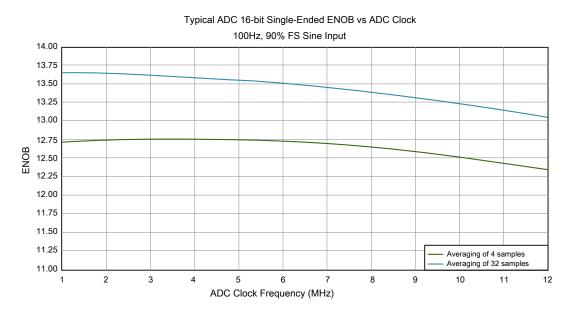

| Data Converters            | A/D 20x16b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl17z64vlh4 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Wake-up source    | Description                                                                 |

|-------------------|-----------------------------------------------------------------------------|

| l <sup>2</sup> Cx | Address match wakeup                                                        |

| LPUART0 , LPUART1 | Any enabled interrupt can be a source as long as the module remains clocked |

| UART2             | Active edge on RXD                                                          |

| RTC               | Alarm or seconds interrupt                                                  |

| NMI               | NMI pin                                                                     |

| ТРМх              | Any enabled interrupt can be a source as long as the module remains clocked |

| LPTMR             | Any enabled interrupt can be a source as long as the module remains clocked |

| SPIx              | Slave mode interrupt                                                        |

| FlexIO            | Any enabled interrupt can be a source as long as the module remains clocked |

#### Table 2. AWIC stop wake-up sources (continued)

## 2.1.4 Memory

This device has the following features:

- 8/16 KB of embedded RAM accessible (read/write) at CPU clock speed with 0 wait states.

- The non-volatile memory is divided into two arrays

- 32/64 KB of embedded program memory

- 16 KB ROM (built-in bootloader to support UART, I2C, and SPI interfaces)

The program flash memory contains a 16-byte flash configuration field that stores default protection settings and security information. The page size of program flash is 1 KB.

The protection setting can protect 32 regions of the program flash memory from unintended erase or program operations.

The security circuitry prevents unauthorized access to RAM or flash contents from debug port.

• System register file

This device contains a 32-byte register file that is powered in all power modes.

Also, it retains contents during low power modes and is reset only during a power-on reset.

7

## 2.1.5 Reset and boot

The following table lists all the reset sources supported by this device.

## NOTE

In the following table, Y means the specific module, except for the registers, bits or conditions mentioned in the footnote, is reset by the corresponding Reset source. N means the specific module is not reset by the corresponding Reset source.

| Reset         | Descriptions                                           | Modules        |                |                |                |      |                            |     |       |        |

|---------------|--------------------------------------------------------|----------------|----------------|----------------|----------------|------|----------------------------|-----|-------|--------|

| sources       |                                                        | PMC            | SIM            | SMC            | RCM            | LLWU | Reset pin<br>is<br>negated | RTC | LPTMR | Others |

| POR reset     | Power-on reset (POR)                                   | Y              | Y              | Y              | Y              | Y    | Y                          | Y   | Y     | Y      |

| System resets | Low-voltage detect (LVD)                               | Y <sup>1</sup> | Y              | Y              | Y              | Y    | Y                          | Ν   | Y     | Y      |

|               | Low leakage wakeup<br>(LLWU) reset                     | N              | Y <sup>2</sup> | N              | Y              | Ν    | Y <sup>3</sup>             | Ν   | N     | Y      |

|               | External pin reset<br>(RESET)                          | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y              | Y    | Y                          | Ν   | N     | Y      |

|               | Computer operating<br>properly (COP) watchdog<br>reset | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Υ <sup>5</sup> | Y    | Y                          | Ν   | N     | Y      |

|               | Stop mode acknowledge<br>error (SACKERR)               | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | N     | Y      |

|               | Software reset (SW)                                    | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | N     | Y      |

|               | Lockup reset (LOCKUP)                                  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | N     | Y      |

|               | MDM DAP system reset                                   | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | N     | Y      |

| Debug reset   | Debug reset                                            | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | N     | Y      |

### Table 3. Reset source

1. Except PMC\_LVDSC1[LVDV] and PMC\_LVDSC2[LVWV]

2. Except SIM\_SOPT1

3. Only if RESET is used to wake from VLLS mode.

4. Except SMC\_PMCTRL, SMC\_STOPCTRL, SMC\_PMSTAT

5. Except RCM\_RPFC, RCM\_RPFW, RCM\_FM

The CM0+ core adds support for a programmable Vector Table Offset Register (VTOR) to relocate the exception vector table after reset. This device supports booting from:

- internal flash

- boot ROM

8

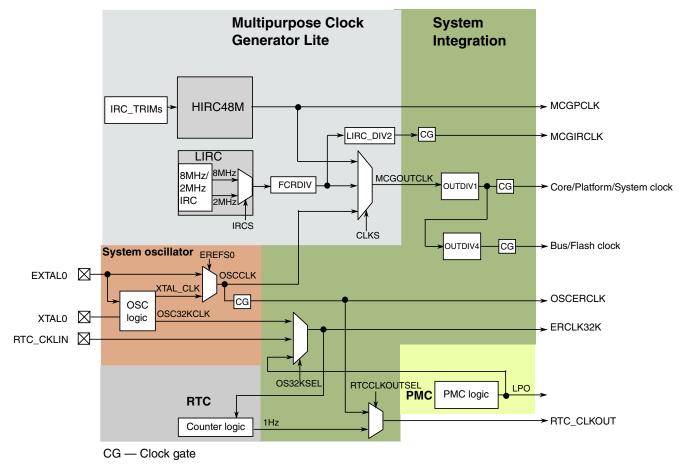

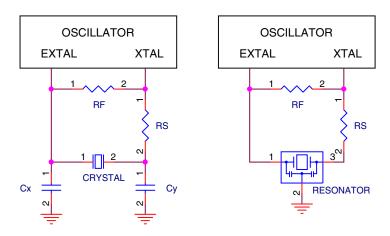

The system oscillator supports low frequency crystals (32 kHz to 40 kHz), high frequency crystals (1 MHz to 32 MHz), and ceramic resonators (1 MHz to 32 MHz). An external clock source, DC to 48 MHz, can be used as the system clock through the EXTAL0 pin. The external oscillator also supports a low speed external clock (32.768 kHz) on the RTC\_CLKIN pin for use with the RTC.

For more details on the clock operations and configurations, see Reference Manual.

The following figure is a high level block diagram of the clock generation.

Figure 3. Clock block diagram

In order to provide flexibility, many peripherals can select from multiple clock sources for operation. This enables the peripheral to select a clock that will always be available during operation in various operational modes.

The following table summarizes the clocks associated with each module.

The PMC provides Run (Run), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS), Low Leakage Stop (LLS), and Very Low Leakage Stop (VLLS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC), and the Low Leakage Wake-Up Controller (LLWU) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes. The LLWU is used to wake up the MCU core from LLS and VLLSx modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, or the LLWU, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                        |  |  |  |  |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                    |  |  |  |  |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                             |  |  |  |  |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                       |  |  |  |  |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode. |  |  |  |  |

Table 6. Peripherals states in different operational modes

Table continues on the next page ...

- 16-bit prescaler with compensation that can correct errors between 0.12 ppm and 3906 ppm

- Register write protection with register lock mechanism

- 1 Hz square wave or second pulse output with optional interrupt

## 2.2.8 PIT

The Periodic Interrupt Timer (PIT) is used to generate periodic interrupt to the CPU. It has two independent channels and each channel has a 32-bit counter. Both channels can be chained together to form a 64-bit counter.

Channel 0 can be used to periodically trigger DMA channel 0, and channel 1 can be used to periodically trigger DMA channel 1. Either channel can be programmed as an ADC trigger source, or TPM trigger source. Channel 0 can be programmed to trigger DAC.

The PIT module has the following features:

- Each 32-bit timers is able to generate DMA trigger

- Each 32-bit timers is able to generate timeout interrupts

- Two timers can be cascaded to form a 64-bit timer

- Each timer can be programmed as ADC/TPM trigger source

- Timer 0 is able to trigger DAC

# 2.2.9 LPTMR

The low-power timer (LPTMR) can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter, across all power modes, including the low-leakage modes. It can also continue operating through most system reset events, allowing it to be used as a time of day counter.

The LPTMR module has the following features:

- 16-bit time counter or pulse counter with compare

- Optional interrupt can generate asynchronous wakeup from any low-power mode

- Hardware trigger output

- Counter supports free-running mode or reset on compare

- Configurable clock source for prescaler/glitch filter

- Configurable input source for pulse counter

# 2.2.10 CRC

This device contains one cyclic redundancy check (CRC) module which can generate 16/32-bit CRC code for error detection.

The CRC module provides a programmable polynomial, WAS, and other parameters required to implement a 16-bit or 32-bit CRC standard.

The CRC module has the following features:

- Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift register

- Programmable initial seed value and polynomial

- Option to transpose input data or output data (the CRC result) bitwise or bytewise.

- Option for inversion of final CRC result

- 32-bit CPU register programming interface

## 2.2.11 UART

This device contains a basic universal asynchronous receiver/transmitter (UART) module with DMA function supported. Generally, this module is used in RS-232, RS-485, and other communications and supports LIN slave operation and ISO7816.

The UART module has the following features:

- Full-duplex operation

- 13-bit baud rate selection with /32 fractional divide, based on the module clock frequency

- Programmable 8-bit or 9-bit data format

- Programmable transmitter output polarity

- Programmable receive input polarity

- Up to 14-bit break character transmission.

- 11-bit break character detection option

- Two receiver wakeup methods with idle line or address mark wakeup

- Address match feature in the receiver to reduce address mark wakeup ISR overhead

- Ability to select MSB or LSB to be first bit on wire

- Support for ISO 7816 protocol to interface with SIM cards and smart cards

- Receiver framing error detection

- Hardware parity generation and checking

- 1/16 bit-time noise detection

- DMA interface

# 2.2.12 LPUART

This product contains two Low-Power UART modules, both of their clock sources are selectable from IRC48M, IRC8M/2M or external crystal clock, and can work in Stop and VLPS modes. They also support  $4 \times$  to  $32 \times$  data oversampling rate to meet different applications.

The LPUART module has the following features:

- Programmable baud rates (13-bit modulo divider) with configurable oversampling ratio from  $4 \times$  to  $32 \times$

- Transmit and receive baud rate can operate asynchronous to the bus clock and can be configured independently of the bus clock frequency, support operation in Stop mode

- Interrupt, DMA or polled operation

- Hardware parity generation and checking

- Programmable 8-bit, 9-bit or 10-bit character length

- Programmable 1-bit or 2-bit stop bits

- Three receiver wakeup methods

- Idle line wakeup

- Address mark wakeup

- Receive data match

- Automatic address matching to reduce ISR overhead:

- Address mark matching

- Idle line address matching

- Address match start, address match end

- Optional 13-bit break character generation / 11-bit break character detection

- Configurable idle length detection supporting 1, 2, 4, 8, 16, 32, 64 or 128 idle characters

- Selectable transmitter output and receiver input polarity

# 2.2.13 SPI

This device contains two SPI modules. SPI modules support 8-bit and 16-bit modes. FIFO function is available only on SPI1 module.

The SPI modules have the following features:

#### Pinouts

| 64<br>LQFP | 36<br>XFB<br>GA | 32<br>QFN | 48<br>QFN | 64<br>MAP<br>BGA | Pin Name         | Default                        | ALT0                           | ALT1             | ALT2           | ALT3           | ALT4           | ALT5           | ALT6            | ALT7    |

|------------|-----------------|-----------|-----------|------------------|------------------|--------------------------------|--------------------------------|------------------|----------------|----------------|----------------|----------------|-----------------|---------|

|            |                 |           |           |                  |                  | ADC0_<br>SE4a                  | ADC0_<br>SE4a                  |                  |                |                |                |                |                 |         |

| 11         | E1              | _         | -         | G2               | PTE22            | ADC0_DP3/<br>ADC0_SE3          | ADC0_DP3/<br>ADC0_SE3          | PTE22            |                | TPM2_CH0       | UART2_TX       |                | FXIO0_D6        |         |

| 12         | F1              | _         | -         | F2               | PTE23            | ADC0_<br>DM3/<br>ADC0_<br>SE7a | ADC0_<br>DM3/<br>ADC0_<br>SE7a | PTE23            |                | TPM2_CH1       | UART2_RX       |                | FXIO0_D7        |         |

| 13         | D3              | 7         | 9         | F4               | VDDA             | VDDA                           | VDDA                           |                  |                |                |                |                |                 |         |

| 14         | D3              | 7         | 10        | G4               | VREFH            | VREFH                          | VREFH                          |                  |                |                |                |                |                 |         |

| 14         | _               | _         | 10        | G4               | VREFO            | VREFO_A                        | VREFO_A                        |                  |                |                |                |                |                 |         |

| 15         | D4              | 8         | 11        | G3               | VREFL            | VREFL                          | VREFL                          |                  |                |                |                |                |                 |         |

| 16         | D4              | 8         | 12        | F3               | VSSA             | VSSA                           | VSSA                           |                  |                |                |                |                |                 |         |

| 17         | -               | -         | 13        | H1               | PTE29            | CMP0_IN5/<br>ADC0_<br>SE4b     | CMP0_IN5/<br>ADC0_<br>SE4b     | PTE29            |                | TPM0_CH2       | TPM_<br>Clkino |                |                 |         |

| 18         | F2              | 9         | 14        | H2               | PTE30            | ADC0_<br>SE23/<br>CMP0_IN4     | ADC0_<br>SE23/<br>CMP0_IN4     | PTE30            |                | TPM0_CH3       | TPM_<br>Clkin1 | LPUART1_<br>TX | LPTMR0_<br>ALT1 |         |

| 19         | _               | _         | _         | H3               | PTE31            | DISABLED                       |                                | PTE31            |                | TPM0_CH4       |                |                |                 |         |

| 20         | _               | _         | 15        | H4               | PTE24            | DISABLED                       |                                | PTE24            |                | TPM0_CH0       |                | I2C0_SCL       |                 |         |

| 21         | _               | _         | 16        | H5               | PTE25            | DISABLED                       |                                | PTE25            |                | TPM0_CH1       |                | I2C0_SDA       |                 |         |

| 22         | F3              | 10        | 17        | D3               | PTA0             | SWD_CLK                        |                                | PTA0             |                | TPM0_CH5       |                |                |                 | SWD_CLK |

| 23         | F4              | 11        | 18        | D4               | PTA1             | DISABLED                       |                                | PTA1             | LPUART0_<br>RX | TPM2_CH0       |                |                |                 |         |

| 24         | E4              | 12        | 19        | E5               | PTA2             | DISABLED                       |                                | PTA2             | LPUART0_<br>TX | TPM2_CH1       |                |                |                 |         |

| 25         | E5              | 13        | 20        | D5               | PTA3             | SWD_DIO                        |                                | PTA3             | I2C1_SCL       | TPM0_CH0       |                |                |                 | SWD_DIO |

| 26         | F5              | 14        | 21        | G5               | PTA4             | NMI_b                          |                                | PTA4             | I2C1_SDA       | TPM0_CH1       |                |                |                 | NMI_b   |

| 27         | _               | _         | _         | F5               | PTA5             | DISABLED                       |                                | PTA5             |                | TPM0_CH2       |                |                |                 |         |

| 28         | _               | _         | _         | H6               | PTA12            | DISABLED                       |                                | PTA12            |                | TPM1_CH0       |                |                |                 |         |

| 29         | _               | _         | _         | G6               | PTA13            | DISABLED                       |                                | PTA13            |                | TPM1_CH1       |                |                |                 |         |

| 30         | C3              | 15        | 22        | G7               | VDD              | VDD                            | VDD                            |                  |                |                |                |                |                 |         |

| 31         | C4              | 16        | 23        | H7               | VSS              | VSS                            | VSS                            |                  |                |                |                |                |                 |         |

| 32         | F6              | 17        | 24        | H8               | PTA18            | EXTAL0                         | EXTAL0                         | PTA18            |                | LPUART1_<br>RX | TPM_<br>CLKIN0 |                |                 |         |

| 33         | E6              | 18        | 25        | G8               | PTA19            | XTALO                          | XTAL0                          | PTA19            |                | LPUART1_<br>TX | TPM_<br>CLKIN1 |                | LPTMR0_<br>ALT1 |         |

| 34         | D5              | 19        | 26        | F8               | PTA20            | RESET_b                        |                                | PTA20            |                |                |                |                |                 | RESET_b |

| 35         | D6              | 20        | 27        | F7               | PTB0/<br>LLWU_P5 | ADC0_SE8                       | ADC0_SE8                       | PTB0/<br>LLWU_P5 | I2C0_SCL       | TPM1_CH0       | SPI1_MOSI      | SPI1_MISO      |                 |         |

| 36         | C6              | 21        | 28        | F6               | PTB1             | ADC0_SE9                       | ADC0_SE9                       | PTB1             | I2C0_SDA       | TPM1_CH1       | SPI1_MISO      | SPI1_MOSI      |                 |         |

| 64 LQFP | 36<br>XFBGA | 32 QFN | 48 QFN | 64 MAPBGA | Pin name          | Driver strength | Default status after POR | Pullup/ pulldown setting after POR | Slew rate after POR | Passive pin filter after POR | Open drain | Pin interrupt |

|---------|-------------|--------|--------|-----------|-------------------|-----------------|--------------------------|------------------------------------|---------------------|------------------------------|------------|---------------|

| 46      | B5          | 24     | 36     | C8        | PTC3/<br>LLWU_P7  | HD              | Hi-Z                     | _                                  | FS                  | N                            | N          | Y             |

| 47      | —           | —      | —      | E3        | VSS               | _               | —                        | —                                  | —                   | —                            | —          | —             |

| 48      | —           | —      | —      | E4        | VDD               | —               | —                        | —                                  | —                   |                              | —          | —             |

| 49      | A6          | 25     | 37     | B8        | PTC4/<br>LLWU_P8  | HD              | Hi-Z                     | _                                  | FS                  | N                            | N          | Y             |

| 50      | A5          | 26     | 38     | A8        | PTC5/<br>LLWU_P9  | ND              | Hi-Z                     | _                                  | FS                  | N                            | N          | Y             |

| 51      | B4          | 27     | 39     | A7        | PTC6/<br>LLWU_P10 | ND              | Hi-Z                     | _                                  | FS                  | N                            | N          | Y             |

| 52      | A4          | 28     | 40     | B6        | PTC7              | ND              | Hi-Z                     |                                    | FS                  | N                            | N          | Y             |

| 53      | —           | —      | —      | A6        | PTC8              | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 54      | —           | —      | —      | B5        | PTC9              | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 55      | —           | —      | —      | B4        | PTC10             | ND              | Hi-Z                     |                                    | SS                  | N                            | N          | Y             |

| 56      | —           | —      | —      | A5        | PTC11             | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 57      | —           | —      | 41     | C3        | PTD0              | ND              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| 58      | —           | _      | 42     | A4        | PTD1              | ND              | Hi-Z                     | _                                  | FS                  | N                            | N          | Y             |

| 59      | _           |        | 43     | C2        | PTD2              | ND              | Hi-Z                     | _                                  | FS                  | N                            | Ν          | Y             |

| 60      | —           | _      | 44     | B3        | PTD3              | ND              | Hi-Z                     | _                                  | FS                  | N                            | N          | Y             |

| 61      | A3          | 29     | 45     | A3        | PTD4/<br>LLWU_P14 | ND              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| 62      | B3          | 30     | 46     | C1        | PTD5              | ND              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| 63      | B2          | 31     | 47     | B2        | PTD6/<br>LLWU_P15 | HD              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| 64      | A2          | 32     | 48     | A2        | PTD7              | HD              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| Properties               | Abbreviation | Descriptions    |

|--------------------------|--------------|-----------------|

| Driver strength          | ND           | Normal drive    |

|                          | HD           | High drive      |

| Default status after POR | Hi-Z         | High impendence |

Table continues on the next page...

|   | 1     | 2                 | 3                 | 4                 | 5                              | 6                |   |

|---|-------|-------------------|-------------------|-------------------|--------------------------------|------------------|---|

| A | PTE0  | PTD7              | PTD4/<br>LLWU_P14 | PTC7              | PTC5/<br>LLWU_P9               | PTC4/<br>LLWU_P8 | A |

| В | PTE1  | PTD6/<br>LLWU_P15 | PTD5              | PTC6/<br>LLWU_P10 | PTC3/<br>LLWU_P7               | PTC2             | в |

| с | PTE17 | PTE16             | VDD               | VSS               | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | PTB1             | С |

| D | PTE18 | PTE19             | VDDA/<br>VREFH    | VREFL/<br>VSSA    | PTA20                          | PTB0/<br>LLWU_P5 | D |

| E | PTE22 | PTE21             | PTE20             | PTA2              | PTA3                           | PTA19            | E |

| F | PTE23 | VREF0/<br>PTE30   | PTA0              | PTA1              | PTA4                           | PTA18            | F |

|   | 1     | 2                 | 3                 | 4                 | 5                              | 6                |   |

Figure 10. 36 XFBGA Pinout diagram (transparent top view)

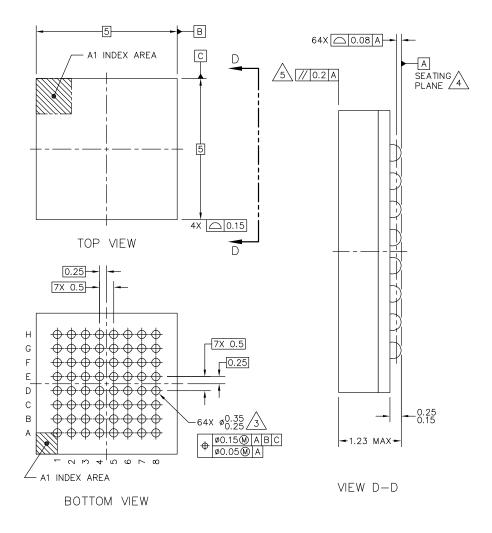

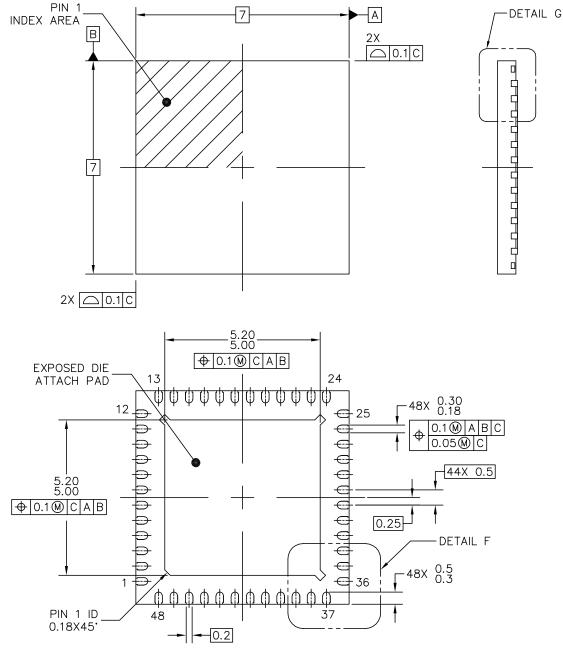

## 4.5 Package dimensions

The following figures show the dimensions of the package options for the devices supported by this document.

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

/3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

4. DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

### Figure 13. 64-pin MAPBGA package dimension

#### Pinouts

### 5.2.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent the characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

### NOTE

The while(1) test is executed with flash cache enabled.

| Symbol                | Description                                                                                                                                     | Min. | Тур. | Max.     | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>      | Analog supply current                                                                                                                           | _    |      | See note | mA   | 1     |

| I <sub>DD_RUNCO</sub> | Running CoreMark in flash in compute<br>operation mode—48M HIRC mode, 48 MHz<br>core / 24 MHz flash, V <sub>DD</sub> = 3.0 V                    |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | —    | 4.79 | 4.98     | mA   |       |

|                       | • at 105 °C                                                                                                                                     |      | 4.94 | 5.14     |      |       |

| I <sub>DD_RUNCO</sub> | Running While(1) loop in flash in compute<br>operation mode—48M HIRC mode, 48 MHz<br>core / 24 MHz flash, V <sub>DD</sub> = 3.0 V               |      |      |          |      |       |

|                       | • at 25 °C                                                                                                                                      | —    | 2.73 | 2.87     | mA   |       |

|                       | • at 105 °C                                                                                                                                     |      | 2.9  | 3.05     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable<br>48 MHz core/24 MHz flash, $V_{DD} = 3.0 V$         |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | —    | 5.45 | 5.67     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | —    | 5.6  | 5.82     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in flash all peripheral clock disable,<br>24 MHz core/12 MHz flash, V <sub>DD</sub> = 3.0 V |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      |      |      |          |      |       |

|                       | • at 105 °C                                                                                                                                     | —    | 3.41 | 3.55     | mA   |       |

|                       |                                                                                                                                                 | —    | 3.56 | 3.70     | mA   |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable<br>12 MHz core/6 MHz flash, $V_{DD} = 3.0 \text{ V}$  |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | —    | 2.37 | 2.49     | mA   |       |

|                       | • at 105 °C                                                                                                                                     |      | 2.52 | 2.65     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock enable<br>48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V   |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | —    | 7.05 | 7.33     | mA   |       |

|                       | • at 105 °C                                                                                                                                     |      | 7.2  | 7.49     |      |       |

| Table 38. | Power of | consumption | operating | behaviors |

|-----------|----------|-------------|-----------|-----------|

|-----------|----------|-------------|-----------|-----------|

Table continues on the next page...

## 5.2.3.2 General switching specifications

These general-purpose specifications apply to all signals configured for GPIO and UART signals.

| Description                                                                           | Min. | Max. | Unit                | Notes |

|---------------------------------------------------------------------------------------|------|------|---------------------|-------|

| GPIO pin interrupt pulse width (digital glitch filter disabled)<br>— Synchronous path | 1.5  | —    | Bus clock<br>cycles | 1     |

| External RESET and NMI pin interrupt pulse width — Asynchronous path                  | 100  | _    | ns                  | 2     |

| GPIO pin interrupt pulse width — Asynchronous path                                    | 16   | _    | ns                  | 2     |

| Port rise and fall time                                                               |      | 36   | ns                  | 3     |

#### Table 42. General switching specifications

1. The synchronous and asynchronous timing must be met.

2. This is the shortest pulse that is guaranteed to be recognized.

3. 75 pF load

## 5.2.4 Thermal specifications

#### 5.2.4.1 Thermal operating requirements Table 43. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed the maximum. The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\theta JA} \times chip$  power dissipation.

### 5.2.4.2 Thermal attributes

### NOTE

The 48 QFN and 64 MAPBGA packages for this product are not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/ KPYW for more details.

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |  |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|--|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | _    | 40   | kHz  |       |  |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency —<br>high-frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |  |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency —<br>high frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |  |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | _    | —    | 48   | MHz  | 1, 2  |  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |  |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | —    | 750  | _    | ms   | 3, 4  |  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | _    | 250  | _    | ms   |       |  |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |  |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |  |

### 5.3.3.2.2 Oscillator frequency specifications Table 49. Oscillator frequency specifications

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

3. Proper PC board layout procedures must be followed to achieve specifications.

4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

## 5.3.4 Memories and memory interfaces

### 5.3.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

### 5.3.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

**Electrical characteristics**

| Symbol                | Description                        | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>   | Longword Program high-voltage time | —    | 7.5  | 18   | μs   | —     |

| t <sub>hversscr</sub> | Sector Erase high-voltage time     | —    | 13   | 113  | ms   | 1     |

| t <sub>hversall</sub> | Erase All high-voltage time        | —    | 52   | 452  | ms   | 1     |

#### Table 50. NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

#### 5.3.4.1.2 Flash timing specifications — commands Table 51. Flash command timing specifications

| Symbol                | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|------|-------|

| t <sub>rd1sec1k</sub> | Read 1s Section execution time (flash sector) | _    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | _    | _    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | _    | 65   | 145  | μs   |       |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | _    | —    | 0.9  | ms   | 1     |

| t <sub>rdonce</sub>   | Read Once execution time                      | _    | —    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | _    | 65   | —    | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | _    | 70   | 575  | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | _    | —    | 30   | μs   | 1     |

| t <sub>ersallu</sub>  | Erase All Blocks Unsecure execution time      | _    | 70   | 575  | ms   | 2     |

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

### 5.3.4.1.3 Flash high voltage current behaviors Table 52. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation |      | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       | _    | 1.5  | 4.0  | mA   |

# 5.3.4.1.4 Reliability specifications

### Table 53. NVM reliability specifications

| Symbol        | Description | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |  |

|---------------|-------------|------|-------------------|------|------|-------|--|

| Program Flash |             |      |                   |      |      |       |  |

Table continues on the next page...

### 5.3.6.1.3 Voltage reference electrical specifications

| Symbol           | Description    | Min. | Max. | Unit | Notes |

|------------------|----------------|------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage |      | 3.6  | V    |       |

Table 56.

VREF full-range operating requirements

Table continues on the next page...

**Electrical characteristics**

1. If configured as an output.

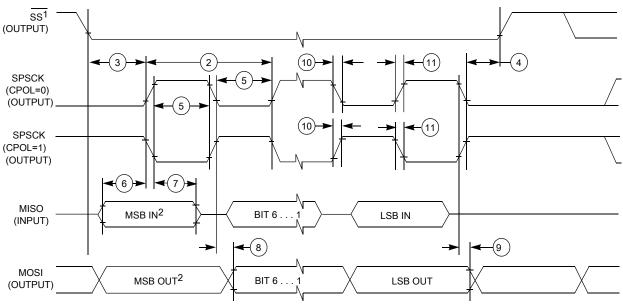

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 29. SPI master mode timing (CPHA = 0)

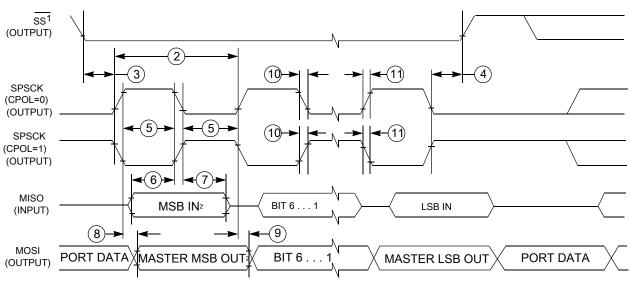

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 30. SPI master mode timing (CPHA = 1)

#### Table 62. SPI slave mode timing on slew rate disabled pads

| Num. | Symbol             | Description            | Min.                    | Max.                   | Unit                | Note |

|------|--------------------|------------------------|-------------------------|------------------------|---------------------|------|

| 1    | f <sub>op</sub>    | Frequency of operation | 0                       | f <sub>periph</sub> /4 | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub> | SPSCK period           | 4 x t <sub>periph</sub> | _                      | ns                  | 2    |

| 3    | t <sub>Lead</sub>  | Enable lead time       | 1                       |                        | t <sub>periph</sub> | —    |

Table continues on the next page ...

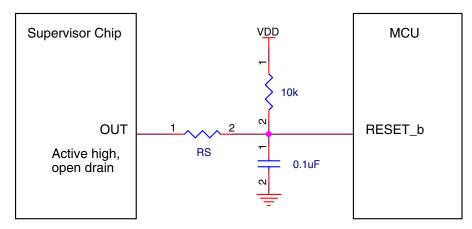

Figure 37. Reset signal connection to external reset chip

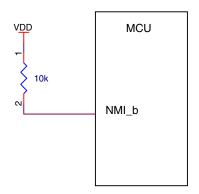

### • NMI pin

Do not add a pull-down resistor or capacitor on the NMI\_b pin, because a low level on this pin will trigger non-maskable interrupt. When this pin is enabled as the NMI function, an external pull-up resistor (10 k $\Omega$ ) as shown in the following figure is recommended for robustness.

If the NMI\_b pin is used as an I/O pin, the non-maskable interrupt handler is required to disable the NMI function by remapping to another function. The NMI function is disabled by programming the FOPT[NMI\_DIS] bit to zero.

Figure 38. NMI pin biasing

• Debug interface

This MCU uses the standard ARM SWD interface protocol as shown in the following figure. While pull-up or pull-down resistors are not required (SWD\_DIO has an internal pull-up and SWD\_CLK has an internal pull-down), external 10 k $\Omega$  pull resistors are recommended for system robustness. The RESET\_b pin recommendations mentioned above must also be considered.

**Design considerations**

Figure 43. Crystal connection – Diagram 4

# 6.2 Software considerations

All Kinetis MCUs are supported by comprehensive Freescale and third-party hardware and software enablement solutions, which can reduce development costs and time to market. Featured software and tools are listed below. Visit http://www.freescale.com/kinetis/sw for more information and supporting collateral.

Evaluation and Prototyping Hardware

- Freescale Freedom Development Platform: http://www.freescale.com/freedom

- Tower System Development Platform: http://www.freescale.com/tower

IDEs for Kinetis MCUs

- Kinetis Design Studio IDE: http://www.freescale.com/kds

- Partner IDEs: http://www.freescale.com/kide

## Development Tools

- PEG Graphics Software: http://www.freescale.com/peg

- Processor Expert Software and Embedded Components: http://www.freescale.com/ processorexpert )

Run-time Software

- Kinetis SDK: http://www.freescale.com/ksdk

- Kinetis Bootloader: http://www.freescale.com/kboot

- ARM mbed Development Platform: http://www.freescale.com/mbed

- MQX RTOS: http://www.freescale.com/mqx