# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | SPI                                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 28-SO                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f260g1m6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.4 SYSTEM INTEGRITY MANAGEMENT (SI)

The System Integrity Management block contains group the Low voltage Detector (LVD) and Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

**Note:** A reset can also be triggered following the detection of an illegal opcode or prebyte code. Refer to Section 12.2.1 on page 123 for further details.

#### 6.4.1 Low Voltage Detector (LVD)

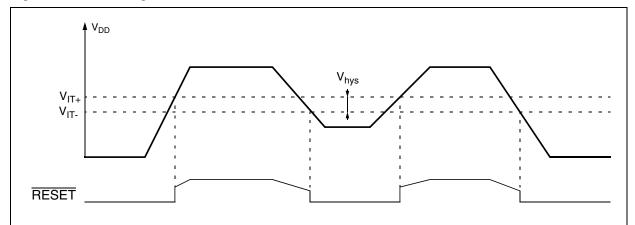

The Low Voltage Detector function (LVD) generates a static reset when the V<sub>DD</sub> supply voltage is below a V<sub>IT</sub>- reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The  $V_{IT-}$  reference value for a voltage drop is lower than the  $V_{IT+}$  reference value for power-on in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{\text{DD}}$  is below:

$-V_{IT+}$  when  $V_{DD}$  is rising

$-V_{IT}$  when  $V_{DD}$  is falling

The LVD function is illustrated in Figure 14.

The voltage threshold can be configured by option byte to be low, medium or high.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT-}$ , the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

The LVD allows the device to be used without any external RESET circuitry.

The LVD is an optional function which can be selected by option byte.

Use of LVD with capacitive power supply: with this type of power supply, if power cuts occur in the application, it is recommended to pull  $V_{DD}$  down to 0V to ensure optimum restart conditions. Refer to circuit example in Figure 91 on page 151 and note 6.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

#### Figure 14. Low Voltage Detector vs Reset

#### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

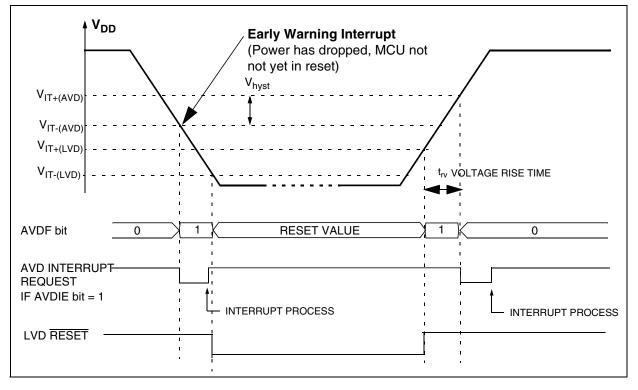

#### 6.4.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a V<sub>IT</sub> and V<sub>IT</sub> reference value and the V<sub>DD</sub> main supply. The V<sub>IT</sub> reference value for falling voltage is lower than the V<sub>IT</sub> reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (VDF) in the SICSR register. This bit is read only.

**Caution**: The AVD functions only if the LVD is enabled through the option byte.

#### 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see Section 15.1 on page 162).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{\text{IT+(AVD)}}$  or  $V_{\text{IT-(AVD)}}$  threshold (AVDF bit toggles).

#### Figure 15. Using the AVD to Monitor V<sub>DD</sub>

57/

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 15.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{\rm rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If t<sub>rv</sub> is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then 2 AVD interrupts will be received: the first when the AVDIE bit is set, and the second when the threshold is reached.

- If the AVD interrupt is enabled after the  $V_{\text{IT}+(\text{AVD})}$  threshold is reached then only one AVD interrupt will occur.

#### POWER SAVING MODES (Cont'd)

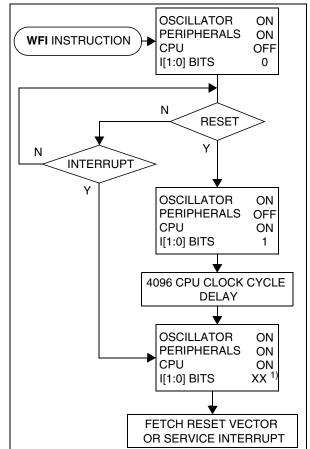

#### 8.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the "WFI" ST7 software instruction.

All peripherals remain active. During WAIT mode, the I [1:0] bits in the CC register are forced to '10b', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or Reset occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 22.

#### Note:

1. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set during the interrupt routine and cleared when the CC register is popped.

#### I/O PORTS (Cont'd)

#### Table 8. I/O Configurations

#### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- 2. When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

- 3. For true open drain, these elements are not implemented.

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 0024h             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### Table 12. Watchdog Timer Register Map and Reset Values

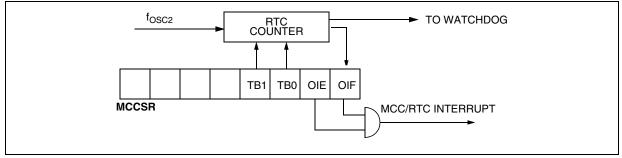

#### 11.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (MCC/RTC)

The Main Clock Controller consists of a real time clock timer with interrupt capability

#### 11.2.1 Real Time Clock Timer (RTC)

5/

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCC-SR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE-HALT mode when the HALT instruction is executed. See Section 8.4 "ACTIVE-HALT AND HALT MODES" on page 35 for more details.

#### Figure 34. Main Clock Controller (MCC/RTC) Block Diagram

#### 11.3.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are 2 output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OCIE bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### **Procedure:**

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 14 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCRi register and CR register:

- OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR2 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \operatorname{OC}_{iR} = \frac{\Delta t * f_{CPU}}{PRESC}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 14 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}$$

i R =  $\Delta t \star f_{\text{EXT}}$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (i.e. clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

#### 11.3.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are loaded in their respective shadow registers (double buffer) only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1). The shadow registers contain the reference values for comparison in PWM "double buffering" mode.

**Note:** There is a locking mechanism for transferring the OCiR value to the buffer. After a write to the OCiHR register, transfer of the new compare value to the buffer is inhibited until OCiLR is also written.

Unlike in Output Compare mode, the compare function is always enabled in PWM mode.

#### Procedure

To use pulse width modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1=0 and OLVL2=1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 14

#### Clock Control Bits). Pulse Width Modulation cycle When Counter = OC1R When Counter = OC2R OCMP1 = OLVL2 Counter is reset to FFFCh ICF1 bit is set

If OLVL1=1 and OLVL2=0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1=OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OCiR Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 14 Clock Control Bits)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 45)

#### Notes:

- 1. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 2. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

#### 11.3.7 Register Description

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

#### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = ICIE Input Capture Interrupt Enable.

0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.*

0: Interrupt is inhibited.

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

#### Bit 3 = FOLV1 Forced Output Compare 1.

This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

#### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

#### Bit 0 = **OLVL1** *Output Level 1.*

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

#### **Related Documentation**

AN 973: SCI software communications using 16bit timer

AN 974: Real Time Clock with ST7 Timer Output Compare

AN 976: Driving a buzzer through the ST7 Timer PWM function

AN1041: Using ST7 PWM signal to generate analog input (sinusoid)

AN1046: UART emulation software

AN1078: PWM duty cycle switch implementing true 0 or 100 per cent duty cycle

AN1504: Starting a PWM signal directly at high level using the ST7 16-Bit timer

#### SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.4.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the Device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the Device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

## 11.4.6.1 Using the SPI to wake-up the Device from Halt mode

In slave configuration, the SPI is able to wake-up the Device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

**Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake-up the Device from Halt mode only if the Slave Select signal (external

57/

SS pin or the SSI bit in the SPICSR register) is low when the Device enters Halt mode. So if Slave selection is configured as external (see Section 11.4.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

#### 11.4.7 Interrupts

| Interrupt Event                | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Trans-<br>fer Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode<br>Fault Event     | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                  | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 11.5.4.9 Clock Deviation Causes

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error (Local oscillator error of the transmitter or the transmitter is transmitting at a different baud rate).

- D<sub>QUANT</sub>: Error due to the baud rate quantisation of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete SCI message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the SCI clock tolerance:

$\mathsf{D}_{\mathsf{TRA}} + \mathsf{D}_{\mathsf{QUANT}} + \mathsf{D}_{\mathsf{REC}} + \mathsf{D}_{\mathsf{TCL}} < 3.75\%$

#### 11.5.4.10 Noise Error Causes

See also description of Noise error in Section 11.5.4.3.

#### Start bit

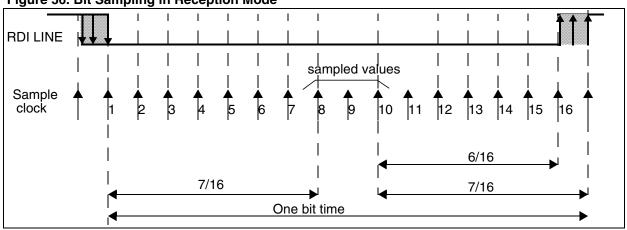

The noise flag (NF) is set during start bit reception if one of the following conditions occurs:

- 1. A valid falling edge is not detected. A falling edge is considered to be valid if the 3 consecutive samples before the falling edge occurs are detected as '1' and, after the falling edge occurs, during the sampling of the 16 samples, if one of the samples numbered 3, 5 or 7 is detected as a "1".

- 2. During sampling of the 16 samples, if one of the samples numbered 8, 9 or 10 is detected as a "1".

Therefore, a valid Start Bit must satisfy both the above conditions to prevent the Noise Flag getting set.

#### **Data Bits**

The noise flag (NF) is set during normal data bit reception if the following condition occurs:

During the sampling of 16 samples, if all three samples numbered 8, 9 and 10 are not the same. The majority of the 8th, 9th and 10th samples is considered as the bit value.

Therefore, a valid Data Bit must have samples 8, 9 and 10 at the same value to prevent the Noise Flag getting set.

#### Figure 56. Bit Sampling in Reception Mode

57/

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

#### Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

#### Bit 7 = R8 Receive data bit 8.

This bit is used to store the 9th bit of the received word when M=1.

#### Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M=1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit  $4 = \mathbf{M}$  Word length. This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

#### Bit 2 = **PCE** *Parity control enable.*

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M=1; 8th bit if M=0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

#### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity will be selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.

0: Parity error interrupt disabled

1: Parity error interrupt enabled.

#### I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### **11.6.4 Functional Description**

Refer to the CR, SR1 and SR2 registers in Section 11.6.7. for the bit definitions.

By default the I<sup>2</sup>C interface operates in Slave mode (M/SL bit is cleared) except when it initiates a transmit or receive sequence.

First the interface frequency must be configured using the FRi bits in the OAR2 register.

#### 11.6.4.1 Slave Mode

As soon as a start condition is detected, the address is received from the SDA line and sent to the shift register; then it is compared with the address of the interface or the General Call address (if selected by software).

**Note:** In 10-bit addressing mode, the comparison includes the header sequence (11110xx0) and the two most significant bits of the address.

**Header matched** (10-bit mode only): the interface generates an acknowledge pulse if the ACK bit is set.

Address not matched: the interface ignores it and waits for another Start condition.

Address matched: the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set.

- EVF and ADSL bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV1).

Next, in 7-bit mode read the DR register to determine from the least significant bit (Data Direction Bit) if the slave must enter Receiver or Transmitter mode.

In 10-bit mode, after receiving the address sequence the slave is always in receive mode. It will enter transmit mode on receiving a repeated Start condition followed by the header sequence with matching address bits and the least significant bit set (11110xx1).

#### **Slave Receiver**

5/

Following the address reception and after SR1 register has been read, the slave receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV2).

#### **Slave Transmitter**

Following the address reception and after SR1 register has been read, the slave sends bytes from the DR register to the SDA line via the internal shift register.

The slave waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV3).

When the acknowledge pulse is received:

The EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

#### **Closing slave communication**

After the last data byte is transferred a Stop Condition is generated by the master. The interface detects this condition and sets:

EVF and STOPF bits with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR2 register (see Figure 59 Transfer sequencing EV4). Error Cases

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and the BERR bits are set with an interrupt if the ITE bit is set.

If it is a Stop then the interface discards the data, released the lines and waits for another Start condition.

If it is a Start then the interface discards the data and waits for the next slave address on the bus.

AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set with an interrupt if the ITE bit is set.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

**Note**: In case of errors, SCL line is not held low; however, the SDA line can remain low if the last bits transmitted are all 0. While AF=1, the SCL line may be held low due to SB or BTF flags that are set at the same time. It is then necessary to release both lines by software.

105/172

#### I<sup>2</sup>C BUS INTERFACE (Cont'd)

57

| Table 21. I | I <sup>2</sup> C Register | Map and | <b>Reset Values</b> |

|-------------|---------------------------|---------|---------------------|

|-------------|---------------------------|---------|---------------------|

| Address<br>(Hex.) | Register<br>Label      | 7          | 6          | 5         | 4         | 3          | 2         | 1         | 0         |

|-------------------|------------------------|------------|------------|-----------|-----------|------------|-----------|-----------|-----------|

| 0028h             | I2CCR<br>Reset Value   | 0          | 0          | PE<br>0   | ENGC<br>0 | START<br>0 | ACK<br>0  | STOP<br>0 | ITE<br>0  |

| 0029h             | I2CSR1<br>Reset Value  | EVF<br>0   | ADD10<br>0 | TRA<br>0  | BUSY<br>0 | BTF<br>0   | ADSL<br>0 | M/SL<br>0 | SB<br>0   |

| 002Ah             | I2CSR2<br>Reset Value  | 0          | 0          | 0         | AF<br>0   | STOPF<br>0 | ARLO<br>0 | BERR<br>0 | GCAL<br>0 |

| 02Bh              | I2CCCR<br>Reset Value  | FM/SM<br>0 | CC6<br>0   | CC5<br>0  | CC4<br>0  | CC3<br>0   | CC2<br>0  | CC1<br>0  | CC0<br>0  |

| 02Ch              | I2COAR1<br>Reset Value | ADD7<br>0  | ADD6<br>0  | ADD5<br>0 | ADD4<br>0 | ADD3<br>0  | ADD2<br>0 | ADD1<br>0 | ADD0<br>0 |

| 002Dh             | I2COAR2<br>Reset Value | FR1<br>0   | FR0<br>1   | 0         | 0         | 0          | ADD9<br>0 | ADD8<br>0 | 0         |

| 002Eh             | I2CDR<br>Reset Value   | MSB<br>0   | 0          | 0         | 0         | 0          | 0         | 0         | LSB<br>0  |

### **12 INSTRUCTION SET**

#### **12.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in 7 main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

Table 24. CPU Addressing Mode Overview

so, most of the addressing modes may be subdivided in two sub-modes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

| Mode      |          | Syntax   | Destination         | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |     |

|-----------|----------|----------|---------------------|------------------------------|------------------------|-------------------|-----|

| Inherent  |          |          | nop                 |                              |                        |                   | + 0 |

| Immediate |          |          | ld A,#\$55          |                              |                        |                   | + 1 |

| Short     | Direct   |          | ld A,\$10           | 00FF                         |                        |                   | + 1 |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF                     |                        |                   | + 2 |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF                         |                        |                   | + 0 |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE                        |                        |                   | + 1 |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF                     |                        |                   | + 2 |

| Short     | Indirect |          | ld A,[\$10]         | 00FF                         | 00FF                   | byte              | + 2 |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF                     | 00FF                   | word              | + 2 |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE                        | 00FF                   | byte              | + 2 |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF                     | 00FF                   | word              | + 2 |

| Relative  | Direct   |          | jrne loop           | PC+/-127                     |                        |                   | + 1 |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127                     | 00FF                   | byte              | + 2 |

| Bit       | Direct   |          | bset \$10,#7        | 00FF                         |                        |                   | + 1 |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF                         | 00FF                   | byte              | + 2 |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF                         |                        |                   | + 2 |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF                         | 00FF                   | byte              | + 3 |

#### INSTRUCTION SET OVERVIEW (Cont'd)

#### 12.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

#### Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table25. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressing ModesIndirectIndexedIndirect

| Long and Short<br>Instructions | Function                                           |

|--------------------------------|----------------------------------------------------|

| LD                             | Load                                               |

| CP                             | Compare                                            |

| AND, OR, XOR                   | Logical Operations                                 |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Sub-<br>stractions operations |

| BCP                            | Bit Compare                                        |

| Short Instructions<br>Only | Function                          |  |  |

|----------------------------|-----------------------------------|--|--|

| CLR                        | Clear                             |  |  |

| INC, DEC                   | Increment/Decrement               |  |  |

| TNZ                        | Test Negative or Zero             |  |  |

| CPL, NEG                   | 1 or 2 Complement                 |  |  |

| BSET, BRES                 | Bit Operations                    |  |  |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |  |  |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Opera-<br>tions  |  |  |

| SWAP                       | Swap Nibbles                      |  |  |

| CALL, JP                   | Call or Jump subroutine           |  |  |

#### 12.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset is following the opcode.

#### Relative (Indirect)

The offset is defined in memory, which address follows the opcode.

#### SUPPLY CURRENT CHARACTERISTICS (Cont'd)

#### 13.4.4 On-chip peripherals

| Symbol                                                | Parameter                                        | Co                     | Тур                   | Unit |    |

|-------------------------------------------------------|--------------------------------------------------|------------------------|-----------------------|------|----|

| I <sub>DD(TIM)</sub>                                  | 16-bit Timer supply current <sup>1)</sup>        | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 200  |    |

|                                                       |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 300  |    |

| I <sub>DD(SPI)</sub> SPI                              | SPI supply current <sup>2)</sup>                 | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 200  |    |

|                                                       |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 250  |    |

| I <sub>DD(SCI)</sub> SCI supply current <sup>3)</sup> | SCI supply surrent <sup>3)</sup>                 | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 350  | ۸  |

|                                                       |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 650  | μA |

| I <sub>DD(I2C)</sub> I2C supply current <sup>4)</sup> | 12C supply current <sup>4</sup>                  | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 350  |    |

|                                                       |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 500  |    |

| I <sub>DD(ADC)</sub>                                  | ADC supply current when converting <sup>5)</sup> | f <sub>ADC</sub> =4MHz | V <sub>DD</sub> =3.0V | 500  |    |

|                                                       |                                                  |                        | V <sub>DD</sub> =5.0V | 600  |    |

#### Notes:

1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer counter running at  $f_{CPU}/2$ ) and timer counter stopped (only TIMD bit set). Data valid for one timer.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to FFh). This measurement includes the pad toggling consumption.

Data based on a differential I<sub>DD</sub> measurement between SCI running at maximum speed configuration (500 kbaud, continuous transmission of AA +RE enabled and SCI off. This measurement includes the pad toggling consumption.

4. Data based on a differential I<sub>DD</sub> measurement between reset configuration (I2C disabled) and a permanent I2C master communication at 300kHz (data sent equal to AAh). This measurement includes the pad toggling consumption (4.7kOhm external pull-up on clock and data lines).

5. Data based on a differential I<sub>DD</sub> measurement between reset configuration (ADC off) and continuous A/D conversion (f<sub>ADC</sub>=4MHz).

57

#### I/O PORT PIN CHARACTERISTICS (Cont'd)

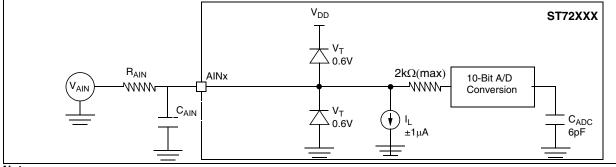

#### **13.12 10-BIT ADC CHARACTERISTICS**

| Symbol            | Parameter                                  | Conditions                    | Min             | Тур | Max                                                | Unit               |

|-------------------|--------------------------------------------|-------------------------------|-----------------|-----|----------------------------------------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                        |                               | 0.5             |     | 4                                                  | MHz                |

| V <sub>AIN</sub>  | Conversion voltage range                   |                               | V <sub>SS</sub> |     | V <sub>DD</sub>                                    | V                  |

| C <sub>ADC</sub>  | Internal sample and hold capacitor         |                               |                 | 6   |                                                    | pF                 |

| t <sub>CONV</sub> | Conversion time                            | FLASH, f <sub>ADC</sub> =4MHz |                 | 28  |                                                    | μs                 |

|                   |                                            |                               |                 | 112 |                                                    | 1/f <sub>ADC</sub> |

|                   |                                            | ROM, f <sub>ADC</sub> =4MHz   | 3.5             |     |                                                    | μs                 |

|                   |                                            |                               |                 | 14  |                                                    | 1/f <sub>ADC</sub> |

| R <sub>AIN</sub>  | External input impedance                   |                               |                 |     | see                                                | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input         |                               |                 |     | Figure 97<br>and<br>Figure<br>98 <sup>1)2)3)</sup> | pF                 |

| f <sub>AIN</sub>  | Variation frequency of analog input signal |                               |                 |     |                                                    | Hz                 |

$V_{DD}$ = 2.7 to 5.5V,  $T_A$  = -40°C to 85°C, unless otherwise specified

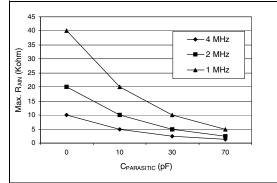

#### Figure 97. R<sub>AIN</sub> max. vs f<sub>ADC</sub> with C<sub>AIN</sub>=0pF<sup>2)</sup>

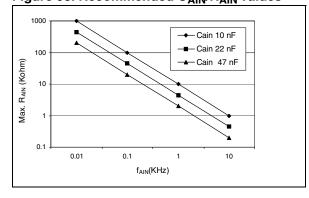

### Figure 98. Recommended CAIN/RAIN values<sup>3)</sup>

Figure 99. Analog Input equivalent circuit

#### Notes:

<u>ل</u>حک

1. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

2.  $C_{PARASITIC}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (3pF). A high  $C_{PARASITIC}$  value will downgrade conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 3. This graph shows that depending on the input signal variation ( $f_{AIN}$ ),  $C_{AIN}$  can be increased for stabilization time and decreased to allow the use of a larger serial resistor ( $R_{AIN}$ ). It is valid for all  $f_{ADC}$  frequencies  $\leq 4$ MHz.