# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | SPI                                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 28-50                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f262g1m6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 2 PIN DE<br>3 REGIS | DUCTION<br>ESCRIPTION<br>TER & MEMORY MAP<br>I PROGRAM MEMORY | 6<br>10 |

|---------------------|---------------------------------------------------------------|---------|

| 4.1                 |                                                               | 14      |

| 4.2                 | MAIN FEATURES                                                 | 14      |

| 4.3                 | PROGRAMMING MODES                                             | 14      |

| 4.4                 | ICC INTERFACE                                                 | 15      |

| 4.5                 | MEMORY PROTECTION                                             | 16      |

| 4.6                 | RELATED DOCUMENTATION                                         | 16      |

| 4.7                 | REGISTER DESCRIPTION                                          | 16      |

| 5 CENT              | RAL PROCESSING UNIT                                           | 17      |

| 5.1                 |                                                               | 17      |

| 5.2                 | MAIN FEATURES                                                 | 17      |

| 5.3                 | CPU REGISTERS                                                 | 17      |

| 6 SUPPL             | LY, RESET AND CLOCK MANAGEMENT                                | 20      |

| 6.1                 | PHASE LOCKED LOOP                                             | 20      |

| 6.2                 | MULTI-OSCILLATOR (MO)                                         | 21      |

| 6.3                 | RESET SEQUENCE MANAGER (RSM)                                  | 22      |

| 6.4                 | SYSTEM INTEGRITY MANAGEMENT (SI)                              | 24      |

| 7 INTER             | RUPTS                                                         | 28      |

| 7.1                 | INTRODUCTION                                                  | 28      |

| 7.2                 | MASKING AND PROCESSING FLOW                                   | 28      |

| 7.3                 | INTERRUPTS AND LOW POWER MODES                                | 30      |

| 7.4                 | CONCURRENT & NESTED MANAGEMENT                                | 30      |

| 7.5                 | INTERRUPT REGISTER DESCRIPTION                                | 31      |

| 8 POWE              | R SAVING MODES                                                | 33      |

| 8.1                 | INTRODUCTION                                                  | 33      |

| 8.2                 | SLOW MODE                                                     | 33      |

| 8.3                 | WAIT MODE                                                     |         |

| 8.4                 | ACTIVE-HALT AND HALT MODES                                    | 35      |

| 8.5                 | HALT MODE                                                     | 36      |

| 9 I/O PO            | RTS                                                           | 38      |

| 9.1                 |                                                               | 38      |

| 9.2                 | FUNCTIONAL DESCRIPTION                                        | 38      |

| 9.3                 | I/O PORT IMPLEMENTATION                                       | 41      |

| 9.4                 | UNUSED I/O PINS                                               | 41      |

| 9.5                 | LOW POWER MODES                                               | 41      |

| 9.6                 | INTERRUPTS                                                    | 41      |

| 9.7                 | DEVICE-SPECIFIC I/O PORT CONFIGURATION                        | 42      |

| 9.8                 | I/O PORT REGISTER DESCRIPTION                                 | 43      |

| 10 MISC             | ELLANEOUS REGISTERS                                           | 45      |

#### CENTRAL PROCESSING UNIT (Cont'd)

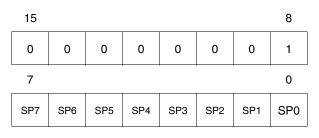

Stack Pointer (SP)

Read/Write

Reset Value: 01 7Fh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 8).

Since the stack is 128 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

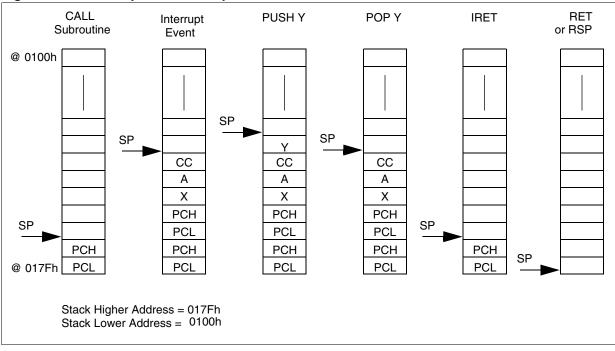

#### Figure 8. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 8

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

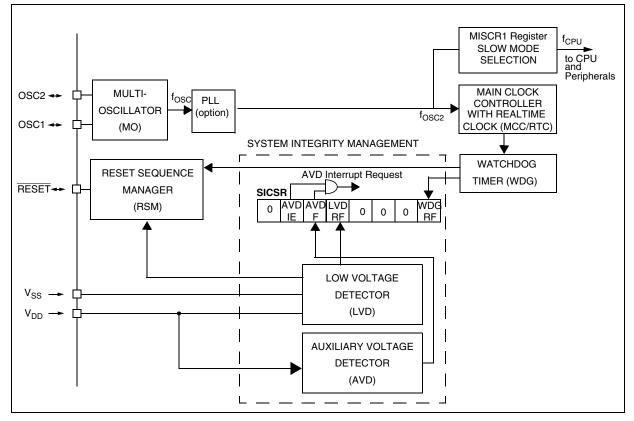

## **6 SUPPLY, RESET AND CLOCK MANAGEMENT**

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components. An overview is shown in Figure 10.

For more details, refer to dedicated parametric section.

#### **Main Features**

- Optional PLL for multiplying the frequency by 2 (not to be used with internal RC oscillator)

- Reset Sequence Manager (RSM)

- Multi-Oscillator Clock Management (MO)

- 4 Crystal/Ceramic resonator oscillators

- 1 Internal RC oscillator

- System Integrity Management (SI)

- Main supply Low Voltage Detector (LVD)

- Auxiliary Voltage Detector (AVD) with interrupt capability for monitoring the main supply

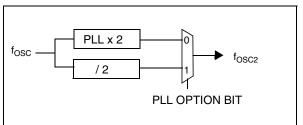

#### 6.1 PHASE LOCKED LOOP

If the clock frequency input to the PLL is in the 2 to 4 MHz range, the PLL can be used to multiply the frequency by two to obtain an  $f_{OSC2}$  of 4 to 8 MHz.

The PLL is enabled by option byte. If the PLL is disabled, then  $f_{OSC2} = f_{OSC}/2$ .

**Caution:** The PLL is not recommended for applications where timing accuracy is required. See "PLL Characteristics" on page 139.

#### Figure 9. PLL Block Diagram

#### Figure 10. Clock, Reset and Supply Block Diagram

## **8 POWER SAVING MODES**

#### **8.1 INTRODUCTION**

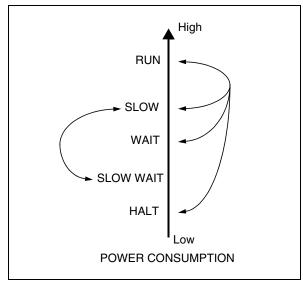

To give a large measure of flexibility to the application in terms of power consumption, three main power saving modes are implemented in the ST7 (see Figure 20).

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided by 2 ( $f_{CPU}$ ).

From Run mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

#### Figure 20. Power Saving Mode Transitions

#### 8.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

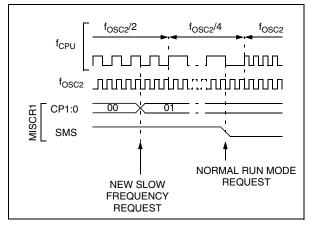

SLOW mode is controlled by three bits in the MISR1 register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency (f<sub>CPU</sub>).

In this mode, the oscillator frequency can be divided by 4, 8, 16 or 32 instead of 2 in normal operating mode. The CPU and peripherals are clocked at this lower frequency.

**Note**: SLOW-WAIT mode is activated when enterring the WAIT mode while the device is already in SLOW mode.

#### Figure 21. SLOW Mode Clock Transitions

#### MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

#### 11.2.2 Low Power Modes

| Mode            | Description                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.<br>MCC/RTC interrupt cause the device to exit<br>from WAIT mode.                                                       |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is<br>set), the registers are frozen.<br>MCC/RTC interrupt cause the device to exit<br>from ACTIVE-HALT mode.     |

| HALT            | MCC/RTC counter and registers are frozen.<br>MCC/RTC operation resumes when the<br>MCU is woken up by an interrupt with "exit<br>from HALT" capability. |

#### 11.2.3 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

#### Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

### 11.2.4 Register Description

#### MCC CONTROL/STATUS REGISTER (MCCSR) Read/Write

Reset Value: 0000 0000 (00h)

| 7 |  |  |

|---|--|--|

|   |  |  |

| 0 | 0 | 0 | 0 | TB1 | ТВ0 | OIE | OIF |

|---|---|---|---|-----|-----|-----|-----|

Bit 7:4 = reserved

#### Bit 3:2 = TB[1:0] Time base control

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                    | TB1                     | тво |     |

|-----------|-------------------------|-------------------------|-----|-----|

| Prescaler | f <sub>OSC2</sub> =4MHz | f <sub>OSC2</sub> =8MHz | 101 | 100 |

| 16000     | 4ms                     | 2ms                     | 0   | 0   |

| 32000     | 8ms                     | 4ms                     | 0   | 1   |

| 80000     | 20ms                    | 10ms                    | 1   | 0   |

| 200000    | 50ms                    | 25ms                    | 1   | 1   |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

#### Bit 1 = **OIE** Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disabled

1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode.

#### Bit 0 = **OIF** Oscillator interrupt flag

This bit is set by hardware and cleared by software reading the CSR register. It indicates when set that the main oscillator has reached the selected elapsed time (TB1:0).

0: Timeout not reached

1: Timeout reached

**CAUTION**: The BRES and BSET instructions must not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.

| Address<br>(Hex.) | Register<br>Label    | 7 | 6          | 5         | 4          | 3        | 2        | 1        | 0          |

|-------------------|----------------------|---|------------|-----------|------------|----------|----------|----------|------------|

| 0025h             | SICSR<br>Reset Value | 0 | AVDIE<br>0 | AVDF<br>0 | LVDRF<br>x | 0        | 0        | 0        | WDGRF<br>x |

| 0026h             | MCCSR<br>Reset Value | 0 | 0          | 0         | 0          | TB1<br>0 | TB0<br>0 | OIE<br>0 | OIF<br>0   |

#### 16-BIT TIMER (Cont'd)

5/

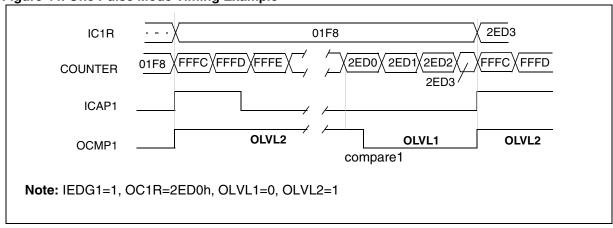

#### Figure 44. One Pulse Mode Timing Example

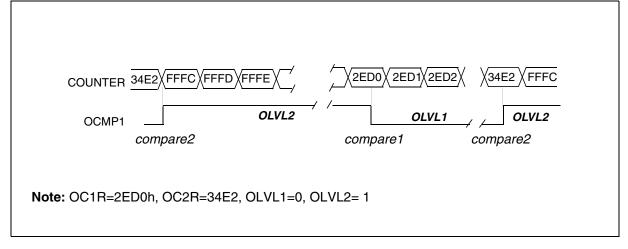

#### Figure 45. Pulse Width Modulation Mode Timing Example

#### SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.4.3.1 Functional Description

57

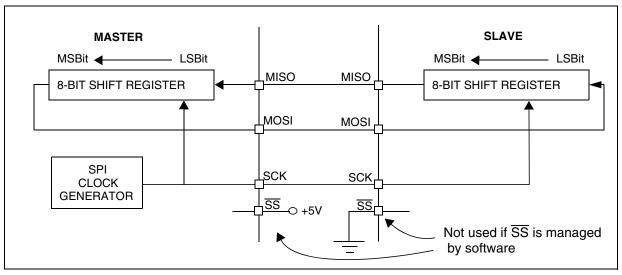

A basic example of interconnections between a single master and a single slave is illustrated in Figure 47.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device re-

Figure 47. Single Master/ Single Slave Application

sponds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 50) but master and slave must be programmed with the same timing mode.

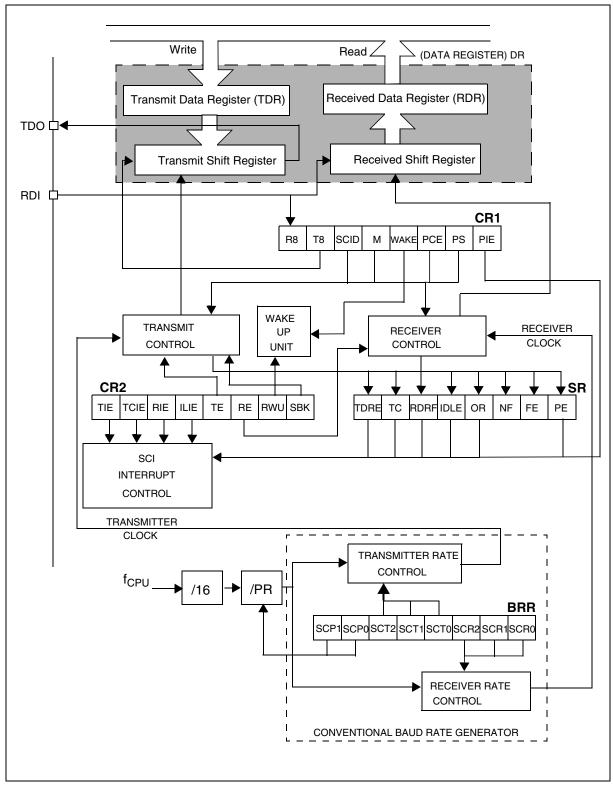

#### Figure 53. SCI Block Diagram

۸Ţ/

#### **11.5.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 53. It contains 6 dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

57

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 11.5.7for the definitions of each bit.

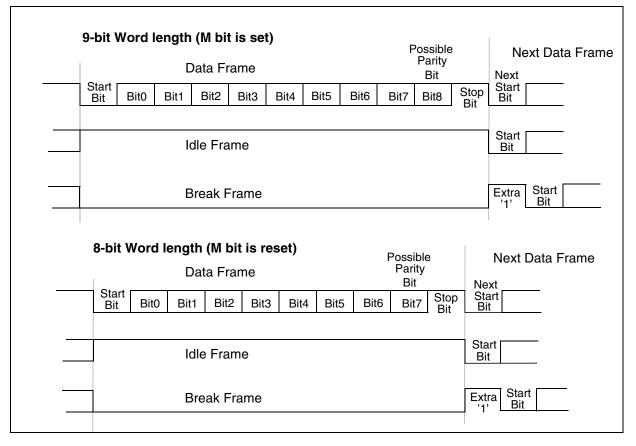

#### 11.5.4.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 53).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

#### Figure 54. Word Length Programming

#### 11.5.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 53).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit or after the break frame) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 54).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set i.e. before writing the next byte in the SCIDR.

#### 11.5.5 Low Power Modes

| Mode | Description                                                                             |

|------|-----------------------------------------------------------------------------------------|

|      | No effect on SCI.                                                                       |

| WAIT | SCI interrupts cause the device to exit from Wait mode.                                 |

|      | SCI registers are frozen.                                                               |

| HALT | In Halt mode, the SCI stops transmit-<br>ting/receiving until Halt mode is exit-<br>ed. |

#### 11.5.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the inter-

| Interrupt Event                 | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|---------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty | TDRE          | TIE                      | Yes                  | No                   |

| Transmission Com-<br>plete      | тс            | TCIE                     | Yes                  | No                   |

| Received Data Ready to be Read  | RDRF          | RIE                      | Yes                  | No                   |

| Overrun Error Detected          | OR            |                          | Yes                  | No                   |

| Idle Line Detected              | IDLE          | ILIE                     | Yes                  | No                   |

| Parity Error                    | PE            | PIE                      | Yes                  | No                   |

rupt mask in the CC register is reset (RIM instruction).

#### 11.5.7 Register Description STATUS REGISTER (SCISR)

#### Read Only

Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |    |    |    | 0  |

|------|----|------|------|----|----|----|----|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |

#### Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

**Note:** Data will not be transferred to the shift register unless the TDRE bit is cleared.

#### Bit 6 = **TC** *Transmission complete.*

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** *Received data ready flag.*

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when a Idle Line is detected. An interrupt is generated if the ILIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit will not be set again until the RDRF bit has been set itself (i.e. a new idle line occurs).

#### Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF=1. An interrupt is generated if RIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set RDR register content will not be lost but the shift register will be overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise is detected

1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = **FE** Framing error.

This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = **PE** Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE=1 in the SCICR1 register. 0: No parity error

1: Parity error

#### Table 20. SCI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Name | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 50                | SCISR            | TDRE  | TC    | RDRF  | IDLE  | OR    | NF    | FE    | PE    |

| 50                | Reset Value      | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 51                | SCIDR            | DR7   | DR6   | DR5   | DR4   | DR3   | DR2   | DR1   | DR0   |

| 51                | Reset Value      | х     | х     | х     | х     | х     | х     | х     | х     |

| 52                | SCIBRR           | SCP1  | SCP0  | SCT2  | SCT1  | SCT0  | SCR2  | SCR1  | SCR0  |

| 52                | Reset Value      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 50                | SCICR1           | R8    | Т8    | SCID  | М     | WAKE  | PCE   | PS    | PIE   |

| 53                | Reset Value      | х     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 54                | SCICR2           | TIE   | TCIE  | RIE   | ILIE  | TE    | RE    | RWU   | SBK   |

| 54                | Reset Value      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 55                | SCIERPR          | ERPR7 | ERPR6 | ERPR5 | ERPR4 | ERPR3 | ERPR2 | ERPR1 | ERPR0 |

| 55                | Reset Value      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 56                | SCIETPR          | ETPR7 | ETPR6 | ETPR5 | ETPR4 | ETPR3 | ETPR2 | ETPR1 | ETPR0 |

| 00                | Reset Value      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### Master Transmitter

Following the address transmission and after SR1 register has been read, the master sends bytes from the DR register to the SDA line via the internal shift register.

The master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV8).

When the acknowledge bit is received, the interface sets:

EVF and BTF bits with an interrupt if the ITE bit is set.

To close the communication: after writing the last byte to the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

#### **Error Cases**

57

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and BERR bits are set by hardware with an interrupt if ITE is set.

Note that BERR will not be set if an error is detected during the first or second pulse of each 9bit transaction:

#### Single Master Mode

If a Start or Stop is issued during the first or second pulse of a 9-bit transaction, the BERR flag will not be set and transfer will continue however the BUSY flag will be reset. To work around this, slave devices should issue a NACK when they receive a misplaced Start or Stop. The reception of a NACK or BUSY by the master in the middle of communication gives the possibility to reinitiate transmission.

Multimaster Mode

Normally the BERR bit would be set whenever unauthorized transmission takes place while transfer is already in progress. However, an issue will arise if an external master generates an unauthorized Start or Stop while the I<sup>2</sup>C master is on the first or second pulse of a 9-bit transaction. It is possible to work around this by polling the BUSY bit during I<sup>2</sup>C master mode transmission. The resetting of the BUSY bit can then be handled in a similar manner as the BERR flag being set.

AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set by hardware with an interrupt if the ITE bit is set. To resume, set the Start or Stop bit.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

ARLO: Detection of an arbitration lost condition. In this case the ARLO bit is set by hardware (with an interrupt if the ITE bit is set and the interface goes automatically back to slave mode (the M/SL bit is cleared).

**Note**: In all these cases, the SCL line is not held low; however, the SDA line can remain low due to possible «0» bits transmitted last. It is then necessary to release both lines by software.

I<sup>2</sup>C BUS INTERFACE (Cont'd) 11.6.7 Register Description

## I<sup>2</sup>C CONTROL REGISTER (CR)

### Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |    |      |       |     |      | 0   |

|---|---|----|------|-------|-----|------|-----|

| 0 | 0 | PE | ENGC | START | ACK | STOP | ITE |

Bit 7:6 = Reserved. Forced to 0 by hardware.

Bit 5 = **PE** Peripheral enable.

This bit is set and cleared by software.

0: Peripheral disabled

1: Master/Slave capability

Notes:

- When PE=0, all the bits of the CR register and the SR register except the Stop bit are reset. All outputs are released while PE=0

- When PE=1, the corresponding I/O pins are selected by hardware as alternate functions.

- To enable the I<sup>2</sup>C interface, write the CR register TWICE with PE=1 as the first write only activates the interface (only PE is set).

#### Bit 4 = ENGC Enable General Call.

This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0). The 00h General Call address is acknowledged (01h ignored).

- 0: General Call disabled

- 1: General Call enabled

**Note:** In accordance with the I2C standard, when GCAL addressing is enabled, an I2C slave can only receive data. It will not transmit data to the master.

Bit 3 = **START** Generation of a Start condition. This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0) or when the Start condition is sent (with interrupt generation if ITE=1).

#### In master mode:

- 0: No start generation

- 1: Repeated start generation

- In slave mode:

- 0: No start generation

- 1: Start generation when the bus is free

#### Bit 2 = **ACK** Acknowledge enable.

This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0).

- 0: No acknowledge returned

- 1: Acknowledge returned after an address byte or a data byte is received

#### Bit 1 = **STOP** Generation of a Stop condition.

This bit is set and cleared by software. It is also cleared by hardware in master mode. Note: This bit is not cleared when the interface is disabled (PE=0).

- In master mode:

- 0: No stop generation

1: Stop generation after the current byte transfer or after the current Start condition is sent. The STOP bit is cleared by hardware when the Stop condition is sent.

- In slave mode:

0: No stop generation

1: Release the SCL and SDA lines after the current byte transfer (BTF=1). In this mode the STOP bit has to be cleared by software.

#### Bit 0 = ITE Interrupt enable.

This bit is set and cleared by software and cleared by hardware when the interface is disabled (PE=0).

- 0: Interrupts disabled

- 1: Interrupts enabled

Refer to Figure 60 for the relationship between the events and the interrupt.

SCL is held low when the ADD10, SB, BTF or ADSL flags or an EV6 event (See Figure 59) is detected.

#### 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### 11.7.3.2 Digital A/D Conversion Result

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{DDA}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the alloted time.

#### 11.7.3.3 A/D Conversion

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the «I/O ports» chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

Select the CH[2:0] bits to assign the analog channel to convert.

#### ADC Conversion mode

In the ADCCSR register:

- Set the SPEED or the SLOW bits

- Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH or a write to any bit of the ADCCSR resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll EOC bit

- 2. Read ADCDRL. This locks the ADCDRH until it is read.

- 3. Read ADCDRH. This clears EOC automatically.

To read only 8 bits, perform the following steps:

- 1. Poll EOC bit

- 2. Read ADCDRH. This clears EOC automatically.

#### 11.7.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed and between single shot conversions.

| Mode | Description                                        |  |  |  |

|------|----------------------------------------------------|--|--|--|

| WAIT | No effect on A/D Converter                         |  |  |  |

|      | A/D Converter disabled.                            |  |  |  |

|      | After wakeup from Halt mode, the A/D               |  |  |  |

| нагт | Converter requires a stabilization time            |  |  |  |

|      | t <sub>STAB</sub> (see Electrical Characteristics) |  |  |  |

|      | before accurate conversions can be                 |  |  |  |

|      | performed.                                         |  |  |  |

#### 11.7.5 Interrupts

None.

#### **13.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### 13.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                            | Maximum value                                      | Unit    |  |

|-----------------------------------|----------------------------------------------------|----------------------------------------------------|---------|--|

| V <sub>DD</sub> - V <sub>SS</sub> | Supply voltage                                     | 6.5                                                | V       |  |

| V <sub>IN</sub>                   | Input voltage on any pin <sup>1) &amp; 2)</sup>    | $V_{\rm SS}\mbox{-}0.3$ to $V_{\rm DD}\mbox{+}0.3$ | v       |  |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (Human Body Model) | see Section 13.7.3 on p                            | 200 1/2 |  |

| V <sub>ESD(MM)</sub>              | Electrostatic discharge voltage (Machine Model)    | See Section 13.7.3 on p                            | aye 142 |  |

#### **13.2.2 Current Characteristics**

| Symbol                                       | Ratings                                                                | Maximum value | Unit |

|----------------------------------------------|------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                             | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>  | 100           | mA   |

| I <sub>VSS</sub>                             | Total current out of V <sub>SS</sub> ground lines (sink) <sup>3)</sup> | 150           |      |

|                                              | Output current sunk by any standard I/O and control pin                | 25            |      |

| I <sub>IO</sub>                              | Output current sunk by any high sink I/O pin                           | 50            |      |

|                                              | Output current source by any I/Os and control pin                      | - 25          |      |

|                                              | Injected current on Flash device pins PB0 and PB1                      | + 5           |      |

| 2) & 4)                                      | Injected current on RESET pin                                          | ± 5           |      |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on OSC1 and OSC2 pins                                 | ± 5           |      |

|                                              | Injected current on any other pin 5) & 6)                              | ± 5           |      |

| $\Sigma I_{INJ(PIN)}^{2)}$                   | Total injected current (sum of all I/O and control pins) <sup>5)</sup> | ± 20          |      |

#### 13.2.3 Thermal Characteristics

| Symbol           | Ratings                                                                        | Value                                                                                                            | Unit |  |  |

|------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|--|--|

| T <sub>STG</sub> | Storage temperature range                                                      | -65 to +150                                                                                                      | °C   |  |  |

| TJ               | Maximum junction temperature (see Section Figure 104.<br>Package" on page 160) | Maximum junction temperature (see Section Figure 104. "Low Profile Fine Pitch Ball Grid Ar Package" on page 160) |      |  |  |

#### Notes:

1. Directly connecting the I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 10k $\Omega$  for I/Os). Unused I/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration. For reset pin, please refer to Figure 91 and Figure 92.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "10-BIT ADC CHARACTERISTICS" on page 157. For best reliability, it is recommended to avoid negative injection of more than 1.6mA.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

#### **13.3 OPERATING CONDITIONS**

#### **13.3.1 General Operating Conditions**

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified.

| Symbol                           | Parameter | Conditions                      | Min  | Max  | Unit |  |

|----------------------------------|-----------|---------------------------------|------|------|------|--|

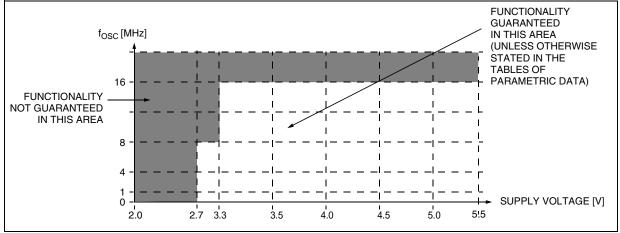

| V <sub>DD</sub> Supply voltage   |           | f <sub>OSC</sub> = 8 MHz. max.  | 2.7  | 5.5  | V    |  |

|                                  |           | f <sub>OSC</sub> = 16 MHz. max. | 3.3  | 5.5  | v    |  |

| F External clock frequency on OS |           | V <sub>DD</sub> ≥3.3V           | up t | o 16 | MHz  |  |

| tosc                             | pin       | V <sub>DD</sub> ≥2.7V           | up   | to 8 |      |  |

#### Figure 64. $f_{OSC}$ Maximum Operating Frequency Versus V<sub>DD</sub> Supply Voltage

#### I/O PORT PIN CHARACTERISTICS (Cont'd)

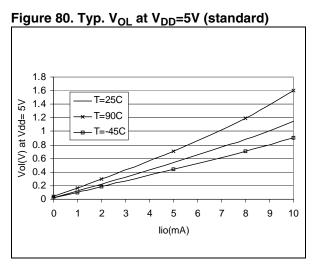

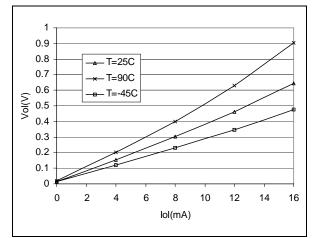

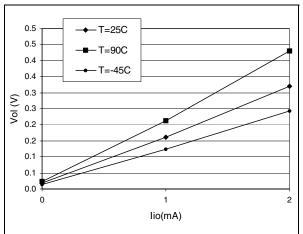

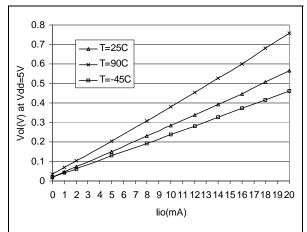

Figure 81. Typ. V<sub>OL</sub> at V<sub>DD</sub>=3V (high-sink)

Figure 82. Typ. V<sub>OL</sub> at V<sub>DD</sub>=2.7V (standard)

Figure 83. Typ. V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink)

#### 16.2.2 I/O Port B and C configuration

When using an external quartz crystal or ceramic resonator, the  $f_{OSC2}$  clock may be disturbed because the device goes into reserved mode controlled by Port B and C.

This happens with either one of the following configurations:

PB1=0, PC2=1, PB3=0 while PLL option is both disabled and PC4 is toggling

PB1=0, PC2=1, PB3=0, PC4=1 while PLL option is enabled

This is detailed in the following table:

| PLL | PB1 | PC2 | PB3 | PC4  | <b>Clock Disturbance</b> |  |  |   |                     |

|-----|-----|-----|-----|------|--------------------------|--|--|---|---------------------|

|     |     |     |     | Tog  | Max. 2 clock cycles      |  |  |   |                     |

| OFF | 0   | 1   | 0   | glin | lost at each rising or   |  |  |   |                     |

|     |     |     |     |      |                          |  |  | g | falling edge of PC4 |

| ON  | 0   | - 1 | 0   | -1   | Max. 1 clock cycle       |  |  |   |                     |

| ON  | 0   | -   | 0   | I    | lost out of every 16     |  |  |   |                     |

As a consequence, for cycle-accurate operations, these configurations are prohibited in either input or output mode.

#### Workaround:

To avoid this occurring, it is recommended to connect one of these pins to GND (PC2 or PC4) or  $V_{DD}$  (PB1 or PB3).

#### 16.2.3 16-bit Timer PWM mode

After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

#### 16.2.4 SPI Multimaster Mode

Multi master mode is not supported.

#### 16.2.5 Internal RC oscillator with LVD

If the LVD is disabled, the internal RC oscillator clock source cannot be used.

In ICP mode, new flash devices must be programmed with an external clock connected to the OSC1 pin or using a crystal or ceramic resonator. In the STVP7 programming tool software, select the "OPTIONS DISABLED" mode.

#### 16.2.6 External clock with PLL

The PLL option is not supported for use with external clock source.

## 16.2.7 Halt mode power consumption with ADC on

If the A/D converter is being used when Halt mode is entered, the power consumption in Halt Mode may exceed the maximum specified in the datasheet.

#### Workaround

Switch off the ADC by software (ADON=0) before executing a HALT instruction.

#### 16.2.8 Active Halt wake-up by external interrupt

External interrupts are not able to wake-up the MCU from Active Halt mode. The MCU can only exit from Active Halt mode by means of an MCC/ RTC interrupt or a reset.

#### Workaround

Use WAIT mode if external interrupt capability is required in low power mode.

#### 16.2.9 SCI Wrong Break duration

#### Description

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M=0

- 22 bits instead of 11 bits if M=1.

In the same way, as long as the SBK bit is set, break characters are sent to the TDO pin. This may lead to generate one break more than expected.

#### Occurrence

The occurrence of the problem is random and proportional to the baudrate. With a transmit frequency of 19200 baud (fCPU=8MHz and SCI-BRR=0xC9), the wrong break duration occurrence is around 1%.

#### Workaround

If this wrong duration is not compliant with the communication protocol in the application, software can request that an Idle line be generated before the break character. In this case, the break duration is always correct assuming the application is not doing anything between the idle and the break. This can be ensured by temporarily disabling interrupts.

The exact sequence is:

- Disable interrupts

- Reset and Set TE (IDLE request)

- Set and Reset SBK (Break Request)

- Re-enable interrupts

## 16.2.10 A/D converter accuracy for first conversion

When the ADC is enabled after being powered down (for example when waking up from HALT, ACTIVE-HALT or setting the ADON bit in the AD-CCSR register), the first conversion (8-bit or 10-