# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 22                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 28-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f262g1m6tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

\_

|    | 10.1  | I/O PORT INTERRUPT SENSITIVITY                            | . 45 |

|----|-------|-----------------------------------------------------------|------|

|    | 10.2  | I/O PORT ALTERNATE FUNCTIONS                              | . 45 |

|    | 10.3  | MISCELLANEOUS REGISTER DESCRIPTION                        | . 46 |

| 11 | ON-C  | HIP PERIPHERALS                                           | . 48 |

|    |       | WATCHDOG TIMER (WDG)                                      |      |

|    | 11.2  | MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (MCC/RTC)      | . 53 |

|    | 11.3  | 16-BIT TIMER                                              | . 55 |

|    | 11.4  | SERIAL PERIPHERAL INTERFACE (SPI)                         |      |

|    | 11.5  | SERIAL COMMUNICATIONS INTERFACE (SCI)                     | . 87 |

|    | 11.6  | I2C BUS INTERFACE (I2C)                                   | 103  |

|    | 11.7  | 10-BIT A/D CONVERTER (ADC)                                | 116  |

| 12 | INSTE | RUCTION SET                                               | 120  |

|    |       | CPU ADDRESSING MODES                                      |      |

|    | 12.2  | INSTRUCTION GROUPS                                        | 123  |

| 13 | ELEC  |                                                           | -    |

|    | 13.1  |                                                           |      |

|    |       | ABSOLUTE MAXIMUM RATINGS                                  |      |

|    |       | OPERATING CONDITIONS                                      |      |

|    | 13.4  | SUPPLY CURRENT CHARACTERISTICS                            | 131  |

|    | 13.5  | CLOCK AND TIMING CHARACTERISTICS                          |      |

|    | 13.6  | MEMORY CHARACTERISTICS                                    | 140  |

|    | 13.7  | EMC CHARACTERISTICS                                       | 141  |

|    | 13.8  | I/O PORT PIN CHARACTERISTICS                              | 144  |

|    | 13.9  | CONTROL PIN CHARACTERISTICS                               | 150  |

|    | 13.10 | TIMER PERIPHERAL CHARACTERISTICS                          | 152  |

|    | 13.11 | COMMUNICATION INTERFACE CHARACTERISTICS                   | 153  |

|    | 13.12 | 10-BIT ADC CHARACTERISTICS                                | 157  |

| 14 | PACK  | AGE CHARACTERISTICS                                       | 159  |

|    | 14.1  | PACKAGE MECHANICAL DATA                                   | 159  |

|    | 14.2  | THERMAL CHARACTERISTICS                                   | 160  |

|    | 14.3  | LEAD-FREE PACKAGE INFORMATION                             | 161  |

| 15 | DEVIC | CE CONFIGURATION AND ORDERING INFORMATION                 | 162  |

|    | 15.1  | OPTION BYTES                                              | 162  |

|    | 15.2  | DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 164  |

|    |       | DEVELOPMENT TOOLS                                         |      |

| 16 |       | VN LIMITATIONS                                            |      |

|    | 16.1  | ALL FLASH AND ROM DEVICES                                 | 168  |

|    | 16.2  | FLASH DEVICES ONLY                                        | 168  |

| 17 | REVIS | SION HISTORY                                              | 171  |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet Please note that the list of known limitations can be found at the end of this document on page 168.

57

# PIN DESCRIPTION (Cont'd)

57

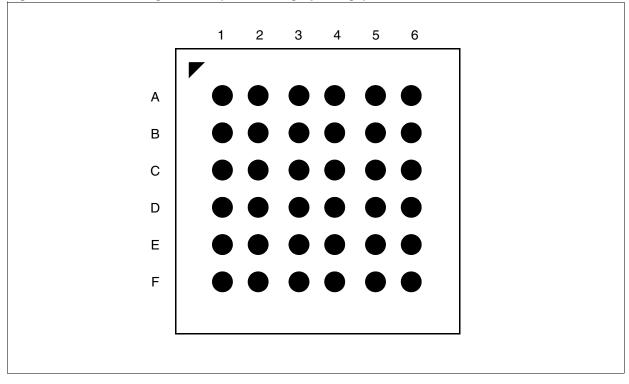

# Figure 4. TFBGA Package Pinout (view through package)

# Table 2. Hardware Register Map

57

| Address                                                     | Block            | Register<br>Label                                                                                                                                                                                   | Register Name                                                                                                                                                    | Reset<br>Status                               | Remarks                                                     |

|-------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|

| 0000h<br>0001h<br>0002h                                     | Port C           | PCDR<br>PCDDR<br>PCOR                                                                                                                                                                               | Port C Data Register<br>Port C Data Direction Register<br>Port C Option Register                                                                                 | xx000000h <sup>1)</sup><br>00h<br>00h         | R/W <sup>2)</sup><br>R/W <sup>2)</sup><br>R/W <sup>2)</sup> |

| 0003h                                                       |                  |                                                                                                                                                                                                     | Reserved (1 Byte)                                                                                                                                                |                                               |                                                             |

| 0004h<br>0005h<br>0006h                                     | Port B           | PBDR<br>PBDDR<br>PBOR                                                                                                                                                                               | Port B Data Register<br>Port B Data Direction Register<br>Port B Option Register                                                                                 | 00h <sup>1)</sup><br>00h<br>00h               | R/W<br>R/W<br>R/W.                                          |

| 0007h                                                       |                  |                                                                                                                                                                                                     | Reserved (1 Byte)                                                                                                                                                |                                               |                                                             |

| 0008h<br>0009h<br>000Ah                                     | Port A           | PADR<br>PADDR<br>PAOR                                                                                                                                                                               | Port A Data Register<br>Port A Data Direction Register<br>Port A Option Register                                                                                 | 00h <sup>1)</sup><br>00h<br>00h               | R/W<br>R/W<br>R/W                                           |

| 000Bh<br>to<br>001Bh                                        |                  |                                                                                                                                                                                                     | Reserved (17 Bytes)                                                                                                                                              |                                               |                                                             |

| 001Ch<br>001Dh<br>001Eh<br>001Fh                            | ITC              | ISPR0<br>ISPR1<br>ISPR2<br>ISPR3                                                                                                                                                                    | Interrupt software priority register0<br>Interrupt software priority register1<br>Interrupt software priority register2<br>Interrupt software priority register3 | FFh<br>FFh<br>FFh<br>FFh                      | R/W<br>R/W<br>R/W<br>R/W                                    |

| 0020h                                                       |                  | MISCR1                                                                                                                                                                                              | Miscellanous register 1                                                                                                                                          | 00h                                           | R/W                                                         |

| 0021h<br>0022h<br>0023h                                     | SPI              | SPIDR<br>SPICR<br>SPICSR                                                                                                                                                                            | SPI Data I/O Register<br>SPI Control Register<br>SPI Status Register                                                                                             | xxh<br>0xh<br>00h                             | R/W<br>R/W<br>R/W                                           |

| 0024h                                                       | WATCHDOG         | WDGCR                                                                                                                                                                                               | Watchdog Control Register                                                                                                                                        | 7Fh                                           | R/W                                                         |

| 0025h                                                       |                  | SICSR                                                                                                                                                                                               | System Integrity Control / Status Register                                                                                                                       | 000x 000x                                     | R/W                                                         |

| 0026h                                                       | MCC              | MCCSR                                                                                                                                                                                               | Main Clock Control / Status Register                                                                                                                             | 00h                                           | R/W                                                         |

| 0027h                                                       |                  |                                                                                                                                                                                                     | Reserved (1 Byte)                                                                                                                                                |                                               |                                                             |

| 0028h<br>0029h<br>002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh | l <sup>2</sup> C | I2CCRI2C Control RegisterI2CSR1I2C Status Register 1I2CSR2I2C Status Register 2I2CCCRI2C Clock Control RegisterI2COAR1I2C Own Address RegisterI2COAR2I2C Own Address RegisterI2CDRI2C Data Register |                                                                                                                                                                  | 00h<br>00h<br>00h<br>00h<br>00h<br>40h<br>00h | R/W<br>Read Only<br>R/W<br>R/W<br>R/W<br>R/W                |

| 002Fh<br>0030h                                              |                  | 1                                                                                                                                                                                                   | Reserved (2 Bytes)                                                                                                                                               | 1                                             |                                                             |

# 6.4 SYSTEM INTEGRITY MANAGEMENT (SI)

The System Integrity Management block contains group the Low voltage Detector (LVD) and Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

**Note:** A reset can also be triggered following the detection of an illegal opcode or prebyte code. Refer to Section 12.2.1 on page 123 for further details.

#### 6.4.1 Low Voltage Detector (LVD)

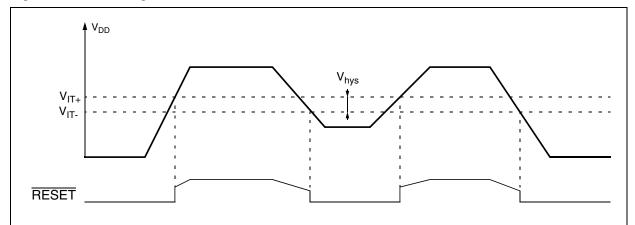

The Low Voltage Detector function (LVD) generates a static reset when the V<sub>DD</sub> supply voltage is below a V<sub>IT</sub>- reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The  $V_{IT-}$  reference value for a voltage drop is lower than the  $V_{IT+}$  reference value for power-on in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{\text{DD}}$  is below:

$-V_{IT+}$  when  $V_{DD}$  is rising

$-V_{IT}$  when  $V_{DD}$  is falling

The LVD function is illustrated in Figure 14.

The voltage threshold can be configured by option byte to be low, medium or high.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT-}$ , the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

The LVD allows the device to be used without any external RESET circuitry.

The LVD is an optional function which can be selected by option byte.

Use of LVD with capacitive power supply: with this type of power supply, if power cuts occur in the application, it is recommended to pull  $V_{DD}$  down to 0V to ensure optimum restart conditions. Refer to circuit example in Figure 91 on page 151 and note 6.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

#### Figure 14. Low Voltage Detector vs Reset

# **7 INTERRUPTS**

# 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non-maskable events: RESET and TRAP

This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

# 7.2 MASKING AND PROCESSING FLOW

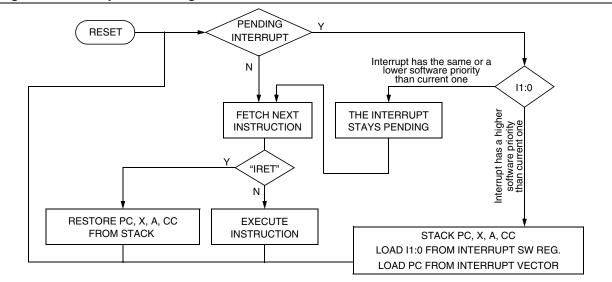

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of each interrupt vector (see Table 4). The processing flow is shown in Figure 16

#### Figure 16. Interrupt Processing Flowchart

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

#### Table 4. Interrupt Software Priority Levels

| Interrupt software priority   | Level | l1 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ★     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

# I/O PORTS (Cont'd)

# 9.7 DEVICE-SPECIFIC I/O PORT CONFIGURATION

The I/O port register configurations are summarised as follows.

# **Interrupt Ports**

PA7, PA5, PA3:0, PB7:0, PC5:0 (with pull-up)

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

# True Open Drain Interrupt Ports PA6, PA4 (without pull-up)

| MODE                         | DDR | OR |

|------------------------------|-----|----|

| floating input               | 0   | 0  |

| floating interrupt input     | 0   | 1  |

| open drain (high sink ports) | 1   | Х  |

#### **Table 9. Port Configuration**

| Port   | Pin Name  | Input ([ | DDR = 0)           | Output (DDR = 1) |           |           |  |

|--------|-----------|----------|--------------------|------------------|-----------|-----------|--|

| 1011   | r in Name | OR = 0   | OR = 1             | OR = 0           | OR = 1    | High-Sink |  |

|        | PA7       | floating | pull-up interrupt  | open drain       | push-pull |           |  |

|        | PA6       | floating | floating interrupt | true ope         | en-drain  |           |  |

| Port A | PA5       | floating | pull-up interrupt  | open drain       | push-pull | Yes       |  |

|        | PA4       | floating | floating interrupt | true ope         | en-drain  |           |  |

|        | PA3:0     | floating | pull-up interrupt  | open drain       | push-pull |           |  |

| Port B | PB7:0     | floating | pull-up interrupt  | open drain       | push-pull | No        |  |

| Port C | PC5:0     | floating | pull-up interrupt  | open drain       | push-pull | NO IN     |  |

# I/O PORTS (Cont'd)

# Table 10. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|--------------------------|-----|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h             | PCDR                     |     |   |   |   |   |   |   |     |

| 0001h             | PCDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0002h             | PCOR                     |     |   |   |   |   |   |   |     |

| 0004h             | PBDR                     |     |   |   |   |   |   |   |     |

| 0005h             | PBDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0006h             | PBOR                     |     |   |   |   |   |   |   |     |

| 0008h             | PADR                     |     |   |   |   |   |   |   |     |

| 0009h             | PADDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Ah             | PAOR                     |     |   |   |   |   |   |   |     |

# MISCELLANEOUS REGISTERS (Cont'd)

# MISCELLANEOUS REGISTER 2 (MISCR2)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |     |     |     | 0   |  |

|---|---|---|---|-----|-----|-----|-----|--|

| 0 | 0 | 0 | 0 | MOD | SOD | SSM | SSI |  |

**Caution:** This register has been provided for compatibility with the ST72254 family only. The same bits are available in the SPICSR register. New applications must use the SPICSR register. Do not use both registers, this will cause the SPI to malfunction.

Bits 7:4 = **Reserved** *always read as 0*

Bits 3 = **MOD** *SPI Master Output Disable* This bit is set and cleared by software. When set, it disables the SPI Master (MOSI) output signal. 0: SPI Master Output enabled. 1: SPI Master Output disabled.

Bit 2 = **SOD** *SPI Slave Output Disable* This bit is set and cleared by software. When set it disable the SPI Slave (MISO) output signal. 0: SPI Slave Output enabled. 1: SPI Slave Output disabled.

Bit 1 = **SSM**  $\overline{SS}$  mode selection

This bit is set and cleared by software.

- 0: Normal mode the level of the SPI SS signal is input from the external SS pin.\_\_\_

- 1: I/O mode, the level of the SPI SS signal is read from the SSI bit.

Bit  $0 = SSI \overline{SS}$  internal mode This bit replaces the  $\overline{SS}$  pin of the SPI when the SSM bit is set to 1. (see SPI description). It is set and cleared by software.

| Address<br>(Hex.) | Register<br>Label     | 7         | 6         | 5        | 4         | 3         | 2        | 1        | 0        |

|-------------------|-----------------------|-----------|-----------|----------|-----------|-----------|----------|----------|----------|

| 0020h             | MISCR1<br>Reset Value | IS11<br>0 | IS10<br>0 | MCO<br>0 | IS01<br>0 | IS00<br>0 | CP1<br>0 | CP0<br>0 | SMS<br>0 |

| 0040h             | MISCR2<br>Reset Value | 0         | 0         | 0        | 0         | MOD<br>0  | SOD<br>0 | SSM<br>0 | SSI<br>0 |

Table 11. Miscellaneous Register Map and Reset Values

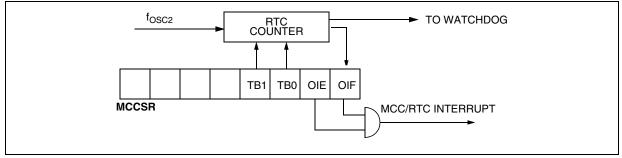

# 11.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (MCC/RTC)

The Main Clock Controller consists of a real time clock timer with interrupt capability

# 11.2.1 Real Time Clock Timer (RTC)

5/

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCC-SR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE-HALT mode when the HALT instruction is executed. See Section 8.4 "ACTIVE-HALT AND HALT MODES" on page 35 for more details.

#### Figure 34. Main Clock Controller (MCC/RTC) Block Diagram

## 16-BIT TIMER (Cont'd)

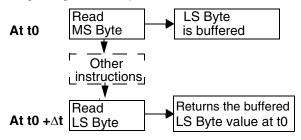

**16-bit read sequence:** (from either the Counter Register or the Alternate Counter Register).

#### Beginning of the sequence

Sequence completed

The user must read the MS Byte first, then the LS Byte value is buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

5/

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true. Clearing the overflow interrupt request is done in two steps:

1. Reading the SR register while the TOF bit is set. 2. An access (read or write) to the CLR register.

**Notes:** The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (Device awakened by an interrupt) or from the reset count (Device awakened by a Reset).

#### 11.3.3.2 External Clock

The external clock (where available) is selected if CC0=1 and CC1=1 in CR2 register.

The status of the EXEDG bit in the CR2 register determines the type of level transition on the external clock pin EXTCLK that will trigger the free running counter.

The counter is synchronised with the falling edge of the internal CPU clock.

A minimum of four falling edges of the CPU clock must occur between two consecutive active edges of the external clock; thus the external clock frequency must be less than a quarter of the CPU clock frequency.

# 16-BIT TIMER (Cont'd)

#### Notes:

- 1. After a processor write cycle to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. If the OC*i*E bit is not set, the OCMP*i* pin is a general I/O port and the OLVL*i* bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- When the timer clock is f<sub>CPU</sub>/2, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value (see Figure 42 on page 63). This behaviour is the same in OPM or PWM mode.

When the timer clock is f<sub>CPU</sub>/4, f<sub>CPU</sub>/8 or in external clock mode, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value plus 1 (see Figure 43 on page 63).

- 4. The output compare functions can be used both for generating external events on the OCMP*i* pins even if the input capture mode is also used.

- 5. The value in the 16-bit OC*i*R register and the OLV*i* bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

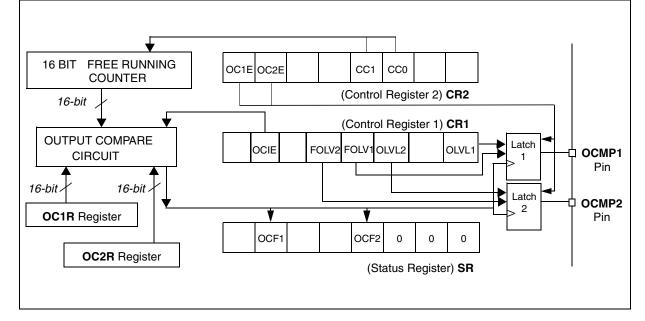

#### Figure 41. Output Compare Block Diagram

#### Forced Compare Output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit=1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

## 16-BIT TIMER (Cont'd)

#### 11.3.7 Register Description

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

#### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = ICIE Input Capture Interrupt Enable.

0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.*

0: Interrupt is inhibited.

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

#### Bit 3 = FOLV1 Forced Output Compare 1.

This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

#### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

#### Bit 0 = **OLVL1** *Output Level 1.*

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

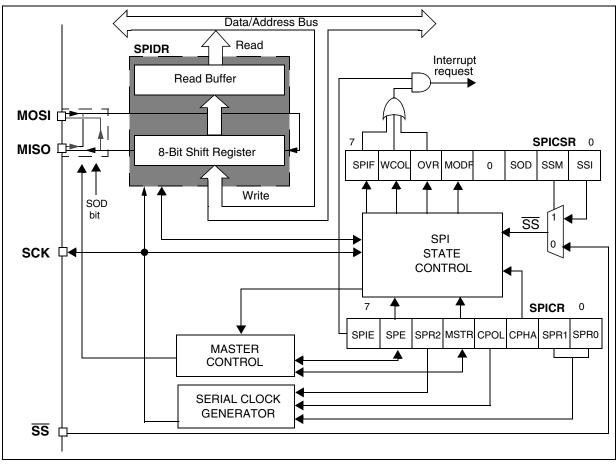

## Figure 46. Serial Peripheral Interface Block Diagram

# SERIAL PERIPHERAL INTERFACE (Cont'd)

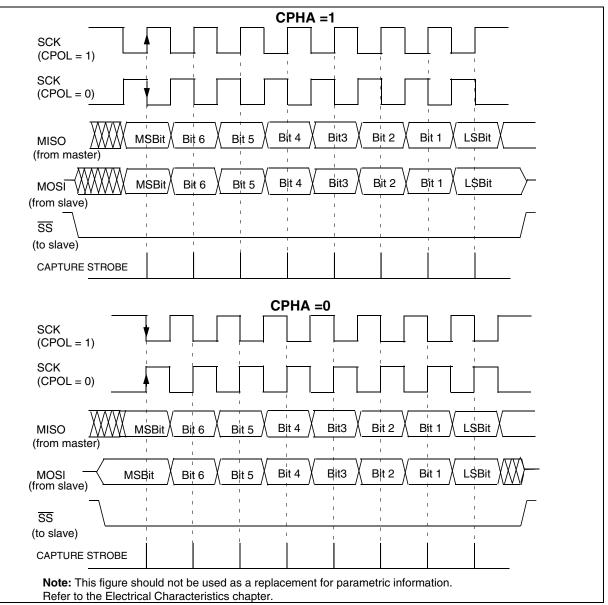

#### 11.4.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 50).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge

Figure 50, shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin, the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Figure 50. Data Clock Timing Diagram

# SERIAL PERIPHERAL INTERFACE (Cont'd)

# 11.4.5 Error Flags

#### 11.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device has its SS pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the Device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the Device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the SS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multi master configuration the Device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multi-master conflict and allows software to handle this using an interrupt routine and either perform to a reset or return to an application default state.

# 11.4.5.2 Overrun Condition (OVR)

An overrun condition occurs, when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### 11.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 11.4.3.2 "Slave Select Management" on page 78.

**Note:** a "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

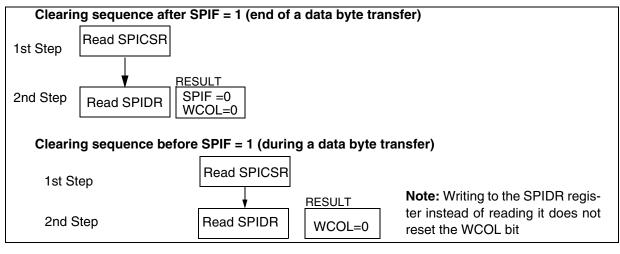

Clearing the WCOL bit is done through a software sequence (see Figure 51).

#### Figure 51. Clearing the WCOL bit (Write Collision Flag) Software Sequence

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 11.5.5 Low Power Modes

| Mode | Description                                                                             |

|------|-----------------------------------------------------------------------------------------|

| WAIT | No effect on SCI.                                                                       |

|      | SCI interrupts cause the device to exit from Wait mode.                                 |

|      | SCI registers are frozen.                                                               |

| HALT | In Halt mode, the SCI stops transmit-<br>ting/receiving until Halt mode is exit-<br>ed. |

## 11.5.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the inter-

| Interrupt Event                 | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|---------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty | TDRE          | TIE                      | Yes                  | No                   |

| Transmission Com-<br>plete      | тс            | TCIE                     | Yes                  | No                   |

| Received Data Ready to be Read  | RDRF          | RIE                      | Yes                  | No                   |

| Overrun Error Detected          | OR            |                          | Yes                  | No                   |

| Idle Line Detected              | IDLE          | ILIE                     | Yes                  | No                   |

| Parity Error                    | PE            | PIE                      | Yes                  | No                   |

rupt mask in the CC register is reset (RIM instruction).

# I<sup>2</sup>C INTERFACE (Cont'd)

#### How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

#### **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

#### 11.6.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

#### Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, **holding the SCL line low** (see Figure 59 Transfer sequencing EV5).

#### Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), **holding the SCL line low** (see Figure 59 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

**Note:** In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

#### Master Receiver

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

**Note:** In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### 11.7.6 Register Description

## **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   |       |      |      |   |     |     | 0   |

|-----|-------|------|------|---|-----|-----|-----|

| EOC | SPEED | ADON | SLOW | 0 | CH2 | CH1 | CH0 |

# Bit 7 = **EOC** End of Conversion

This bit is set by hardware. It is cleared by software reading the ADCDRH register or writing to any bit of the ADCCSR register.

0: Conversion is not complete

1: Conversion complete

# Bit 6 = **SPEED** A/D clock selection

This bit is set and cleared by software.

Table 22. A/D Clock Selection (See Note 1)

| f <sub>ADC</sub> Frequency    | SLOW | SPEED |

|-------------------------------|------|-------|

| f <sub>CPU</sub> (See Note 2) | 0    | 1     |

| f <sub>CPU</sub> /2           | 1    | 1     |

| ICPU/2                        | 0    | 0     |

| f <sub>CPU</sub> /4           | 1    | 0     |

<sup>1)</sup>The SPEED and SLOW bits must be updated before setting the ADON bit.

<sup>2)</sup>Use this setting only if  $f_{CPU} \le 4$  MHz

#### Bit 5 = ADON A/D Converter on

This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

# Bit 4 = **SLOW** A/D Clock Selection This bit is set and cleared by software. It works to-

gether with the SPEED bit. Refer to Table 22.

# Bit 2:0 = CH[2:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin | CH2 | CH1 | CH0 |

|-------------|-----|-----|-----|

| AINO        | 0   | 0   | 0   |

| AIN1        | 0   | 0   | 1   |

| AIN2        | 0   | 1   | 0   |

| AIN3        | 0   | 1   | 1   |

| AIN4        | 1   | 0   | 0   |

| AIN5        | 1   | 0   | 1   |

#### DATA REGISTER (ADCDRH)

Read Only

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

Bit 7:0 = D[9:2] MSB of Analog Converted Value

# DATA REGISTER (ADCDRL)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 = Reserved. Forced by hardware to 0.

#### Bit 1:0 = **D**[1:0] *LSB of Analog Converted Value*

# **15 DEVICE CONFIGURATION AND ORDERING INFORMATION**

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (ROM/FASTROM).

ST7226x devices are ROM versions. ST72P26x devices are Factory Advanced Service Technique ROM (FASTROM) versions: they are factory-programmed XFlash devices.

ST72F26x XFlash devices are shipped to customers with a default program memory content (FFh). The option bytes are programmed to enable the internal RC oscillator. The ROM/FASTROM factory coded parts contain the code supplied by the customer. This implies that FLASH devices have to be configured by the customer using the Option Bytes while the ROM/FASTROM devices are factoryconfigured.

# **15.1 OPTION BYTES**

The two option bytes allow the hardware configuration of the microcontroller to be selected.

The option bytes have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh.

In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

#### **USER OPTION BYTE 0**

OPT 7 = **WDG HALT** *Watchdog reset on HALT* This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

OPT 6 = **WDG SW** Hardware or software watchdog

This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT 5:4 = VD[1:0] Voltage detection selection These option bits enable the voltage detection block (LVD and AVD) with a selected threshold of the LVD and AVD.

| Configuration                     | VD1 | VD0 |

|-----------------------------------|-----|-----|

| LVD Off                           | 1   | 1   |

| Lowest Voltage Threshold (~3.05V) | 1   | 0   |

| Medium Voltage Threshold (~3.6V)  | 0   | 1   |

| Highest Voltage Threshold (~4.1V) | 0   | 0   |

OPT 3:2 = **SEC[1:0]** Sector 0 size definition These option bits indicate the size of sector 0 according to the following table.

| Sector 0 Size           | SEC1 | SEC0 |

|-------------------------|------|------|

| 0.5k                    | 0    | 0    |

| 1k                      | 0    | 1    |

| 2                       | 1    | 0    |

| <b>4k</b> <sup>1)</sup> | 1    | 1    |

Note 1: 4k available on FASTROM devices only.

#### OPT 1 = FMP\_R Read-out protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory.

Erasing the option bytes when the FMP\_R option is selected will cause the whole memory to be erased first, and the device can be reprogrammed. Refer to Section 4.5 and the ST7 Flash Programming Reference Manual for more details.

0: Read-out protection off

1: Read-out protection on

|                  | USER OPTION BYTE 0 |           |     |     |     |          |          | USER OPTION BYTE 1 |       |      |      |      |      |      |      |     |

|------------------|--------------------|-----------|-----|-----|-----|----------|----------|--------------------|-------|------|------|------|------|------|------|-----|

|                  | 7                  |           |     |     |     |          |          | 0                  | 7     |      |      |      |      |      |      | 0   |

|                  |                    |           |     |     | 050 | 050      |          |                    |       |      | OSC  | OSC  | OSC  | OSC  | OSC  | PLL |

|                  | HALT               | WDG<br>SW | VD1 | VD0 | SEC | SEC<br>0 | FMP<br>R | FMP<br>W           | EXTIT | Res. | TYPE | TYPE | RNGE | RNGE | RNGE | OFF |

|                  |                    | 0         |     |     |     | U        |          | •••                |       |      | 1    | 0    | 2    | 1    | 0    | UFF |

| Default<br>Value | 1                  | 1         | 1   | 1   | 1   | 1        | 0        | 0                  | 1     | 1    | 1    | 0    | 1    | 1    | 1    | 1   |