#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                            |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f264g2b6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents

\_

|    | 10.1  | I/O PORT INTERRUPT SENSITIVITY                            | . 45 |

|----|-------|-----------------------------------------------------------|------|

|    | 10.2  | I/O PORT ALTERNATE FUNCTIONS                              | . 45 |

|    | 10.3  | MISCELLANEOUS REGISTER DESCRIPTION                        | . 46 |

| 11 | ON-C  | HIP PERIPHERALS                                           | . 48 |

|    |       | WATCHDOG TIMER (WDG)                                      |      |

|    | 11.2  | MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (MCC/RTC)      | . 53 |

|    | 11.3  | 16-BIT TIMER                                              | . 55 |

|    | 11.4  | SERIAL PERIPHERAL INTERFACE (SPI)                         |      |

|    | 11.5  | SERIAL COMMUNICATIONS INTERFACE (SCI)                     | . 87 |

|    | 11.6  | I2C BUS INTERFACE (I2C)                                   | 103  |

|    | 11.7  | 10-BIT A/D CONVERTER (ADC)                                | 116  |

| 12 | INSTE | RUCTION SET                                               | 120  |

|    |       | CPU ADDRESSING MODES                                      |      |

|    | 12.2  | INSTRUCTION GROUPS                                        | 123  |

| 13 | ELEC  |                                                           | -    |

|    | 13.1  |                                                           |      |

|    |       | ABSOLUTE MAXIMUM RATINGS                                  |      |

|    |       | OPERATING CONDITIONS                                      |      |

|    | 13.4  | SUPPLY CURRENT CHARACTERISTICS                            | 131  |

|    | 13.5  | CLOCK AND TIMING CHARACTERISTICS                          |      |

|    | 13.6  | MEMORY CHARACTERISTICS                                    | 140  |

|    | 13.7  | EMC CHARACTERISTICS                                       | 141  |

|    | 13.8  | I/O PORT PIN CHARACTERISTICS                              | 144  |

|    | 13.9  | CONTROL PIN CHARACTERISTICS                               | 150  |

|    | 13.10 | TIMER PERIPHERAL CHARACTERISTICS                          | 152  |

|    | 13.11 | COMMUNICATION INTERFACE CHARACTERISTICS                   | 153  |

|    | 13.12 | 10-BIT ADC CHARACTERISTICS                                | 157  |

| 14 | PACK  | AGE CHARACTERISTICS                                       | 159  |

|    | 14.1  | PACKAGE MECHANICAL DATA                                   | 159  |

|    | 14.2  | THERMAL CHARACTERISTICS                                   | 160  |

|    | 14.3  | LEAD-FREE PACKAGE INFORMATION                             | 161  |

| 15 | DEVIC | CE CONFIGURATION AND ORDERING INFORMATION                 | 162  |

|    | 15.1  | OPTION BYTES                                              | 162  |

|    | 15.2  | DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 164  |

|    |       | DEVELOPMENT TOOLS                                         |      |

| 16 |       | VN LIMITATIONS                                            |      |

|    | 16.1  | ALL FLASH AND ROM DEVICES                                 | 168  |

|    | 16.2  | FLASH DEVICES ONLY                                        | 168  |

| 17 | REVIS | SION HISTORY                                              | 171  |

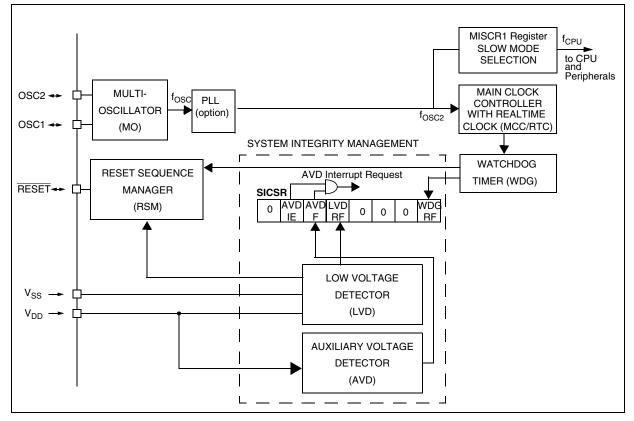

## **6 SUPPLY, RESET AND CLOCK MANAGEMENT**

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components. An overview is shown in Figure 10.

For more details, refer to dedicated parametric section.

#### **Main Features**

- Optional PLL for multiplying the frequency by 2 (not to be used with internal RC oscillator)

- Reset Sequence Manager (RSM)

- Multi-Oscillator Clock Management (MO)

- 4 Crystal/Ceramic resonator oscillators

- 1 Internal RC oscillator

- System Integrity Management (SI)

- Main supply Low Voltage Detector (LVD)

- Auxiliary Voltage Detector (AVD) with interrupt capability for monitoring the main supply

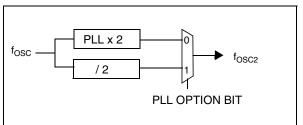

#### 6.1 PHASE LOCKED LOOP

If the clock frequency input to the PLL is in the 2 to 4 MHz range, the PLL can be used to multiply the frequency by two to obtain an  $f_{OSC2}$  of 4 to 8 MHz.

The PLL is enabled by option byte. If the PLL is disabled, then  $f_{OSC2} = f_{OSC}/2$ .

**Caution:** The PLL is not recommended for applications where timing accuracy is required. See "PLL Characteristics" on page 139.

#### Figure 9. PLL Block Diagram

## Figure 10. Clock, Reset and Supply Block Diagram

## **7 INTERRUPTS**

#### 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non-maskable events: RESET and TRAP

This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

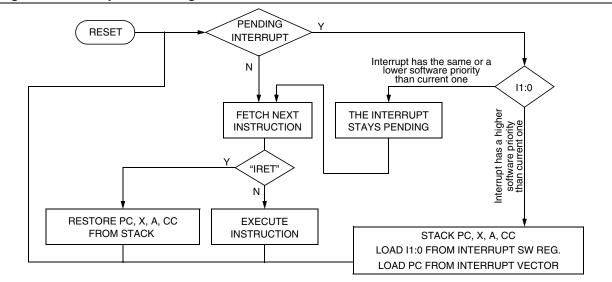

#### 7.2 MASKING AND PROCESSING FLOW

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of each interrupt vector (see Table 4). The processing flow is shown in Figure 16

#### Figure 16. Interrupt Processing Flowchart

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

#### Table 4. Interrupt Software Priority Levels

| Interrupt software priority   | Level | l1 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ★     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

#### POWER SAVING MODES (Cont'd)

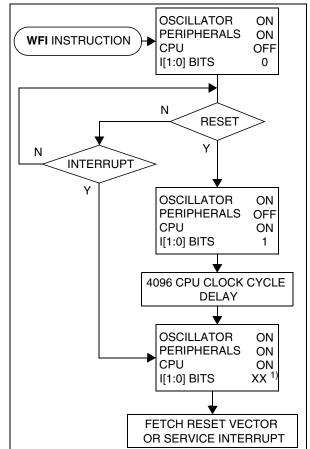

#### 8.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the "WFI" ST7 software instruction.

All peripherals remain active. During WAIT mode, the I [1:0] bits in the CC register are forced to '10b', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or Reset occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 22.

#### Note:

1. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set during the interrupt routine and cleared when the CC register is popped.

## WATCHDOG TIMER (Cont'd)

**\$7**

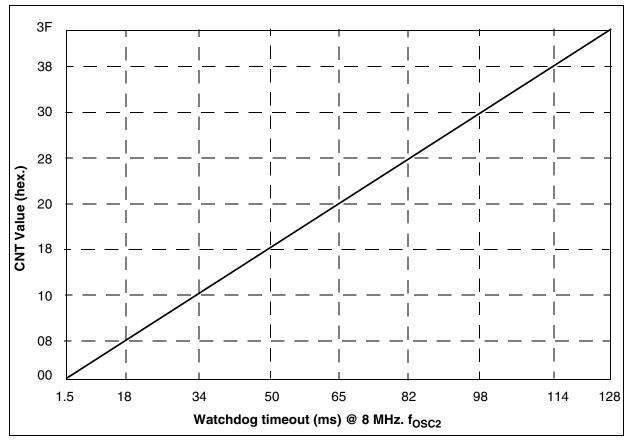

#### 11.1.4 How to Program the Watchdog Timeout

Figure 32 shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If

Figure 32. Approximate Timeout Duration

more precision is needed, use the formulae in Figure 33.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

#### **16-BIT TIMER** (Cont'd)

3. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and

#### 11.3.4 Low Power Modes

ICF1 can also generates interrupt if ICIE is set.

4. When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

| Mode | Description                                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.                                                                                                                                                                                                                                                                                                                              |

|      | Timer interrupts cause the Device to exit from WAIT mode.                                                                                                                                                                                                                                                                                               |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                                      |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the Device is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the Device is woken up by a RESET.                                                                                  |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequent-<br>ly, when the Device is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and<br>the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

#### 11.3.5 Interrupts

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    | ICF1          | ICIE                     | Yes                  | No                   |

| Input Capture 2 event                              | ICF2          | ICIE                     | Yes                  | No                   |

| Output Compare 1 event (not available in PWM mode) | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) | OCF2          | OULE                     | Yes                  | No                   |

| Timer Overflow event                               | TOF           | TOIE                     | Yes                  | No                   |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

#### 11.3.6 Summary of Timer modes

| MODES                       | AVAILABLE RESOURCES |                               |                  |                         |  |  |

|-----------------------------|---------------------|-------------------------------|------------------|-------------------------|--|--|

| MODES                       | Input Capture 1     | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |

| Input Capture (1 and/or 2)  | Yes                 | Yes                           | Yes              | Yes                     |  |  |

| Output Compare (1 and/or 2) | Yes                 | Yes                           | Yes              | Yes                     |  |  |

| One Pulse Mode              | No                  | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |

| PWM Mode                    | No                  | Not Recommended <sup>3)</sup> | No               | No                      |  |  |

<sup>1)</sup> See note 4 in Section 11.3.3.5 "One Pulse Mode" on page 64

<sup>2)</sup> See note 5 in Section 11.3.3.5 "One Pulse Mode" on page 64

<sup>3)</sup> See note 4 in Section 11.3.3.6 "Pulse Width Modulation Mode" on page 66

## SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.4.3.1 Functional Description

57

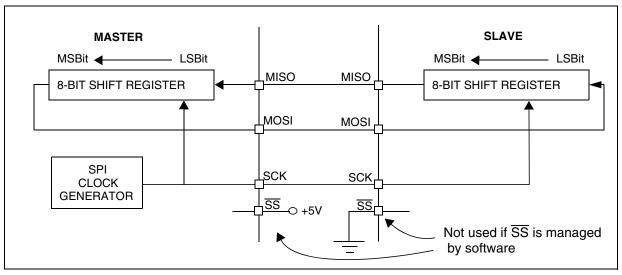

A basic example of interconnections between a single master and a single slave is illustrated in Figure 47.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device re-

Figure 47. Single Master/ Single Slave Application

sponds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 50) but master and slave must be programmed with the same timing mode.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

# 11.4.5.4 Single Master and Multimaster Configurations

There are two types of SPI systems:

- Single Master System

- Multimaster System

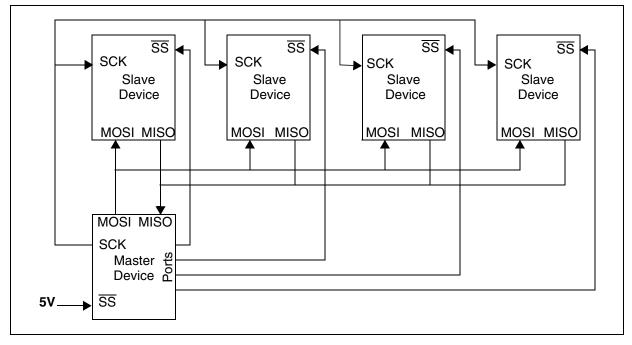

#### Single Master System

A typical single master system may be configured, using a device as the master and four devices as slaves (see Figure 52).

The master device selects the individual slave devices by using four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

#### Multi-Master System

A multi-master system may also be configured by the user. Transfer of master control could be implemented using a handshake method through the I/O ports or by an exchange of code messages through the serial peripheral interface system.

The multi-master system is principally handled by the MSTR bit in the SPICR register and the MODF bit in the SPICSR register.

## **11.5 SERIAL COMMUNICATIONS INTERFACE (SCI)**

#### 11.5.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 11.5.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud.

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

57/

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

#### **11.5.3 General Description**

The interface is externally connected to another device by two pins (see Figure 54):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete.

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates,

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies.

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 11.5.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 53).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit or after the break frame) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 54).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set i.e. before writing the next byte in the SCIDR.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

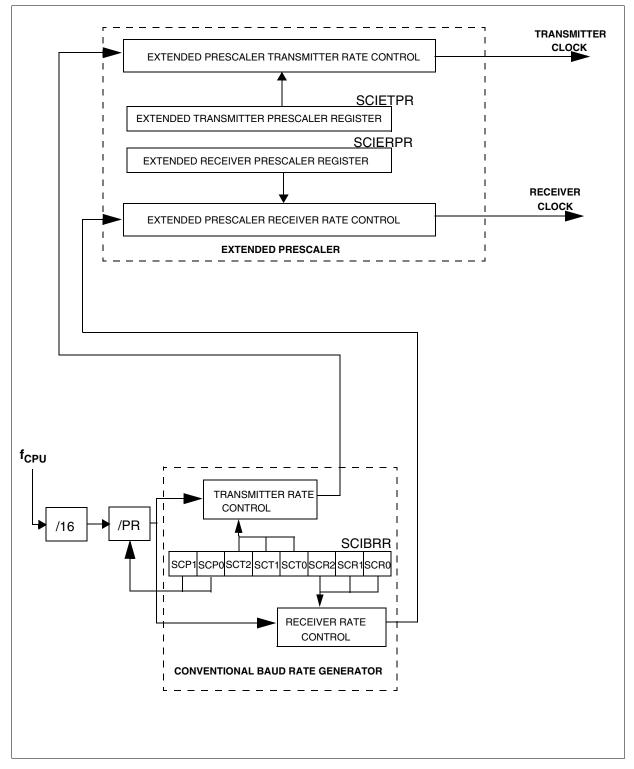

#### Figure 55. SCI Baud Rate and Extended Prescaler Block Diagram

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### **Framing Error**

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

- A break is received.

When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

#### 11.5.4.4 Conventional Baud Rate Generation

The baud rate for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows:

$$Tx = \frac{f_{CPU}}{(16*PR)*TR} \qquad Rx = \frac{f_{CPU}}{(16*PR)*RR}$$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits) TR = 1, 2, 4, 8, 16, 32, 64,128 (see SCT[2:0] bits) RR = 1, 2, 4, 8, 16, 32, 64,128 (see SCR[2:0] bits)

All these bits are in the SCIBRR register.

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR=13 and TR=RR=1, the transmit and receive baud rates are 38400 baud.

**Note:** the baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

#### 11.5.4.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 55.

The output clock rate sent to the transmitter or to the receiver will be the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCIERPR or the SCIETPR register. **Note:** the extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \cdot ETPR^{*}(PR^{*}TR)} Rx = \frac{f_{CPU}}{16 \cdot ERPR^{*}(PR^{*}RR)}$$

with:

ETPR = 1,..,255 (see SCIETPR register)

ERPR = 1,.. 255 (see SCIERPR register)

#### 11.5.4.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non addressed receivers.

The non addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits can not be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

Receiver wakes-up by Idle Line detection when the Receive line has recognised an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes-up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

**Caution**: In Mute mode, do not write to the SCICR2 register. If the SCI is in Mute mode during the read operation (RWU=1) and a address mark wake up event occurs (RWU is reset) before the write operation, the RWU bit will be set again by this write operation. Consequently the address byte is lost and the SCI is not woken up from Mute mode.

57

## I<sup>2</sup>C INTERFACE (Cont'd)

#### How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

#### **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

#### 11.6.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

#### Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, **holding the SCL line low** (see Figure 59 Transfer sequencing EV5).

#### Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), **holding the SCL line low** (see Figure 59 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

**Note:** In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

#### Master Receiver

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 59 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

**Note:** In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

## SUPPLY CURRENT CHARACTERISTICS (Cont'd)

## 13.4.4 On-chip peripherals

| Symbol               | Parameter                                        | Co                     | onditions             | Тур | Unit |

|----------------------|--------------------------------------------------|------------------------|-----------------------|-----|------|

| 1                    | 16-bit Timer supply current <sup>1)</sup>        | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 200 |      |

| IDD(TIM)             |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 300 |      |

| 1                    | SPI supply current <sup>2)</sup>                 | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 200 |      |

| DD(SPI)              |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 250 |      |

| 1                    | SCI supply current <sup>3)</sup>                 | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 350 |      |

| IDD(SCI)             | Set supply current                               | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 650 | μA   |

| I                    | I2C supply current <sup>4)</sup>                 | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 350 |      |

| DD(I2C)              |                                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 500 |      |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>5)</sup> | f <sub>ADC</sub> =4MHz | V <sub>DD</sub> =3.0V | 500 |      |

|                      |                                                  | ADC-411112             | V <sub>DD</sub> =5.0V | 600 |      |

#### Notes:

1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer counter running at  $f_{CPU}/2$ ) and timer counter stopped (only TIMD bit set). Data valid for one timer.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to FFh). This measurement includes the pad toggling consumption.

Data based on a differential I<sub>DD</sub> measurement between SCI running at maximum speed configuration (500 kbaud, continuous transmission of AA +RE enabled and SCI off. This measurement includes the pad toggling consumption.

4. Data based on a differential I<sub>DD</sub> measurement between reset configuration (I2C disabled) and a permanent I2C master communication at 300kHz (data sent equal to AAh). This measurement includes the pad toggling consumption (4.7kOhm external pull-up on clock and data lines).

5. Data based on a differential I<sub>DD</sub> measurement between reset configuration (ADC off) and continuous A/D conversion (f<sub>ADC</sub>=4MHz).

57

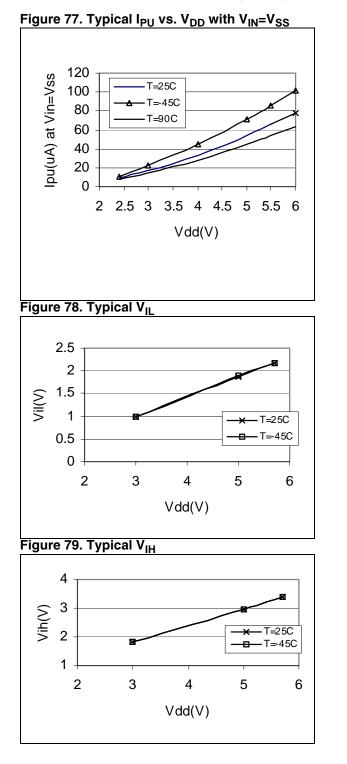

#### I/O PORT PIN CHARACTERISTICS (Cont'd)

## I/O PORT PIN CHARACTERISTICS (Cont'd)

## 13.8.2 Output Driving Current

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified

| Symbol                          | Parameter                                                                             |                   | Conditions                                 | Min                  | Max  | Unit |

|---------------------------------|---------------------------------------------------------------------------------------|-------------------|--------------------------------------------|----------------------|------|------|

|                                 | Output low level voltage for a standard I/O pin                                       |                   | I <sub>IO</sub> =+5mA                      |                      | 1.2  |      |

| V <sub>OL</sub> <sup>1)</sup>   | when 8 pins are sunk at same time<br>Output low level voltage for a high sink I/O pin |                   | I <sub>IO</sub> =+2mA                      |                      | 0.5  |      |

| VOL                             |                                                                                       | =5V               | I <sub>IO</sub> =+20mA,                    |                      | 1.3  |      |

|                                 | when 4 pins are sunk at same time                                                     | V <sub>DD</sub> : | I <sub>IO</sub> =+8mA                      |                      | 0.75 |      |

| V <sub>OH</sub> <sup>2)</sup>   | Output high level voltage for an I/O pin                                              | <b>_</b>          | I <sub>IO</sub> =-5mA,                     | V <sub>DD</sub> -1.6 |      |      |

| VОН                             | when 4 pins are sourced at same time                                                  |                   | I <sub>IO</sub> =-2mA                      | V <sub>DD</sub> -0.8 |      |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O pin when 8 pins are sunk at same time     |                   | I <sub>IO</sub> =+2mA                      |                      | 0.6  |      |

| VOL                             | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time    | 3.3V              | I <sub>IO</sub> =+8mA                      |                      | 0.6  | V    |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time      | V <sub>DD</sub> = | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤85°C | V <sub>DD</sub> -0.8 |      |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O pin when 8 pins are sunk at same time     |                   | I <sub>IO</sub> =+2mA                      |                      | 0.7  |      |

| VOL /                           | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time    | =2.7V             | I <sub>IO</sub> =+8mA                      |                      | 0.7  |      |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time         | V <sub>DD</sub> = | I <sub>IO</sub> =-2mA                      | V <sub>DD</sub> -0.9 |      |      |

#### Notes:

1. The  $I_{\rm IO}$  current sunk must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of  $I_{\rm IO}$  (I/O ports and control pins) must not exceed  $I_{\rm VSS}$ .

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins does not have V<sub>OH</sub>.

3. Not tested in production, based on characterization results.

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

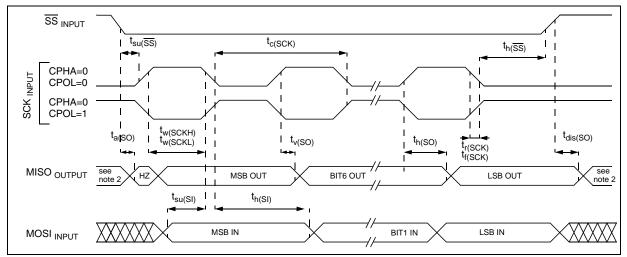

#### Figure 94. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

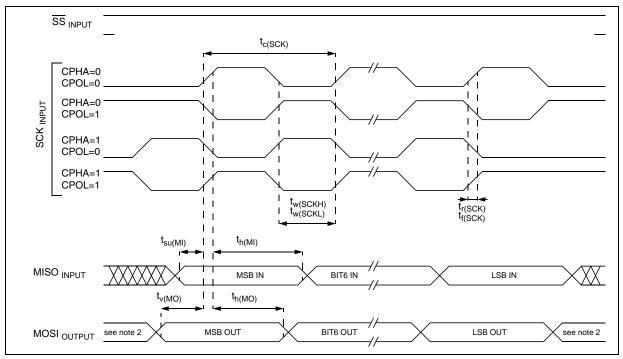

## Figure 95. SPI Master Timing Diagram 1)

#### Notes:

1. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

**لركم**

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

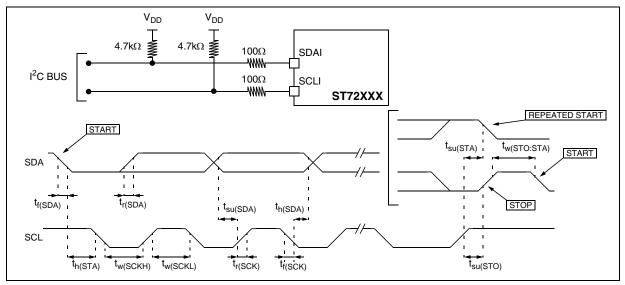

## 13.11.2 I<sup>2</sup>C - Inter IC Control Interface

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics

(SDAI and SCLI). Refer to Table 26 for the speed conditions. The ST7  $I^2C$  interface meets the requirements of the Standard  $I^2C$  communication protocol described in the following table.

| Cymhol                                     | Parameter                               | Standard          | Standard mode I <sup>2</sup> C |                      | Fast mode I <sup>2</sup> C <sup>5)</sup> |      |

|--------------------------------------------|-----------------------------------------|-------------------|--------------------------------|----------------------|------------------------------------------|------|

| Symbol                                     | Parameter                               | Min <sup>1)</sup> | Max <sup>1)</sup>              | Min <sup>1)</sup>    | Max <sup>1)</sup>                        | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7               |                                | 1.3                  |                                          |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0               |                                | 0.6                  |                                          | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250               |                                | 100                  |                                          |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 3)              |                                | 0 <sup>2)</sup>      | 900 <sup>3)</sup>                        |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                   | 1000                           | 20+0.1C <sub>b</sub> | 300                                      | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                   | 300                            | 20+0.1C <sub>b</sub> | 300                                      |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0               |                                | 0.6                  |                                          |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7               |                                | 0.6                  |                                          | μs   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0               |                                | 0.6                  |                                          | μS   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7               |                                | 1.3                  |                                          | μS   |

| Cb                                         | Capacitive load for each bus line       |                   | 400                            |                      | 400                                      | pF   |

## Figure 96. Typical Application with I<sup>2</sup>C Bus and Timing Diagram <sup>4)</sup>

#### Notes:

1. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

2. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

5. At 4MHz f<sub>CPU</sub>, max.I<sup>2</sup>C speed (400kHz) is not achievable. In this case, max. I<sup>2</sup>C speed will be approximately 260KHz.

## TRANSFER OF CUSTOMER CODE (Cont'd)

| ST7<br>Customer                                                                                                    | 72264 ROM/FASTROM MICROC<br>(Last update: 15 Jan                                                                                                                   | ONTROLLER OPTION LIST<br>nuary 2004)                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                                                                                                            |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Contact<br>Phone No<br>Reference /ROM or FAS                                                                       | TROM Code*                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                    | e is assigned by STMicroelectronics.<br>19 formatHex extension cannot be pr                                                                                        | rocessed.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Device Type/Memory                                                                                                 | Size/Package (check only one option                                                                                                                                | n):                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ROM DEVICE:                                                                                                        | 8K                                                                                                                                                                 | 4K                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SO28:  <br>SDIP32:                                                                                                 | []ST72264G2 []ST72262G2  <br>[]ST72264G2 []ST72262G2                                                                                                               | []ST72264G1 []ST72262G1 []ST72260G1<br>[]ST72264G1 []ST72262G1 []ST72260G1                                                                                                                                                                                                                                                                                                                                                             |

| FASTROM DEVICE:                                                                                                    | 8K                                                                                                                                                                 | 4K                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SO28:  <br>SDIP32:  <br>BGA6x6 <sup>:</sup>                                                                        | []ST72P264G2 []ST72P262G2 <br>[]ST72P264G2 []ST72P262G2 <br>[]ST72P264G2 []                                                                                        | []ST72P264G1 []ST72P262G1 []ST72P260G1<br>[]ST72P264G1 []ST72P262G1 []ST72P260G1                                                                                                                                                                                                                                                                                                                                                       |

| DIE FORM:                                                                                                          | <br>[]8K                                                                                                                                                           | [] 4K                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditioning (check only                                                                                           | one option, do not specify for DIP pac                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                    |                                                                                                                                                                    | <br>_<br>[ ] 0°C to + 70°C<br>[ ] - 10°C to + 85°C (except BGA)                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                    |                                                                                                                                                                    | [] - 40°C to + 85°C (except BGA)<br>[] Tested at 25°C only                                                                                                                                                                                                                                                                                                                                                                             |

| Watchdog Reset on Halt<br>Watchdog Selection:<br>VD Reset                                                          | [] Software Activation                                                                                                                                             | ] No Reset<br>] Hardware Activation<br>] Enabled:<br>[ ] Highest threshold                                                                                                                                                                                                                                                                                                                                                             |

| Sector 0 Size:<br>Readout Protection:<br>Flash Write Protection:<br>External Interrupt:<br>Clock Source Selection: | [] Disabled []<br>[] Disabled []<br>[] Port A&C on ei0 interrupt ve<br>[] Port A on ei0 interrupt vecto<br>[] Resonator: [] VL<br>[] LF<br>[] Mi<br>[] Mi<br>[] Mi | [] Ingliest threshold<br>[] Medium threshold<br>[] Lowest threshold<br>] IK [] 2K [] 4K (FASTROM only)<br>] Enabled<br>] Enabled (FASTROM only)<br>ector, Port B on ei1 (PA&C_PB)<br>or, Port B&C on ei1 (PA_PB&C)<br>.P: Very Low power resonator (32 to 100 kHz)<br>P: Low power resonator (1 to 2 MHz)<br>P: Medium power resonator (2 to 4 MHz)<br>S: Medium speed resonator (4 to 8 MHz)<br>S: High speed resonator (8 to 16 MHz) |

|                                                                                                                    | [] Internal RC Oscillator <sup>1)</sup><br>[] External Clock<br>[] Disabled [] Er<br>e in the application:                                                         | nabled                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>o</b> :                                                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Note 1: Use of the PLL v                                                                                           | vith the internal RC oscillator is not sup                                                                                                                         | ported.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ortant note: Not all cont<br>ase download the lates                                                                | •                                                                                                                                                                  | on page 164 for the list of supported part numbers.                                                                                                                                                                                                                                                                                                                                                                                    |

57

## 15.3.2 PACKAGE/SOCKET FOOTPRINT PROPOSAL

## Table 30. Suggested List of SDIP32 Socket Types

| Package / Probe     |         | Adaptor / Socket Reference | Same<br>Footprint | Socket Type |

|---------------------|---------|----------------------------|-------------------|-------------|

| SDIP32<br>EMU PROBE | TEXTOOL | 232-1291-00                | х                 | Textool     |

#### Table 31. Suggested List of SO28 Socket Types

| Package / Probe | Adaptor / Socket Reference                                      | Same<br>Footprint | Socket Type |

|-----------------|-----------------------------------------------------------------|-------------------|-------------|

| SO28            | YAMAICHI IC51-0282-334-1                                        |                   | Clamshell   |

| EMU PROBE       | Adapter from SO28 to SDIP32 footprint (delivered with emulator) | Х                 | SMD to SDIP |

## Table 32. Suggested LFBGA Socket Type

57

| Package    | Socket Reference          |  |

|------------|---------------------------|--|

| LFBGA 6 X6 | ENPLAS OTB-36(144)-0.8-04 |  |