# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 45                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 16K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5602df1clh3r |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

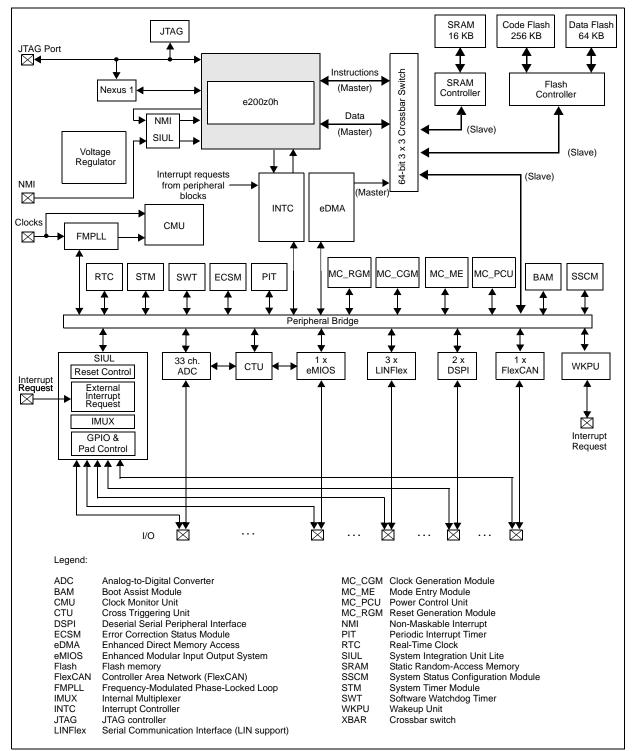

**Block diagram**

### Table 1. MPC5602D device comparison (continued)

| Feature | Device      |                  |             |             |  |  |  |  |

|---------|-------------|------------------|-------------|-------------|--|--|--|--|

|         | MPC5601DxLH | MPC5601DxLL      | MPC5602DxLH | MPC5602DxLL |  |  |  |  |

| Debug   |             | JTAG             |             |             |  |  |  |  |

| Package | 64 LQFP     | 100 LQFP 64 LQFP |             | 100 LQFP    |  |  |  |  |

<sup>1</sup> Refer to eMIOS chapter of device reference manual for information on the channel configuration and functions.

<sup>2</sup> Type X = MC + MCB + OPWMT + OPWMB + OPWFMB + SAIC + SAOC

<sup>3</sup> Type Y = OPWMT + OPWMB + SAIC + SAOC

<sup>4</sup> Type G = MCB + IPWM + IPM + DAOC + OPWMT + OPWMB + OPWFMB + OPWMCB + SAIC + SAOC

<sup>5</sup> Type H = IPWM + IPM + DAOC + OPWMT + OPWMB + SAIC + SAOC

<sup>6</sup> I/O count based on multiplexing with peripherals

## 2 Block diagram

Figure 1 shows a top-level block diagram of the MPC5602D device series.

#### Figure 1. MPC5602D series block diagram

Table 2 summarizes the functions of all blocks present in the MPC5602D series of microcontrollers. Please note that the presence and number of blocks varies by device and package.

| Block                                         | Function                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)             | Multi-channel, 12-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock generation module<br>(MC_CGM)           | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Clock monitor unit (CMU)                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                        | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.                                                                                                                                                   |

| Deserial serial peripheral interface (DSPI)   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access<br>(eDMA)       | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels.                                                                                                                                                                                           |

| Enhanced modular input output system (eMIOS)  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Error correction status module<br>(ECSM)      | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Flash memory                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock      | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Interrupt controller (INTC)                   | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller (JTAGC)                       | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                            | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Mode entry module (MC_ME)                     | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Non-maskable interrupt (NMI)                  | Handles external events that must produce an immediate response, such as power down detection                                                                                                                                                                                                                     |

| Periodic interrupt timer (PIT)                | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                         |

| Power control unit (MC_PCU)                   | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

### Table 2. MPC5602D series block summary

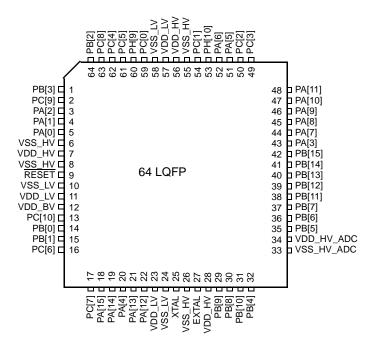

Figure 3 shows the MPC5602D in the 64 LQFP package.

Figure 3. 64 LQFP pin configuration (top view)

### 3.2 Pad configuration during reset phases

All pads have a fixed configuration under reset.

During the power-up phase, all pads are forced to tristate.

After power-up phase, all pads are forced to tristate with the following exceptions:

- PA[9] (FAB) is pull-down. Without external strong pull-up the device starts fetching from flash.

- PA[8] (ABS[0]) is pull-up.

- RESET pad is driven low. This is pull-up only after PHASE2 reset completion.

- JTAG pads (TCK, TMS and TDI) are pull-up while TDO remains tristate.

- Precise ADC pads (PB[7:4] and PD[11:0]) are left tristate (no output buffer available).

- Main oscillator pads (EXTAL, XTAL) are tristate.

### 3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Two dedicated pins are used for 1.2 V regulator stabilization.

#### Package pinouts and signal descriptions

| Dort nin | Function                                                                                                                        | Pin number       |                        |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|--|--|

| Port pin | Function                                                                                                                        | 64 LQFP          | 100 LQFP               |  |  |

| VDD_HV   | Digital supply voltage                                                                                                          | 7, 28, 34, 56    | 15, 37, 52, 70, 84     |  |  |

| VSS_HV   | Digital ground                                                                                                                  | 6, 8, 26, 33, 55 | 14, 16, 35, 51, 69, 83 |  |  |

| VDD_LV   | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{SS_{LV}}$ pin. <sup>1</sup> | 11, 23, 57       | 19, 32, 85             |  |  |

| VSS_LV   | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV}$ pin. <sup>1</sup>   | 10, 24, 58       | 18, 33, 86             |  |  |

| VDD_BV   | Internal regulator supply voltage                                                                                               | 12               | 20                     |  |  |

### Table 3. Voltage supply pin descriptions

<sup>1</sup> A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device datasheet for details).

### 3.4 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$S = Slow^1$

$M = Medium^{1 \ 2}$

$F = Fast^{1 2}$

$I = Input only with analog feature^1$

J = Input/Output ('S' pad) with analog feature

X = Oscillator

### 3.5 System pins

The system pins are listed in Table 4.

### Table 4. System pin descriptions

| Port pin  | Function                                                                                                                                                                                        | I/O       | Pad type  | RESET                                       | Pin number |          |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|---------------------------------------------|------------|----------|--|

| i ort pin | T unction                                                                                                                                                                                       | direction | i au type | configuration                               | 64 LQFP    | 100 LQFP |  |

| RESET     | Bidirectional reset with Schmitt-Trigger<br>characteristics and noise filter.                                                                                                                   | I/O       | Μ         | Input, weak<br>pull-up only<br>after PHASE2 | 9          | 17       |  |

| EXTAL     | Analog output of the oscillator amplifier circuit,<br>when the oscillator is not in bypass mode.<br>Analog input for the clock generator when the<br>oscillator is in bypass mode. <sup>1</sup> | I/O       | Х         | Tristate                                    | 27         | 36       |  |

| XTAL      | Analog input of the oscillator amplifier circuit.<br>Needs to be grounded if oscillator is used in<br>bypass mode. <sup>1</sup>                                                                 | I         | Х         | Tristate                                    | 25         | 34       |  |

<sup>1</sup> Refer to the relevant section of the device datasheet.

<sup>1.</sup> See the I/O pad electrical characteristics in the device datasheet for details.

<sup>2.</sup> All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium (see the PCR[SRC] description in the device reference manual).

### Package pinouts and signal descriptions

|          |         |                                                   |                                                              |                                                  |                                        |             | r<br>tion              | Pin number |          |  |

|----------|---------|---------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------|----------------------------------------|-------------|------------------------|------------|----------|--|

| Port pin | PCR     | Alternate<br>function <sup>1</sup>                | Function                                                     | Peripheral                                       | I/O<br>direction <sup>2</sup>          | Pad<br>type | RESET<br>configuration | 64 LQFP    | 100 LQFP |  |

| PA[7]    | PCR[7]  | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[7]<br>E0UC[7]<br>—<br>EIRQ[2]<br>ADC1_S[1]              | SIUL<br>eMIOS_0<br><br>SIUL<br>ADC               | I/O<br>I/O<br>—<br>I<br>I              | S           | Tristate               | 44         | 71       |  |

| PA[8]    | PCR[8]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>N/A <sup>5</sup> | GPIO[8]<br>E0UC[8]<br>E0UC[14]<br>—<br>EIRQ[3]<br>ABS[0]     | SIUL<br>eMIOS_0<br>eMIOS_0<br><br>SIUL<br>BAM    | I/O<br>I/O<br>—<br>I<br>I              | S           | Input, weak<br>pull-up | 45         | 72       |  |

| PA[9]    | PCR[9]  | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>5</sup>      | GPIO[9]<br>E0UC[9]<br>—<br>CS2_1<br>FAB                      | SIUL<br>eMIOS_0<br><br>DSPI_1<br>BAM             | I/O<br>I/O<br>—<br>I/O<br>I            | S           | Pull-down              | 46         | 73       |  |

| PA[10]   | PCR[10] | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[10]<br>E0UC[10]<br>—<br>LIN2TX<br>ADC1_S[2]             | SIUL<br>eMIOS_0<br><br>LINFlex_2<br>ADC          | I/O<br>I/O<br>—<br>0<br>I              | S           | Tristate               | 47         | 74       |  |

| PA[11]   | PCR[11] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—           | GPIO[11]<br>E0UC[11]<br>—<br>EIRQ[16]<br>ADC1_S[3]<br>LIN2RX | SIUL<br>eMIOS_0<br>—<br>SIUL<br>ADC<br>LINFlex_2 | I/O<br>I/O<br>—<br>I<br>I<br>I         | S           | Tristate               | 48         | 75       |  |

| PA[12]   | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[12]<br>—<br>—<br>EIRQ[17]<br>SIN_0                      | SIUL<br>—<br>—<br>SIUL<br>DSPI_0                 | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S           | Tristate               | 22         | 31       |  |

| PA[13]   | PCR[13] | AF0<br>AF1<br>AF2<br>AF3                          | GPIO[13]<br>SOUT_0<br>—<br>CS3_1                             | SIUL<br>DSPI_0<br><br>DSPI_1                     | I/O<br>O<br>—<br>I/O                   | М           | Tristate               | 21         | 30       |  |

| PA[14]   | PCR[14] | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[14]<br>SCK_0<br>CS0_0<br>E0UC[0]<br>EIRQ[4]             | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>SIUL      | I/O<br>I/O<br>I/O<br>I/O<br>I          | Μ           | Tristate               | 19         | 28       |  |

|          |         |                                    |                                                               |                               |                               |             | T<br>ttion             | Pin n   | umber    |  |

|----------|---------|------------------------------------|---------------------------------------------------------------|-------------------------------|-------------------------------|-------------|------------------------|---------|----------|--|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                      | Peripheral                    | I/O<br>direction <sup>2</sup> | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |  |

|          | Port D  |                                    |                                                               |                               |                               |             |                        |         |          |  |

| PD[0]    | PCR[48] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[48]<br>—<br>—<br>—<br>WKPU[27] <sup>3</sup><br>ADC1_P[4] | SIUL<br>—<br>—<br>WKPU<br>ADC | <br> -<br> <br>               | Ι           | Tristate               |         | 41       |  |

| PD[1]    | PCR[49] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[49]<br>—<br>—<br>WKPU[28] <sup>3</sup><br>ADC1_P[5]      | SIUL<br>—<br>—<br>WKPU<br>ADC | <br><br>_<br> <br>            | Ι           | Tristate               | _       | 42       |  |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[50]<br>—<br>—<br>ADC1_P[6]                               | SIUL<br>   <br>ADC            | <br> -<br> <br>               | Ι           | Tristate               | _       | 43       |  |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[51]<br>—<br>—<br>ADC1_P[7]                               | SIUL<br> <br>ADC              | <br> -<br> <br>               | -           | Tristate               |         | 44       |  |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[52]<br>—<br>—<br>ADC1_P[8]                               | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | Ι           | Tristate               |         | 45       |  |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[53]<br>—<br>—<br>—<br>ADC1_P[9]                          | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | Ι           | Tristate               | _       | 46       |  |

| PD[6]    | PCR[54] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[54]<br>—<br>—<br>ADC1_P[10]                              | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | I           | Tristate               |         | 47       |  |

| PD[7]    | PCR[55] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[55]<br>—<br>—<br>ADC1_P[11]                              | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | Ι           | Tristate               | _       | 48       |  |

|          |         |                                    |                                                        |                                          |                               |             | r<br>ttion             | Pin n   | umber    |

|----------|---------|------------------------------------|--------------------------------------------------------|------------------------------------------|-------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                               | Peripheral                               | I/O<br>direction <sup>2</sup> | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PE[0]    | PCR[64] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[64]<br>E0UC[16]<br>—<br>—<br>WKPU[6] <sup>3</sup> | SIUL<br>eMIOS_0<br>—<br>WKPU             | I/O<br>I/O<br>—<br>I          | S           | Tristate               | _       | 6        |

| PE[1]    | PCR[65] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[65]<br>E0UC[17]<br>—                              | SIUL<br>eMIOS_0<br>—                     | I/O<br>I/O<br>—               | М           | Tristate               | _       | 8        |

| PE[2]    | PCR[66] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[66]<br>E0UC[18]<br>—<br>EIRQ[21]<br>SIN_1         | SIUL<br>eMIOS_0<br>—<br>SIUL<br>DSPI_1   | I/O<br>I/O<br>—<br>I<br>I     | Μ           | Tristate               | _       | 89       |

| PE[3]    | PCR[67] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[67]<br>E0UC[19]<br>SOUT_1<br>—                    | SIUL<br>eMIOS_0<br>DSPI_1<br>—           | I/O<br>I/O<br>O<br>—          | М           | Tristate               | _       | 90       |

| PE[4]    | PCR[68] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[68]<br>E0UC[20]<br>SCK_1<br>—<br>EIRQ[9]          | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>SIUL   | I/O<br>I/O<br>I/O<br>—<br>I   | М           | Tristate               | _       | 93       |

| PE[5]    | PCR[69] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[69]<br>E0UC[21]<br>CS0_1<br>MA[2]                 | SIUL<br>eMIOS_0<br>DSPI_1<br>ADC         | I/O<br>I/O<br>I/O<br>O        | М           | Tristate               | _       | 94       |

| PE[6]    | PCR[70] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[70]<br>E0UC[22]<br>CS3_0<br>MA[1]<br>EIRQ[22]     | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC<br>SIUL | I/O<br>I/O<br>O<br>I          | М           | Tristate               | _       | 95       |

| PE[7]    | PCR[71] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[71]<br>E0UC[23]<br>CS2_0<br>MA[0]<br>EIRQ[23]     | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC<br>SIUL | I/O<br>I/O<br>O<br>I          | Μ           | Tristate               | _       | 96       |

| PE[8]    | PCR[72] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[72]<br>—<br>E0UC[22]<br>—                         | SIUL<br>—<br>eMIOS_0<br>—                | I/O<br>—<br>I/O<br>—          | М           | Tristate               | —       | 9        |

.

| Symbol               |    | Parameter                                                                           | Conditions                                 | Va                    | Unit                  |    |

|----------------------|----|-------------------------------------------------------------------------------------|--------------------------------------------|-----------------------|-----------------------|----|

| Symbo                |    | Falameter                                                                           | Conditions                                 | Min Max               |                       |    |

| V <sub>DD_BV</sub>   | SR | Voltage on VDD_BV (regulator supply) pin                                            | _                                          | -0.3                  | 6.0                   | V  |

|                      |    | with respect to ground $(V_{SS})$                                                   | Relative to V <sub>DD</sub>                | $V_{DD} - 0.3$        | V <sub>DD</sub> + 0.3 |    |

| $V_{SS\_ADC}$        | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> ) | _                                          | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V  |

| $V_{DD\_ADC}$        | SR | Voltage on VDD_HV_ADC (ADC                                                          | _                                          | -0.3                  | 6.0                   | V  |

|                      |    | reference) pin with respect to ground (V $_{\rm SS}$ )                              | Relative to V <sub>DD</sub>                | $V_{DD} - 0.3$        | V <sub>DD</sub> + 0.3 |    |

| V <sub>IN</sub>      | SR | /oltage on any GPIO pin with respect to                                             |                                            | -0.3                  | 6.0                   | V  |

|                      |    | ground (V <sub>SS</sub> )                                                           | Relative to V <sub>DD</sub>                | $V_{DD}-0.3$          | V <sub>DD</sub> + 0.3 |    |

| I <sub>INJPAD</sub>  | SR | Injected input current on any pin during overload condition                         | _                                          | -10                   | 10                    | mA |

| I <sub>INJSUM</sub>  | SR | Absolute sum of all injected input currents during overload condition               | _                                          | -50                   | 50                    | mA |

| I <sub>AVGSEG</sub>  | SR | Sum of all the static I/O current within a                                          | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | —                     | 70                    | mA |

|                      |    | supply segment <sup>1</sup>                                                         | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —                     | 64                    |    |

| ICORELV              | SR | Low voltage static current sink through<br>VDD_BV                                   | _                                          | —                     | 150                   | mA |

| T <sub>STORAGE</sub> | SR | Storage temperature                                                                 | _                                          | -55                   | 150                   | °C |

<sup>1</sup> Supply segments are described in Section 4.7.5, I/O pad current specification.

### NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

### 4.5 Recommended operating conditions

| bl | с | Parameter  | Conditions | Va  | lue |

|----|---|------------|------------|-----|-----|

|    | • | Falalletei | Conditiono | Min | N   |

### Table 11. Recommended operating conditions (3.3 V)

|                              |                 |   |                                                                                               |   | Min                   | Max                   |   |

|------------------------------|-----------------|---|-----------------------------------------------------------------------------------------------|---|-----------------------|-----------------------|---|

| V <sub>SS</sub>              | SR              | — | Digital ground on VSS_HV pins                                                                 | — | 0                     | 0                     | V |

| V <sub>DD</sub> <sup>1</sup> | SR              |   | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | — | 3.0                   | 3.6                   | V |

| V <sub>SS_LV</sub>           | <sup>2</sup> SR |   | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _ | V <sub>SS</sub> - 0.1 | V <sub>SS</sub> + 0.1 | V |

Symbo

Unit

#### **Electrical characteristics**

| Table 2 | 21. I/O | weight <sup>1</sup> |

|---------|---------|---------------------|

|---------|---------|---------------------|

|        | 100 LQFP/64 LQFP     |         |         |         |  |  |  |

|--------|----------------------|---------|---------|---------|--|--|--|

| Pad    | Weigl                | nt 5 V  | Weigh   | t 3.3 V |  |  |  |

|        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 |  |  |  |

| PB[3]  | 9%                   | 9%      | 10%     | 10%     |  |  |  |

| PC[9]  | 8%                   | 8%      | 10%     | 10%     |  |  |  |

| PC[14] | 8%                   | 8%      | 10%     | 10%     |  |  |  |

| PC[15] | 8%                   | 11%     | 9%      | 10%     |  |  |  |

| PA[2]  | 8%                   | 8%      | 9%      | 9%      |  |  |  |

| PE[0]  | 7%                   | 7%      | 9%      | 9%      |  |  |  |

| PA[1]  | 7%                   | 7%      | 8%      | 8%      |  |  |  |

| PE[1]  | 7%                   | 10%     | 8%      | 8%      |  |  |  |

| PE[8]  | 6%                   | 9%      | 8%      | 8%      |  |  |  |

| PE[9]  | 6%                   | 6%      | 7%      | 7%      |  |  |  |

| PE[10] | 6%                   | 6%      | 7%      | 7%      |  |  |  |

| PA[0]  | 5%                   | 7%      | 6%      | 7%      |  |  |  |

| PE[11] | 5%                   | 5%      | 6%      | 6%      |  |  |  |

| PC[11] | 7%                   | 7%      | 9%      | 9%      |  |  |  |

| PC[10] | 8%                   | 11%     | 9%      | 10%     |  |  |  |

| PB[0]  | 8%                   | 11%     | 9%      | 10%     |  |  |  |

| PB[1]  | 8%                   | 8%      | 10%     | 10%     |  |  |  |

| PC[6]  | 8%                   | 8%      | 10%     | 10%     |  |  |  |

| PC[7]  | 8%                   | 8%      | 10%     | 10%     |  |  |  |

| PA[15] | 8%                   | 11%     | 9%      | 10%     |  |  |  |

| PA[14] | 7%                   | 11%     | 9%      | 9%      |  |  |  |

| PA[4]  | 7%                   | 7%      | 8%      | 8%      |  |  |  |

| PA[13] | 7%                   | 10%     | 8%      | 9%      |  |  |  |

| PA[12] | 7%                   | 7%      | 8%      | 8%      |  |  |  |

| PB[9]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

| PB[8]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

| PB[10] | 5%                   | 5%      | 6%      | 6%      |  |  |  |

| PD[0]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

| PD[1]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

| PD[2]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

| PD[3]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

| PD[4]  | 1%                   | 1%      | 1%      | 1%      |  |  |  |

|        | 100 LQFP/64 LQFP     |         |              |         |  |  |

|--------|----------------------|---------|--------------|---------|--|--|

| Pad    | Weigl                | nt 5 V  | Weight 3.3 V |         |  |  |

|        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0      | SRC = 1 |  |  |

| PC[0]  | 6%                   | 9%      | 7%           | 8%      |  |  |

| PE[2]  | 7%                   | 10%     | 8%           | 9%      |  |  |

| PE[3]  | 7%                   | 10%     | 9%           | 9%      |  |  |

| PC[5]  | 8%                   | 11%     | 9%           | 10%     |  |  |

| PC[4]  | 8%                   | 11%     | 9%           | 10%     |  |  |

| PE[4]  | 8%                   | 12%     | 10%          | 10%     |  |  |

| PE[5]  | 8%                   | 12%     | 10%          | 11%     |  |  |

| PE[6]  | 9%                   | 12%     | 10%          | 11%     |  |  |

| PE[7]  | 9%                   | 12%     | 10%          | 11%     |  |  |

| PC[12] | 9%                   | 13%     | 11%          | 11%     |  |  |

| PC[13] | 9%                   | 9%      | 11%          | 11%     |  |  |

| PC[8]  | 9%                   | 9%      | 11%          | 11%     |  |  |

| PB[2]  | 9%                   | 13%     | 11%          | 12%     |  |  |

### Table 21. I/O weight<sup>1</sup> (continued)

<sup>1</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% \text{ / } 5.0 \text{ V} \pm 10\%, \text{ } T_{A} = -40 \text{ to } 125 \text{ °C}, \text{ unless otherwise specified}$ <sup>2</sup> SRC: "Slew Rate Control" bit in SIU\_PCR

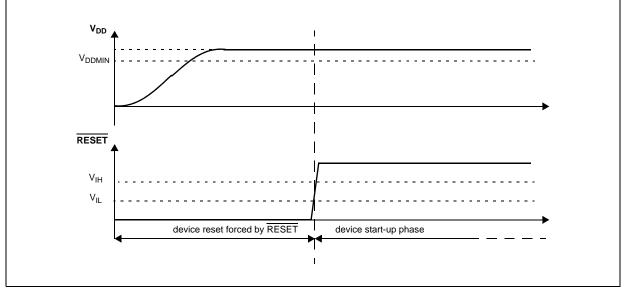

#### **RESET** electrical characteristics 4.8

The device implements a dedicated bidirectional RESET pin.

Figure 5. Start-up reset requirements

| Symbol                |    | с | Parameter                                                                 | Conditions <sup>1</sup>                                     |                  | Value            |                  | Unit |

|-----------------------|----|---|---------------------------------------------------------------------------|-------------------------------------------------------------|------------------|------------------|------------------|------|

|                       |    | C | Parameter                                                                 | Conditions                                                  | Min              | Тур              | Max              | Unit |

| C <sub>DEC1</sub>     | SR |   | Decoupling capacitance <sup>2</sup> ballast                               | $V_{DD_BV}/V_{SS_LV}$ pair:<br>$V_{DD_BV} = 4.5$ V to 5.5 V | 100 <sup>3</sup> | 470 <sup>4</sup> | _                | nF   |

|                       |    |   |                                                                           | $V_{DD_BV}/V_{SS_LV}$ pair:<br>$V_{DD_BV} = 3 V$ to 3.6 V   | 400              |                  |                  |      |

| C <sub>DEC2</sub>     | SR |   | Decoupling capacitance regulator supply                                   | V <sub>DD</sub> /V <sub>SS</sub> pair                       | 10               | 100              | —                | nF   |

| V <sub>MREG</sub>     | СС | Т | Main regulator output voltage                                             | Before exiting from reset                                   | _                | 1.32             | —                | V    |

| Р                     |    | Ρ |                                                                           | After trimming                                              | 1.16             | 1.28             |                  |      |

| I <sub>MREG</sub>     | SR | _ | Main regulator current provided to $V_{DD_{LV}}$ domain                   | —                                                           | _                | _                | 150              | mA   |

| IMREGINT              | СС | D | Main regulator module current                                             | I <sub>MREG</sub> = 200 mA                                  | —                | —                | 2                | mA   |

|                       |    |   | consumption                                                               | I <sub>MREG</sub> = 0 mA                                    | —                | —                | 1                |      |

| V <sub>LPREG</sub>    | СС | Ρ | Low-power regulator output voltage                                        | After trimming                                              | 1.16             | 1.28             | —                | V    |

| I <sub>LPREG</sub>    | SR |   | Low power regulator current provided to $V_{\text{DD}\_\text{LV}}$ domain | —                                                           | —                | _                | 15               | mA   |

| I <sub>LPREGINT</sub> | СС | D | Low-power regulator module current consumption                            | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C       | _                | _                | 600              | μA   |

|                       |    |   |                                                                           | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C        | _                | 5                |                  |      |

| V <sub>ULPREG</sub>   | СС | Ρ | Ultra low power regulator output voltage                                  | After trimming                                              | 1.16             | 1.28             | _                | V    |

| I <sub>ULPREG</sub>   | SR | _ | Ultra low power regulator current provided to V <sub>DD_LV</sub> domain   | —                                                           |                  | _                | 5                | mA   |

| IULPREGINT            | СС | D | Ultra low power regulator module current consumption                      | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C       | _                | —                | 100              | μA   |

|                       |    |   |                                                                           | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C       | —                | 2                | —                |      |

| I <sub>DD_BV</sub>    | СС | D | In-rush average current on $V_{DD_BV}$ during power-up <sup>5</sup>       | —                                                           | —                | _                | 300 <sup>6</sup> | mA   |

| Table 23. Voltage regulator electrical characteristics (continued) |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

<sup>1</sup> V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

$^3\,$  This value is acceptable to guarantee operation from 4.5 V to 5.5 V.

<sup>4</sup> External regulator and capacitance circuitry must be capable of providing I<sub>DD\_BV</sub> while maintaining supply V<sub>DD\_BV</sub> in operating range.

<sup>5</sup> In-rush average current is seen only for short time during power-up and on standby exit (maximum 20 µs, depending on external capacitances to be loaded).

<sup>6</sup> The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

| Symbol C             |    | C | Parameter   | Conditions <sup>1</sup> | Value                   |     |     | Unit |    |

|----------------------|----|---|-------------|-------------------------|-------------------------|-----|-----|------|----|

|                      |    | C | raidilietei |                         | Min                     | Тур | Max | onn  |    |

| I <sub>DDSTDBY</sub> | СС | Ρ |             |                         | T <sub>A</sub> = 25 °C  |     | 30  | 100  | μA |

|                      |    | D |             | (128 kHz) running       | T <sub>A</sub> = 55 °C  |     | 75  | _    |    |

|                      |    | D |             |                         | T <sub>A</sub> = 85 °C  |     | 180 | 700  |    |

|                      |    | D |             |                         | T <sub>A</sub> = 105 °C | _   | 315 | 1000 |    |

|                      |    | Ρ |             |                         | T <sub>A</sub> = 125 °C |     | 560 | 1700 |    |

Table 25. Power consumption on VDD\_BV and VDD\_HV (continued) (continued)

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

<sup>2</sup> Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

- <sup>3</sup> Higher current may be sinked by device during power-up and standby exit. Please refer to in-rush average current on Table 23.

- <sup>4</sup> RUN current measured with typical application with accesses on both flash memory and SRAM.

- <sup>5</sup> Only for the "P" classification: Code fetched from SRAM: serial IPs CAN and LIN in loop-back mode, DSPI as Master, PLL as system clock (3 × Multiplier) peripherals on (eMIOS/CTU/ADC) and running at maximum frequency, periodic SW/WDG timer reset enabled.

- <sup>6</sup> Data flash power down. Code flash in low power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: 0 ON (clocked but no reception or transmission). LINFlex: instances: 0, 1, 2 ON (clocked but no reception or transmission), instance: 3 clocks gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON.PIT ON. STM ON. ADC ON but no conversion except 2 analog watchdogs.

- <sup>7</sup> Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPVreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- <sup>8</sup> When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- <sup>9</sup> Only for the "P" classification: ULPVreg on, HP/LPVreg off, 16 KB SRAM on, device configured for minimum consumption, all possible modules switched off.

### 4.11 Flash memory electrical characteristics

The data flash operation depends strongly on the code flash operation. If code flash is switched-off, the data flash is disabled.

### 4.11.1 Program/Erase characteristics

Table 26 shows the program and erase characteristics.

| Symbol              |    | с | Parameter                                                                                                                                               | Conditions <sup>1</sup>           |                 | Value |      |      | Unit |

|---------------------|----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-------|------|------|------|

|                     |    | C | Faiameter                                                                                                                                               |                                   | Min             | Тур   | Max  | Onit |      |

| IFIRCSTOP           | CC | Т | Fast internal RC oscillator high                                                                                                                        | T <sub>A</sub> = 25 °C            | sysclk = off    |       | 500  | _    | μA   |

|                     |    |   | frequency and system clock<br>current in stop mode                                                                                                      |                                   | sysclk = 2 MHz  |       | 600  |      |      |

|                     |    |   | ·                                                                                                                                                       |                                   | sysclk = 4 MHz  |       | 700  |      |      |

|                     |    |   |                                                                                                                                                         |                                   | sysclk = 8 MHz  |       | 900  |      |      |

|                     |    |   |                                                                                                                                                         |                                   | sysclk = 16 MHz |       | 1250 |      |      |

| t <sub>FIRCSU</sub> | СС | С | Fast internal RC oscillator start-up time                                                                                                               | $V_{DD} = 5.0 \text{ V} \pm 10\%$ |                 | _     | 1.1  | 2.0  | μs   |

| $\Delta_{FIRCPRE}$  | СС | С | Fast internal RC oscillator<br>precision after software<br>trimming of f <sub>FIRC</sub>                                                                | T <sub>A</sub> = 25 °C            |                 | -1    | —    | 1    | %    |

| $\Delta_{FIRCTRIM}$ | СС | С | Fast internal RC oscillator<br>trimming step                                                                                                            | T <sub>A</sub> = 25 °C            |                 |       | 1.6  |      | %    |

|                     | СС | С | Fast internal RC oscillator<br>variation in temperature and<br>supply with respect to $f_{FIRC}$ at<br>$T_A = 55$ °C in high-frequency<br>configuration |                                   | _               | -5    |      | 5    | %    |

Table 38. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified.

<sup>2</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

### 4.16 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz slow internal RC oscillator (SIRC). This can be used as the reference clock for the RTC module.

Table 39. Slow internal RC oscillator (128 kHz) electrical characteristics

| Symbol                          | Symbol |   | Parameter                                                                          | Conditions <sup>1</sup>                                |     | Value |     | Unit |

|---------------------------------|--------|---|------------------------------------------------------------------------------------|--------------------------------------------------------|-----|-------|-----|------|

| Cymbol                          |        | С | i di dificici                                                                      | Conditions                                             | Min | Тур   | Max | onn  |

| f <sub>SIRC</sub>               | СС     | Ρ | Slow internal RC oscillator low                                                    | T <sub>A</sub> = 25 °C, trimmed                        | _   | 128   | —   | kHz  |

|                                 | SR     | _ | frequency                                                                          | _                                                      | 100 | _     | 150 |      |

| I <sub>SIRC</sub> <sup>2,</sup> | СС     |   | Slow internal RC oscillator low<br>frequency current                               | T <sub>A</sub> = 25 °C, trimmed                        |     | _     | 5   | μA   |

| t <sub>SIRCSU</sub>             | СС     |   | Slow internal RC oscillator start-up time                                          | $T_A = 25 \text{ °C}, V_{DD} = 5.0 \text{ V} \pm 10\%$ |     | 8     | 12  | μs   |

| ∆ <sub>SIRCPRE</sub>            | CC     |   | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub> | T <sub>A</sub> = 25 °C                                 | -2  | _     | 2   | %    |

|                                 | СС     |   | Slow internal RC oscillator trimming step                                          | —                                                      |     | 2.7   | _   |      |

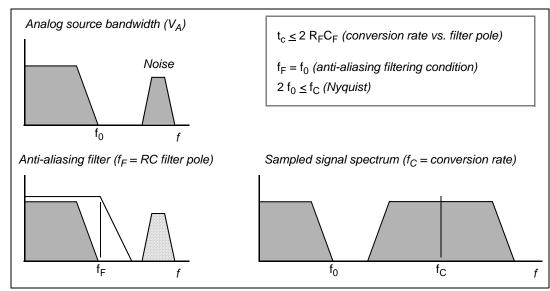

Figure 15. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $t_c$ ). Again the conversion period  $t_c$  is longer than the sampling time  $t_s$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $t_s$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive Equation 11 between the ideal and real sampled voltage on  $C_S$ :

Eqn. 11

$$\frac{V_{A2}}{V_A} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

Eqn. 12

$$C_F > 2048 \bullet C_S$$

| Table 41. ADC conversion | characteristics | (continued) |

|--------------------------|-----------------|-------------|

|--------------------------|-----------------|-------------|

| Symbo               | ,  | с | Parameter            | Conditions <sup>1</sup>   |     | Value |     | Unit |

|---------------------|----|---|----------------------|---------------------------|-----|-------|-----|------|

| - Cymse             |    | Ŭ | i urumotor           | Conditions                | Min | Тур   | Max |      |

| TUEX <sup>(7)</sup> | СС |   | -                    | Without current injection | -10 |       | 10  | LSB  |

|                     |    | Т | for extended channel | With current injection    | -12 |       | 12  |      |

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified.

- $^2\,$  Analog and digital V\_{SS} must be common (to be tied together externally).

- <sup>3</sup> V<sub>AINx</sub> may exceed V<sub>SS\_ADC</sub> and V<sub>DD\_ADC</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0xFFF.

- <sup>4</sup> Duty cycle is ensured by using system clock without prescaling. When ADCLKSEL = 0, the duty cycle is ensured by internal divider by 2.

- <sup>5</sup> During the sampling time the input capacitance  $C_S$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_S$ . After the end of the sampling time  $t_S$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_S$  depend on programming.

- <sup>6</sup> This parameter does not include the sampling time t<sub>S</sub>, but only the time for determining the digital result and the time to load the result's register with the conversion result.

- <sup>7</sup> Total Unadjusted Error: The maximum error that occurs without adjusting Offset and Gain errors. This error is a combination of Offset, Gain and Integral Linearity errors.

### 4.18 On-chip peripherals

### 4.18.1 Current consumption

| Symbol                    |    | С | Parameter                                             | Co                                                                               | onditions                                                                                                                            | Typical value <sup>2</sup>   | Unit |

|---------------------------|----|---|-------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|

| I <sub>DD_BV(CAN)</sub>   | СС | Т | CAN (FlexCAN) supply                                  | ,                                                                                | al (static + dynamic)                                                                                                                | 8 × f <sub>periph</sub> + 85 | μΑ   |

|                           |    |   | current on V <sub>DD_BV</sub>                         | 125 Kbyte/s<br>n<br>• X<br>C<br>• N                                              | isumption:<br>FlexCAN in loop-back<br>node<br>KTAL at 8 MHz used as<br>CAN engine clock source<br>Message sending period<br>s 580 μs | 8 × f <sub>periph</sub> + 27 | μA   |

| I <sub>DD_BV(eMIOS)</sub> | СС | Т | eMIOS supply current<br>on V <sub>DD_BV</sub>         | Static consumption:<br>• eMIOS channel OFF<br>• Global prescaler enabled         |                                                                                                                                      | 29 × f <sub>periph</sub>     | μA   |

|                           |    |   |                                                       | <ul> <li>Dynamic consum</li> <li>It does not cha<br/>frequency (0.00)</li> </ul> | ange varying the                                                                                                                     | 3                            | μA   |

| I <sub>DD_BV(SCI)</sub>   | СС | Т | SCI (LINFlex) supply<br>current on V <sub>DD_BV</sub> | Total (static + dynamic) consumption:<br>• LIN mode<br>• Baudrate: 20 Kbyte/s    |                                                                                                                                      | 5 × f <sub>periph</sub> + 31 | μA   |

### Table 42. On-chip peripherals current consumption<sup>1</sup>

| No   | No. Symbol                       |    | Symbol |                                                                                                                | с           | Paramete                 | DSPI0/DSPI1         |                    |      |  | Unit |

|------|----------------------------------|----|--------|----------------------------------------------------------------------------------------------------------------|-------------|--------------------------|---------------------|--------------------|------|--|------|

| 110. |                                  |    | Ŭ      | raiametei                                                                                                      |             | Min                      | Тур                 | Max                | Jint |  |      |

|      | ∆t <sub>CSC</sub>                | CC | D      | Internal delay between pad<br>associated to SCK and pad<br>associated to CSn in master<br>mode                 | Master mode | _                        | _                   | 130 <sup>2</sup>   | ns   |  |      |

|      | Δt <sub>ASC</sub>                | CC | D      | Internal delay between pad associated to SCK and pad associated to CSn in master mode for CSn1 $\rightarrow$ 1 | Master mode | _                        |                     | 130 <sup>(2)</sup> | ns   |  |      |

| 2    | t <sub>CSCext</sub> <sup>3</sup> | SR | D      | CS to SCK delay                                                                                                | Slave mode  | 32                       | _                   | —                  | ns   |  |      |

| 3    | t <sub>ASCext</sub> 4            | SR | D      | After SCK delay                                                                                                | Slave mode  | 1/f <sub>DSPI</sub> + 5  | _                   | —                  | ns   |  |      |

| 4    | t <sub>SDC</sub>                 | СС | D      | SCK duty cycle                                                                                                 | Master mode | _                        | t <sub>SCK</sub> /2 |                    | ns   |  |      |

|      |                                  | SR | D      |                                                                                                                | Slave mode  | t <sub>SCK</sub> /2      | —                   | _                  |      |  |      |

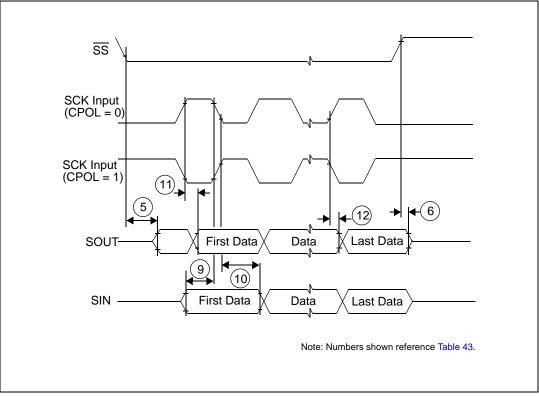

| 5    | t <sub>A</sub>                   | SR | D      | Slave access time                                                                                              | —           | 1/f <sub>DSPI</sub> + 70 | —                   | _                  | ns   |  |      |

| 6    | t <sub>DI</sub>                  | SR | D      | Slave SOUT disable time                                                                                        | —           | 7                        | —                   |                    | ns   |  |      |

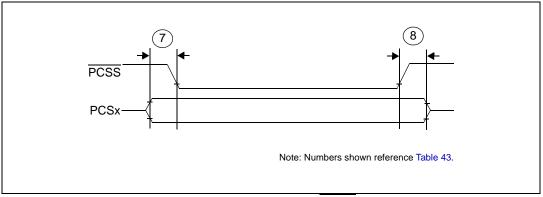

| 7    | t <sub>PCSC</sub>                | SR | D      | PCSx to PCSS time                                                                                              | —           | 0                        | —                   | _                  | ns   |  |      |

| 8    | t <sub>PASC</sub>                | SR | D      | PCSS to PCSx time                                                                                              | —           | 0                        | —                   | _                  | ns   |  |      |

| 9    | t <sub>SUI</sub>                 | SR | D      | Data setup time for inputs                                                                                     | Master mode | 43                       | —                   | _                  | ns   |  |      |

|      |                                  |    |        |                                                                                                                | Slave mode  | 5                        | —                   | _                  |      |  |      |

| 10   | t <sub>HI</sub>                  | SR | D      | Data hold time for inputs                                                                                      | Master mode | 0                        | _                   | _                  | ns   |  |      |

|      |                                  |    |        |                                                                                                                | Slave mode  | 2 <sup>5</sup>           | —                   |                    |      |  |      |

| 11   | t <sub>SUO</sub> 6               | СС | D      | Data valid after SCK edge                                                                                      | Master mode | —                        | —                   | 32                 | ns   |  |      |

|      |                                  |    |        |                                                                                                                | Slave mode  | —                        | —                   | 52                 |      |  |      |

| 12   | t <sub>HO</sub> <sup>(6)</sup>   | СС | D      | Data hold time for outputs                                                                                     | Master mode | 0                        | —                   | —                  | ns   |  |      |

|      |                                  |    |        |                                                                                                                | Slave mode  | 8                        | —                   | —                  |      |  |      |

| Table 43. DSPI characteristics <sup>1</sup> | (continued) |

|---------------------------------------------|-------------|

|---------------------------------------------|-------------|

$^1\,$  Operating conditions:  $C_{\text{OUT}}$  = 10 to 50 pF, Slew\_{IN} = 3.5 to 15 ns

<sup>2</sup> Maximum is reached when CSn pad is configured as SLOW pad while SCK pad is configured as MEDIUM pad

<sup>3</sup> The t<sub>CSC</sub> delay value is configurable through a register. When configuring t<sub>CSC</sub> (using PCSSCK and CSSCK fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than  $\Delta t_{CSC}$  to ensure positive t<sub>CSCext</sub>.

<sup>4</sup> The t<sub>ASC</sub> delay value is configurable through a register. When configuring t<sub>ASC</sub> (using PASC and ASC fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than  $\Delta t_{ASC}$  to ensure positive t<sub>ASCext</sub>.

<sup>5</sup> This delay value corresponds to SMPL\_PT = 00b which is bit field 9 and 8 of DSPI\_MCR.

<sup>6</sup> SCK and SOUT configured as MEDIUM pad

Figure 23. DSPI modified transfer format timing – slave, CPHA = 1

Figure 24. DSPI PCS strobe (PCSS) timing

Package characteristics

### 4.18.3 JTAG characteristics

| Table | 44. | JTAG      | characteristics |

|-------|-----|-----------|-----------------|

|       |     | • • • • • |                 |

| No. | Symbol            |    | с | Parameter              |       | Value | Unit |      |

|-----|-------------------|----|---|------------------------|-------|-------|------|------|

| NO. |                   |    | C | raiameter              | Min   | Тур   | Max  | Unit |

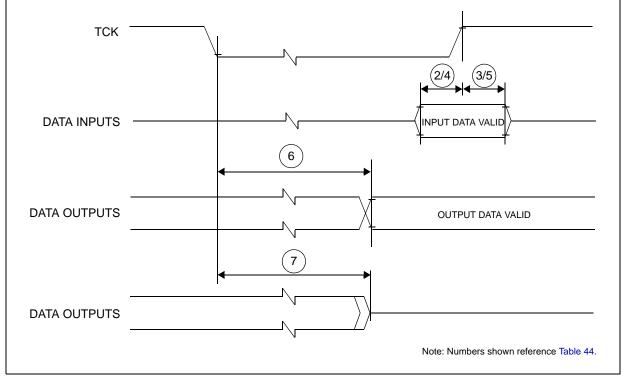

| 1   | t <sub>JCYC</sub> | CC | D | TCK cycle time         | 83.33 | _     | —    | ns   |

| 2   | t <sub>TDIS</sub> | CC | D | TDI setup time         | 15    | _     | —    | ns   |

| 3   | t <sub>TDIH</sub> | CC | D | TDI hold time          | 5     | _     | —    | ns   |

| 4   | t <sub>TMSS</sub> | CC | D | TMS setup time         | 15    | _     | —    | ns   |

| 5   | t <sub>TMSH</sub> | CC | D | TMS hold time          | 5     | _     | —    | ns   |

| 6   | t <sub>TDOV</sub> | CC | D | TCK low to TDO valid   | —     | _     | 49   | ns   |

| 7   | t <sub>TDOI</sub> | CC | D | TCK low to TDO invalid | 6     |       | —    | ns   |

Figure 25. Timing diagram – JTAG boundary scan

# 5 Package characteristics

- 5.1 Package mechanical data

- 5.1.1 100 LQFP

### **Document revision history**

| <ul> <li>Features: Replaced "e20020" with "e20020h"; added an explanation of which LINFlemodules support master mode and slave</li> <li>MPC5601D/MPC5602D series block summary: <ul> <li>added definition for "AUTOSAR" acronym</li> <li>changed "System watchdog timer" to "Software watchdog timer"64 LQFP pin configuration (top view): changed pin 6 from VPP_TEST to VSS_HV</li> <li>Added section "Pad configuration during reset phases"</li> <li>Added section "Voltage supply pins"</li> <li>Added section "Pad types"</li> <li>Added section "System pins"</li> <li>Renamed and updated section "Functional ports" (was previously section "Pin muxing update includes replacing all instances of WKUP with WKPU (WKPU is the correlable viation for Wakeup Unit)</li> <li>Section "NVUSRO register": edited content to separate configuration into electrical parameters and digital functionality</li> <li>Added section "NUSRO[WATCHDOG_EN] field description"</li> <li>Absolute maximum ratings: Removed "C" column from table</li> <li>Replaced "TBD" with "—" in T<sub>VDD</sub> min value cell of 3.3 V and 5 V recommended operating conditions tables</li> <li>LQFP thermal characteristics: removed R<sub>6JB</sub> single layer board conditions; updated footnote 4</li> <li>I/O input DC electrical characteristics: removed footnote "All values need to be confirmed during device validation"; updated I<sub>LKG</sub> characteristics: changed "I<sub>OH</sub> = 100 μ</li> </ul> </li> </ul>                                                                                                                                                     | Revision | Date | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>I/O consumption: replaced instances of "Root medium square" with "Root mean squa<br/>Updated section "Voltage regulator electrical characteristics"</li> <li>Section "Low voltage detector electrical characteristics": changed title (was "Voltage<br/>monitor electrical characteristics"); added a fifth LVD (LVDHV3B); added event stat<br/>flag names found in RGM chapter of device reference manual to POR module an<br/>LVD descriptions; replaced instances of "Low voltage monitor" with "Low voltage<br/>detector"; deleted note referencing power domain No. 2 (this domain is not prese<br/>on the device); updated electrical characteristics table</li> <li>Updated and renamed section "Power consumption" (was previously section "Low<br/>voltage domain power consumption")</li> <li>Program and erase specifications (code flash): updated symbols; updated t<sub>esus</sub> valu<br/>Updated Flash memory read access timing</li> <li>EMI radiated emission measurement: updated S<sub>EMI</sub> values</li> <li>Updated FMPLL electrical characteristics</li> <li>Crystal oscillator and resonator connection scheme: inserted footnote about possibly<br/>requiring a series resistor</li> <li>Fast internal RC oscillator (16 MHz) electrical characteristics: updated t<sub>FIRCSU</sub> value<br/>Section "Input impedance and ADC accuracy": changed "V<sub>A</sub>/V<sub>A2</sub>" to "V<sub>A2</sub>/V<sub>A</sub>" in<br/>Equation 13</li> <li>ADC conversion characteristics:</li> <li>updated conditions for sampling time V<sub>DD</sub> = 5.0 V</li> <li>updated conditions for conversion time V<sub>DD</sub> = 5.0 V</li> </ul> |          |      | Formatting and editorial changes throughout           Device comparison table: for the "Total timer I/O eMIOS", changed "13 ch" to "14 ch"           Features: Replaced "e20020" with "e20020"; added an explanation of which LINFlex           modules support master mode and slave           MPC5601D/MPC5602D series block summary:           • added definition for "AUTOSAR" acronym           changed "System watchdog time" to "Software watchdog timer"64 LQFP pin configuration (top view): changed pin 6 from VPP_TEST to VSS_HV           Added section "Pad types"           Added section "Pad types"           Added section "Voltage supply pins"           Added section "Voltage supply pins"           Added section "Voltage supply pins"           Added section "Notuse pins"           Renamed and updated section "Functional ports" (was previously section "Pin muxing"); update includes replacing all instances of WKUP with WKPU (WKPU is the correct abbreviation for Wakeup Unit)           Section "NVUSRO[WATCHDOC_EN] field description"           Added section "NUVSRO[WATCHDOC_EN] field description"           Added section "NUVSRO[WATCHDOC_EN] field description"           Added section voltage differentistics: removed footnote "All values need to be confirmed during device validation"; updated l <sub>LKG</sub> characteristics           MDDUM configuration output buffer electrical characteristics: changed "G <sub>OH</sub> = 100 µA" to 'I <sub>OL</sub> = 100 µA" in V <sub>OL</sub> conditions           I/O consumption: replaced instances of "Low relaterestics" |

### Table 45. Revision history (continued)