# E·XFL

#### NXP USA Inc. - SPC5602DF1MLL3 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, LINbus, SCI, SPI                                               |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 79                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 33x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5602df1mll3 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Block diagram**

#### Table 1. MPC5602D device comparison (continued)

| Feature |                                              | Device   |         |          |  |  |  |  |

|---------|----------------------------------------------|----------|---------|----------|--|--|--|--|

| reature | MPC5601DxLH MPC5601DxLL MPC5602DxLH MPC5602I |          |         |          |  |  |  |  |

| Debug   | JTAG                                         |          |         |          |  |  |  |  |

| Package | 64 LQFP                                      | 100 LQFP | 64 LQFP | 100 LQFP |  |  |  |  |

<sup>1</sup> Refer to eMIOS chapter of device reference manual for information on the channel configuration and functions.

<sup>2</sup> Type X = MC + MCB + OPWMT + OPWMB + OPWFMB + SAIC + SAOC

<sup>3</sup> Type Y = OPWMT + OPWMB + SAIC + SAOC

<sup>4</sup> Type G = MCB + IPWM + IPM + DAOC + OPWMT + OPWMB + OPWFMB + OPWMCB + SAIC + SAOC

<sup>5</sup> Type H = IPWM + IPM + DAOC + OPWMT + OPWMB + SAIC + SAOC

<sup>6</sup> I/O count based on multiplexing with peripherals

## 2 Block diagram

Figure 1 shows a top-level block diagram of the MPC5602D device series.

| Block                                         | Function                                                                                                                                                                                                                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-time counter (RTC)                       | Provides a free-running counter and interrupt generation capability that can be used for timekeeping applications                                                                                                                |

| Reset generation module<br>(MC_RGM)           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                    |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR (Automotive Open System Architecture) and operating system tasks                                                                                                      |

| Software watchdog timer (SWT)                 | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events.                                                                         |

### 3.1 Package pinouts

The available LQFP pinouts are provided in the following figures. For pin signal descriptions, please refer to Table 5.

|          |         |                                    |                                                          |                                      |                                        |             | T<br>Ition             | Pin n   | umber    |

|----------|---------|------------------------------------|----------------------------------------------------------|--------------------------------------|----------------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                 | Peripheral                           | I/O<br>direction <sup>2</sup>          | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PB[7]    | PCR[23] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[23]<br>—<br>—<br>—<br>ADC1_P[3]                     | SIUL<br>—<br>—<br>ADC                | <br> -<br> <br>                        | I           | Tristate               | 37      | 55       |

| PB[8]    | PCR[24] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[24]<br>—<br>—<br>ADC1_S[4]<br>WKPU[25] <sup>3</sup> | SIUL<br>—<br>—<br>ADC<br>WKPU        | <br><br><br> <br>                      | Ι           | Tristate               | 30      | 39       |

| PB[9]    | PCR[25] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[25]<br>—<br>—<br>ADC1_S[5]<br>WKPU[26] <sup>3</sup> | SIUL<br>—<br>—<br>ADC<br>WKPU        | <br><br><br> <br>                      | I           | Tristate               | 29      | 38       |

| PB[10]   | PCR[26] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[26]<br>—<br>—<br>ADC1_S[6]<br>WKPU[8] <sup>3</sup>  | SIUL<br>—<br>—<br>ADC<br>WKPU        | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | J           | Tristate               | 31      | 40       |

| PB[11]   | PCR[27] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[27]<br>E0UC[3]<br>—<br>CS0_0<br>ADC1_S[12]          | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>I/O<br>I                 | J           | Tristate               | 38      | 59       |

| PB[12]   | PCR[28] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[28]<br>E0UC[4]<br>—<br>CS1_0<br>ADC1_X[0]           | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>—<br>0<br>I              | J           | Tristate               | 39      | 61       |

| PB[13]   | PCR[29] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[29]<br>E0UC[5]<br>—<br>CS2_0<br>ADC1_X[1]           | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>—<br>0<br>I              | J           | Tristate               | 40      | 63       |

| PB[14]   | PCR[30] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[30]<br>E0UC[6]<br><br>CS3_0<br>ADC1_X[2]            | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>—<br>0<br>I              | J           | Tristate               | 41      | 65       |

|          |         |                                    |                                                                |                                              |                                |             | r<br>tion              | Pin n   | umber    |

|----------|---------|------------------------------------|----------------------------------------------------------------|----------------------------------------------|--------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                       | Peripheral                                   | I/O<br>direction <sup>2</sup>  | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PC[7]    | PCR[39] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[39]<br>—<br>—<br>LIN1RX                                   | SIUL<br>—<br>—<br>LINFlex_1<br>WKPU          | I/O<br> -<br> -<br> -          | S           | Tristate               | 17      | 26       |

| PC[8]    | PCR[40] | AF0<br>AF1<br>AF2<br>AF3           | WKPU[12] <sup>3</sup><br>GPIO[40]<br>LIN2TX<br>E0UC[3]<br>—    | SIUL<br>LINFlex_2<br>eMIOS_0                 | I<br>0<br>I/O<br>—             | S           | Tristate               | 63      | 99       |

| PC[9]    | PCR[41] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[41]<br><br>E0UC[7]<br><br>LIN2RX<br>WKPU[13] <sup>3</sup> | SIUL<br><br>eMIOS_0<br><br>LINFlex_2<br>WKPU | I/O<br>—<br>I/O<br>—<br>I<br>I | S           | Tristate               | 2       | 2        |

| PC[10]   | PCR[42] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[42]<br><br>MA[1]                                          | SIUL<br>—<br>—<br>ADC                        | I/O<br>—<br>—<br>O             | М           | Tristate               | 13      | 22       |

| PC[11]   | PCR[43] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[43]<br>—<br>—<br>MA[2]<br>WKPU[5] <sup>3</sup>            | SIUL<br>—<br>ADC<br>WKPU                     | I/O<br>—<br>—<br>O<br>I        | S           | Tristate               | _       | 21       |

| PC[12]   | PCR[44] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[44]<br>E0UC[12]<br>—<br>EIRQ[19]                          | SIUL<br>eMIOS_0<br>—<br>SIUL                 | I/O<br>I/O<br>—<br>I           | Μ           | Tristate               | _       | 97       |

| PC[13]   | PCR[45] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[45]<br>E0UC[13]<br>—<br>—                                 | SIUL<br>eMIOS_0<br>—                         | I/O<br>I/O<br>—                | S           | Tristate               | _       | 98       |

| PC[14]   | PCR[46] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[46]<br>E0UC[14]<br>—<br>EIRQ[8]                           | SIUL<br>eMIOS_0<br><br>SIUL                  | I/O<br>I/O<br>—<br>I           | S           | Tristate               | _       | 3        |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[47]<br>E0UC[15]<br><br>EIRQ[20]                           | SIUL<br>eMIOS_0<br>—<br>SIUL                 | I/O<br>I/O<br>—<br>I           | Μ           | Tristate               | _       | 4        |

|          |         |                                    |                                                  | L                                     | Pin number                    |             |                        |         |          |

|----------|---------|------------------------------------|--------------------------------------------------|---------------------------------------|-------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                         | Peripheral                            | I/O<br>direction <sup>2</sup> | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PD[8]    | PCR[56] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[56]<br>—<br>—<br>—<br>ADC1_P[12]            | SIUL<br>—<br>—<br>—<br>ADC            | <br><br><br>                  | I           | Tristate               | _       | 49       |

| PD[9]    | PCR[57] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[57]<br>—<br>—<br>—<br>ADC1_P[13]            | SIUL<br>—<br>—<br>—<br>ADC            | <br><br><br>                  | I           | Tristate               |         | 56       |

| PD[10]   | PCR[58] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[58]<br>—<br>—<br>—<br>ADC1_P[14]            | SIUL<br>—<br>—<br>—<br>ADC            | <br><br><br>                  | Ι           | Tristate               |         | 57       |

| PD[11]   | PCR[59] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[59]<br>—<br>—<br>—<br>ADC1_P[15]            | SIUL<br>—<br>—<br>—<br>ADC            | <br><br><br>                  | I           | Tristate               |         | 58       |

| PD[12]   | PCR[60] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[60]<br>CS5_0<br>E0UC[24]<br>—<br>ADC1_S[8]  | SIUL<br>DSPI_0<br>eMIOS_0<br>—<br>ADC | I/O<br>O<br>I/O<br><br>I      | J           | Tristate               |         | 60       |

| PD[13]   | PCR[61] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[61]<br>CS0_1<br>E0UC[25]<br>—<br>ADC1_S[9]  | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC | I/O<br>I/O<br>I/O<br>—<br>I   | J           | Tristate               | _       | 62       |

| PD[14]   | PCR[62] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[62]<br>CS1_1<br>E0UC[26]<br>—<br>ADC1_S[10] | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC | I/O<br>O<br>I/O<br>—<br>I     | J           | Tristate               |         | 64       |

| PD[15]   | PCR[63] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>ADC1_S[11] | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC | I/O<br>O<br>I/O<br>—<br>I     | J           | Tristate               |         | 66       |

|          |         | I                                  |                                                  | Port                                  | E                             |             |                        | I       | I        |

| Table 5. Functional | port pin       | descriptions | (continued) | ) |

|---------------------|----------------|--------------|-------------|---|

|                     | P • · • P ···· |              | (           | / |

### 4.3.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 7 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Value <sup>1</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

#### Table 7. PAD3V5V field description

Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

### 4.3.2 NVUSRO[OSCILLATOR\_MARGIN] field description

The fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value. Table 8 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

#### Table 8. OSCILLATOR\_MARGIN field description

| Value <sup>1</sup> | Description                                 |

|--------------------|---------------------------------------------|

| 0                  | Low consumption configuration (4 MHz/8 MHz) |

| 1                  | High margin configuration (4 MHz/16 MHz)    |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

### 4.3.3 NVUSRO[WATCHDOG\_EN] field description

The watchdog enable/disable configuration after reset is dependent on the WATCHDOG\_EN bit value. Table 8 shows how NVUSRO[WATCHDOG\_EN] controls the device configuration.

#### Table 9. WATCHDOG\_EN field description

| 0 Disable after reset) | Value <sup>1</sup> | Description          |

|------------------------|--------------------|----------------------|

|                        | 0                  | Disable after reset) |

| 1 Enable after reset   | 1                  | Enable after reset   |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

### 4.4 Absolute maximum ratings

#### Table 10. Absolute maximum ratings

| Symbo              | <b>.</b> | Parameter                                                                                     | Conditions | Va                    | lue                   | Unit |

|--------------------|----------|-----------------------------------------------------------------------------------------------|------------|-----------------------|-----------------------|------|

| Symbo              | /        | raiametei                                                                                     | Conditions | Min                   | Max                   | Onit |

| V <sub>SS</sub>    | SR       | Digital ground on VSS_HV pins                                                                 | _          | 0                     | 0                     | V    |

| V <sub>DD</sub>    |          | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | _          | -0.3                  | 6.0                   | V    |

| V <sub>SS_LV</sub> |          | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _          | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

- Table 16 provides output driver characteristics for I/O pads when in SLOW configuration.

- Table 17 provides output driver characteristics for I/O pads when in MEDIUM configuration.

| Symb             |    | 2 | Parameter              | Conditions <sup>1</sup>                            |                     |    | Value | )   | Unit     |

|------------------|----|---|------------------------|----------------------------------------------------|---------------------|----|-------|-----|----------|

| Synn             | -  |   | raiametei              | Continions                                         |                     |    | Тур   | Max | <b>.</b> |

| I <sub>WPU</sub> | СС | Ρ | Weak pull-up current   | $V_{IN} = V_{IL}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | PAD3V5V = 0         | 10 | —     | 150 | μA       |

|                  |    | С | absolute value         |                                                    | $PAD3V5V = 1^2$     | 10 | —     | 250 |          |

|                  |    | Ρ |                        | $V_{IN} = V_{IL}, V_{DD} = 3.3 \text{ V} \pm 10\%$ | PAD3V5V = 1         | 10 | —     | 150 |          |

| $ I_{WPD} $      | СС | Ρ | Weak pull-down current | $V_{IN} = V_{IH}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | PAD3V5V = 0         | 10 | —     | 150 | μA       |

|                  |    | С | absolute value         |                                                    | $PAD3V5V = 1^{(2)}$ | 10 | —     | 250 |          |

|                  |    | Ρ |                        | $V_{IN} = V_{IH}, V_{DD} = 3.3 \text{ V} \pm 10\%$ | PAD3V5V = 1         | 10 | —     | 150 |          |

#### Table 15. I/O pull-up/pull-down DC electrical characteristics

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

<sup>2</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

#### Table 16. SLOW configuration output buffer electrical characteristics

| Sym             | hal | 6 | Parameter                               |           | Conditions <sup>1</sup>                                                                              | v                     | alue |                    | Unit |

|-----------------|-----|---|-----------------------------------------|-----------|------------------------------------------------------------------------------------------------------|-----------------------|------|--------------------|------|

| Jym             | 001 | C | Farameter                               |           |                                                                                                      | Min                   | Тур  | Max                | Unit |

| V <sub>OH</sub> | CC  | Ρ | Output high level<br>SLOW configuration | Push Pull | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>    |      | _                  | V    |

|                 |     | С |                                         |           | I <sub>OH</sub> = -2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>                  | 0.8V <sub>DD</sub>    | —    | _                  |      |

|                 |     | С |                                         |           | I <sub>OH</sub> = −1 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)              | V <sub>DD</sub> – 0.8 | _    | _                  |      |

| V <sub>OL</sub> | CC  | Ρ | Output low level<br>SLOW configuration  | Push Pull | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended)  | —                     | _    | 0.1V <sub>DD</sub> | V    |

|                 |     | С |                                         |           | I <sub>OL</sub> = 2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(2)</sup>                 | _                     | —    | 0.1V <sub>DD</sub> |      |

|                 |     | С |                                         |           | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended)  | —                     | —    | 0.5                |      |

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

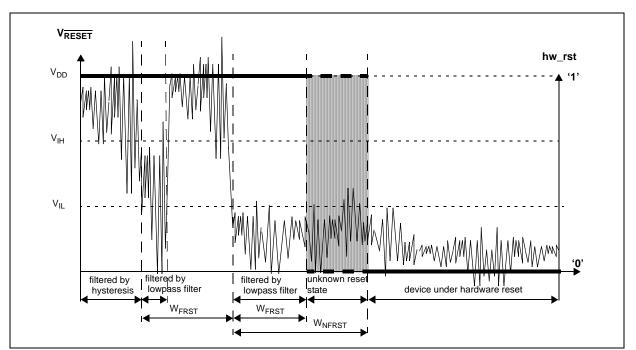

Figure 6. Noise filtering on reset signal

| Symb             |    | с | Parameter                                  | Conditions <sup>1</sup>                                                                             |                     | Value |                       | Unit |

|------------------|----|---|--------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|-------|-----------------------|------|

| Cynis            |    | Ŭ | i didiliciti                               | Conditions                                                                                          | Min Typ Max         |       |                       | onn  |

| V <sub>IH</sub>  | SR | Ρ | Input High Level CMOS<br>(Schmitt Trigger) | _                                                                                                   | 0.65V <sub>DD</sub> | _     | V <sub>DD</sub> + 0.4 | V    |

| V <sub>IL</sub>  | SR | Ρ | Input low Level CMOS<br>(Schmitt Trigger)  | _                                                                                                   | -0.4                | _     | 0.35V <sub>DD</sub>   | V    |

| V <sub>HYS</sub> | СС | С | Input hysteresis CMOS<br>(Schmitt Trigger) | _                                                                                                   | 0.1V <sub>DD</sub>  |       | —                     | V    |

| V <sub>OL</sub>  | СС | Ρ | Output low level                           | Push Pull, $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                   | _     | 0.1V <sub>DD</sub>    | V    |

|                  |    |   |                                            | Push Pull, I <sub>OL</sub> = 1 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>       | —                   | _     | 0.1V <sub>DD</sub>    |      |

|                  |    |   |                                            | Push Pull, $I_{OL} = 1 \text{ mA}$ ,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | —                   | _     | 0.5                   |      |

Table 22. Reset electrical characteristics

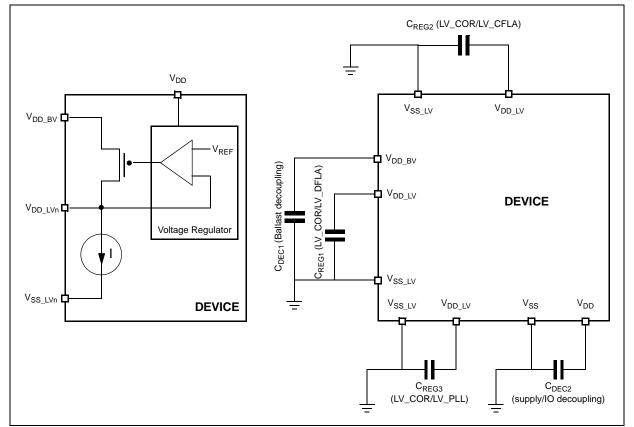

- LV\_CFLA: Low voltage supply for code flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_DFLA: Low voltage supply for data flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_PLL: Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

Figure 7. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three  $V_{DD_LV}/V_{SS_LV}$  supply pairs to ensure stable voltage (see Section 4.5, Recommended operating conditions).

| Symbo             | I  | с | Parameter                                        | Conditions <sup>1</sup>    |     | Value |     | Unit |

|-------------------|----|---|--------------------------------------------------|----------------------------|-----|-------|-----|------|

| Cymbo             |    | Ŭ | i arameter                                       | Conditions                 | Min | Тур   | Max | onne |

| C <sub>REGn</sub> | SR | - | Internal voltage regulator external capacitance  | —                          | 200 | _     | 500 | nF   |

| R <sub>REG</sub>  | SR |   | Stability capacitor equivalent serial resistance | Range:<br>10 kHz to 20 MHz | _   | _     | 0.2 | Ω    |

Table 23. Voltage regulator electrical characteristics

| Symbol                 |    | с | Parameter                                   | Conditions <sup>1</sup> |      | Value |      | Unit |

|------------------------|----|---|---------------------------------------------|-------------------------|------|-------|------|------|

| Symbol                 |    | C | raiametei                                   | Conditions              | Min  | Тур   | Max  | Unit |

| V <sub>PORUP</sub>     | SR | Ρ | Supply for functional POR module            | T <sub>A</sub> = 25 °C, | 1.0  | _     | 5.5  | V    |

| V <sub>PORH</sub>      | СС | Ρ | Power-on reset threshold                    | after trimming          | 1.5  |       | 2.6  | V    |

| V <sub>LVDHV3H</sub>   | СС | Т | LVDHV3 low voltage detector high threshold  |                         | —    |       | 2.95 | V    |

| V <sub>LVDHV3L</sub>   | СС | Ρ | LVDHV3 low voltage detector low threshold   | -                       | 2.6  |       | 2.9  | V    |

| V <sub>LVDHV3BH</sub>  | СС | Ρ | LVDHV3B low voltage detector high threshold |                         | —    |       | 2.95 | V    |

| V <sub>LVDHV3BL</sub>  | СС | Ρ | LVDHV3B low voltage detector low threshold  | -                       | 2.6  | _     | 2.9  | V    |

| V <sub>LVDHV5H</sub>   | СС | Т | LVDHV5 low voltage detector high threshold  | -                       | _    |       | 4.5  | V    |

| V <sub>LVDHV5L</sub>   | СС | Ρ | LVDHV5 low voltage detector low threshold   |                         | 3.8  |       | 4.4  | V    |

| V <sub>LVDLVCORL</sub> | СС | Ρ | LVDLVCOR low voltage detector low threshold |                         | 1.08 | _     | 1.16 | V    |

| V <sub>LVDLVBKPL</sub> | СС | Ρ | LVDLVBKP low voltage detector low threshold |                         | 1.08 | _     | 1.16 | V    |

$\overline{^{1}}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

### 4.10 Power consumption

Table 25 provides DC electrical characteristics for significant application modes. These values are indicative values; actual consumption depends on the application.

| Table 25. Power consumption on VDD_BV and VDD_HV | Table 25 | . Power | consumption | on VDD_E | 3V and VDD_H | V |

|--------------------------------------------------|----------|---------|-------------|----------|--------------|---|

|--------------------------------------------------|----------|---------|-------------|----------|--------------|---|

| Symbol                          |    | с | Parameter                           | Conditions <sup>1</sup>     |                         |     | Value |                   | Unit |

|---------------------------------|----|---|-------------------------------------|-----------------------------|-------------------------|-----|-------|-------------------|------|

| Symbol                          |    | C | raiametei                           | Conditions                  |                         | Min | Тур   | Max               | onn  |

| I <sub>DDMAX</sub> <sup>2</sup> | СС | D | RUN mode maximum<br>average current | _                           |                         |     | 90    | 130 <sup>3</sup>  | mA   |

| I <sub>DDRUN</sub> 4            | СС | Т | RUN mode typical                    | f <sub>CPU</sub> = 8 MHz    |                         |     | 7     | —                 | mA   |

|                                 |    | Т | average current <sup>5</sup>        | f <sub>CPU</sub> = 16 MHz   |                         | _   | 18    |                   |      |

|                                 |    | Т |                                     | f <sub>CPU</sub> = 32 MHz   |                         | _   | 29    |                   |      |

|                                 |    | Ρ |                                     | f <sub>CPU</sub> = 48 MHz   |                         | _   | 40    | 100               |      |

| IDDHALT                         | СС | С | HALT mode current <sup>6</sup>      |                             | T <sub>A</sub> = 25 °C  | —   | 8     | 15                | mA   |

|                                 |    | Ρ |                                     | (128 kHz) running           | T <sub>A</sub> = 125 °C | —   | 14    | 25                |      |

| IDDSTOP                         | СС | Ρ | STOP mode current <sup>7</sup>      | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 180   | 700 <sup>8</sup>  | μA   |

|                                 |    | D |                                     | (128 kHz) running           | T <sub>A</sub> = 55 °C  | —   | 500   | —                 |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 85 °C  | _   | 1     | 6 <sup>(8)</sup>  | mA   |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 105 °C | —   | 2     | 9 <sup>(8)</sup>  |      |

|                                 |    | Ρ |                                     |                             | T <sub>A</sub> = 125 °C | —   | 4.5   | 12 <sup>(8)</sup> |      |

| Symbol               |    | с | Parameter                         | Conditions <sup>1</sup> |                         |     | Value |          | Unit |

|----------------------|----|---|-----------------------------------|-------------------------|-------------------------|-----|-------|----------|------|

| -                    |    | Ŭ | i diameter                        | Conditions              | Min                     | Тур | Мах   | <b>U</b> |      |

| I <sub>DDSTDBY</sub> | СС | Ρ | STANDBY mode current <sup>9</sup> |                         | T <sub>A</sub> = 25 °C  |     | 30    | 100      | μA   |

|                      |    | D |                                   | (128 kHz) running       | T <sub>A</sub> = 55 °C  | _   | 75    | _        |      |

|                      |    | D |                                   |                         | T <sub>A</sub> = 85 °C  | _   | 180   | 700      |      |

|                      |    | D |                                   |                         | T <sub>A</sub> = 105 °C | _   | 315   | 1000     |      |

|                      |    | Ρ |                                   |                         | T <sub>A</sub> = 125 °C |     | 560   | 1700     |      |

Table 25. Power consumption on VDD\_BV and VDD\_HV (continued) (continued)

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

<sup>2</sup> Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

- <sup>3</sup> Higher current may be sinked by device during power-up and standby exit. Please refer to in-rush average current on Table 23.

- <sup>4</sup> RUN current measured with typical application with accesses on both flash memory and SRAM.

- <sup>5</sup> Only for the "P" classification: Code fetched from SRAM: serial IPs CAN and LIN in loop-back mode, DSPI as Master, PLL as system clock (3 × Multiplier) peripherals on (eMIOS/CTU/ADC) and running at maximum frequency, periodic SW/WDG timer reset enabled.

- <sup>6</sup> Data flash power down. Code flash in low power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: 0 ON (clocked but no reception or transmission). LINFlex: instances: 0, 1, 2 ON (clocked but no reception or transmission), instance: 3 clocks gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON.PIT ON. STM ON. ADC ON but no conversion except 2 analog watchdogs.

- <sup>7</sup> Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPVreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- <sup>8</sup> When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- <sup>9</sup> Only for the "P" classification: ULPVreg on, HP/LPVreg off, 16 KB SRAM on, device configured for minimum consumption, all possible modules switched off.

### 4.11 Flash memory electrical characteristics

The data flash operation depends strongly on the code flash operation. If code flash is switched-off, the data flash is disabled.

### 4.11.1 Program/Erase characteristics

Table 26 shows the program and erase characteristics.

| Symbo              | 0  | с | Parameter                                                                               | Conditions <sup>1</sup> |            |  | Valu | e   | Unit |

|--------------------|----|---|-----------------------------------------------------------------------------------------|-------------------------|------------|--|------|-----|------|

| Symb               | 01 | C | Falameter                                                                               | Conditions              |            |  | Тур  | Max | •    |

| I <sub>FLPW</sub>  | СС |   | Sum of the current consumption on $V_{DDHV}$ and $V_{DDBV}$ during flash low-power mode | _                       | Code flash |  | —    | 910 | μA   |

| I <sub>CFPWD</sub> | СС |   | Sum of the current consumption on                                                       | _                       | Code flash |  | —    | 125 | μΑ   |

| I <sub>DFPWD</sub> | СС | D | V <sub>DDHV</sub> and V <sub>DDBV</sub> during<br>flash power-down mode                 |                         | Data flash |  | —    | 25  | μA   |

Table 30. Flash power supply DC electrical characteristics

$^1~$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

### 4.11.3 Start-up/Switch-off timings

#### Table 31. Start-up time/Switch-off time

| Symbol                  |    | с | Parameter                                                  | Conditions <sup>1</sup> | Value |     |                  | Unit |

|-------------------------|----|---|------------------------------------------------------------|-------------------------|-------|-----|------------------|------|

| Symbol                  |    | Ŭ | i didineter                                                | Conditions              | Min   | Тур | Мах              |      |

| t <sub>FLARSTEXIT</sub> | СС | Т | Delay for flash module to exit reset mode                  | Code flash              | —     | —   | 125              | μs   |

|                         |    |   |                                                            | Data flash              |       | —   | 150              | μs   |

| t <sub>FLALPEXIT</sub>  | СС | Т | Delay for flash module to exit low-power mode <sup>2</sup> | Code flash              |       | _   | 0.5              | μs   |

| t <sub>FLAPDEXIT</sub>  | СС | Т | Delay for flash module to exit power-down                  | Code flash              |       | —   | 30               | μs   |

|                         |    |   | mode                                                       | Data flash              |       |     | 30 <sup>3</sup>  | μs   |

| t <sub>FLALPENTRY</sub> | СС | Т | Delay for flash module to enter low-power mode             | Code flash              | —     | —   | 0.5              | μs   |

| t <sub>FLAPDENTRY</sub> | СС | Т | Delay for flash module to enter                            | Code flash              |       |     | 1.5              | μs   |

|                         |    |   | power-down mode                                            | Data flash              | _     |     | 4 <sup>(3)</sup> | μs   |

$\overline{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> Data flash does not support low-power mode

<sup>3</sup> If code flash is already switched-on.

### 4.12 Electromagnetic compatibility (EMC) characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### 4.12.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

• Software recommendations – The software flowchart must include the management of runaway conditions such as:

### 4.17.2 Input impedance and ADC accuracy

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance: being  $C_S$  and  $C_{p2}$  substantially two switched capacitances, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{p2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (f_c \times (C_S+C_{p2}))$ ), where  $f_c$  represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{p2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

Eqn. 4

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

Equation 4 generates a constraint for external network design, in particular on a resistive path.

| Symbol                     |                                                                                                                                                                      | С | Parameter                                            | Parameter Con             |                                                                        | Typical value <sup>2</sup>    | Unit |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------|---------------------------|------------------------------------------------------------------------|-------------------------------|------|--|

| I <sub>DD_BV(SPI)</sub> CC |                                                                                                                                                                      | т | SPI (DSPI) supply                                    | Ballast static            | consumption (only clocked)                                             | 1                             | μA   |  |

|                            | current on V <sub>DD_BV</sub><br>Ballast dynamic consumption (continuous<br>communication):<br>• Baudrate: 2 Mbit/s<br>• Transmission every 8 μs<br>• Frame: 16 bits |   |                                                      |                           | 16 × f <sub>periph</sub>                                               | μA                            |      |  |

| I <sub>DD_BV(ADC)</sub>    | СС                                                                                                                                                                   | Т | ADC supply current on V <sub>DD_BV</sub>             | V <sub>DD</sub> = 5.5 V   | Ballast static consumption (no conversion)                             | 41 × f <sub>periph</sub>      | μA   |  |

|                            |                                                                                                                                                                      |   |                                                      |                           | Ballast dynamic<br>consumption (continuous<br>conversion) <sup>3</sup> | 5 × f <sub>periph</sub>       | μA   |  |

| IDD_HV_ADC(ADC)            | сс                                                                                                                                                                   | Т | ADC supply current on V <sub>DD_HV_ADC</sub>         | V <sub>DD</sub> = 5.5 V   | Analog static consumption (no conversion)                              | 2 × f <sub>periph</sub>       | μA   |  |

|                            |                                                                                                                                                                      |   |                                                      |                           | Analog dynamic<br>consumption (continuous<br>conversion)               | 75 × f <sub>periph</sub> + 32 | μA   |  |

| I <sub>DD_HV</sub> (FLASH) | СС                                                                                                                                                                   | Т | CFlash + DFlash supply current on V <sub>DD_HV</sub> | V <sub>DD</sub> = 5.5 V   | _                                                                      | 8.21                          | mA   |  |

| I <sub>DD_HV(PLL)</sub>    | СС                                                                                                                                                                   | Т | PLL supply current on<br>V <sub>DD_HV</sub>          | V <sub>DD</sub> = 5.5 V — |                                                                        | 30 × f <sub>periph</sub>      | μA   |  |

| Table 42. | On-chip | peripherals | current | consum | ption <sup>1</sup> | (continued) | ļ |

|-----------|---------|-------------|---------|--------|--------------------|-------------|---|

|-----------|---------|-------------|---------|--------|--------------------|-------------|---|

<sup>1</sup> Operating conditions: T<sub>A</sub> = 25 °C, f<sub>periph</sub> = 8 MHz to 48 MHz

<sup>2</sup> f<sub>periph</sub> is an absolute value.

<sup>3</sup> During the conversion, the total current consumption is given from the sum of the static and dynamic consumption, i.e.,  $(41 + 5) \times f_{periph}$ .

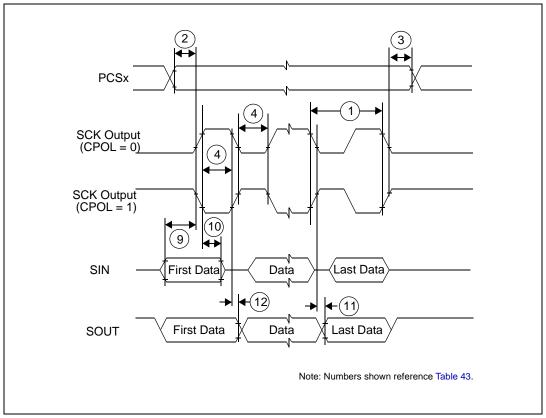

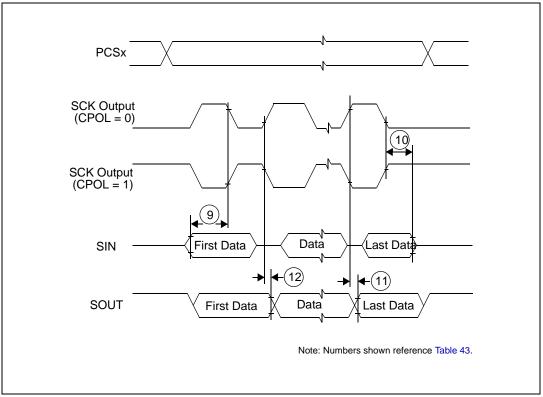

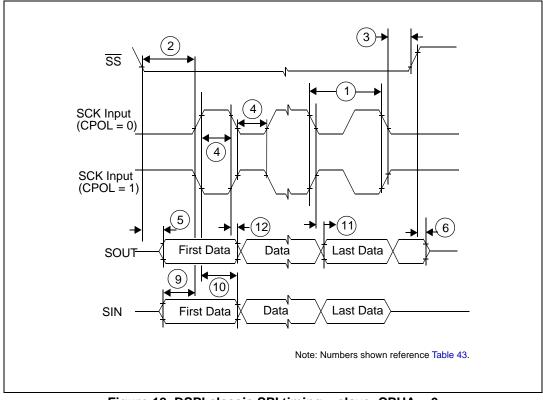

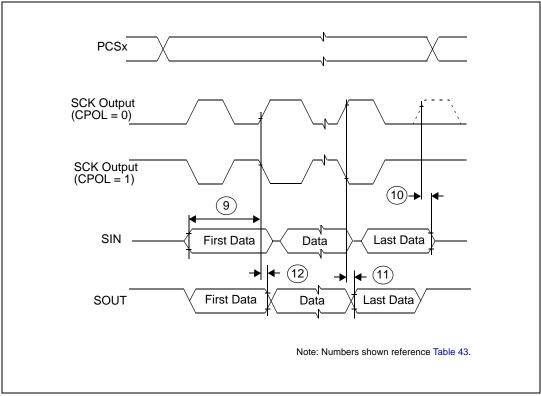

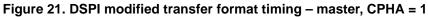

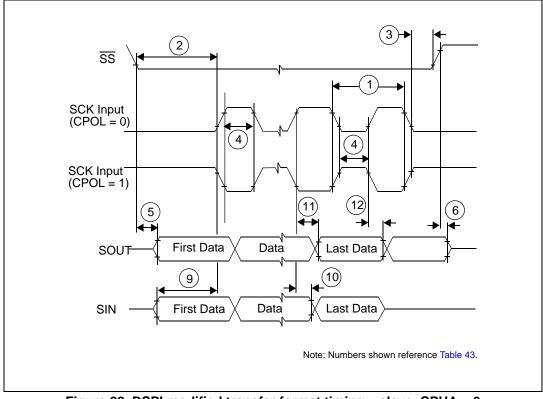

#### 4.18.2 **DSPI** characteristics

| Table 43. DS | SPI characteristics <sup>1</sup> |

|--------------|----------------------------------|

|--------------|----------------------------------|

| No. Symbol |                   | Symbol C Parameter |   | Paramata                         |                           | DSPIC | )/DSPI1 |                  | Unit |

|------------|-------------------|--------------------|---|----------------------------------|---------------------------|-------|---------|------------------|------|

|            |                   |                    |   |                                  | Min Typ Ma                |       | Max     |                  |      |

| 1          | t <sub>SCK</sub>  | SR                 | D | SCK cycle time                   | Master mode<br>(MTFE = 0) | 125   | _       | —                | ns   |

|            |                   |                    | D |                                  | Slave mode<br>(MTFE = 0)  | 125   | —       | —                |      |

|            |                   |                    | D |                                  | Master mode<br>(MTFE = 1) | 83    | _       | —                |      |

|            |                   |                    | D |                                  | Slave mode<br>(MTFE = 1)  | 83    | _       | —                |      |

| —          | f <sub>DSPI</sub> | SR                 | D | SPI digital controller frequency |                           | —     | _       | f <sub>CPU</sub> | MHz  |

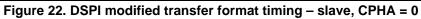

Figure 16. DSPI classic SPI timing – master, CPHA = 0

Figure 18. DSPI classic SPI timing – slave, CPHA = 0

|                                                                                                                                                                                                                                                       | MECHANICAL OUTLINES<br>DICTIONARY |                                    | DOCUMENT NO: 98ASS23308W |            |    |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|--------------------------|------------|----|--|--|

|                                                                                                                                                                                                                                                       |                                   |                                    | PAGE:                    | 98         | 33 |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE                      | THIS DRAWING                       | REV:                     | Н          |    |  |  |

| NOTES:                                                                                                                                                                                                                                                |                                   |                                    |                          |            |    |  |  |

| 1. ALL DIMENSIONS ARE IN MILL                                                                                                                                                                                                                         | IMETERS.                          |                                    |                          |            |    |  |  |

| 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.                                                                                                                                                                                          |                                   |                                    |                          |            |    |  |  |

| 3. DATUMS B, C AND D TO BE                                                                                                                                                                                                                            | DETERMINED AT I                   | DATUM PLANE H.                     |                          |            |    |  |  |

| 4. THE TOP PACKAGE BODY SIZ<br>BY A MAXIMUM OF 0.1 MM.                                                                                                                                                                                                | E MAY BE SMALL                    | ER THAN THE BO                     | TTOM PA                  | CKAGE SIZ  | Έ  |  |  |

| 5. DIMENSIONS DO NOT INCLUDE<br>PROTRUSION IS 0.25 mm PE<br>SIZE DIMENSIONS INCLUDING                                                                                                                                                                 | ER SIDE. THE DIMI                 | ONS. THE MAXIMU<br>ENSIONS ARE MAX | M ALLOW<br>(IMUM BO      | ABLE<br>DY |    |  |  |

| 6. DIMENSION DOES NOT INCLUE<br>CAUSE THE LEAD WIDTH TO<br>AND AN ADJACENT LEAD SH                                                                                                                                                                    | EXCEED 0.35. MII                  | NIMUM SPACE BET                    |                          |            |    |  |  |

| 7. DIMENSIONS ARE DETERMINED                                                                                                                                                                                                                          | ) AT THE SEATING                  | G PLANE, DATUM                     | A.                       |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   |                                    |                          |            |    |  |  |

| 100 LEAD LQF                                                                                                                                                                                                                                          | P                                 | CASE NUMBER: 9                     |                          |            |    |  |  |

| 14 X 14, 0.5 PITCH,                                                                                                                                                                                                                                   |                                   | STANDARD: NON-                     |                          |            |    |  |  |

|                                                                                                                                                                                                                                                       |                                   | PACKAGE CODE:                      | 8264                     | SHEET:     | 3  |  |  |

#### Figure 28. 100 LQFP package mechanical drawing (Part 3 of 3)

MPC5602D Microcontroller Data Sheet, Rev. 6

NP

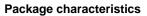

#### **Package characteristics**

Figure 30. 64 LQFP mechanical drawing (part 2 of 3)

Document revision history

# 7 Document revision history

Table 45 summarizes revisions to this document.

#### Table 45. Revision history

| Revision         | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | 30 Sep 2009 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2                | 18 Feb 2010 | Updated the following tables:<br>- Absolute maximum ratings<br>- Low voltage power domain electrical characteristics;<br>- On-chip peripherals current consumption<br>- DSPI characteristics;<br>- JTAG characteristics;<br>- ADC conversion characteristics;<br>Inserted a note on "Flash power supply DC characteristics" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3                | 10 Aug 2010 | <ul> <li>"Features" section: Updated information concerning eMIOS, ADC, LINFlex, Nexus and<br/>low power capabilities</li> <li>"MPC5602D device comparison" table: updated the "Execution speed" row</li> <li>"MPC5602D series block diagram" figure:</li> <li>updated max number of Crossbar Switches</li> <li>updated Legend</li> <li>"MPC5602D series block summary" table: added contents concernig the eDMA block</li> <li>"100 LQFP pin configuration (top view)" figure:</li> <li>removed alternate functions</li> <li>updated supply pins</li> <li>"64 LQFP pin configuration (top view)" figure: removed alternate functions</li> <li>Added "Pin muxing" section</li> <li>"NVUSRO register" section: Deleted "NVUSRO[WATCHDOG_EN] field description" section</li> <li>"Recommended operating conditions (3.3 V)" table:</li> <li>TV<sub>DD</sub>: deleted min value</li> <li>In footnote No. 3, changed capacitance value between V<sub>DD_BV</sub> and V<sub>SS_LV</sub></li> <li>"Recommended operating conditions (5.0 V)" table: deleted TV<sub>DD</sub> min value</li> <li>"LQFP thermal characteristics" table: changed R<sub>BUC</sub> values</li> <li>"I/O input DC electrical characteristics" table:</li> <li>W<sub>FF</sub>: updated max value</li> <li>W<sub>NFF</sub>: updated max value</li> <li>"Wupf: updated min value</li> <li>"I/O consumption" table: removed I<sub>DYNSEG</sub> row</li> <li>Added "I/O weight" table</li> <li>"Program and erase specifications (Code Flash)" table: deleted T<sub>Bank_C</sub> row</li> <li>Updated the following tables:</li> <li>"Voltage regulator electrical characteristics"</li> <li>"Low voltage monitor electrical characteristics"</li> <li>"Low voltage power domain electrical characteristics"</li> <li>"Fast internal RC oscillator (16 MHz) electrical characteristics"</li> <li>"Fast internal RC oscillator (16 MHz) electrical characteristics"</li> <li>"ADC conversion characteristics"</li> <li>"DSPI characteristics" section: removed "DSPI PCS strobe (PCSS) timing" figure</li> </ul> |

| 3<br>(continued) | 10 Aug 2010 | "Ordering information" section: removed "Orderable part number summary" table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |