# E·XFL

## NXP USA Inc. - SPC5602DF1VLL3 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, LINbus, SCI, SPI                                               |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 79                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 33x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5602df1vll3 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.6 Functional ports

The functional port pins are listed in Table 5.

| Table 5. Functiona | al port pin | descriptions |

|--------------------|-------------|--------------|

|--------------------|-------------|--------------|

|          |        |                                    |                                                                     |                                               |                               |             | T<br>ttion             | Pin n   | umber    |

|----------|--------|------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|-------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR    | Alternate<br>function <sup>1</sup> | Function                                                            | Peripheral                                    | I/O<br>direction <sup>2</sup> | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

|          |        |                                    |                                                                     | Port                                          | Α                             |             |                        |         |          |

| PA[0]    | PCR[0] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[0]<br>E0UC[0]<br>CLKOUT<br>E0UC[13]<br>WKPU[19] <sup>3</sup>   | SIUL<br>eMIOS_0<br>CGL<br>eMIOS_0<br>WKPU     | I/O<br>I/O<br>O<br>I/O<br>I   | Μ           | Tristate               | 5       | 12       |

| PA[1]    | PCR[1] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[1]<br>E0UC[1]<br>—<br>NMI <sup>4</sup><br>WKPU[2] <sup>3</sup> | SIUL<br>eMIOS_0<br>—<br>WKPU<br>WKPU<br>WKPU  | I/O<br>I/O<br>—<br>I<br>I     | S           | Tristate               | 4       | 7        |

| PA[2]    | PCR[2] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[2]<br>E0UC[2]<br>—<br>MA[2]<br>WKPU[3] <sup>3</sup>            | SIUL<br>eMIOS_0<br>—<br>ADC<br>WKPU           | I/O<br>I/O<br>—<br>0<br>I     | S           | Tristate               | 3       | 5        |

| PA[3]    | PCR[3] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[3]<br>E0UC[3]<br>—<br>CS4_0<br>EIRQ[0]<br>ADC1_S[0]            | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>SIUL<br>ADC | I/O<br>I/O<br>I/O<br>I<br>I   | S           | Tristate               | 43      | 68       |

| PA[4]    | PCR[4] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[4]<br>E0UC[4]<br>—<br>CS0_1<br>WKPU[9] <sup>3</sup>            | SIUL<br>eMIOS_0<br>—<br>DSPI_1<br>WKPU        | I/O<br>I/O<br>—<br>I/O<br>I   | S           | Tristate               | 20      | 29       |

| PA[5]    | PCR[5] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[5]<br>E0UC[5]<br>—                                             | SIUL<br>eMIOS_0<br>—                          | I/O<br>I/O<br>—               | М           | Tristate               | 51      | 79       |

| PA[6]    | PCR[6] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[6]<br>E0UC[6]<br><br>CS1_1<br>EIRQ[1]                          | SIUL<br>eMIOS_0<br><br>DSPI_1<br>SIUL         | I/O<br>I/O<br>I/O<br>I        | S           | Tristate               | 52      | 80       |

## Package pinouts and signal descriptions

|          |         |                                                   |                                                              |                                                  |                                        |             | tion                   | Pin number |          |  |

|----------|---------|---------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------|----------------------------------------|-------------|------------------------|------------|----------|--|

| Port pin | PCR     | Alternate<br>function <sup>1</sup>                | Function                                                     | Peripheral                                       | I/O<br>direction <sup>2</sup>          | Pad<br>type | RESET<br>configuration | 64 LQFP    | 100 LQFP |  |

| PA[7]    | PCR[7]  | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[7]<br>E0UC[7]<br>—<br>EIRQ[2]<br>ADC1_S[1]              | SIUL<br>eMIOS_0<br><br>SIUL<br>ADC               | I/O<br>I/O<br>—<br>I<br>I              | S           | Tristate               | 44         | 71       |  |

| PA[8]    | PCR[8]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>N/A <sup>5</sup> | GPIO[8]<br>E0UC[8]<br>E0UC[14]<br>—<br>EIRQ[3]<br>ABS[0]     | SIUL<br>eMIOS_0<br>eMIOS_0<br><br>SIUL<br>BAM    | I/O<br>I/O<br>—<br>I<br>I              | S           | Input, weak<br>pull-up | 45         | 72       |  |

| PA[9]    | PCR[9]  | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>5</sup>      | GPIO[9]<br>E0UC[9]<br>—<br>CS2_1<br>FAB                      | SIUL<br>eMIOS_0<br><br>DSPI_1<br>BAM             | I/O<br>I/O<br>—<br>I/O<br>I            | S           | Pull-down              | 46         | 73       |  |

| PA[10]   | PCR[10] | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[10]<br>E0UC[10]<br>—<br>LIN2TX<br>ADC1_S[2]             | SIUL<br>eMIOS_0<br><br>LINFlex_2<br>ADC          | I/O<br>I/O<br>—<br>0<br>I              | S           | Tristate               | 47         | 74       |  |

| PA[11]   | PCR[11] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—           | GPIO[11]<br>E0UC[11]<br>—<br>EIRQ[16]<br>ADC1_S[3]<br>LIN2RX | SIUL<br>eMIOS_0<br>—<br>SIUL<br>ADC<br>LINFlex_2 | I/O<br>I/O<br>—<br>I<br>I<br>I         | S           | Tristate               | 48         | 75       |  |

| PA[12]   | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[12]<br>—<br>—<br>EIRQ[17]<br>SIN_0                      | SIUL<br>—<br>—<br>SIUL<br>DSPI_0                 | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S           | Tristate               | 22         | 31       |  |

| PA[13]   | PCR[13] | AF0<br>AF1<br>AF2<br>AF3                          | GPIO[13]<br>SOUT_0<br>—<br>CS3_1                             | SIUL<br>DSPI_0<br><br>DSPI_1                     | I/O<br>O<br>—<br>I/O                   | М           | Tristate               | 21         | 30       |  |

| PA[14]   | PCR[14] | AF0<br>AF1<br>AF2<br>AF3<br>—                     | GPIO[14]<br>SCK_0<br>CS0_0<br>E0UC[0]<br>EIRQ[4]             | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>SIUL      | I/O<br>I/O<br>I/O<br>I/O<br>I          | Μ           | Tristate               | 19         | 28       |  |

## Package pinouts and signal descriptions

|          |         |                                    |                                                          |                                      |                                        | f           | Pin number             |         |          |

|----------|---------|------------------------------------|----------------------------------------------------------|--------------------------------------|----------------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                 | Peripheral                           | I/O<br>direction <sup>2</sup>          | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PB[7]    | PCR[23] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[23]<br>—<br>—<br>—<br>ADC1_P[3]                     | SIUL<br>—<br>—<br>ADC                | <br> -<br> <br>                        | I           | Tristate               | 37      | 55       |

| PB[8]    | PCR[24] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[24]<br>—<br>—<br>ADC1_S[4]<br>WKPU[25] <sup>3</sup> | SIUL<br>—<br>—<br>ADC<br>WKPU        | <br><br><br> <br>                      | Ι           | Tristate               | 30      | 39       |

| PB[9]    | PCR[25] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[25]<br>—<br>—<br>ADC1_S[5]<br>WKPU[26] <sup>3</sup> | SIUL<br>—<br>—<br>ADC<br>WKPU        | <br><br><br> <br>                      | I           | Tristate               | 29      | 38       |

| PB[10]   | PCR[26] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[26]<br>—<br>—<br>ADC1_S[6]<br>WKPU[8] <sup>3</sup>  | SIUL<br>—<br>—<br>ADC<br>WKPU        | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | J           | Tristate               | 31      | 40       |

| PB[11]   | PCR[27] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[27]<br>E0UC[3]<br>—<br>CS0_0<br>ADC1_S[12]          | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>I/O<br>I                 | J           | Tristate               | 38      | 59       |

| PB[12]   | PCR[28] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[28]<br>E0UC[4]<br>—<br>CS1_0<br>ADC1_X[0]           | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>—<br>0<br>I              | J           | Tristate               | 39      | 61       |

| PB[13]   | PCR[29] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[29]<br>E0UC[5]<br>—<br>CS2_0<br>ADC1_X[1]           | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>—<br>0<br>I              | J           | Tristate               | 40      | 63       |

| PB[14]   | PCR[30] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[30]<br>E0UC[6]<br><br>CS3_0<br>ADC1_X[2]            | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC | I/O<br>I/O<br>—<br>0<br>I              | J           | Tristate               | 41      | 65       |

|          |         |                                    |                                                               |                               |                               |             | T<br>ttion             | Pin n   | umber    |

|----------|---------|------------------------------------|---------------------------------------------------------------|-------------------------------|-------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                      | Peripheral                    | I/O<br>direction <sup>2</sup> | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

|          | Port D  |                                    |                                                               |                               |                               |             |                        |         |          |

| PD[0]    | PCR[48] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[48]<br>—<br>—<br>—<br>WKPU[27] <sup>3</sup><br>ADC1_P[4] | SIUL<br>—<br>—<br>WKPU<br>ADC | <br> -<br> <br>               | Ι           | Tristate               |         | 41       |

| PD[1]    | PCR[49] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[49]<br>—<br>—<br>WKPU[28] <sup>3</sup><br>ADC1_P[5]      | SIUL<br>—<br>—<br>WKPU<br>ADC | <br><br>_<br> <br>            | Ι           | Tristate               | _       | 42       |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[50]<br>—<br>—<br>ADC1_P[6]                               | SIUL<br>   <br>ADC            | <br> -<br> <br>               | Ι           | Tristate               | _       | 43       |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[51]<br>—<br>—<br>ADC1_P[7]                               | SIUL<br> <br>ADC              | <br> -<br> <br>               | -           | Tristate               |         | 44       |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[52]<br>—<br>—<br>ADC1_P[8]                               | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | Ι           | Tristate               |         | 45       |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[53]<br>—<br>—<br>—<br>ADC1_P[9]                          | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | Ι           | Tristate               | _       | 46       |

| PD[6]    | PCR[54] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[54]<br>—<br>—<br>ADC1_P[10]                              | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | I           | Tristate               |         | 47       |

| PD[7]    | PCR[55] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[55]<br>—<br>—<br>ADC1_P[11]                              | SIUL<br>—<br>—<br>ADC         | <br><br><br>                  | Ι           | Tristate               | _       | 48       |

| Sumbo                |    | Parameter                                                                           | Conditions                                 | Va                    | Unit                  |      |

|----------------------|----|-------------------------------------------------------------------------------------|--------------------------------------------|-----------------------|-----------------------|------|

| Symbo                |    | Falameter                                                                           | Conditions                                 | Min                   | Max                   | Unit |

| V <sub>DD_BV</sub>   | SR | Voltage on VDD_BV (regulator supply) pin                                            | —                                          | -0.3                  | 6.0                   | V    |

|                      |    | with respect to ground $(V_{SS})$                                                   | Relative to V <sub>DD</sub>                | $V_{DD} - 0.3$        | V <sub>DD</sub> + 0.3 |      |

| $V_{SS\_ADC}$        | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> ) | _                                          | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| $V_{DD\_ADC}$        | SR | Voltage on VDD_HV_ADC (ADC                                                          | _                                          | -0.3                  | 6.0                   | V    |

|                      |    | reference) pin with respect to ground (V $_{\rm SS}$ )                              | Relative to V <sub>DD</sub>                | $V_{DD} - 0.3$        | V <sub>DD</sub> + 0.3 |      |

| V <sub>IN</sub>      | SR | Voltage on any GPIO pin with respect to                                             | _                                          | -0.3                  | 6.0                   | V    |

|                      |    | ground (V <sub>SS</sub> )                                                           | Relative to V <sub>DD</sub>                | $V_{DD}-0.3$          | V <sub>DD</sub> + 0.3 |      |

| I <sub>INJPAD</sub>  | SR | Injected input current on any pin during overload condition                         | _                                          | -10                   | 10                    | mA   |

| I <sub>INJSUM</sub>  | SR | Absolute sum of all injected input currents during overload condition               | _                                          | -50                   | 50                    | mA   |

| I <sub>AVGSEG</sub>  | SR | Sum of all the static I/O current within a                                          | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | —                     | 70                    | mA   |

|                      |    | supply segment <sup>1</sup>                                                         | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —                     | 64                    |      |

| ICORELV              | SR | Low voltage static current sink through<br>VDD_BV                                   | _                                          | —                     | 150                   | mA   |

| T <sub>STORAGE</sub> | SR | Storage temperature                                                                 | _                                          | -55                   | 150                   | °C   |

<sup>1</sup> Supply segments are described in Section 4.7.5, I/O pad current specification.

## NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

# 4.5 Recommended operating conditions

| bl | с | Parameter | Conditions | Value |   |  |

|----|---|-----------|------------|-------|---|--|

|    | • |           | Conditions | Min   | N |  |

## Table 11. Recommended operating conditions (3.3 V)

|                              |                 |   |                                                                                               |   | Min                   | Max                   |   |

|------------------------------|-----------------|---|-----------------------------------------------------------------------------------------------|---|-----------------------|-----------------------|---|

| V <sub>SS</sub>              | SR              | — | Digital ground on VSS_HV pins                                                                 | — | 0                     | 0                     | V |

| V <sub>DD</sub> <sup>1</sup> | SR              |   | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | — | 3.0                   | 3.6                   | V |

| V <sub>SS_LV</sub>           | <sup>2</sup> SR |   | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _ | V <sub>SS</sub> - 0.1 | V <sub>SS</sub> + 0.1 | V |

Symbo

Unit

| Symbo                           |    | с | Parameter                                                                              | Conditions                   | Va                   | lue                   | Unit |

|---------------------------------|----|---|----------------------------------------------------------------------------------------|------------------------------|----------------------|-----------------------|------|

| Symbo                           | 1  | C | Farameter                                                                              | Conditions                   | Min                  | Max                   | Unit |

| V <sub>DD_BV</sub> <sup>3</sup> | SR | — | Voltage on VDD_BV pin (regulator supply) with                                          | —                            | 3.0                  | 3.6                   | V    |

|                                 |    |   | respect to ground (V <sub>SS</sub> )                                                   | Relative to V <sub>DD</sub>  | $V_{DD} - 0.1$       | V <sub>DD</sub> + 0.1 |      |

| $V_{SS\_ADC}$                   | SR |   | Voltage on VSS_HV_ADC (ADC reference) pin<br>with respect to ground (V <sub>SS</sub> ) | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> + 0.1 | V    |

| $V_{\text{DD}\_\text{ADC}}{}^4$ | SR | — | Voltage on VDD_HV_ADC pin (ADC reference)                                              | —                            | 3.0 <sup>5</sup>     | 3.6                   | V    |

|                                 |    |   | with respect to ground ( $V_{SS}$ )                                                    | Relative to V <sub>DD</sub>  | $V_{DD} - 0.1$       | V <sub>DD</sub> + 0.1 |      |

| V <sub>IN</sub> SR — Volta      |    | — | Voltage on any GPIO pin with respect to ground                                         | —                            | $V_{SS} - 0.1$       | —                     | V    |

|                                 |    |   | (*SS/                                                                                  | Relative to $V_{DD}$         | —                    | V <sub>DD</sub> + 0.1 |      |

| I <sub>INJPAD</sub>             | SR |   | Injected input current on any pin during overload condition                            | —                            | -5                   | 5                     | mA   |

| I <sub>INJSUM</sub>             | SR |   | Absolute sum of all injected input currents during overload condition                  | —                            | -50                  | 50                    | mA   |

| TV <sub>DD</sub>                | SR | — | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                          | —                            | —                    | 0.25                  | V/µs |

| T <sub>A C-Grade</sub><br>Part  | SR |   | Ambient temperature under bias                                                         | $f_{CPU} \le 48 \text{ MHz}$ | -40                  | 85                    | °C   |

| T <sub>J C-Grade</sub><br>Part  | SR |   | Junction temperature under bias                                                        |                              | -40                  | 110                   |      |

| T <sub>A V-Grade</sub><br>Part  | SR |   | Ambient temperature under bias                                                         |                              | -40                  | 105                   |      |

| T <sub>J V</sub> -Grade<br>Part | SR |   | Junction temperature under bias                                                        |                              | -40                  | 130                   |      |

| T <sub>A M</sub> -Grade<br>Part | SR |   | Ambient temperature under bias                                                         | ]                            | -40                  | 125                   |      |

| T <sub>J M</sub> -Grade<br>Part | SR |   | Junction temperature under bias                                                        | ]                            | -40                  | 150                   |      |

Table 11. Recommended operating conditions (3.3 V) (continued)

$^1$  100 nF capacitance needs to be provided between each  $V_{\text{DD}}/V_{\text{SS}}$  pair.

$^2~$  330 nF capacitance needs to be provided between each V\_{DD\_LV}/V\_{SS\_LV} supply pair.

<sup>3</sup> 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

$^4~$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation

| Symbo           | Symbol C |   | Parameter                     | Conditions | Va  | Unit |   |

|-----------------|----------|---|-------------------------------|------------|-----|------|---|

| Cymbe           |          |   | i arameter                    | Conditions | Min | Мах  |   |

| V <sub>SS</sub> | SR       | _ | Digital ground on VSS_HV pins | _          | 0   | 0    | V |

Table 12. Recommended operating conditions (5.0 V)

| Symbo                           | .1 | с | Parameter                                                                         | Conditions                   | Va                   | lue                   | Unit |

|---------------------------------|----|---|-----------------------------------------------------------------------------------|------------------------------|----------------------|-----------------------|------|

| Symbo                           | ,  | C | Falameter                                                                         | Conditions                   | Min                  | Max                   | Unit |

| $V_{DD}^{1}$                    | SR | _ | Voltage on VDD_HV pins with respect to ground                                     | —                            | 4.5                  | 5.5                   | V    |

|                                 |    |   | (V <sub>SS</sub> )                                                                | Voltage drop <sup>2</sup>    | 3.0                  | 5.5                   |      |

| $V_{SS_{LV}}^{3}$               | SR |   | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V_SS) | _                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> + 0.1 | V    |

| $V_{DD_BV}^4$                   | SR | _ | Voltage on VDD_BV pin (regulator supply) with                                     | —                            | 4.5                  | 5.5                   | V    |

|                                 |    |   | respect to ground (V <sub>SS</sub> )                                              | Voltage drop <sup>(2)</sup>  | 3.0                  | 5.5                   |      |

|                                 |    |   |                                                                                   | Relative to $V_{DD}$         | $V_{DD} - 0.1$       | V <sub>DD</sub> + 0.1 |      |

| $V_{SS\_ADC}$                   | SR |   | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V $_{\rm SS}$   | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> + 0.1 | V    |

| $V_{DD_ADC}^5$                  | SR | — | Voltage on VDD_HV_ADC pin (ADC reference) with                                    | —                            | 4.5                  | 5.5                   | V    |

|                                 |    |   | respect to ground (V <sub>SS</sub> )                                              | Voltage drop <sup>(2)</sup>  | 3.0                  | 5.5                   |      |

|                                 |    |   |                                                                                   | Relative to V <sub>DD</sub>  | $V_{DD} - 0.1$       | V <sub>DD</sub> + 0.1 |      |

| V <sub>IN</sub> SF              |    |   | Voltage on any GPIO pin with respect to ground                                    | —                            | $V_{SS} - 0.1$       | —                     | V    |

|                                 |    |   | (V <sub>SS</sub> )                                                                | Relative to V <sub>DD</sub>  | —                    | V <sub>DD</sub> + 0.1 |      |

| I <sub>INJPAD</sub>             | SR |   | Injected input current on any pin during overload condition                       | —                            | -5                   | 5                     | mA   |

| I <sub>INJSUM</sub>             | SR | _ | Absolute sum of all injected input currents during overload condition             |                              | -50                  | 50                    | mA   |

| TV <sub>DD</sub>                | SR |   | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                     | —                            | —                    | 0.25                  | V/µs |

| T <sub>A C-Grade</sub><br>Part  | SR | — | Ambient temperature under bias                                                    | $f_{CPU} \le 48 \text{ MHz}$ | -40                  | 85                    | °C   |

| T <sub>J C-Grade</sub><br>Part  | SR | — | Junction temperature under bias                                                   |                              | -40                  | 110                   |      |

| T <sub>A V-Grade</sub><br>Part  | SR | — | Ambient temperature under bias                                                    |                              | -40                  | 105                   |      |

| T <sub>J V-Grade</sub><br>Part  | SR |   | Junction temperature under bias                                                   |                              | -40                  | 130                   |      |

| T <sub>A M-Grade</sub><br>Part  | SR | — | Ambient temperature under bias                                                    | 1                            | -40                  | 125                   |      |

| T <sub>J M</sub> -Grade<br>Part | SR |   | Junction temperature under bias                                                   |                              | -40                  | 150                   |      |

$^1\,$  100 nF capacitance needs to be provided between each V\_DD/V\_SS pair.

<sup>2</sup> Full device operation is guaranteed by design when the voltage drops below 4.5 V down to 3.6 V. However, certain analog electrical characteristics will not be guaranteed to stay within the stated limits.

$^3\,$  330 nF capacitance needs to be provided between each V\_{DD\_LV}\!/V\_{SS\_LV} supply pair.

- <sup>4</sup> 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

- $^{5}$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

- <sup>6</sup> Guaranteed by device validation

$$T_{J} = T_{A} + (P_{D} \times R_{\theta JA})$$

Eqn. 1

Where:

$T_A$  is the ambient temperature in °C.

$R_{\theta JA}$  is the package junction-to-ambient thermal resistance, in °C/W.

$P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ .

$P_{INT}$  is the product of  $I_{DD}$  and  $V_{DD}$ , expressed in watts. This is the chip internal power.

P<sub>I/O</sub> represents the power dissipation on input and output pins; user determined.

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_{D} = K / (T_{J} + 273 °C)$$

Eqn. 2

Therefore, solving equations 1 and 2:

$$K = P_D x (T_A + 273 °C) + R_{\theta JA} x P_D^2$$

Eqn. 3

Where:

K is a constant for the particular part, which may be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  may be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

# 4.7 I/O pad electrical characteristics

## 4.7.1 I/O pad types

The device provides four main I/O pad types depending on the associated alternate functions:

- Slow pads—These pads are the most common pads, providing a good compromise between transition time and low electromagnetic emission.

- Medium pads—These pads provide transition fast enough for the serial communication channels with controlled current to reduce electromagnetic emission.

- Input only pads—These pads are associated to ADC channels (ADC\_P[X]) providing low input leakage.

Medium pads can use slow configuration to reduce electromagnetic emission except for PC[1], that is medium only, at the cost of reducing AC performance.

# 4.7.2 I/O input DC characteristics

Table 14 provides input DC electrical characteristics as described in Figure 4.

- Table 16 provides output driver characteristics for I/O pads when in SLOW configuration.

- Table 17 provides output driver characteristics for I/O pads when in MEDIUM configuration.

| Symt             | Symbol |   | Parameter              | Conditions <sup>1</sup>                            |                     | Value |     |     | Unit |

|------------------|--------|---|------------------------|----------------------------------------------------|---------------------|-------|-----|-----|------|

| Synn             | 501    | C | raiametei              | Conditions                                         |                     |       | Тур | Max |      |

| I <sub>WPU</sub> | СС     | Ρ | Weak pull-up current   | $V_{IN} = V_{IL}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | PAD3V5V = 0         | 10    | —   | 150 | μA   |

|                  |        | С | absolute value         |                                                    | $PAD3V5V = 1^2$     | 10    | —   | 250 |      |

|                  |        | Ρ |                        | $V_{IN} = V_{IL}, V_{DD} = 3.3 \text{ V} \pm 10\%$ | PAD3V5V = 1         | 10    | —   | 150 |      |

| $ I_{WPD} $      | СС     | Ρ | Weak pull-down current | $V_{IN} = V_{IH}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | PAD3V5V = 0         | 10    | —   | 150 | μA   |

|                  |        | С | absolute value         |                                                    | $PAD3V5V = 1^{(2)}$ | 10    | —   | 250 |      |

|                  |        | Ρ |                        | $V_{IN} = V_{IH}, V_{DD} = 3.3 \text{ V} \pm 10\%$ | PAD3V5V = 1         | 10    | —   | 150 |      |

## Table 15. I/O pull-up/pull-down DC electrical characteristics

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

<sup>2</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

## Table 16. SLOW configuration output buffer electrical characteristics

| Sym             | hal | 6 | Parameter                               |                                                                                                          | Conditions <sup>1</sup>                                                                             | v                     | Unit |                    |      |

|-----------------|-----|---|-----------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|------|--------------------|------|

| Jym             | 001 | C | Farameter                               |                                                                                                          | Conditions                                                                                          |                       |      | Max                | Unit |

| V <sub>OH</sub> | CC  | Ρ | Output high level<br>SLOW configuration | Push Pull $I_{OH} = -2 \text{ mA}$ ,<br>$V_{DD} = 5.0 \text{ V} \pm 10\%$ , PAD3V5V = 0<br>(recommended) |                                                                                                     | 0.8V <sub>DD</sub>    |      | _                  | V    |

|                 |     | С |                                         |                                                                                                          | I <sub>OH</sub> = -2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>                 | 0.8V <sub>DD</sub>    | —    | _                  |      |

|                 |     | С |                                         |                                                                                                          | I <sub>OH</sub> = −1 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)             | V <sub>DD</sub> – 0.8 | _    | _                  |      |

| V <sub>OL</sub> | СС  | Ρ | Output low level<br>SLOW configuration  | Push Pull                                                                                                | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | —                     | _    | 0.1V <sub>DD</sub> | V    |

|                 |     | С |                                         |                                                                                                          | I <sub>OL</sub> = 2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(2)</sup>                | _                     | —    | 0.1V <sub>DD</sub> |      |

|                 |     | С |                                         |                                                                                                          | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended) | —                     | —    | 0.5                |      |

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

| Symbol                             |    | с                                                                     | Parameter                          | Condi                                        | tions <sup>1</sup>                            |     | Value |      | Unit |

|------------------------------------|----|-----------------------------------------------------------------------|------------------------------------|----------------------------------------------|-----------------------------------------------|-----|-------|------|------|

| Symbol                             |    | C                                                                     | Farameter                          | Condi                                        | 10115                                         | Min | Тур   | Max  | Onic |

| I <sub>SWTSLW</sub> ,2             | СС | D                                                                     | Dynamic I/O current<br>for SLOW    | C <sub>L</sub> = 25 pF                       | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     | _     | 20   | mA   |

|                                    |    |                                                                       | configuration                      |                                              | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | —     | 16   |      |

| I <sub>SWTMED</sub> <sup>(2)</sup> | СС | D                                                                     | for MEDIUM                         | C <sub>L</sub> = 25 pF                       | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   | —     | 29   | mA   |

|                                    |    |                                                                       | configuration                      |                                              | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |       | 17   |      |

| I <sub>RMSSLW</sub>                | СС | D                                                                     | Root mean square                   | C <sub>L</sub> = 25 pF, 2 MHz                | $V_{DD} = 5.0 V \pm 10\%,$                    |     | —     | 2.3  | mA   |

|                                    |    |                                                                       | I/O current for SLOW configuration | $10^{\circ} = 25 \text{ pc} = 4 \text{ MHz}$ | _                                             | —   | 3.2   |      |      |

|                                    |    |                                                                       | <b>3</b>                           | C <sub>L</sub> = 100 pF, 2 MHz               |                                               | _   | —     | 6.6  |      |

|                                    |    |                                                                       |                                    | C <sub>L</sub> = 25 pF, 2 MHz                | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     | _     | 1.6  |      |

|                                    |    |                                                                       |                                    | C <sub>L</sub> = 25 pF, 4 MHz                | PAD3V5V = 1                                   |     | —     | 2.3  |      |

|                                    |    |                                                                       |                                    | C <sub>L</sub> = 100 pF, 2 MHz               |                                               |     |       | 4.7  |      |

| IRMSMED                            | СС | D                                                                     | Root mean square                   | C <sub>L</sub> = 25 pF, 13 MHz               | $V_{DD} = 5.0 V \pm 10\%$ ,                   |     |       | 6.6  | mA   |

|                                    |    |                                                                       | I/O current for<br>MEDIUM          | C <sub>L</sub> = 25 pF, 40 MHz               | PAD3V5V = 0                                   |     |       | 13.4 | 1    |

|                                    |    |                                                                       | configuration                      | C <sub>L</sub> = 100 pF, 13 MHz              |                                               | _   | —     | 18.3 |      |

|                                    |    |                                                                       |                                    | C <sub>L</sub> = 25 pF, 13 MHz               | $V_{DD} = 3.3 V \pm 10\%$ ,                   | _   | —     | 5    |      |

|                                    |    |                                                                       |                                    | C <sub>L</sub> = 25 pF, 40 MHz               | PAD3V5V = 1                                   | —   | —     | 8.5  |      |

|                                    |    |                                                                       |                                    | C <sub>L</sub> = 100 pF, 13 MHz              |                                               | _   | —     | 11   |      |

| I <sub>AVGSEG</sub>                | SR | D                                                                     |                                    | V <sub>DD</sub> = 5.0 V ± 10%, P             | AD3V5V = 0                                    |     | _     | 70   | mA   |

|                                    |    | I/O current within a supply segment $V_{DD} = 3.3 \text{ V} \pm 10\%$ |                                    | V <sub>DD</sub> = 3.3 V ± 10%, P             | AD3V5V = 1                                    | —   | —     | 65   |      |

## Table 20. I/O consumption

<sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

Table 21 provides the weight of concurrent switching I/Os.

In order to ensure device functionality, the sum of the weight of concurrent switching I/Os on a single segment should remain below 100%.

|        |                      | 100 LQFF | P/64 LQFP    |         |  |

|--------|----------------------|----------|--------------|---------|--|

| Pad    | Weigl                | nt 5 V   | Weight 3.3 V |         |  |

|        | SRC <sup>2</sup> = 0 | SRC = 1  | SRC = 0      | SRC = 1 |  |

| PC[0]  | 6%                   | 9%       | 7%           | 8%      |  |

| PE[2]  | 7%                   | 10%      | 8%           | 9%      |  |

| PE[3]  | 7%                   | 10%      | 9%           | 9%      |  |

| PC[5]  | 8%                   | 11%      | 9%           | 10%     |  |

| PC[4]  | 8%                   | 11%      | 9%           | 10%     |  |

| PE[4]  | 8%                   | 12%      | 10%          | 10%     |  |

| PE[5]  | 8%                   | 12%      | 10%          | 11%     |  |

| PE[6]  | 9%                   | 12%      | 10%          | 11%     |  |

| PE[7]  | 9%                   | 12%      | 10%          | 11%     |  |

| PC[12] | 9%                   | 13%      | 11%          | 11%     |  |

| PC[13] | 9%                   | 9%       | 11%          | 11%     |  |

| PC[8]  | 9%                   | 9%       | 11%          | 11%     |  |

| PB[2]  | 9%                   | 13%      | 11%          | 12%     |  |

## Table 21. I/O weight<sup>1</sup> (continued)

<sup>1</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% \text{ / } 5.0 \text{ V} \pm 10\%, \text{ } T_{A} = -40 \text{ to } 125 \text{ °C}, \text{ unless otherwise specified}$ <sup>2</sup> SRC: "Slew Rate Control" bit in SIU\_PCR

#### **RESET** electrical characteristics 4.8

The device implements a dedicated bidirectional RESET pin.

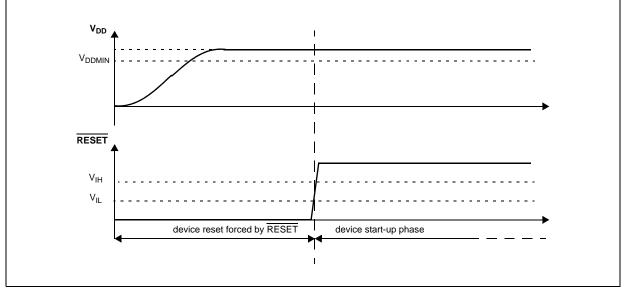

Figure 5. Start-up reset requirements

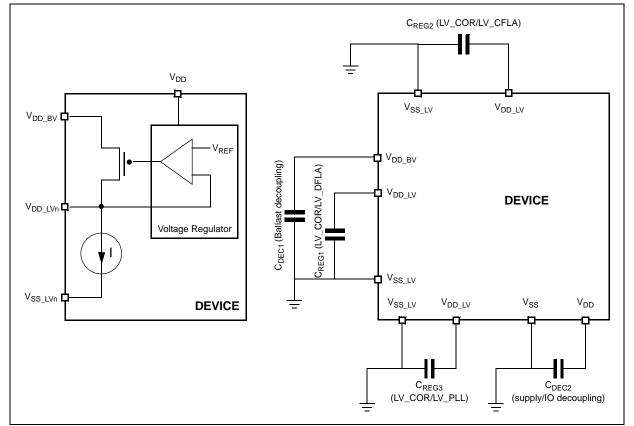

- LV\_CFLA: Low voltage supply for code flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_DFLA: Low voltage supply for data flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_PLL: Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

Figure 7. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three  $V_{DD_LV}/V_{SS_LV}$  supply pairs to ensure stable voltage (see Section 4.5, Recommended operating conditions).

| Symbol            |    | с | Parameter                                        | Conditions <sup>1</sup>    |     | Unit |     |           |

|-------------------|----|---|--------------------------------------------------|----------------------------|-----|------|-----|-----------|

|                   |    | Ŭ | i arameter                                       | Conditions                 | Min | Тур  | Max | • · · · · |

| C <sub>REGn</sub> | SR |   | Internal voltage regulator external capacitance  | —                          | 200 | _    | 500 | nF        |

| R <sub>REG</sub>  | SR |   | Stability capacitor equivalent serial resistance | Range:<br>10 kHz to 20 MHz | _   | _    | 0.2 | Ω         |

Table 23. Voltage regulator electrical characteristics

# 4.9.2 Low voltage detector electrical characteristics

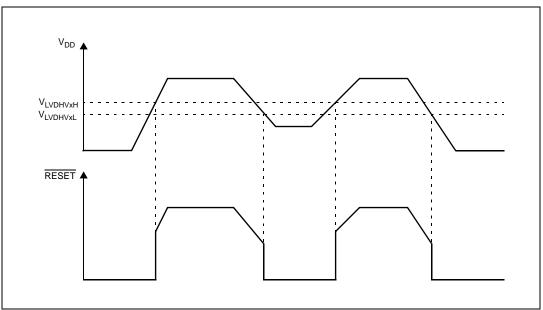

The device implements a power-on reset (POR) module to ensure correct power-up initialization, as well as five low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD}$  LV voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV3B monitors V<sub>DD\_BV</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27\_VREG in device reference manual)

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual)

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

Figure 8. Low voltage detector vs reset

| Symbol                |                                                   | С | Ratings                                               | Conditions                                           | Class | Max value | Unit |

|-----------------------|---------------------------------------------------|---|-------------------------------------------------------|------------------------------------------------------|-------|-----------|------|

| V <sub>ESD(HBM)</sub> | CC                                                |   | Electrostatic discharge voltage<br>(Human Body Model) | $T_A = 25 \degree C$<br>conforming to AEC-Q100-002   | H1C   | 2000      | V    |

| V <sub>ESD(MM)</sub>  | CC                                                |   | Electrostatic discharge voltage<br>(Machine Model)    | T <sub>A</sub> = 25 °C<br>conforming to AEC-Q100-003 | M2    | 200       | V    |

| V <sub>ESD(CDM)</sub> | CC                                                |   | Electrostatic discharge voltage                       | $T_{A} = 25 ^{\circ}C$                               | C3A   | 500       | V    |

|                       | (Charged Device Model) conforming to AEC-Q100-011 |   |                                                       | 750 (corners)                                        | V     |           |      |

| Table 33. | ESD | absolute | maximum | ratings <sup>1 2</sup> |

|-----------|-----|----------|---------|------------------------|

|-----------|-----|----------|---------|------------------------|

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

## 4.12.3.2 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

#### Table 34. Latch-up results

| Syn | nbol | С | Parameter             | Conditions                                   | Class      |

|-----|------|---|-----------------------|----------------------------------------------|------------|

| LU  | CC   | Т | Static latch-up class | $T_A = 125 \text{ °C}$ conforming to JESD 78 | II level A |

# 4.13 Fast external crystal oscillator (4 to 16 MHz) electrical characteristics

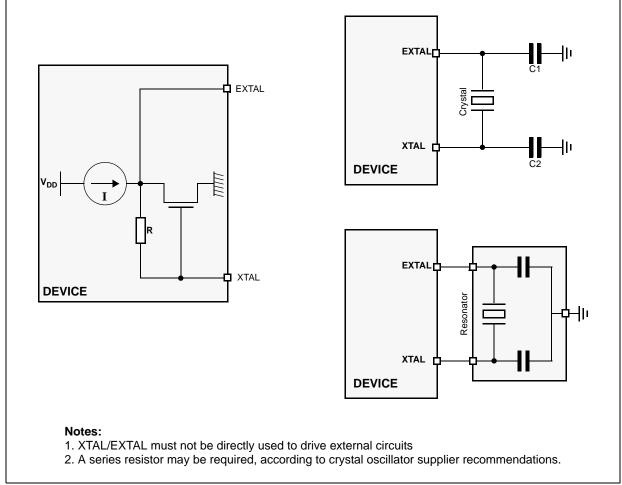

The device provides an oscillator/resonator driver. Figure 9 describes a simple model of the internal oscillator driver and provides an example of a connection for an oscillator or a resonator.

Table 35 provides the parameter description of 4 MHz to 16 MHz crystals used for the design simulations.

Figure 9. Crystal oscillator and resonator connection scheme

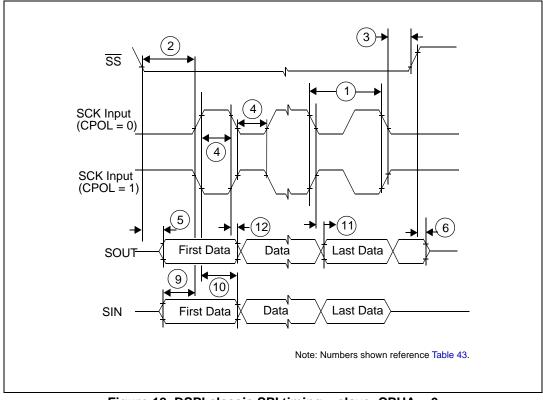

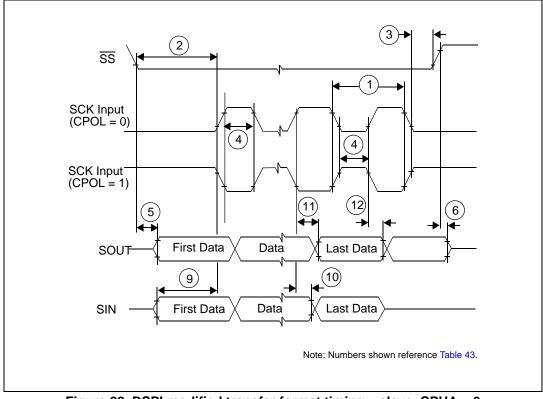

Figure 18. DSPI classic SPI timing – slave, CPHA = 0

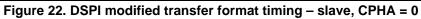

Figure 26. 100 LQFP package mechanical drawing (Part 1 of 3)

Abbreviations

| Abbreviation | Meaning                                                              |

|--------------|----------------------------------------------------------------------|

| OPWMCB       | Center aligned output pulse width modulation buffered with dead time |

| OPWMT        | Output pulse width modulation trigger                                |

| PWM          | Pulse width modulation                                               |

| SAIC         | Single action input capture                                          |

| SAOC         | Single action output compare                                         |

| SCK          | Serial communications clock                                          |

| SOUT         | Serial data out                                                      |

| TBD          | To be defined                                                        |

| ТСК          | Test clock input                                                     |

| TDI          | Test data input                                                      |

| TDO          | Test data output                                                     |

| TMS          | Test mode select                                                     |

## Table A-1. Abbreviations (continued)

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MPC5602D Rev. 6 01/2013 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org © Freescale Semiconductor, Inc. 2009–2013. All rights reserved.