Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | C500                                                                         |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 1.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.25V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-QFP                                                                       |

| Supplier Device Package    | PG-MQFP-44-2                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c505ca4emcabxuma1 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2000-12

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2000. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# Table 2Pin Definitions and Functions

| Symbol    | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                   |

|-----------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0-P1.7 | 40-44,1-3  | I/O       | arrangement. Port 1 pins<br>or as analog inputs of th<br>have 1's written to them<br>transistors and in that a<br>inputs, port 1 pins being<br>current ( $I_{IL}$ , in the DC<br>internal pullup transistor<br>used as analog inputs via<br>As secondary digital func<br>timer, clock, capture and<br>corresponding to a a<br>programmed to a one (1) | tions, port 1 contains the interrupt,<br>d compare pins. The output latch<br>secondary function must be<br>for that function to operate (except<br>). The secondary functions are |

|           | 40         |           | P1.0 / AN0 / ĪNT3 / CC0                                                                                                                                                                                                                                                                                                                               | Analog input channel 0<br>interrupt 3 input /<br>capture/compare channel 0 I/O                                                                                                    |

|           | 41         |           | P1.1 / AN1 / INT4 / CC1                                                                                                                                                                                                                                                                                                                               | Analog input channel 1/<br>interrupt 4 input /<br>capture/compare channel 1 I/O                                                                                                   |

|           | 42         |           | P1.2 / AN2 / INT5 / CC2                                                                                                                                                                                                                                                                                                                               | · ·                                                                                                                                                                               |

|           | 43         |           | P1.3 / AN3 / INT6 / CC3                                                                                                                                                                                                                                                                                                                               | Analog input channel 3<br>interrupt 6 input /<br>capture/compare channel 3 I/O                                                                                                    |

|           | 44         |           | P1.4 / AN4                                                                                                                                                                                                                                                                                                                                            | Analog input channel 4                                                                                                                                                            |

|           | 1          |           | P1.5 / AN5 / T2EX                                                                                                                                                                                                                                                                                                                                     | Analog input channel 5 / Timer 2<br>external reload / trigger input                                                                                                               |

|           | 2          |           | P1.6 / AN6 / CLKOUT                                                                                                                                                                                                                                                                                                                                   | Analog input channel 6 /<br>system clock output                                                                                                                                   |

|           | 3          |           | P1.7 / AN7 / T2                                                                                                                                                                                                                                                                                                                                       | Analog input channel 7 /<br>counter 2 input                                                                                                                                       |

|           |            |           |                                                                                                                                                                                                                                                                                                                                                       | order address byte during program<br>COM versions (i.e. C505(C)(A)-2R/                                                                                                            |

\*) I = Input

# Table 2Pin Definitions and Functions (cont'd)

| Symbol    | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2.0-P2.7 | 18-25      | Ι/Ο       | <b>Port 2</b><br>is a an 8-bit quasi-bidirectional I/O port with internal pullup<br>resistors. Port 2 pins that have 1's written to them are pulled<br>high by the internal pullup resistors, and in that state can be<br>used as inputs. As inputs, port 2 pins being externally pulled<br>low will source current ( $I_{IL}$ , in the DC characteristics)<br>because of the internal pullup resistors. Port 2 emits the<br>high-order address byte during fetches from external<br>program memory and during accesses to external data<br>memory that use 16-bit addresses (MOVX @DPTR). In this<br>application it uses strong internal pullup transistors when<br>issuing 1s. During accesses to external data memory that<br>use 8-bit addresses (MOVX @Ri), port 2 issues the<br>contents of the P2 special function register and uses only<br>the internal pullup resistors. |

| PSEN      | 26         | 0         | The <b>Program Store Enable</b><br>output is a control signal that enables the external program<br>memory to the bus during external fetch operations. It is<br>activated every three oscillator periods except during<br>external data memory accesses. Remains high during<br>internal program execution. This pin should not be driven<br>during reset operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALE       | 27         | 0         | The Address Latch Enable<br>output is used for latching the low-byte of the address into<br>external memory during normal operation. It is activated<br>every three oscillator periods except during an external data<br>memory access. When instructions are executed from<br>internal ROM or OTP ( $\overline{EA}$ =1) the ALE generation can be<br>disabled by bit EALE in SFR SYSCON.<br>ALE should not be driven during reset operation.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

\*) I = Input

# Table 2Pin Definitions and Functions (cont'd)

| Symbol            | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ĒĀ                | 29         | I         | External Access Enable<br>When held at high level, instructions are fetched from the<br>nternal program memory when the PC is less than 4000<br>C505(C)(A)-2R) or 8000 <sub>H</sub> (C505A-4R/C505CA-4R/C505A<br>4E/C505CA-4E). When held at low level, the C505 fetche<br>all instructions from external program memory.<br>For the C505 romless versions (i.e. C505-L, C505C-L<br>C505A-L and C505CA-L) this pin must be tied low.<br>For the ROM protection version EA pin is latched durin<br>eset.                                                           |  |  |  |

| P0.0-P0.7         | 37-30      | I/O       | <b>Port 0</b><br>is an 8-bit open-drain bidirectional I/O port. Port 0 pins that<br>have 1's written to them float, and in that state can be used<br>as high-impendance inputs. Port 0 is also the multiplexed<br>low-order address and data bus during accesses to external<br>program or data memory. In this application it uses strong<br>internal pullup transistors when issuing 1's.<br>Port 0 also outputs the code bytes during program<br>verification in the C505 ROM versions. External pullup<br>resistors are required during program verification. |  |  |  |

| VAREF             | 38         | _         | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V <sub>AGND</sub> | 39         | -         | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| V <sub>SS</sub>   | 16         | -         | Ground (0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| V <sub>DD</sub>   | 17         | -         | Power Supply (+5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

\*) I = Input

#### **Reset and System Clock**

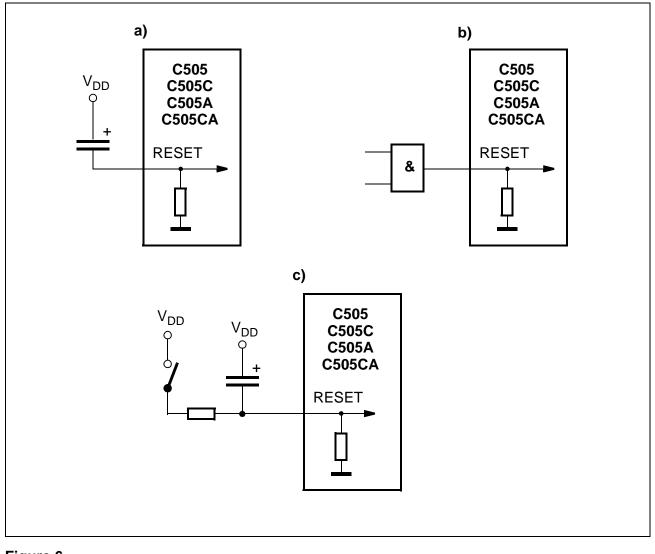

The reset input is an active high input at pin RESET. Since the reset is synchronized internally, the RESET pin must be held high for at least two machine cycles (12 oscillator periods) while the oscillator is running. A pulldown resistor is internally connected to  $V_{\rm SS}$  to allow a power-up reset with an external capacitor only. An automatic reset can be obtained when  $V_{\rm DD}$  is applied by connecting the RESET pin to  $V_{\rm DD}$  via a capacitor. Figure 6 shows the possible reset circuitries.

Figure 6 Reset Circuitries

#### **Multiple Datapointers**

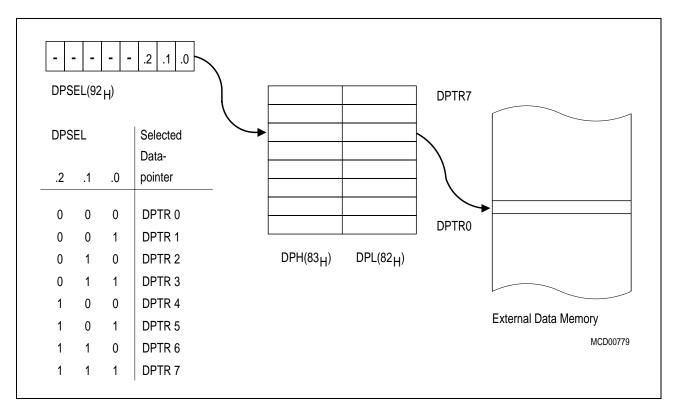

As a functional enhancement to the standard 8051 architecture, the C505 contains eight 16-bit datapointers instead of only one datapointer. The instruction set uses just one of these datapointers at a time. The selection of the actual datapointer is done in the special function regsiter DPSEL. **Figure 8** illustrates the datapointer addressing mechanism.

Figure 8 External Data Memory Addressing using Multiple Datapointers

#### **Enhanced Hooks Emulation Concept**

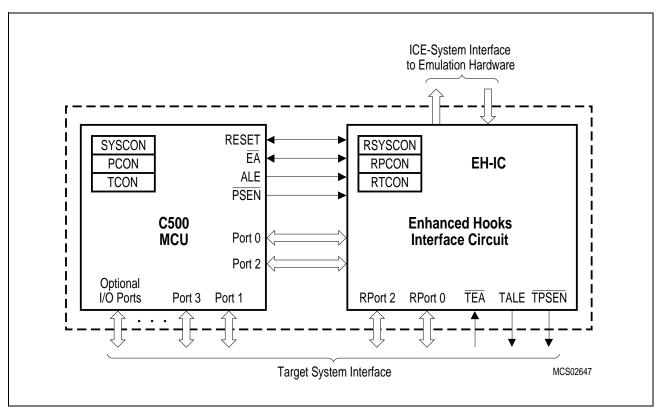

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative way to control the execution of C500 MCUs and to gain extensive information on the internal operation of the controllers. Emulation of on-chip ROM based programs is possible, too.

Each production chip has built-in logic for the supprt of the Enhanced Hooks Emulation Concept. Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation and production chips are identical.

The Enhanced Hooks Technology<sup>™ 1)</sup>, which requires embedded logic in the C500 allows the C500 together with an EH-IC to function similar to a bond-out chip. This simplifies the design and reduces costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate all operating modes of the different versions of the C500 microcontrollers. This includes emulation of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in single step mode and to read the SFRs after a break.

### Figure 9

### Basic C500 MCU Enhanced Hooks Concept Configuration

Port 0, port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks Emulation Concept to control the operation of the device during emulation and to transfer informations about the programm execution and data transfer between the external emulation hardware (ICE-system) and the C500 MCU.

<sup>&</sup>quot;Enhanced Hooks Technology" is a trademark and patent of Metalink Corporation licensed to Infineon Technologies.

### Special Function Registers

The registers, except the program counter and the four general purpose register banks, reside in the special function register area. The special function register area consists of two portions : the standard special function register area and the mapped special function register area. Five special function register of the C505 (PCON1,P1ANA, VR0, VR1, VR2) are located in the mapped special function register area. For accessing the mapped special function register area, bit RMAP in special function register SYSCON must be set. All other special function registers are located in the standard special function register area which is accessed when RMAP is cleared ("0").

The registers and data locations of the CAN controller (CAN-SFRs) are located in the external data memory area at addresses  $F700_{\text{H}}$  to  $F7FF_{\text{H}}$ .

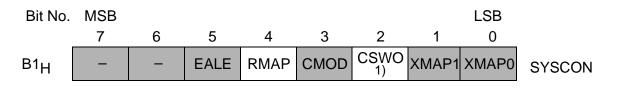

# Special Function Register SYSCON (Address B1<sub>H</sub>) (C505CA only)

Reset Value : XX100X01<sub>B</sub> Reset Value : XX100001<sub>B</sub>

The functions of the shaded bits are not described here. 1) This bit is only available in the C505CA.

| Bit  | Function                                                                                                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP | <ul> <li>Special function register map bit</li> <li>RMAP = 0 : The access to the non-mapped (standard) special function register area is enabled.</li> <li>RMAP = 1 : The access to the mapped special function register area is enabled.</li> </ul> |

| CSWO | CAN Controller switch-off bit<br>CSWO = 0 : CAN Controller is enabled (default after reset).<br>CSWO = 1 : CAN Controller is switched off.                                                                                                           |

As long as bit RMAP is set, mapped special function register area can be accessed. This bit is not cleared by hardware automatically. Thus, when non-mapped/mapped registers are to be accessed, the bit RMAP must be cleared/set respectively by software.

All SFRs with addresses where address bits 0-2 are 0 (e.g.  $80_H$ ,  $88_H$ ,  $90_H$ ,  $98_H$ , ...,  $F8_H$ ,  $FF_H$ ) are bitaddressable.

The 52 special function registers (SFRs) in the standard and mapped SFR area include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. The SFRs of the C505 are listed in **Table 3** and **Table 4**. In **Table 3** they are organized in groups which refer to the functional blocks of the C505. The CAN-SFRs (applicable for the C505C and C505CA only) are also included in **Table 3**. **Table 4** illustrates the contents of the SFRs in numeric order of their addresses. **Table 5** list the CAN-SFRs in numeric order of their addresses.

# Table 3 Special Function Registers - Functional Blocks (cont'd)

| Block       | Symbol                 | Name                                      | Address                       | Contents after<br>Reset             |

|-------------|------------------------|-------------------------------------------|-------------------------------|-------------------------------------|

| Ports       | P0                     | Port 0                                    | 80 <sub>H</sub> <sup>1)</sup> | FF <sub>H</sub>                     |

|             | P1                     | Port 1                                    | 90H <sup>1)</sup>             | FFH                                 |

|             | P1ANA <sup>2) 4)</sup> | Port 1 Analog Input Selection Register    | 90H <sup>1)</sup>             | FFH                                 |

|             | P2                     | Port 2                                    | A0H <sup>1)</sup>             | FFH                                 |

|             | P3                     | Port 3                                    | B0H <sup>1)</sup>             | FFH                                 |

|             | P4                     | Port 4                                    | E8H <sup>1)</sup>             | XXXXXX11 <sub>B</sub>               |

| Serial      | ADCON0 <sup>2)</sup>   | A/D Converter Control Register 0          | D8H <sup>1)</sup>             | 00X00000B <sup>3)</sup>             |

| Channel     |                        | Power Control Register                    | 87 <sub>H</sub>               | 00 <sub>H</sub>                     |

|             | SBUF                   | Serial Channel Buffer Register            | 99 <sub>H</sub>               | XX <sub>H</sub> <sup>3)</sup>       |

|             | SCON                   | Serial Channel Control Register           | 98H <sup>1)</sup>             | 00 <sub>H</sub>                     |

|             | SRELL                  | Serial Channel Reload Register, low byte  | AAH                           | D9 <sub>H</sub>                     |

|             | SRELH                  | Serial Channel Reload Register, high byte | BAH                           | XXXXXX11 <sub>B<sup>3)</sup></sub>  |

| Timer 0/    | TCON                   | Timer 0/1 Control Register                | 88H <sup>1)</sup>             | 00 <sub>H</sub>                     |

| Timer 1     | тно                    | Timer 0, High Byte                        | 8C <sub>H</sub>               | 00H                                 |

|             | TH1                    | Timer 1, High Byte                        | 8D <sub>H</sub>               | 00H                                 |

|             | TLO                    | Timer 0, Low Byte                         | 8A <sub>H</sub>               | 00 <sub>H</sub>                     |

|             | TL1                    | Timer 1, Low Byte                         | 8B <sub>H</sub>               | 00 <sub>H</sub>                     |

|             | TMOD                   | Timer Mode Register                       | 89 <sub>H</sub>               | 00 <sub>H</sub>                     |

| Compare/    | CCEN                   | Comp./Capture Enable Reg.                 | C1 <sub>H</sub>               | 00 <sub>H</sub> <sup>3)</sup>       |

| Capture     | CCH1                   | Comp./Capture Reg. 1, High Byte           | C3 <sub>H</sub>               | 00H                                 |

| Unit /      | CCH2                   | Comp./Capture Reg. 2, High Byte           | C5 <sub>H</sub>               | 00 <sub>H</sub>                     |

| Timer 2     | CCH3                   | Comp./Capture Reg. 3, High Byte           | C7 <sub>H</sub>               | 00 <sub>H</sub>                     |

|             | CCL1                   | Comp./Capture Reg. 1, Low Byte            | C2 <sub>H</sub>               | 00H                                 |

|             | CCL2                   | Comp./Capture Reg. 2, Low Byte            | C4 <sub>H</sub>               | 00 <sub>H</sub>                     |

|             | CCL3                   | Comp./Capture Reg. 3, Low Byte            | C6 <sub>H</sub>               | 00H                                 |

|             | CRCH                   | Reload Register High Byte                 | CBH                           | 00H                                 |

|             | CRCL                   | Reload Register Low Byte                  | CAH                           | 00H                                 |

|             | TH2                    | Timer 2, High Byte                        | CDH                           | 00H                                 |

|             | TL2                    | Timer 2, Low Byte                         | CCH                           | 00H                                 |

|             | T2CON                  | Timer 2 Control Register                  | C8 <sub>H</sub> <sup>1)</sup> | 00X00000 <sub>B</sub> <sup>3)</sup> |

|             | IEN0 <sup>2)</sup>     | Interrupt Enable Register 0               | A8H <sup>1)</sup>             | 00H                                 |

|             | IEN1 <sup>2)</sup>     | Interrupt Enable Register 1               | B8H <sup>1)</sup>             | 00H                                 |

| Watchdog    | WDTREL                 | Watchdog Timer Reload Register            | 86 <sub>H</sub>               | 00 <sub>H</sub>                     |

| . ratoridoy | IEN0 <sup>2)</sup>     | Interrupt Enable Register 0               | A8H <sup>1)</sup>             | 00H                                 |

|             | IEN1 <sup>2)</sup>     | Interrupt Enable Register 1               | B8H <sup>1)</sup>             | 00H                                 |

|             | IP0 <sup>2)</sup>      | Interrupt Priority Register 0             | A9 <sub>H</sub>               | 00H                                 |

| Pow. Save   |                        | Power Control Register                    | 87 <sub>H</sub>               | 00 <sub>H</sub>                     |

| Modes       | PCON1 <sup>4)</sup>    | Power Control Register 1                  | 88H <sup>1)</sup>             | 0XX0XXXX <sub>B</sub> <sup>3)</sup> |

|             |                        |                                           | N                             | D                                   |

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) "X" means that the value is undefined and the location is reserved

4) SFR is located in the mapped SFR area. For accessing this SFR, bit RMAP in SFR SYSCON must be set.

### **Timer 2 Compare Modes**

The compare function of a timer/register combination operates as follows : the 16-bit value stored in a compare or compare/capture register is compared with the contents of the timer register; if the count value in the timer register matches the stored value, an appropriate output signal is generated at a corresponding port pin and an interrupt can be generated.

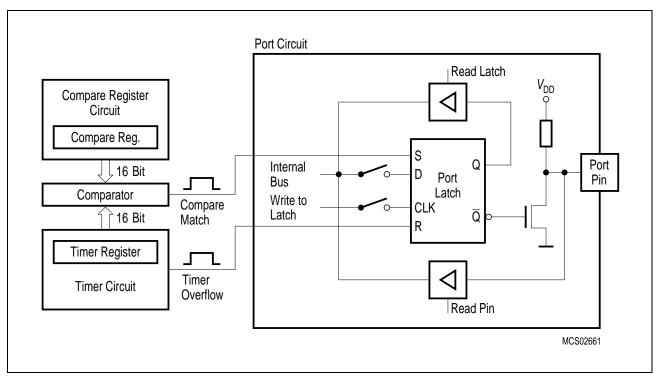

#### Compare Mode 0

In compare mode 0, upon matching the timer and compare register contents, the output signal changes from low to high. It goes back to a low level on timer overflow. As long as compare mode 0 is enabled, the appropriate output pin is controlled by the timer circuit only and writing to the port will have no effect. Figure 12 shows a functional diagram of a port circuit when used in compare mode 0. The port latch is directly controlled by the timer overflow and compare match signals. The input line from the internal bus and the write-to-latch line of the port latch are disconnected when compare mode 0 is enabled.

#### Figure 12 Port Latch in Compare Mode 0

### CAN Controller (C505C and C505CA only)

The on-chip CAN controller, compliant to version 2.0B, is the functional heart which provides all resources that are required to run the standard CAN protocol (11-bit identifiers) as well as the extended CAN protocol (29-bit identifiers). It provides a sophisticated object layer to relieve the CPU of as much overhead as possible when controlling many different message objects (up to 15). This includes bus arbitration, resending of garbled messages, error handling, interrupt generation, etc. In order to implement the physical layer, external components have to be connected to the C505C/C505CA.

The internal bus interface connects the on-chip CAN controller to the internal bus of the microcontroller. The registers and data locations of the CAN interface are mapped to a specific 256 byte wide address range of the external data memory area ( $F700_H$  to  $F7FF_H$ ) and can be accessed using MOVX instructions. Figure 15 shows a block diagram of the on-chip CAN controller.

The **TX/RX Shift Register** holds the destuffed bit stream from the bus line to allow the parallel access to the whole data or remote frame for the acceptance match test and the parallel transfer of the frame to and from the Intelligent Memory.

The **Bit Stream Processor (BSP)** is a sequencer controlling the sequential data stream between the TX/RX Shift Register, the CRC Register, and the bus line. The BSP also controls the EML and the parallel data stream between the TX/RX Shift Register and the Intelligent Memory such that the processes of reception, arbitration, transmission, and error signalling are performed according to the CAN protocol. Note that the automatic retransmission of messages which have been corrupted by noise or other external error conditions on the bus line is handled by the BSP.

The **Cyclic Redundancy Check Register (CRC)** generates the Cyclic Redundancy Check code to be transmitted after the data bytes and checks the CRC code of incoming messages. This is done by dividing the data stream by the code generator polynomial.

The **Error Management Logic (EML)** is responsible for the fault confinement of the CAN device. Its counters, the Receive Error Counter and the Transmit Error Counter, are incremented and decremented by commands from the Bit Stream Processor. According to the values of the error counters, the CAN controller is set into the states error *active*, error *passive* and busoff.

The **Bit Timing Logic (BTL)** monitors the busline input RXDC and handles the busline related bit timing according to the CAN protocol. The BTL synchronizes on a *recessive* to *dominant* busline transition at *Start of Frame* (hard synchronization) and on any further *recessive* to *dominant* busline transition, if the CAN controller itself does not transmit a *dominant* bit (resynchronization). The BTL also provides programmable time segments to compensate for the propagation delay time and for phase shifts and to define the position of the Sample Point in the bit time. The programming of the BTL depends on the baudrate and on external physical delay times.

The **Intelligent Memory** (CAM/RAM array) provides storage for up to 15 message objects of maximum 8 data bytes length. Each of these objects has a unique identifier and its own set of control and status bits. After the initial configuration, the Intelligent Memory can handle the reception and transmission of data without further microcontroller actions.

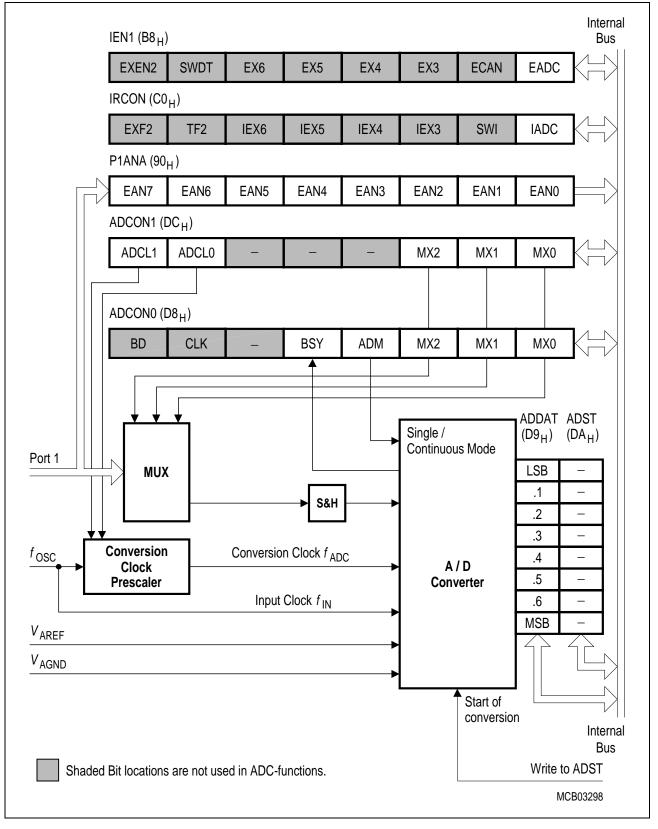

### Figure 18 Block Diagram of the 8-Bit A/D Converter

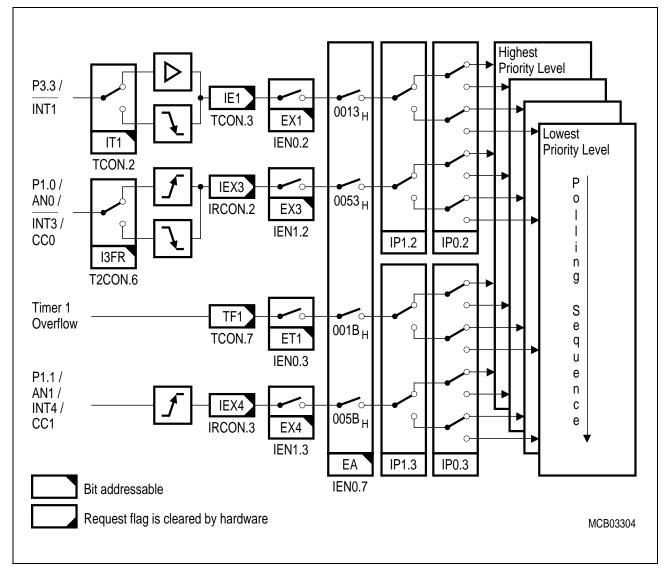

#### Figure 22 Interrupt Structure, Overview Part 2

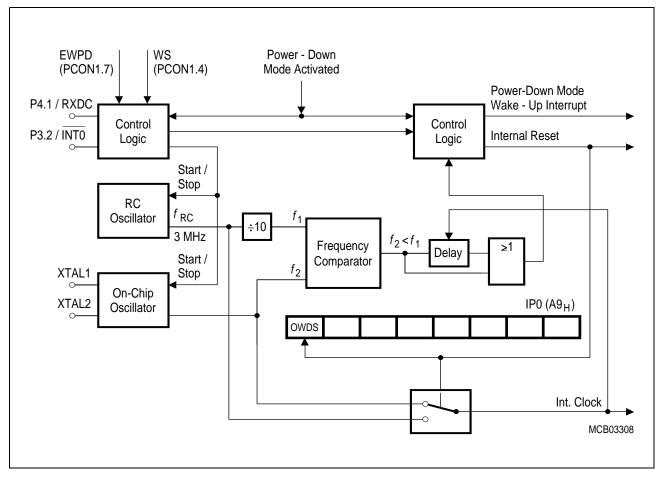

### Figure 25 Functional Block Diagram of the Oscillator Watchdog

#### Power Saving Modes

The C505 provides two basic power saving modes, the idle mode and the power down mode. Additionally, a slow down mode is available. This power saving mode reduces the internal clock rate in normal operating mode and it can be also used for further power reduction in idle mode.

#### - Idle mode

In the idle mode the main oscillator of the C505 continues to run, but the CPU is gated off from the clock signal. All peripheral units are further provided with the clock. The CPU status is preserved in its entirety. The idle mode can be terminated by any enabled interrupt of a peripheral unit or by a hardware reset.

#### - Power down mode

The operation of the C505 is completely stopped and the oscillator is turned off. This mode is used to save the contents of the internal RAM with a very low standby current. Power down mode is entered by software and can be left by reset or by a short low pulse at pin P3.2/ INT0.or P4.1/RXDC.

#### - Slow down mode

The controller keeps up the full operating functionality, but its normal clock frequency is internally divided by 32. This slows down all parts of the controller, the CPU and all peripherals, to 1/32-th of their normal operating frequency. Slowing down the frequency significantly reduces power consumption.

In the power down mode of operation,  $V_{\text{DD}}$  can be reduced to minimize power consumption. It must be ensured, however, that  $V_{\text{DD}}$  is not reduced before the power down mode is invoked, and that  $V_{\text{DD}}$ is restored to its normal operating level, before the power down mode is terminated. Table 10 gives a general overview of the entry and exit procedures of the power saving modes.

| Mode            | Entering<br>(Instruction<br>Example) | Leaving by                                             | Remarks                                                                               |

|-----------------|--------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------|

| Idle Mode       | ORL PCON, #01H<br>ORL PCON, #20H     | Ocurrence of an<br>interrupt from a<br>peripheral unit | CPU clock is stopped;<br>CPU maintains their data;<br>peripheral units are active (if |

|                 |                                      | Hardware Reset                                         | enabled) and provided with clock                                                      |

| Power Down Mode | ORL PCON, #02H                       | Hardware Reset                                         | Oscillator is stopped;                                                                |

|                 | ORL PCON, #40H                       | Short low pulse at<br>pin P3.2/INT0 or<br>P4.1/RXDC    | contents of on-chip RAM and SFR's are maintained;                                     |

| Slow Down Mode  | ORL PCON,#10H                        | ANL PCON,#0EFH<br>or<br>Hardware Reset                 | Oscillator frequency is<br>reduced to 1/32 of its nominal<br>frequency                |

### Table 10 Power Saving Modes Overview

# Table 11Pin Definitions and Functions in Programming Mode (cont'd)

| Symbol             | Pin Number                  | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|-----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2.0-7             | 18-25                       | I         | Address lines<br>P2.0-7 are used as multiplexed address input lines A0-A7 and<br>A8-A14. A8-A14 must be latched with PALE.                                                                                                                                                                                                                                                                           |

| PSEN               | 26                          | 1         | <b>Program store enable</b><br>This input must be at static "0" level during the whole<br>programming mode.                                                                                                                                                                                                                                                                                          |

| PROG               | 27                          | I         | <b>Programming mode write strobe</b><br>This input is used in programming mode as a write strobe for<br>OTP memory program, and lock bit write operations During<br>basic programming mode selection a low level must be applied<br>to PROG.                                                                                                                                                         |

| EA/V <sub>PP</sub> | 29                          | _         | <b>External Access / Programming voltage</b><br>This pin must be at 11.5V ( $V_{PP}$ ) voltage level during<br>programming of an OTP memory byte or lock bit. During an<br>OTP memory read operation this pin must be at $V_{IH}$ high level.<br>This pin is also used for basic programming mode selection. At<br>basic programming mode selection a low level must be applied<br>to EA/ $V_{PP}$ . |

| D7-0               | 30-37                       | I/O       | Data lines 0-7<br>During programming mode, data bytes are transferred via the<br>bidirectional port 0 data lines.                                                                                                                                                                                                                                                                                    |

| N.C.               | 1-3, 6, 11-13,<br>28, 38-44 | -         | Not Connected<br>These pins should not be connected in programming mode.                                                                                                                                                                                                                                                                                                                             |

\*) I = Input

## Table 12Access Modes Selection

| A access Made           | EA/             | <b>BBBBBBBBBBBBBB</b> |     | PMSEL |   | Address                     | Data      |  |

|-------------------------|-----------------|-----------------------|-----|-------|---|-----------------------------|-----------|--|

| Access Mode             | V <sub>PP</sub> | PROG                  | PRD | 1     | 0 | (Port 2)                    | (Port 0)  |  |

| Program OTP memory byte | V <sub>PP</sub> |                       | Н   | Н     | Н | A0-7                        | D0-7      |  |

| Read OTP memory byte    | V <sub>IH</sub> | Н                     |     |       |   | A8-14                       |           |  |

| Program OTP lock bits   | V <sub>PP</sub> |                       | Н   | Н     | L | _                           | D1,D0 see |  |

| Read OTP lock bits      | V <sub>IH</sub> | Н                     |     |       |   |                             | Table 13  |  |

| Read OTP version byte   | V <sub>IH</sub> | Н                     | Ţ   | L     | Н | Byte addr.<br>of sign. byte | D0-7      |  |

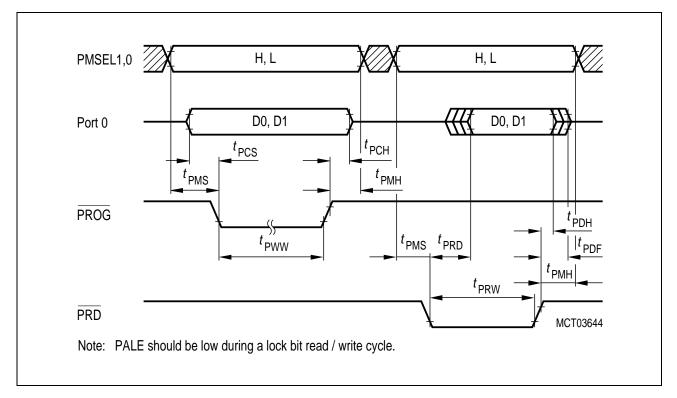

### Lock Bits Programming / Read

The C505A-4E/C505CA-4E has two programmable lock bits which, when programmed according to **Table 13**, provide four levels of protection for the on-chip OTP code memory. The state of the lock bits can also be read.

### Table 13Lock Bit Protection Types

| Lock Bi | ts at D1,D0 | Protection | Protection Type                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|---------|-------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D1      | D0          | Level      |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 1       | 1           | Level 0    | The OTP lock feature is disabled. During normal operation of<br>the C505A-4E/C505CA-4E, the state of the EA pin is no<br>latched on reset.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 1       | 0           | Level 1    | During normal operation of the C505A-4E/C505CA-4E, MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory. EA is sampled and latched on reset. An OTP memory read operation is only possible using the ROM/OTP verification mode 2 for protection level 1. Further programming of the OTP memory is disabled (reprogramming security). |  |  |  |  |  |

| 0       | 1           | Level 2    | Same as level 1, but also OTP memory read operation using OTP verification mode is disabled.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 0       | 0           | Level 3    | Same as level 2; but additionally external code execution by<br>setting EA=low during normal operation of the C505A-4E/<br>C505CA-4E is no more possible.<br>External code execution, which is initiated by an internal<br>program (e.g. by an internal jump instruction above the ROM<br>boundary), is still possible.                                                                            |  |  |  |  |  |

#### Note:

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 2) During the sample time the input capacitance C<sub>AIN</sub> must be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach their final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

- 3) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time for the calibration. Values for the conversion clock t<sub>ADC</sub> depend on programming and can be taken from the table on the previous page.

- 4) T<sub>UE</sub> is tested at V<sub>AREF</sub> = 5.0 V, V<sub>AGND</sub> = 0 V, V<sub>DD</sub> = 4.9 V. It is guaranteed by design characterization for all other voltages within the defined voltage range.

If an overload condition occurs on maximum 2 unused analog input pins and the absolute sum of input overload currents on all analog input pins does not exceed 10 mA, an additional conversion error of 1/2 LSB is permissible.

- 5) During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference source must allow the capacitance to reach their final voltage level within the indicated time. The maximum internal resistance results from the programmed conversion timing.

- 6) Not 100% tested, but guaranteed by design characterization.

### AC Characteristics (16 MHz, 0.4 to 0.6 Duty Cycle, cont'd)

#### **External Data Memory Characteristics**

| Parameter                                                         | Symbol                   |                                          |      | Limit Values                             |                                    | Unit |

|-------------------------------------------------------------------|--------------------------|------------------------------------------|------|------------------------------------------|------------------------------------|------|

|                                                                   |                          | 16-MHz clock<br>Duty Cycle<br>0.4 to 0.6 |      | Variable Clock<br>1/CLP= 2 MHz to 16 MHz |                                    |      |

|                                                                   |                          | min.                                     | max. | min.                                     | max.                               |      |

| RD pulse width                                                    | t <sub>RLRH</sub>        | 158                                      | -    | 3 CLP - 30                               | -                                  | ns   |

| WR pulse width                                                    | t <sub>wLwH</sub>        | 158                                      | -    | 3 CLP - 30                               | -                                  | ns   |

| Address hold after ALE                                            | t <sub>LLAX2</sub>       | 48                                       | -    | CLP - 15                                 | -                                  | ns   |

| RD to valid data in                                               | t <sub>RLDV</sub>        | -                                        | 100  | -                                        | 2 CLP+<br>TCL <sub>Hmin</sub> - 50 | ns   |

| Data hold after RD                                                | t <sub>RHDX</sub>        | 0                                        | -    | 0                                        | -                                  | ns   |

| Data float after RD                                               | t <sub>RHDZ</sub>        | _                                        | 51   | -                                        | CLP - 12                           | ns   |

| ALE to valid data in                                              | t <sub>LLDV</sub>        | _                                        | 200  | -                                        | 4 CLP - 50                         | ns   |

| Address to valid data in                                          | t <sub>AVDV</sub>        | -                                        | 200  | _                                        | 4 CLP +<br>TCL <sub>Hmin</sub> -75 | ns   |

| ALE to WR or RD                                                   | t <sub>LLWL</sub>        | 73                                       | 103  | CLP +<br>TCL <sub>Lmin</sub> - 15        | CLP+<br>TCL <sub>Lmin</sub> + 15   | ns   |

| Address valid to WR                                               | <i>t</i> <sub>AVWL</sub> | 95                                       | -    | 2 CLP - 30                               | -                                  | ns   |

| $\overline{\text{WR}}$ or $\overline{\text{RD}}$ high to ALE high | t <sub>WHLH</sub>        | 10                                       | 40   | TCL <sub>Hmin</sub> - 15                 | TCL <sub>Hmin</sub> + 15           | ns   |

| Data valid to WR transition                                       | <i>t</i> <sub>QVWX</sub> | 5                                        | -    | TCL <sub>Lmin</sub> - 20                 | -                                  | ns   |

| Data setup before $\overline{WR}$                                 | t <sub>QVWH</sub>        | 163                                      | -    | 3 CLP +<br>TCL <sub>Lmin</sub> - 50      | -                                  | ns   |

| Data hold after WR                                                | t <sub>WHQX</sub>        | 5                                        | -    | TCL <sub>Hmin</sub> - 20                 | -                                  | ns   |

| Address float after RD                                            | t <sub>RLAZ</sub>        | _                                        | 0    | _                                        | 0                                  | ns   |

### Figure 38 Lock Bit Access Timing

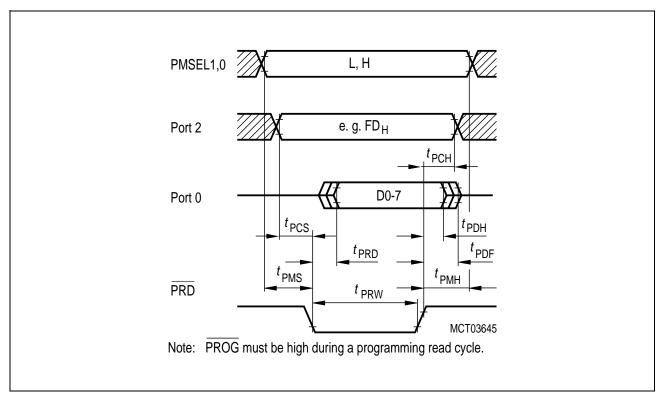

### Figure 39 Version Byte Read Timing