Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| 2 0 0 0 0 0                |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | C500                                                                         |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 1.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.25V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-QFP                                                                       |

| Supplier Device Package    | PG-MQFP-44-2                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c505ca4emcakxqma1 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| C505/C5050<br>Revision Hi       |                                 | 5CA Data Sheet<br>Current Version : 2000-12                     |

|---------------------------------|---------------------------------|-----------------------------------------------------------------|

| Previous Re                     | leases :                        | 08.00, 06.00, 07.99, 12.97                                      |

| Page<br>(in previous<br>version | Page<br>(in current<br>version) | Subjects (major changes since last revision)                    |

| 24                              | 24                              | Version register VR2 for C505A-4R/C505CA-4R BB step is updated. |

|                                 |                                 |                                                                 |

Controller Area Network (CAN): License of Robert Bosch GmbH

# We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

# 8-Bit Single-Chip Microcontroller C500 Family

C505/C505C/C505A/ C505CA

#### **Advance Information**

- Fully compatible to standard 8051 microcontroller

- Superset of the 8051 architecture with 8 datapointers

- Up to 20 MHz operating frequency

- 375 ns instruction cycle time @16 MHz

- 300 ns instruction cycle time @20 MHz (50 % duty cycle)

- On-chip program memory (with optional memory protection)

- C505(C)(A)-2R : 16K byte on-chip ROM

- C505A-4R/C505CA-4R: 32K byte on-chip ROM

- C505A-4E/C505CA-4E: 32K byte on-chip OTP

- alternatively up to 64k byte external program memory

- 256 byte on-chip RAM

- On-chip XRAM

- C505/C505C : 256 byte

- C505A/C505CA : 1K byte

(more features on next page)

| Module    | Oscillator<br>Watchdog                                       | XRAM<br>C505/C505C: 256 byte<br>C505A/C505CA: 1K byte |                                  | RAM<br>256 byte | Port 0 |

|-----------|--------------------------------------------------------------|-------------------------------------------------------|----------------------------------|-----------------|--------|

| Support I | A/D Converter<br>C505/C505C : 8-bit<br>C505A/C505CA : 10-bit | Timer<br>0                                            | C500<br>Core                     | 8-bit<br>USART  | Port 1 |

| Emulation | Timer 2                                                      | Timer<br>1                                            | 8 Datapointers                   | USAN            | Port 2 |

|           | Full-CAN Controller<br>C505C/C505CA only                     | F                                                     | Program Memoi<br>C505(C)(A)-2R : | -               | Port 3 |

| On-Chip   | Watchdog Timer                                               |                                                       | 4R/C505CÁ-4R :<br>-4E/C505CA-4E  | 32K ROM         |        |

#### Figure 1 C505 Functional Units

# Table 2Pin Definitions and Functions (cont'd)

| Symbol       | Pin Number | I/O<br>*)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4.0<br>P4.1 | 6<br>28    | I/O<br>I/O | Port 4is a 2-bit quasi-bidirectional port with internal pull-up<br>arrangement. Port 4 pins that have 1's written to them are<br>pulled high by the internal pull-up transistors and in that<br>state can be used as inputs. As inputs, port 4 pins being<br>externally pulled low will source current ( $I_{IL}$ , in the DC<br>characteristics) because of the internal pullup transistors.<br>The output latch corresponding to the secondary function<br>RXDC must be programmed to a one (1) for that function to<br>operate. The secondary functions are assigned to the two<br>pins of port 4 as follows (C505C and C505CA only) :<br>P4.0 / TXDC<br>P4.1 / RXDC |

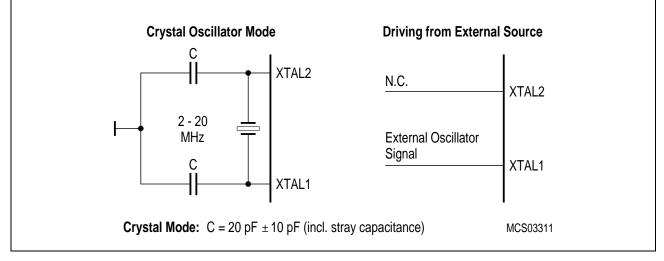

| XTAL2        | 14         | 0          | <b>XTAL2</b><br>Output of the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XTAL1        | 15         | I          | XTAL1<br>Input to the inverting oscillator amplifier and input to the<br>internal clock generator circuits.<br>To drive the device from an external clock source, XTAL1<br>should be driven, while XTAL2 is left unconnected. To<br>operate above a frequency of 16 MHz, a duty cycle of the<br>etxernal clock signal of 50 % should be maintained.<br>Minimum and maximum high and low times as well as rise/<br>fall times specified in the AC characteristics must be<br>observed.                                                                                                                                                                                   |

\*) I = Input

O= Output

#### **Multiple Datapointers**

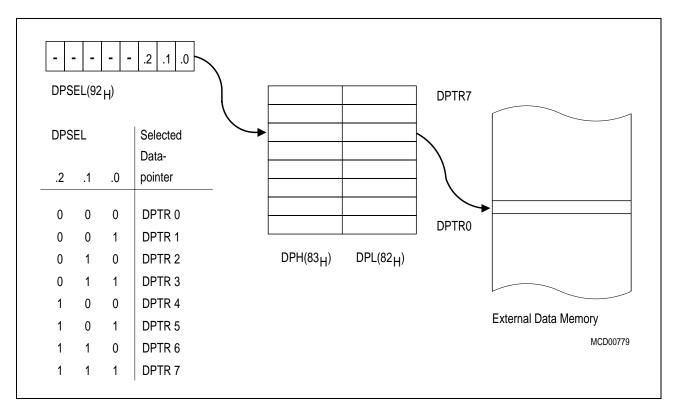

As a functional enhancement to the standard 8051 architecture, the C505 contains eight 16-bit datapointers instead of only one datapointer. The instruction set uses just one of these datapointers at a time. The selection of the actual datapointer is done in the special function regsiter DPSEL. **Figure 8** illustrates the datapointer addressing mechanism.

Figure 8 External Data Memory Addressing using Multiple Datapointers

# Table 4 Contents of the SFRs, SFRs in numeric order of their addresses (cont'd)

| Addr                          | Register     | Content<br>after<br>Reset <sup>1)</sup> | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2       | Bit 1      | Bit 0      |

|-------------------------------|--------------|-----------------------------------------|------------|------------|------------|------------|------------|-------------|------------|------------|

| В0 <sub>Н</sub> ²)            | P3           | FF <sub>H</sub>                         | RD         | WR         | T1         | то         | INT1       | <b>INTO</b> | TxD        | RxD        |

| B1 <sub>H</sub>               | SYSCON<br>3) | XX10-<br>0X01 <sub>B</sub>              | _          | _          | EALE       | RMAP       | CMOD       | _           | XMAP1      | XMAP0      |

| B1 <sub>H</sub>               | SYSCON<br>4) | XX10-<br>0001 <sub>B</sub>              | -          | _          | EALE       | RMAP       | CMOD       | CSWO        | XMAP1      | XMAP0      |

| B8 <sub>H</sub> 2)            | IEN1         | 00 <sub>H</sub>                         | EXEN2      | SWDT       | EX6        | EX5        | EX4        | EX3         | ECAN       | EADC       |

| B9 <sub>H</sub>               | IP1          | XX00-<br>0000 <sub>B</sub>              | _          | _          | .5         | .4         | .3         | .2          | .1         | .0         |

| BA <sub>H</sub>               | SRELH        | xxxx-<br>XX11 <sub>B</sub>              | _          | _          | _          | _          | _          | _           | .1         | .0         |

| C0 <sub>H</sub> <sup>2)</sup> | IRCON        | 00 <sub>H</sub>                         | EXF2       | TF2        | IEX6       | IEX5       | IEX4       | IEX3        | SWI        | IADC       |

| C1 <sub>H</sub>               | CCEN         | 00 <sub>H</sub>                         | COCA<br>H3 | COCAL<br>3 | COCA<br>H2 | COCAL<br>2 | COCA<br>H1 | COCAL<br>1  | COCA<br>H0 | COCAL<br>0 |

| C2 <sub>H</sub>               | CCL1         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| C3 <sub>H</sub>               | CCH1         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| C4 <sub>H</sub>               | CCL2         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| C5 <sub>H</sub>               | CCH2         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| C6 <sub>H</sub>               | CCL3         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| C7 <sub>H</sub>               | ССНЗ         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| C8 <sub>H</sub> ²)            | T2CON        | 00X0-<br>0000 <sub>B</sub>              | T2PS       | I3FR       | -          | T2R1       | T2R0       | T2CM        | T2I1       | T2I0       |

| CAH                           | CRCL         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| Св <sub>Н</sub>               | CRCH         | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| сс <sup>н</sup>               | TL2          | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| CDH                           | TH2          | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2          | .1         | .0         |

| D0H <sup>2)</sup>             | PSW          | 00 <sub>H</sub>                         | CY         | AC         | F0         | RS1        | RS0        | OV          | F1         | Р          |

| D8 <sub>H</sub> ²)            | ADCON0       | 00X0-<br>0000 <sub>B</sub>              | BD         | CLK        | _          | BSY        | ADM        | MX2         | MX1        | MX0        |

1) X means that the value is undefined and the location is reserved

2) Bit-addressable special function registers

3) C505 /C505C/C505A only

4) C505CA only

#### **Timer 2 Operating Modes**

The timer 2, which is a 16-bit-wide register, can operate as timer, event counter, or gated timer. A roll-over of the count value in TL2/TH2 from all 1's to all 0's sets the timer overflow flag TF2 in SFR IRCON, which can generate an interrupt. The bits in register T2CON are used to control the timer 2 operation.

<u>Timer Mode</u> : In timer function, the count rate is derived from the oscillator frequency. A prescaler offers the possibility of selecting a count rate of 1/6 or 1/12 of the oscillator frequency.

<u>Gated Timer Mode</u>: In gated timer function, the external input pin T2 (P1.7) functions as a gate to the input of timer 2. If T2 is high, the internal clock input is gated to the timer. T2 = 0 stops the counting procedure. This facilitates pulse width measurements. The external gate signal is sampled once every machine cycle.

<u>Event Counter Mode</u>: In the event counter function. the timer 2 is incremented in response to a 1to-0 transition at its corresponding external input pin T2 (P1.7). In this function, the external input is sampled every machine cycle. Since it takes two machine cycles (12 oscillator periods) to recognize a 1-to-0 transition, the maximum count rate is 1/6 of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it must be held for at least one full machine cycle.

Reload of Timer 2 : Two reload modes are selectable:

In mode 0, when timer 2 rolls over from all 1's to all 0's, it not only sets TF2 but also causes the timer 2 registers to be loaded with the 16-bit value in the CRC register, which is preset by software. In mode 1, a 16-bit reload from the CRC register is caused by a negative transition at the corresponding input pin P1.5/T2EX. This transition will also set flag EXF2 if bit EXEN2 in SFR IEN1 has been set.

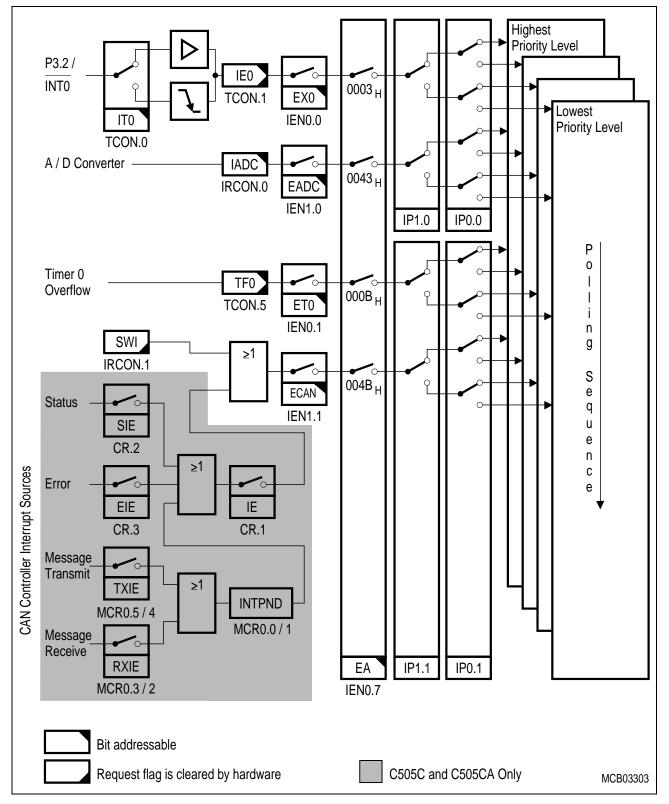

# Figure 21

# Interrupt Structure, Overview Part 1

Note: Each of the 15 CAN controller message objects (C505C and C505CA only), shown in the shaded area of **Figure 21** provides the bits/flags.

## Fail Save Mechanisms

The C505 offers enhanced fail safe mechanisms, which allow an automatic recovery from software upset or hardware failure :

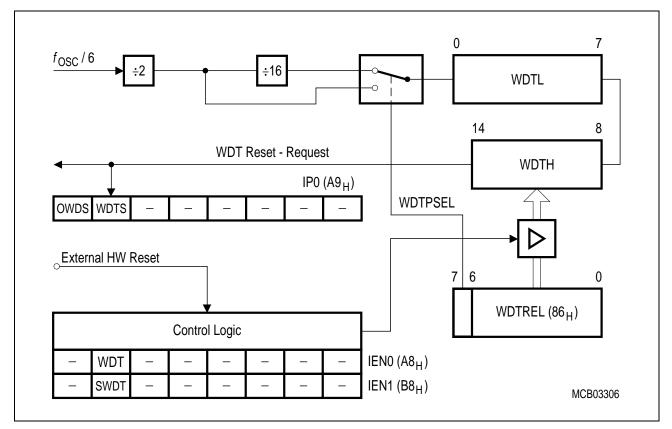

- a programmable watchdog timer (WDT), with variable time-out period from 192  $\mu$ s up to approx. 393.2 ms at 16 MHz (314.5 ms at 20 MHz).

- an oscillator watchdog (OWD) which monitors the on-chip oscillator and forces the microcontroller into reset state in case the on-chip oscillator fails; it also provides the clock for a fast internal reset after power-on.

The watchdog timer in the C505 is a 15-bit timer, which is incremented by a count rate of  $f_{OSC}/12$  upto  $f_{OSC}/192$ . The system clock of the C505 is divided by two prescalers, a divide-by-two and a divide-by-16 prescaler. For programming of the watchdog timer overflow rate, the upper 7 bits of the watchdog timer can be written. Figure 24 shows the block diagram of the watchdog timer unit.

# Figure 24

### Block Diagram of the Programmable Watchdog Timer

The watchdog timer can be started by software (bit SWDT in SFR IEN1) but it cannot be stopped during active mode of the device. If the software fails to refresh the running watchdog timer an internal reset will be initiated on watchdog timer overflow. For refreshing of the watchdog timer the content of the SFR WDTREL is transfered to the upper 7-bit of the watchdog timer. The refresh sequence consists of two consequtive instructions which set the bits WDT and SWDT each. The reset cause (external reset or reset caused by the watchdog) can be examined by software (flag WDTS). It must be noted, however, that the watchdog timer is halted during the idle mode and power down mode of the processor.

# Table 12Access Modes Selection

| A access Made           | EA/             | <b>DDOO</b> | 000 | PN | ISEL | Address                     | Data      |

|-------------------------|-----------------|-------------|-----|----|------|-----------------------------|-----------|

| Access Mode             | V <sub>PP</sub> | PROG        | PRD | 1  | 0    | (Port 2)                    | (Port 0)  |

| Program OTP memory byte | V <sub>PP</sub> |             | Н   | Н  | Н    | A0-7                        | D0-7      |

| Read OTP memory byte    | V <sub>IH</sub> | Н           |     |    |      | A8-14                       |           |

| Program OTP lock bits   | V <sub>PP</sub> |             | Н   | Н  | L    | _                           | D1,D0 see |

| Read OTP lock bits      | V <sub>IH</sub> | Н           |     |    |      |                             | Table 13  |

| Read OTP version byte   | V <sub>IH</sub> | Н           | Ţ   | L  | Н    | Byte addr.<br>of sign. byte | D0-7      |

### Lock Bits Programming / Read

The C505A-4E/C505CA-4E has two programmable lock bits which, when programmed according to **Table 13**, provide four levels of protection for the on-chip OTP code memory. The state of the lock bits can also be read.

# Table 13Lock Bit Protection Types

| Lock Bi | Bits at D1,D0 Protection |         | Protection Type                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|--------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1      | D0                       | Level   |                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1       | 1                        | Level 0 | The OTP lock feature is disabled. During normal operation of the C505A-4E/C505CA-4E, the state of the $\overline{EA}$ pin is not latched on reset.                                                                                                                                                                                                                                                 |

| 1       | 0                        | Level 1 | During normal operation of the C505A-4E/C505CA-4E, MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory. EA is sampled and latched on reset. An OTP memory read operation is only possible using the ROM/OTP verification mode 2 for protection level 1. Further programming of the OTP memory is disabled (reprogramming security). |

| 0       | 1                        | Level 2 | Same as level 1, but also OTP memory read operation using OTP verification mode is disabled.                                                                                                                                                                                                                                                                                                       |

| 0       | 0                        | Level 3 | Same as level 2; but additionally external code execution by<br>setting EA=low during normal operation of the C505A-4E/<br>C505CA-4E is no more possible.<br>External code execution, which is initiated by an internal<br>program (e.g. by an internal jump instruction above the ROM<br>boundary), is still possible.                                                                            |

## **Operating Conditions**

| Parameter                | Symbol           | Limit              | Values                         | Unit | Notes                         |

|--------------------------|------------------|--------------------|--------------------------------|------|-------------------------------|

|                          |                  | min.               | max.                           |      |                               |

| Supply voltage           | V <sub>DD</sub>  | 4.25               | 5.5                            | V    | Active mode,                  |

|                          |                  |                    |                                |      | f <sub>osc max</sub> = 20 MHz |

|                          |                  | 2                  | 5.5                            | V    | PowerDown mode                |

| Ground voltage           | V <sub>SS</sub>  | 0                  |                                | V    | Reference voltage             |

| Ambient temperature      |                  |                    |                                | °C   | -                             |

| SAB-C505                 | T <sub>A</sub>   | 0                  | 70                             |      |                               |

| SAF-C505                 | T <sub>A</sub>   | -40                | 85                             |      |                               |

| SAH-C505                 | T <sub>A</sub>   | -40                | 110                            |      |                               |

| SAK-C505                 | T <sub>A</sub>   | -40                | 125                            |      |                               |

| Analog reference voltage | $V_{AREF}$       | 4                  | V <sub>DD</sub> + 0.1          | V    | -                             |

| Analog ground voltage    | $V_{\rm AGND}$   | $V_{\rm SS} - 0.1$ | V <sub>SS</sub> + 0.2          | V    | -                             |

| Analog input voltage     | $V_{AIN}$        | $V_{AGND}$ -0.2    | V <sub>AREF</sub> +0.2         | V    | -                             |

| XTAL clock               | f <sub>osc</sub> | 2                  | 20<br>(with 50% duty<br>cycle) | MHz  | 1)                            |

1) For the extended temperature range -40 °C to 110 °C (SAH) and -40 °C to 125 °C (SAK), the devices C505-2R, C505-L, C505C-2R and C505C-L have the max. operating frequency of 16MHz with 50% clock duty cycle.

### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C505 and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C505 will provide signals with the respective characteristics.

SR (System Requirement):

The external system must provide signals with the respective characteristics to the C505.

# **Power Supply Currents**

| Parameter                              |                                    | Symbol           | Limit                              | Values       | Unit                | <b>Test Condition</b> |                                      |

|----------------------------------------|------------------------------------|------------------|------------------------------------|--------------|---------------------|-----------------------|--------------------------------------|

|                                        |                                    |                  |                                    | typ.12)      | max. <sup>13)</sup> |                       |                                      |

| C505 /<br>C505C                        | Active Mode                        | 12 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 19.3<br>31.3 | 27.0<br>39          | mA                    | 7)                                   |

|                                        | Idle Mode                          | 12 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 10.3<br>16.2 | 13.0<br>21.0        | mA                    | 8)                                   |

|                                        | Active Mode with slow-down enabled | 12 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 3.9<br>4.8   | 5.5<br>7.5          | mA                    | 9)                                   |

|                                        | Idle Mode with slow-down enabled   | 12 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 3.2<br>4.0   | 5.0<br>7.0          | mA                    | 10)                                  |

|                                        | Power down mode                    |                  | I <sub>PD</sub>                    | 10           | 50                  | μA                    | $V_{\rm DD}$ = 25.5 V <sup>11)</sup> |

| C505A-4E<br>/C505CA-4E                 | Active Mode                        | 16 MHz<br>20 MHz | $I_{\rm DD}$<br>$I_{\rm DD}$       | 28.7<br>35.2 | 30.7<br>37.6        | mA                    | 7)                                   |

|                                        | Idle Mode                          | 16 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 14.9<br>17.7 | 15.9<br>18.9        | mA                    | 8)                                   |

|                                        | Active Mode with slow-down enabled | 16 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 9.9<br>12.3  | 12.8<br>15.6        | mA                    | 9)                                   |

|                                        | Idle Mode with slow-down enabled   | 16 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 5.1<br>6.3   | 5.6<br>6.8          | mA                    | 10)                                  |

|                                        | Power down mode                    |                  | I <sub>PD</sub>                    | 5.6          | 20                  | μA                    | $V_{\rm DD}$ = 25.5 V <sup>11)</sup> |

| C505A-4R /<br>C505CA-4R                | Active Mode                        | 16 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 22.8<br>27.6 | 29.2<br>35.3        | mA                    | 7)                                   |

| /C505A-2R /<br>C505CA-2R<br>/C505A-L / | Idle Mode                          | 16 MHz<br>20 MHz | $I_{\rm DD}$<br>$I_{\rm DD}$       | 12.7<br>15.0 | 16.3<br>19.3        | mA                    | 8)                                   |

| C505CA-L                               | Active Mode with slow-down enabled | 16 MHz<br>20 MHz | $I_{\rm DD}$<br>$I_{\rm DD}$       | 6.6<br>7.3   | 8.2<br>9.3          | mA                    | 9)                                   |

|                                        | Idle Mode with slow-down enabled   | 16 MHz<br>20 MHz | I <sub>DD</sub><br>I <sub>DD</sub> | 5.0<br>5.3   | 5.9<br>6.5          | mA                    | 10)                                  |

|                                        | Power down mode                    |                  | I <sub>PD</sub>                    | 5.3          | 30                  | μA                    | $V_{\rm DD}$ = 25.5 V <sup>11)</sup> |

Notes see Page 60

#### Note:

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be 00<sub>H</sub> or FF<sub>H</sub>, respectively.

- 2) During the sample time the input capacitance C<sub>AIN</sub> must be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach their final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

- 3) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result. Values for the conversion clock t<sub>ADC</sub> depend on programming and can be taken from the table on the previous page.

- 4)  $T_{UE}$  (max.) is tested at  $-40 \le T_A \le 125 \text{ °C}$ ;  $V_{DD} \le 5.5 \text{ V}$ ;  $V_{AREF} \le V_{DD} + 0.1 \text{ V}$  and  $V_{SS} \le V_{AGND}$ . It is guaranteed by design characterization for all other voltages within the defined voltage range. If an overload condition occurs on maximum 2 unused analog input pins and the absolute sum of input overload currents on all analog input pins does not exceed 10 mA, an additional conversion error of 1/2 LSB is permissible.

- 5) During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference source must allow the capacitance to reach their final voltage level within the indicated time. The maximum internal resistance results from the programmed conversion timing.

- 6) Not 100% tested, but guaranteed by design characterization.

#### Note:

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 2) During the sample time the input capacitance C<sub>AIN</sub> must be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach their final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

- 3) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time for the calibration. Values for the conversion clock t<sub>ADC</sub> depend on programming and can be taken from the table on the previous page.

- 4) T<sub>UE</sub> is tested at V<sub>AREF</sub> = 5.0 V, V<sub>AGND</sub> = 0 V, V<sub>DD</sub> = 4.9 V. It is guaranteed by design characterization for all other voltages within the defined voltage range.

If an overload condition occurs on maximum 2 unused analog input pins and the absolute sum of input overload currents on all analog input pins does not exceed 10 mA, an additional conversion error of 1/2 LSB is permissible.

- 5) During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference source must allow the capacitance to reach their final voltage level within the indicated time. The maximum internal resistance results from the programmed conversion timing.

- 6) Not 100% tested, but guaranteed by design characterization.

# AC Characteristics (16 MHz, 0.4 to 0.6 Duty Cycle)

(Operating Conditions apply)

( $C_{L}$  for port 0, ALE and  $\overline{PSEN}$  outputs = 100 pF;  $C_{L}$  for all other outputs = 80 pF)

## **Program Memory Characteristics**

| Parameter                          | Symbol                                   | Limit Values |                        |                                 |                                    |    |

|------------------------------------|------------------------------------------|--------------|------------------------|---------------------------------|------------------------------------|----|

|                                    | 16-MHz clock<br>Duty Cycle<br>0.4 to 0.6 |              | Variabl<br>1/CLP= 2 Mł | -                               |                                    |    |

|                                    |                                          | min.         | max.                   | min.                            | max.                               |    |

| ALE pulse width                    | t <sub>LHLL</sub>                        | 48           | _                      | CLP - 15                        | -                                  | ns |

| Address setup to ALE               | <i>t</i> <sub>AVLL</sub>                 | 10           | _                      | TCL <sub>Hmin</sub> -15         | -                                  | ns |

| Address hold after ALE             | t <sub>LLAX</sub>                        | 10           | _                      | TCL <sub>Hmin</sub> -15         | -                                  | ns |

| ALE to valid instruction in        | t <sub>LLIV</sub>                        | _            | 75                     | _                               | 2 CLP - 50                         | ns |

| ALE to PSEN                        | t <sub>LLPL</sub>                        | 10           | -                      | TCL <sub>Lmin</sub> -15         | -                                  | ns |

| PSEN pulse width                   | t <sub>PLPH</sub>                        | 73           | -                      | CLP+<br>TCL <sub>Hmin</sub> -15 | _                                  | ns |

| PSEN to valid instruction in       | t <sub>PLIV</sub>                        | _            | 38                     | -                               | CLP+<br>TCL <sub>Hmin</sub> - 50   | ns |

| Input instruction hold after PSEN  | t <sub>PXIX</sub>                        | 0            | -                      | 0                               | -                                  | ns |

| Input instruction float after PSEN | t <sub>PXIZ</sub> *)                     | _            | 15                     | _                               | TCL <sub>Lmin</sub> -10            | ns |

| Address valid after PSEN           | t <sub>PXAV</sub> *)                     | 20           | -                      | TCL <sub>Lmin</sub> - 5         | -                                  | ns |

| Address to valid instruction in    | t <sub>AVIV</sub>                        | _            | 95                     | -                               | 2 CLP +<br>TCL <sub>Hmin</sub> -55 | ns |

| Address float to PSEN              | t <sub>AZPL</sub>                        | -5           | -                      | -5                              | -                                  | ns |

\*) Interfacing the C505 to devices with float times up to 20 ns is permissible. This limited bus contention will not cause any damage to port 0 drivers.

# AC Characteristics (16 MHz, 0.4 to 0.6 Duty Cycle, cont'd)

#### **External Data Memory Characteristics**

| Parameter                                                         | Symbol                   | Limit Values |                             |                                     |                                    |    |

|-------------------------------------------------------------------|--------------------------|--------------|-----------------------------|-------------------------------------|------------------------------------|----|

|                                                                   |                          | Duty         | Iz clock<br>Cycle<br>to 0.6 | Variab<br>1/CLP= 2 M                |                                    |    |

|                                                                   |                          | min.         | max.                        | min.                                | max.                               |    |

| RD pulse width                                                    | t <sub>RLRH</sub>        | 158          | -                           | 3 CLP - 30                          | -                                  | ns |

| WR pulse width                                                    | t <sub>wLwH</sub>        | 158          | -                           | 3 CLP - 30                          | -                                  | ns |

| Address hold after ALE                                            | t <sub>LLAX2</sub>       | 48           | -                           | CLP - 15                            | -                                  | ns |

| RD to valid data in                                               | t <sub>RLDV</sub>        | -            | 100                         | -                                   | 2 CLP+<br>TCL <sub>Hmin</sub> - 50 | ns |

| Data hold after RD                                                | t <sub>RHDX</sub>        | 0            | -                           | 0                                   | -                                  | ns |

| Data float after RD                                               | t <sub>RHDZ</sub>        | _            | 51                          | _                                   | CLP - 12                           | ns |

| ALE to valid data in                                              | t <sub>LLDV</sub>        | _            | 200                         | -                                   | 4 CLP - 50                         | ns |

| Address to valid data in                                          | t <sub>AVDV</sub>        | -            | 200                         | _                                   | 4 CLP +<br>TCL <sub>Hmin</sub> -75 | ns |

| ALE to WR or RD                                                   | t <sub>LLWL</sub>        | 73           | 103                         | CLP +<br>TCL <sub>Lmin</sub> - 15   | CLP+<br>TCL <sub>Lmin</sub> + 15   | ns |

| Address valid to WR                                               | <i>t</i> <sub>AVWL</sub> | 95           | -                           | 2 CLP - 30                          | -                                  | ns |

| $\overline{\text{WR}}$ or $\overline{\text{RD}}$ high to ALE high | t <sub>WHLH</sub>        | 10           | 40                          | TCL <sub>Hmin</sub> - 15            | TCL <sub>Hmin</sub> + 15           | ns |

| Data valid to WR transition                                       | <i>t</i> <sub>QVWX</sub> | 5            | -                           | TCL <sub>Lmin</sub> - 20            | -                                  | ns |

| Data setup before $\overline{WR}$                                 | t <sub>QVWH</sub>        | 163          | -                           | 3 CLP +<br>TCL <sub>Lmin</sub> - 50 | -                                  | ns |

| Data hold after WR                                                | t <sub>WHQX</sub>        | 5            | -                           | TCL <sub>Hmin</sub> - 20            | -                                  | ns |

| Address float after RD                                            | t <sub>RLAZ</sub>        | _            | 0                           | _                                   | 0                                  | ns |

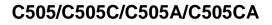

# AC Characteristics of Programming Mode (C505A-4E and C505CA-4E only)

$V_{\rm DD}$  = 5 V ± 10 %;  $V_{\rm PP}$  = 11.5 V ± 5 %;  $T_{\rm A}$  = 25 °C ± 10 °C

| Parameter                                          | Symbol            | L    | Limit Values |    |  |  |

|----------------------------------------------------|-------------------|------|--------------|----|--|--|

|                                                    |                   | min. | max.         |    |  |  |

| PALE pulse width                                   | t <sub>PAW</sub>  | 35   | _            | ns |  |  |

| PMSEL setup to PALE rising edge                    | t <sub>PMS</sub>  | 10   | _            |    |  |  |

| Address setup to PALE, PROG, or PRD falling edge   | t <sub>PAS</sub>  | 10   | -            | ns |  |  |

| Address hold after PALE, PROG, or PRD falling edge | t <sub>PAH</sub>  | 10   | -            | ns |  |  |

| Address, data setup to PROG or PRD                 | t <sub>PCS</sub>  | 100  | _            | ns |  |  |

| Address, data hold after PROG or PRD               | t <sub>PCH</sub>  | 0    | _            | ns |  |  |

| PMSEL setup to PROG or PRD                         | t <sub>PMS</sub>  | 10   | _            | ns |  |  |

| PMSEL hold after PROG or PRD                       | t <sub>PMH</sub>  | 10   | _            | ns |  |  |

| PROG pulse width                                   | t <sub>PWW</sub>  | 100  | _            | μs |  |  |

| PRD pulse width                                    | t <sub>PRW</sub>  | 100  | _            | ns |  |  |

| Address to valid data out                          | t <sub>PAD</sub>  | -    | 75           | ns |  |  |

| PRD to valid data out                              | t <sub>PRD</sub>  | _    | 20           | ns |  |  |

| Data hold after PRD                                | t <sub>PDH</sub>  | 0    | _            | ns |  |  |

| Data float after PRD                               | t <sub>PDF</sub>  | _    | 20           | ns |  |  |

| PROG high between two consecutive PROG low pulses  | t <sub>PWH1</sub> | 1    | -            | μs |  |  |

| PRD high between two consecutive PRD low pulses    | t <sub>PWH2</sub> | 100  |              | ns |  |  |

| XTAL clock period                                  | t <sub>CLKP</sub> | 83.3 | 500          | ns |  |  |

#### Figure 36 Programming Code Byte - Write Cycle Timing

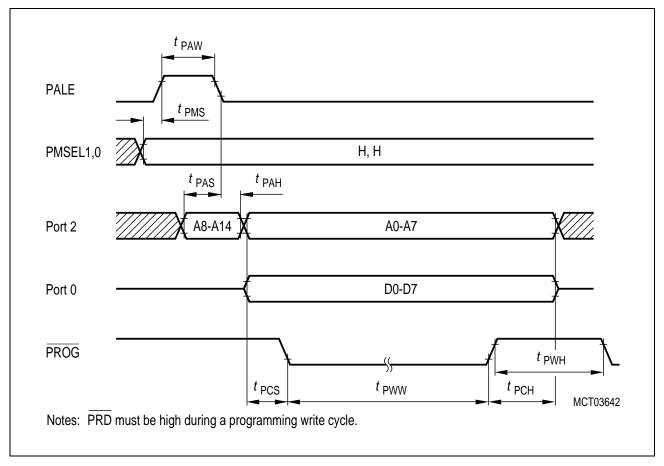

# **ROM/OTP** Verification Characteristics for C505 (cont'd)

# **ROM/OTP Verification Mode 2**

| Parameter             | Symbol           | Limit Values |                 |       | Unit |

|-----------------------|------------------|--------------|-----------------|-------|------|

|                       |                  | min.         | typ             | max.  |      |

| ALE pulse width       | t <sub>AWD</sub> | _            | CLP             | -     | ns   |

| ALE period            | t <sub>ACY</sub> | -            | 6 CLP           | -     | ns   |

| Data valid after ALE  | t <sub>DVA</sub> | _            | -               | 2 CLP | ns   |

| Data stable after ALE | t <sub>DSA</sub> | 4 CLP        | -               | -     | ns   |

| P3.5 setup to ALE low | t <sub>AS</sub>  | -            | t <sub>CL</sub> | -     | ns   |

| Oscillator frequency  | 1/ CLP           | 4            | -               | 6     | MHz  |

### Figure 41 ROM/OTP Verification Mode 2

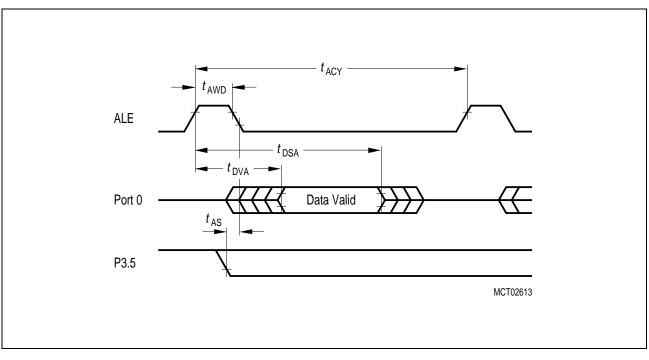

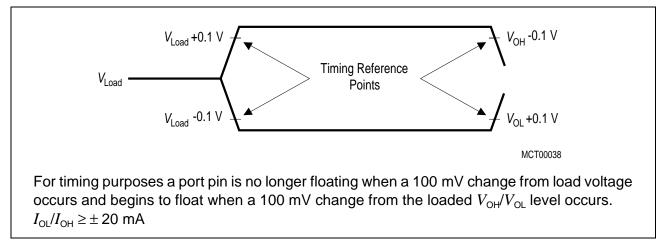

# Figure 42 AC Testing: Input, Output Waveforms

# Figure 43 AC Testing : Float Waveforms

# Figure 44

Recommended Oscillator Circuits for Crystal Oscillator

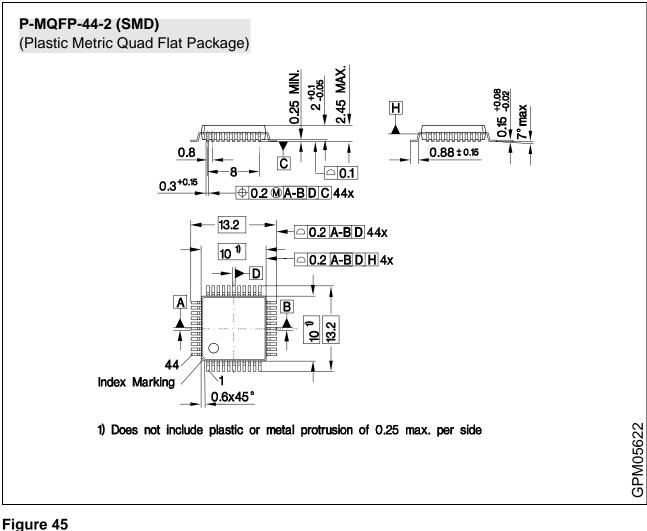

P-MQFP-44 Package Outline

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information" SMD = Surface Mounted Device

Dimensions in mm