Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 21                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 768 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 16x10b; D/A 1x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f338-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Tables**

|    | System Overview                                                          |    |

|----|--------------------------------------------------------------------------|----|

| 2. | Ordering Information                                                     |    |

| _  | Table 2.1. Product Selection Guide                                       | 18 |

| 3. | Pin Definitions                                                          |    |

|    | Table 3.1. Pin Definitions for the C8051F336/7/8/9                       | 19 |

| 4. | QFN-20 Package Specifications                                            |    |

|    | Table 4.1. QFN-20 Package Dimensions                                     |    |

|    | Table 4.2. QFN-20 PCB Land Pattern Dimesions                             | 24 |

| 5. | QFN-24 Package Specifications                                            |    |

|    | Table 5.1. QFN-24 Package Dimensions                                     |    |

|    | Table 5.2. QFN-24 PCB Land Pattern Dimesions                             | 26 |

| 6. | Electrical Characteristics                                               |    |

|    | Table 6.1. Absolute Maximum Ratings                                      |    |

|    | Table 6.2. Global Electrical Characteristics                             |    |

|    | Table 6.3. Port I/O DC Electrical Characteristics                        | 29 |

|    | Table 6.4. Reset Electrical Characteristics                              | 30 |

|    | Table 6.5. Flash Electrical Characteristics                              | 30 |

|    | Table 6.6. Internal High-Frequency Oscillator Electrical Characteristics | 31 |

|    | Table 6.7. Internal Low-Frequency Oscillator Electrical Characteristics  | 31 |

|    | Table 6.8. ADC0 Electrical Characteristics                               |    |

|    | Table 6.9. Temperature Sensor Electrical Characteristics                 | 33 |

|    | Table 6.10. Voltage Reference Electrical Characteristics                 |    |

|    | Table 6.11. IDAC Electrical Characteristics                              | 34 |

|    | Table 6.12. Comparator Electrical Characteristics                        | 35 |

| 7. | 10-Bit ADC (ADC0, C8051F336/8 only)                                      |    |

| 8. | Temperature Sensor (C8051F336/8 only)                                    |    |

| 9. | 10-Bit Current Mode DAC (IDA0, C8051F336/8 only)                         |    |

| 10 | Voltage Reference (C8051F336/8 only)                                     |    |

| 11 | . Comparator0                                                            |    |

| 12 | 2. CIP-51 Microcontroller                                                |    |

|    | Table 12.1. CIP-51 Instruction Set Summary                               | 67 |

| 13 | B. Memory Organization                                                   |    |

| 14 | . Special Function Registers                                             |    |

|    | Table 14.1. Special Function Register (SFR) Memory Map                   | 78 |

|    | Table 14.2. Special Function Registers                                   |    |

| 15 | i. Interrupts                                                            |    |

|    | Table 15.1. Interrupt Summary                                            | 84 |

| 16 | 5. Flash Memory                                                          |    |

|    | Table 16.1. Flash Security Summary                                       | 94 |

| 17 | . Reset Sources                                                          |    |

| 18 | 8. Power Management Modes                                                |    |

|    | ). Oscillators and Clock Selection                                       |    |

| 20 | ). Port Input/Output                                                     |    |

|    |                                                                          |    |

# SFR Definition 9.2. IDA0H: IDA0 Data Word MSB

| Bit    | 7            | 6 | 5 | 4  | 3          | 2 | 1 | 0 |  |  |

|--------|--------------|---|---|----|------------|---|---|---|--|--|

| Name   | IDA0[9:2]    |   |   |    |            |   |   |   |  |  |

| Туре   |              |   |   | R/ | W          |   |   |   |  |  |

| Reset  | 0            | 0 | 0 | 0  | 0          | 0 | 0 | 0 |  |  |

| SFR Ad | dress = 0x97 | 7 |   |    |            |   |   |   |  |  |

| D:4    | Mana         |   |   |    | E.m. atian |   |   |   |  |  |

| Bit | Name      | Function                                   |

|-----|-----------|--------------------------------------------|

| 7:0 | IDA0[9:2] | IDA0 Data Word High-Order Bits.            |

|     |           | Upper 8 bits of the 10-bit IDA0 Data Word. |

### SFR Definition 9.3. IDA0L: IDA0 Data Word LSB

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|---|---|---|---|---|---|---|

| Name  | IDA0[1:0] |   |   |   |   |   |   |   |

| Туре  | R/W       |   | R | R | R | R | R | R |

| Reset | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x96

| Bit | Name      | Function                                    |  |  |  |  |  |

|-----|-----------|---------------------------------------------|--|--|--|--|--|

| 7:6 | IDA0[1:0] | A0 Data Word Low-Order Bits.                |  |  |  |  |  |

|     |           | Lower 2 bits of the 10-bit IDA0 Data Word.  |  |  |  |  |  |

| 5:0 | Unused    | Unused. Read = 000000b. Write = Don't care. |  |  |  |  |  |

## SFR Definition 11.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|---|---|--------|--------|---|---|------------|---|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

SFR Address = 0x9D

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:6 | Unused     | Unused. Read = 00b, Write = Don't Care.                                    |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.                                  |

|     |            | 0: Comparator0 Rising-edge interrupt disabled.                             |

|     |            | 1: Comparator0 Rising-edge interrupt enabled.                              |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.                                 |

|     |            | 0: Comparator0 Falling-edge interrupt disabled.                            |

|     |            | 1: Comparator0 Falling-edge interrupt enabled.                             |

| 3:2 | Unused     | Unused. Read = 00b, Write = don't care.                                    |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.                                                   |

|     |            | These bits affect the response time and power consumption for Comparator0. |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |

|     |            | 01: Mode 1                                                                 |

|     |            | 10: Mode 2                                                                 |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |

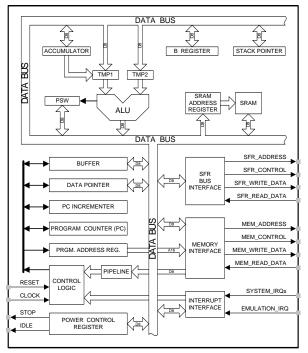

# 12. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 26), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 12.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 12.1. CIP-51 Block Diagram

# 14. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F336/7/8/9's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F336/7/8/9. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 14.1 lists the SFRs implemented in the C8051F336/7/8/9 device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 14.2, for a detailed description of each register.

| F8 | SPIOCN | PCA0L         | PCA0H    | PCA0CPL0 | PCA0CPH0 | POMAT   | POMASK  | VDM0CN  |

|----|--------|---------------|----------|----------|----------|---------|---------|---------|

| F0 | В      | POMDIN        | P1MDIN   | P2MDIN   |          |         | EIP1    | PCA0PWM |

| E8 | ADC0CN | PCA0CPL1      | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | P1MAT   | P1MASK  | RSTSRC  |

| E0 | ACC    | XBR0          | XBR1     | OSCLCN   | IT01CF   |         | EIE1    | SMB0ADM |

| D8 | PCA0CN | PCA0MD        | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 |         |         |         |

| D0 | PSW    | <b>REF0CN</b> |          |          | P0SKIP   | P1SKIP  | P2SKIP  | SMB0ADR |

| C8 | TMR2CN |               | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H   |         |         |

| C0 | SMB0CN | SMB0CF        | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL | ADC0LTH |         |

| B8 | IP     | IDA0CN        | AMX0N    | AMX0P    | ADC0CF   | ADC0L   | ADC0H   |         |

| B0 |        | OSCXCN        | OSCICN   | OSCICL   |          |         | FLSCL   | FLKEY   |

| A8 | IE     | CLKSEL        | EMI0CN   |          |          |         |         |         |

| A0 | P2     | SPI0CFG       | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT | P2MDOUT |         |

| 98 | SCON0  | SBUF0         |          | CPT0CN   |          | CPT0MD  |         | CPT0MX  |

| 90 | P1     | TMR3CN        | TMR3RLL  | TMR3RLH  | TMR3L    | TMR3H   | IDA0L   | IDA0H   |

| 88 | TCON   | TMOD          | TL0      | TL1      | TH0      | TH1     | CKCON   | PSCTL   |

| 80 | P0     | SP            | DPL      | DPH      |          |         |         | PCON    |

|    | 0(8)   | 1(9)          | 2(A)     | 3(B)     | 4(C)     | 5(D)    | 6(E)    | 7(F)    |

#### Table 14.1. Special Function Register (SFR) Memory Map

**Note:** SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations and can be used with bitwise instructions.

| Table 1 | 5.1. | Interrupt | Summary |

|---------|------|-----------|---------|

|---------|------|-----------|---------|

| Interrupt Source                | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|---------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                           | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(/INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow                | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(/INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow                | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                           | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow                | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                            | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                            | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| Port Match                      | 0x0043              | 8                 | None                                                                       | N/A              | N/A            | EMAT<br>(EIE1.1)   | PMAT<br>(EIP1.1)    |

| ADC0 Window Com-<br>pare        | 0x004B              | 9                 | ADOWINT<br>(ADC0CN.3)                                                      | Y                | N              | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 Conversion<br>Complete     | 0x0053              | 10                | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable Coun-<br>ter Array | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                     | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| RESERVED                        | 0x006B              | 13                | N/A                                                                        | N/A              | N/A            | N/A                | N/A                 |

| Timer 3 Overflow                | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

#### **15.2.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## SFR Definition 15.4. EIP1: Extended Interrupt Priority 1

| Bit   | 7   | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|-----|----------|------|-------|-------|--------|------|-------|

| Name  | PT3 | Reserved | PCP0 | PPCA0 | PADC0 | PWADC0 | PMAT | PSMB0 |

| Туре  | R/W | R/W      | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0   | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xF6

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                     |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PT3      | Timer 3 Interrupt Priority Control.This bit sets the priority of the Timer 3 interrupt.0: Timer 3 interrupts set to low priority level.1: Timer 3 interrupts set to high priority level.                                                                                                                     |

| 6   | Reserved | Reserved. Must Write 0.                                                                                                                                                                                                                                                                                      |

| 5   | PCP0     | Comparator0 (CP0) Interrupt Priority Control.<br>This bit sets the priority of the CP0 interrupt.<br>0: CP0 interrupt set to low priority level.<br>1: CP0 interrupt set to high priority level.                                                                                                             |

| 4   | PPCA0    | <ul> <li>Programmable Counter Array (PCA0) Interrupt Priority Control.</li> <li>This bit sets the priority of the PCA0 interrupt.</li> <li>0: PCA0 interrupt set to low priority level.</li> <li>1: PCA0 interrupt set to high priority level.</li> </ul>                                                    |

| 3   | PADC0    | <ul> <li>ADC0 Conversion Complete Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Conversion Complete interrupt.</li> <li>0: ADC0 Conversion Complete interrupt set to low priority level.</li> <li>1: ADC0 Conversion Complete interrupt set to high priority level.</li> </ul> |

| 2   | PWADC0   | <ul> <li>ADC0 Window Comparator Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Window interrupt.</li> <li>0: ADC0 Window interrupt set to low priority level.</li> <li>1: ADC0 Window interrupt set to high priority level.</li> </ul>                                          |

| 1   | PMAT     | Port Match Interrupt Priority Control.<br>This bit sets the priority of the Port Match Event interrupt.<br>0: Port Match interrupt set to low priority level.<br>1: Port Match interrupt set to high priority level.                                                                                         |

| 0   | PSMB0    | SMBus (SMB0) Interrupt Priority Control.This bit sets the priority of the SMB0 interrupt.0: SMB0 interrupt set to low priority level.1: SMB0 interrupt set to high priority level.                                                                                                                           |

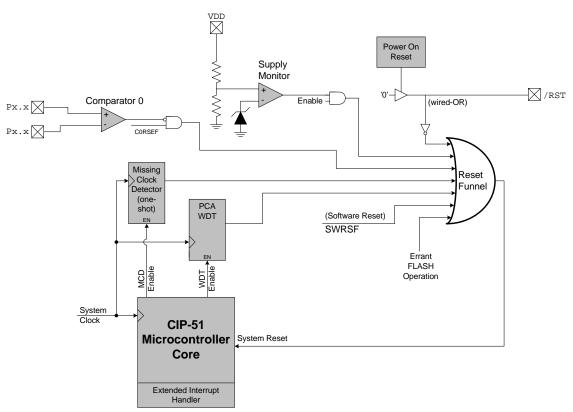

# 17. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. Upon entering this reset state, the following events occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 17.1. Reset Sources

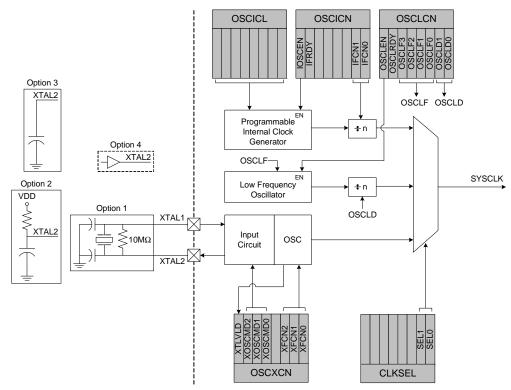

# **19. Oscillators and Clock Selection**

C8051F336/7/8/9 devices include a programmable internal high-frequency oscillator, a programmable internal low-frequency oscillator, and an external oscillator drive circuit. The internal high-frequency oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 19.1. The internal low-frequency oscillator can be enabled/disabled and calibrated using the OSCLCN register. The system clock can be sourced by the external oscillator circuit or either internal oscillator. Both internal oscillators offer a selectable post-scaling feature.

Figure 19.1. Oscillator Options

### 19.1. System Clock Selection

The CLKSL[1:0] bits in register CLKSEL select which oscillator source is used as the system clock. CLKSL[1:0] must be set to 01b for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator, external oscillator, and Clock Multiplier so long as the selected clock source is enabled and has settled.

The internal high-frequency and low-frequency oscillators require little start-up time and may be selected as the system clock immediately following the register write which enables the oscillator. The external RC and C modes also typically require no startup time.

External crystals and ceramic resonators however, typically require a start-up time before they are settled and ready for use. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external crystal or ceramic resonator is settled. In crystal mode, to avoid reading a false XTLVLD, software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.

#### 19.4.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 19.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation 19.2, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in Volts.

#### Equation 19.2. C Mode Oscillator Frequency

$f = (KF)/(R \times V_{DD})$

For example: Assume  $V_{DD}$  = 3.0 V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 19.5 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

#### 20.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE =  $^{1}$ ).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 20.8 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to '1' enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

# SFR Definition 20.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7 | 6 | 5     | 4    | 3      | 2     | 1     | 0     |

|-------|---|---|-------|------|--------|-------|-------|-------|

| Name  |   |   | CP0AE | CP0E | SYSCKE | SMB0E | SPI0E | URT0E |

| Туре  | R | R | R/W   | R/W  | R/W    | R/W   | R/W   | R/W   |

| Reset | 0 | 0 | 0     | 0    | 0      | 0     | 0     | 0     |

SFR Address = 0xE1

| Bit | Name   | Function                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------|

| 7:6 | UNUSED | Unused. Read = 00b; Write = Don't Care.                                                    |

| 5   | CP0AE  | Comparator0 Asynchronous Output Enable.                                                    |

|     |        | 0: Asynchronous CP0 unavailable at Port pin.                                               |

|     |        | 1: Asynchronous CP0 routed to Port pin.                                                    |

| 4   | CP0E   | Comparator0 Output Enable.                                                                 |

|     |        | 0: CP0 unavailable at Port pin.                                                            |

|     |        | 1: CP0 routed to Port pin.                                                                 |

| 3   | SYSCKE | /SYSCLK Output Enable.                                                                     |

|     |        | 0: /SYSCLK unavailable at Port pin.                                                        |

|     |        | 1: /SYSCLK output routed to Port pin.                                                      |

| 2   | SMB0E  | SMBus I/O Enable.                                                                          |

|     |        | 0: SMBus I/O unavailable at Port pins.                                                     |

|     |        | 1: SMBus I/O routed to Port pins.                                                          |

| 1   | SPI0E  | SPI I/O Enable.                                                                            |

|     |        | 0: SPI I/O unavailable at Port pins.                                                       |

|     |        | 1: SPI I/O routed to Port pins. Note that the SPI can be assigned either 3 or 4 GPIO pins. |

| 0   | URT0E  |                                                                                            |

| U   | URIUE  | UART I/O Output Enable.                                                                    |

|     |        | 0: UART I/O unavailable at Port pin.                                                       |

|     |        | 1: UART TX0, RX0 routed to Port pins P0.4 and P0.5.                                        |

## SFR Definition 20.4. P0MAT: Port 0 Match Register

| Bit   | 7          | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------|-----------------|---|----|---|---|---|---|--|--|--|

| Name  | POMAT[7:0] |                 |   |    |   |   |   |   |  |  |  |

| Туре  |            |                 |   | R/ | W |   |   |   |  |  |  |

| Reset | 1          | 1 1 1 1 1 1 1 1 |   |    |   |   |   |   |  |  |  |

SFR Address = 0xFD

| Bit | Name       | Function                                                                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MAT[7:0] | Port 0 Match Value.                                                                                                                                                                           |

|     |            | Match comparison value used on Port 0 for bits in P0MASK which are set to '1'.<br>0: P0.n pin logic value is compared with logic LOW.<br>1: P0.n pin logic value is compared with logic HIGH. |

## SFR Definition 20.5. P1MASK: Port 1 Mask Register

| Bit   | 7           | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|-----|---|---|---|---|---|---|--|--|--|

| Name  | P1MASK[7:0] |     |   |   |   |   |   |   |  |  |  |

| Туре  |             | R/W |   |   |   |   |   |   |  |  |  |

| Reset | 0           | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xEE

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

# SFR Definition 20.7. P0: Port 0

| Bit   | 7       | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------|-----|---|---|---|---|---|---|--|--|--|

| Name  | P0[7:0] |     |   |   |   |   |   |   |  |  |  |

| Туре  |         | R/W |   |   |   |   |   |   |  |  |  |

| Reset | 1       | 1   | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

SFR Address = 0x80; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | LOW.<br>1: Set output latch to logic | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

## SFR Definition 20.8. P0MDIN: Port 0 Input Mode

| Bit   | 7           | 6             | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|---------------|---|----|---|---|---|---|--|--|--|

| Name  | POMDIN[7:0] |               |   |    |   |   |   |   |  |  |  |

| Туре  |             |               |   | R/ | W |   |   |   |  |  |  |

| Reset | 1           | 1 1 1 1 1 1 1 |   |    |   |   |   |   |  |  |  |

SFR Address = 0xF1

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P0.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P0.n pin is not configured for analog mode.                                                |

# SFR Definition 20.11. P1: Port 1

| Bit   | 7       | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------|-----|---|---|---|---|---|---|--|--|--|

| Name  | P1[7:0] |     |   |   |   |   |   |   |  |  |  |

| Туре  |         | R/W |   |   |   |   |   |   |  |  |  |

| Reset | 1       | 1   | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

SFR Address = 0x90; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------|

| 7:0 | P1[7:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. |       | 0: P1.n Port pin is logic<br>LOW.<br>1: P1.n Port pin is logic<br>HIGH. |

## SFR Definition 20.12. P1MDIN: Port 1 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P1MDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0xF2

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P1.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P1.n pin is not configured for analog mode.                                                |

### 22.1. Enhanced Baud Rate Generation

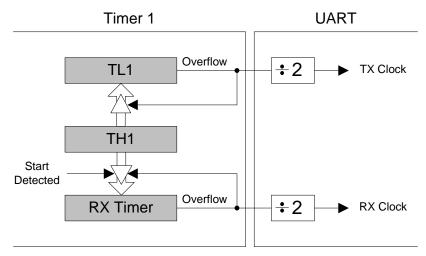

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 22.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 22.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "24.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 184). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK/4, SYSCLK/12, SYSCLK/48, the external oscillator clock/8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 22.1-A and Equation 22.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

## Equation 22.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "24. Timers" on page 180. A quick reference for typical baud rates and system clock frequencies is given in Table 22.1 through Table 22.2. The internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and reenabling SPI0 with the SPIEN bit. Figure 23.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

#### 23.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

#### 23.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 23.5. For slave mode, the clock and data relationships are shown in Figure 23.6 and Figure 23.7. Note that CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 23.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the slave's SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

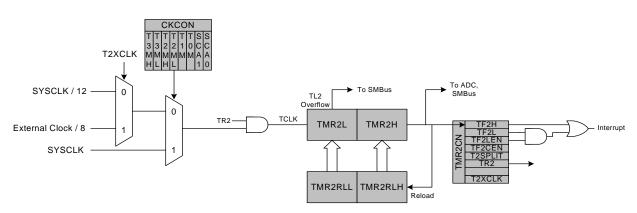

#### 24.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 2 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 24.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 24.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x00.

Figure 24.4. Timer 2 16-Bit Mode Block Diagram

# SFR Definition 24.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit   | 7                 | 6            | 5                                 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------------|--------------|-----------------------------------|---|---|---|---|---|

| Nam   | e                 | TMR2RLL[7:0] |                                   |   |   |   |   |   |

| Туре  | )                 | R/W          |                                   |   |   |   |   |   |

| Rese  | et O              | 0            | 0                                 | 0 | 0 | 0 | 0 | 0 |

| SFR A | FR Address = 0xCA |              |                                   |   |   |   |   |   |

| Bit   | Name              |              | Function                          |   |   |   |   |   |

| 7:0   | TMR2RLL[7:0       | ] Timer 2 I  | Fimer 2 Reload Register Low Byte. |   |   |   |   |   |

TMR2RLL holds the low byte of the reload value for Timer 2.

#### SFR Definition 24.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit               | 7               | 6                                                                                                                         | 5        | 4 | 3 | 2 | 1 | 0 |

|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|----------|---|---|---|---|---|

| Name TMR2RLH[7:0] |                 |                                                                                                                           |          |   |   |   |   |   |

| Туре              | pe R/W          |                                                                                                                           |          |   |   |   |   |   |

| Rese              | et <sup>0</sup> | 0                                                                                                                         | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR A             | Address = 0xCB  |                                                                                                                           |          |   |   |   |   |   |

| Bit               | Name            |                                                                                                                           | Function |   |   |   |   |   |

| 7:0               | TMR2RLH[7:0]    | IR2RLH[7:0]       Timer 2 Reload Register High Byte.         TMR2RLH holds the high byte of the reload value for Timer 2. |          |   |   |   |   |   |

#### SFR Definition 24.11. TMR2L: Timer 2 Low Byte

| Bit    | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|-------------|---|---|---|---|---|---|---|

| Name   | TMR2L[7:0]  |   |   |   |   |   |   |   |

| Туре   | R/W         |   |   |   |   |   |   |   |

| Reset  | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Ad | dress = 0xC | С |   |   |   |   |   |   |

| Bit    | Name        |   |   |   |   |   |   |   |

| BIt | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

# 26. C2 Interface

C8051F336/7/8/9 devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

#### 26.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

#### C2 Register Definition 26.1. C2ADD: C2 Address

| Bit   | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|------------|---|---|---|---|---|---|

| Name  |     | C2ADD[7:0] |   |   |   |   |   |   |

| Туре  | R/W |            |   |   |   |   |   |   |

| Reset | 0   | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       |                     | Function                                                                                                                        |  |  |  |  |  |

|-----|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | C2ADD[7:0] | C2 Address.         |                                                                                                                                 |  |  |  |  |  |

|     |            |                     | The C2ADD register is accessed via the C2 interface to select the target Data register or C2 Data Read and Data Write commands. |  |  |  |  |  |

|     |            | Address Description |                                                                                                                                 |  |  |  |  |  |

|     |            | 0x00                | Selects the Device ID register for Data Read instructions                                                                       |  |  |  |  |  |

|     |            | 0x01                | Selects the Revision ID register for Data Read instructions                                                                     |  |  |  |  |  |

|     |            | 0x02                | Selects the C2 Flash Programming Control register for Data<br>Read/Write instructions                                           |  |  |  |  |  |

|     |            | 0xB4                | Selects the C2 Flash Programming Data register for Data<br>Read/Write instructions                                              |  |  |  |  |  |