Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1847-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

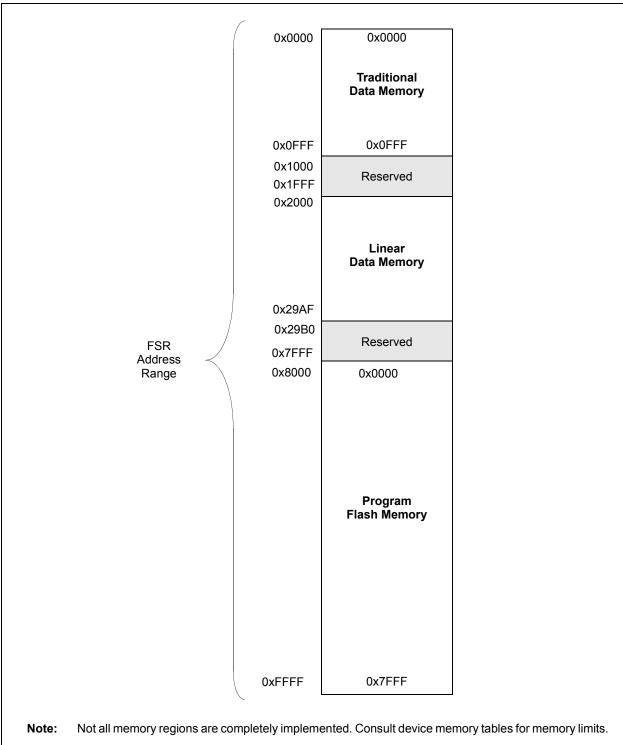

#### 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC16(L)F1847: Data Memory, Program Memory and Data EEPROM Memory<sup>(1)</sup>.

- Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Device Memory Maps

- Special Function Registers Summary

- Data EEPROM memory<sup>(1)</sup>

Note 1: The Data EEPROM Memory and the method to access Flash memory through the EECON registers is described in Section 11.0 "Data EEPROM and Flash Program Memory Control". The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a  $32K \times 14$  program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1847 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

#### TABLE 3-1:DEVICE SIZES AND ADDRESSES

| Device        | Program Memory Space (Words) | Last Program Memory Address |

|---------------|------------------------------|-----------------------------|

| PIC16(L)F1847 | 8,192                        | 1FFFh                       |

| Address             | Name    | Bit 7                          | Bit 6          | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------------------|---------|--------------------------------|----------------|------------------|-----------------|---------------|-------------|--------|---------|----------------------|---------------------------------|

| Bank 2              |         |                                |                |                  |                 |               |             |        |         |                      |                                 |

| 100h <sup>(1)</sup> | INDF0   | Addressing the (not a physic)  |                | es contents of   | FSR0H/FSR0      | )L to address | data memory | /      |         | XXXX XXXX            | XXXX XXXX                       |

| 101h <sup>(1)</sup> | INDF1   | Addressing th<br>(not a physic |                | es contents of   | FSR1H/FSR1      | IL to address | data memory | 1      |         | XXXX XXXX            | XXXX XXXX                       |

| 102h <sup>(1)</sup> | PCL     | Program Cou                    | unter (PC) Lea | st Significant E | Byte            |               |             |        |         | 0000 0000            | 0000 0000                       |

| 103h <sup>(1)</sup> | STATUS  | —                              | _              | —                | TO              | PD            | Z           | DC     | С       | 1 1000               | q quuu                          |

| 104h <sup>(1)</sup> | FSR0L   | Indirect Data                  | Memory Addr    | ess 0 Low Poir   | nter            |               |             |        |         | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(1)</sup> | FSR0H   | Indirect Data                  | Memory Addr    | ess 0 High Poi   | nter            |               |             |        |         | 0000 0000            | 0000 0000                       |

| 106h <sup>(1)</sup> | FSR1L   | Indirect Data                  | Memory Addr    | ess 1 Low Poir   | nter            |               |             |        |         | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(1)</sup> | FSR1H   | Indirect Data                  | Memory Addr    | ess 1 High Poi   | nter            |               |             |        |         | 0000 0000            | 0000 0000                       |

| 108h <sup>(1)</sup> | BSR     | _                              | _              | —                |                 |               | BSR<4:0>    |        |         | 0 0000               | 0 0000                          |

| 109h <sup>(1)</sup> | WREG    | Working Reg                    | ister          |                  |                 |               |             |        |         | 0000 0000            | uuuu uuuu                       |

| 10Ah <sup>(1)</sup> | PCLATH  | _                              | Write Buffer f | or the upper 7   | bits of the Pro | ogram Counte  | r           |        |         | -000 0000            | -000 0000                       |

| 10Bh <sup>(1)</sup> | INTCON  | GIE                            | PEIE           | TMR0IE           | INTE            | IOCE          | TMR0IF      | INTF   | IOCF    | 0000 000x            | 0000 000u                       |

| 10Ch                | LATA    | LATA7                          | LATA6          | —                | LATA4           | LATA3         | LATA2       | LATA1  | LATA0   | xx-x xxxx            | uu-u uuuu                       |

| 10Dh                | LATB    | LATB7                          | LATB6          | LATB5            | LATB4           | LATB3         | LATB2       | LATB1  | LATB0   | XXXX XXXX            | uuuu uuuu                       |

| 10Eh                | —       | Unimplement                    | ted            | •                | •               | •             |             |        | •       | _                    | _                               |

| 10Fh                | —       | Unimplement                    | ted            |                  |                 |               |             |        |         | _                    | _                               |

| 110h                | _       | Unimplement                    | ted            |                  |                 |               |             |        |         | _                    | _                               |

| 111h                | CM1CON0 | C10N                           | C10UT          | C10E             | C1POL           | _             | C1SP        | C1HYS  | C1SYNC  | 0000 -100            | 0000 -100                       |

| 112h                | CM1CON1 | C1INTP                         | C1INTN         | C1PCH            | l<1:0>          | _             | _           | C1NCI  | H<1:0>  | 000000               | 000000                          |

| 113h                | CM2CON0 | C2ON                           | C2OUT          | C2OE             | C2POL           | _             | C2SP        | C2HYS  | C2SYNC  | 0000 -100            | 0000 -100                       |

| 114h                | CM2CON1 | C2INTP                         | C2INTN         | C2PCH            | l<1:0>          | _             | _           | C2NCI  | H<1:0>  | 000000               | 000000                          |

| 115h                | CMOUT   | _                              | _              | —                |                 | _             | _           | MC2OUT | MC10UT  | 00                   | 00                              |

| 116h                | BORCON  | SBOREN                         | _              | —                | _               | _             | _           | _      | BORRDY  | 1 q                  | u u                             |

| 117h                | FVRCON  | FVREN                          | FVRRDY         | TSEN             | TSRNG           | CDAFV         | R<1:0>      | ADFVF  | R<1:0>  | 0qrr 0000            | 0qrr 0000                       |

| 118h                | DACCON0 | DACEN                          | DACLPS         | DACOE            |                 | DACPS         | S<1:0>      |        | DACNSS  | 000- 00-0            | 000- 00-0                       |

| 119h                | DACCON1 | _                              | _              | —                |                 | [             | DACR<4:0>   |        |         | 0 0000               | 0 0000                          |

| 11Ah                | SRCON0  | SRLEN                          |                | SRCLK<2:0>       |                 | SRQEN         | SRNQEN      | SRPS   | SRPR    | 0000 0000            | 0000 0000                       |

| 11Bh                | SRCON1  | SRSPE                          | SRSCKE         | SRSC2E           | SRSC1E          | SRRPE         | SRRCKE      | SRRC2E | SRRC1E  | 0000 0000            | 0000 0000                       |

| 11Ch                | —       | Unimplement                    | ted            |                  |                 |               |             |        |         | —                    | —                               |

| 11Dh                | APFCON0 | RXDTSEL                        | SDO1SEL        | SS1SEL           | P2BSEL          | CCP2SEL       | P1DSEL      | P1CSEL | CCP1SEL | 0000 0000            | 0000 0000                       |

|                     | APFCON1 | _                              | _              | _                | _               |               | _           |        | TXCKSEL | 0                    | 0                               |

| 11Eh                | AFICONT |                                |                |                  |                 |               |             |        | INCOLCE | 0                    | -                               |

#### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:legend: Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.$

**Note 1:** These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

| Address             | Name   | Bit 7                            | Bit 6           | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------------------|--------|----------------------------------|-----------------|------------------|-----------------|---------------|-------------|-------|--------|----------------------|---------------------------------|

| Bank 8              |        |                                  |                 |                  |                 |               |             |       |        |                      |                                 |

| 400h <sup>(1)</sup> | INDF0  | Addressing th<br>(not a physical |                 | es contents of   | FSR0H/FSR0      | )L to address | data memory | ,     |        | XXXX XXXX            | XXXX XXXX                       |

| 401h <sup>(1)</sup> | INDF1  | Addressing th<br>(not a physica  |                 | es contents of   | FSR1H/FSR1      | L to address  | data memory | ,     |        | XXXX XXXX            | XXXX XXXX                       |

| 402h <sup>(1)</sup> | PCL    | Program Cou                      | inter (PC) Lea  | st Significant E | Byte            |               |             |       |        | 0000 0000            | 0000 0000                       |

| 403h <sup>(1)</sup> | STATUS | _                                | —               | —                | TO              | PD            | Z           | DC    | С      | 1 1000               | q quuu                          |

| 404h <sup>(1)</sup> | FSR0L  | Indirect Data                    | Memory Addr     | ess 0 Low Poi    | nter            |               |             |       |        | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(1)</sup> | FSR0H  | Indirect Data                    | Memory Addr     | ess 0 High Poi   | inter           |               |             |       |        | 0000 0000            | 0000 0000                       |

| 406h <sup>(1)</sup> | FSR1L  | Indirect Data                    | Memory Addr     | ess 1 Low Poir   | nter            |               |             |       |        | 0000 0000            | uuuu uuuu                       |

| 407h <sup>(1)</sup> | FSR1H  | Indirect Data                    | Memory Addr     | ess 1 High Poi   | inter           |               |             |       |        | 0000 0000            | 0000 0000                       |

| 408h <sup>(1)</sup> | BSR    | _                                | _               | _                |                 |               | BSR<4:0>    |       |        | 0 0000               | 0 0000                          |

| 409h <sup>(1)</sup> | WREG   | Working Reg                      | ister           |                  |                 |               |             |       |        | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1)</sup> | PCLATH | _                                | Write Buffer f  | or the upper 7   | bits of the Pro | ogram Counte  | er          |       |        | -000 0000            | -000 0000                       |

| 40Bh <sup>(1)</sup> | INTCON | GIE                              | PEIE            | TMR0IE           | INTE            | IOCE          | TMR0IF      | INTF  | IOCF   | 0000 000x            | 0000 000u                       |

| 40Ch                | —      | Unimplement                      | ed              |                  | •               |               | •           |       |        | _                    | —                               |

| 40Dh                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 40Eh                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 40Fh                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 410h                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 411h                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 412h                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 413h                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 414h                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 415h                | TMR4   | Timer4 Modu                      | le Register     |                  |                 |               |             |       |        | 0000 0000            | 0000 0000                       |

| 416h                | PR4    | Timer4 Perio                     | d Register      |                  |                 |               |             |       |        | 1111 1111            | 1111 1111                       |

| 417h                | T4CON  | _                                |                 | T4OUTF           | PS<3:0>         |               | TMR40N      | T4CKP | S<1:0> | -000 0000            | -000 0000                       |

| 418h                | _      | Unimplement                      | ed              |                  |                 |               | •           |       |        | _                    | _                               |

| 419h                | _      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | _                               |

| 41Ah                | —      | Unimplement                      | ed              |                  |                 |               |             |       |        | _                    | —                               |

| 41Bh                | —      | Unimplement                      | Unimplemented — |                  |                 |               |             |       | _      | —                    |                                 |

| 41Ch                | TMR6   | Timer6 Modu                      | le Register     |                  |                 |               |             |       |        | 0000 0000            | 0000 0000                       |

| 41Dh                | PR6    | Timer6 Perio                     | d Register      |                  |                 |               |             |       |        | 1111 1111            | 1111 1111                       |

| 41Eh                | T6CON  | _                                |                 | T6OUTF           | PS<3:0>         |               | TMR6ON      | T6CKP | S<1:0> | -000 0000            | -000 0000                       |

| 41Fh                |        | Unimplement                      | ied             |                  |                 |               | •           | •     |        | 1                    | İ                               |

#### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:legend: Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.$

Note 1: These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

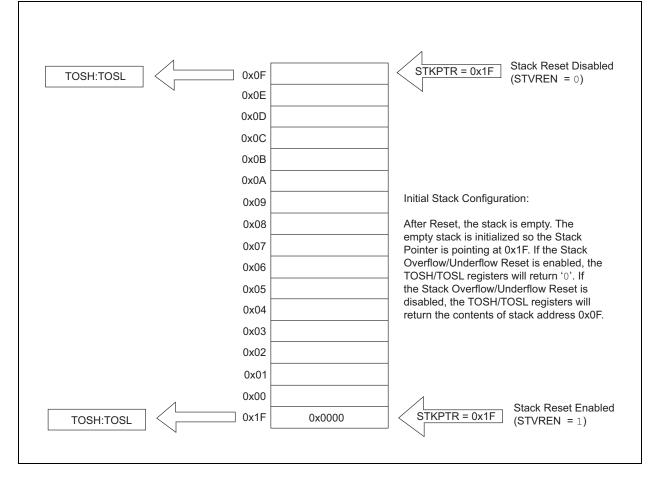

#### 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-4 through 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit = 0 (Configuration Words). This means that after the stack has been PUSHed 16 times, the 17th PUSH overwrites the value that was stored from the first PUSH. The 18th PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

#### FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

#### 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

| Note: | The DEBUG bit in Configuration Word is      |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH REFERENCE CLOCK SOURCES

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3          | Bit 2 | Bit 1       | Bit 0 | Register<br>on Page |

|---------|--------|--------|---------|-------|----------------|-------|-------------|-------|---------------------|

| CLKRCON | CLKREN | CLKROE | CLKRSLR | CLKRI | DC<1:0>        | C     | LKRDIV<2:0> | >     | 70                  |

| Logondi |        |        |         |       | alla ara natua |       | l l         |       |                     |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

#### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH REFERENCE CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREI    | N<1:0>    | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   |          | FOSC<2:0> |         | 46                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

| U-0              | U-0                                                                                                  | R/W-0/0                        | R/W-0/0  | R/W-0/0        | U-0              | R/W-0/0           | U-0        |

|------------------|------------------------------------------------------------------------------------------------------|--------------------------------|----------|----------------|------------------|-------------------|------------|

| —                |                                                                                                      | CCP4IE                         | CCP3IE   | TMR6IE         | —                | TMR4IE            |            |

| bit 7            |                                                                                                      |                                |          |                |                  |                   | bit 0      |

|                  |                                                                                                      |                                |          |                |                  |                   |            |

| Legend:          |                                                                                                      |                                |          |                |                  |                   |            |

| R = Readable     | bit                                                                                                  | W = Writable                   | bit      | U = Unimpler   | mented bit, read | as '0'            |            |

| u = Bit is unch  | anged                                                                                                | x = Bit is unkr                | nown     | -n/n = Value a | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is set |                                                                                                      | '0' = Bit is clea              | ared     |                |                  |                   |            |

|                  |                                                                                                      |                                |          |                |                  |                   |            |

| bit 7-6          | Unimplemen                                                                                           | ted: Read as '                 | 0'       |                |                  |                   |            |

| bit 5            | CCP4IE: CCF                                                                                          | P4 Interrupt En                | able bit |                |                  |                   |            |

|                  |                                                                                                      | the CCP4 inter                 |          |                |                  |                   |            |

|                  |                                                                                                      | the CCP4 inter                 | •        |                |                  |                   |            |

| bit 4            |                                                                                                      | P3 Interrupt En                |          |                |                  |                   |            |

|                  |                                                                                                      | the CCP3 inter                 |          |                |                  |                   |            |

| 1.1.0            |                                                                                                      | the CCP3 inter                 | •        |                |                  |                   |            |

| bit 3            |                                                                                                      | R6 to PR6 Mate                 |          |                |                  |                   |            |

|                  |                                                                                                      | the TMR6 to P<br>the TMR6 to P |          |                |                  |                   |            |

| bit 2            |                                                                                                      | ted: Read as '                 |          |                |                  |                   |            |

| bit 1            | -                                                                                                    |                                |          | nable bit      |                  |                   |            |

|                  | <b>TMR4IE:</b> TMR4 to PR4 Match Interrupt Enable bit<br>1 = Enables the TMR4 to PR4 Match interrupt |                                |          |                |                  |                   |            |

|                  |                                                                                                      | the TMR4 to P                  |          |                |                  |                   |            |

| bit 0            | Unimplemen                                                                                           | ted: Read as '                 | 0'       |                |                  |                   |            |

|                  |                                                                                                      |                                |          |                |                  |                   |            |

|                  | PEIE of the IN                                                                                       |                                | must bo  |                |                  |                   |            |

#### REGISTER 8-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

ote 1: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### 10.0 WATCHDOG TIMER

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (typical)

- Multiple Reset conditions

- Operation during Sleep

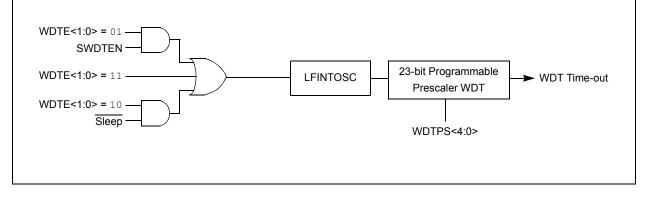

#### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

#### 16.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 16-1: ADCON0: ADC CONTROL REGISTER 0

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|----------|---------|---------|---------|---------|

| _     |         |         | CHS<4:0> |         |         | GO/DONE | ADON    |

| bit 7 |         |         |          |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-2 | CHS<4:0>: Analog Channel Select bits                                                                                                                                                                                                                      |

|         | 00000 <b>= ANO</b>                                                                                                                                                                                                                                        |

|         | 00001 <b>= AN1</b>                                                                                                                                                                                                                                        |

|         | 00010 <b>= AN2</b>                                                                                                                                                                                                                                        |

|         | 00011 <b>= AN3</b>                                                                                                                                                                                                                                        |

|         | 00100 <b>= AN4</b>                                                                                                                                                                                                                                        |

|         | 00101 <b>= AN5</b>                                                                                                                                                                                                                                        |

|         | 00110 <b>= AN6</b>                                                                                                                                                                                                                                        |

|         | 00111 <b>= AN7</b>                                                                                                                                                                                                                                        |

|         | 01000 <b>= AN8</b>                                                                                                                                                                                                                                        |

|         | 01001 <b>= AN9</b>                                                                                                                                                                                                                                        |

|         | 01010 = AN10                                                                                                                                                                                                                                              |

|         | 01011 = AN11                                                                                                                                                                                                                                              |

|         | 01100 = Reserved. No channel connected.                                                                                                                                                                                                                   |

|         |                                                                                                                                                                                                                                                           |

|         | •                                                                                                                                                                                                                                                         |

|         | 11100 = Reserved. No channel connected.                                                                                                                                                                                                                   |

|         | 11101 = Temperature Indicator                                                                                                                                                                                                                             |

|         | 11110 = DAC output <sup>(1)</sup>                                                                                                                                                                                                                         |

|         | 11111 = FVR (Fixed Voltage Reference) Buffer 1 Output <sup>(2)</sup>                                                                                                                                                                                      |

| bit 1   | GO/DONE: ADC Conversion Status bit                                                                                                                                                                                                                        |

|         | <ul> <li>1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle.<br/>This bit is automatically cleared by hardware when the ADC conversion has completed.</li> <li>0 = ADC conversion completed/not in progress</li> </ul> |

| bit 0   | ADON: ADC Enable bit                                                                                                                                                                                                                                      |

|         | 1 = ADC is enabled                                                                                                                                                                                                                                        |

|         | 0 = ADC is disabled and consumes no operating current                                                                                                                                                                                                     |

| Note 1: | See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information.                                                                                                                                                                         |

| 2:      | See Section TABLE 14-1: "Summary of Registers Associated with the Fixed Voltage Reference"                                                                                                                                                                |

|         | for more information.                                                                                                                                                                                                                                     |

| R/W-0/0          | R/W-0/0                                                                                                                                                                                      | R/W-0/0                            | R/W-0/0        | U-0            | U-0              | R/W-0/0          | R/W-0/0      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|------------------|------------------|--------------|--|--|

| CxINTP           | CxINTP CXINTN CxPCH<1:0                                                                                                                                                                      |                                    | H<1:0>         | _              |                  | CxNCI            | H<1:0>       |  |  |

| bit 7            |                                                                                                                                                                                              |                                    |                |                |                  |                  | bit (        |  |  |

|                  |                                                                                                                                                                                              |                                    |                |                |                  |                  |              |  |  |

| Legend:          |                                                                                                                                                                                              |                                    |                |                |                  |                  |              |  |  |

| R = Readable     | bit                                                                                                                                                                                          | W = Writable                       | bit            | U = Unimpler   | mented bit, read | l as '0'         |              |  |  |

| u = Bit is unch  | nanged                                                                                                                                                                                       | x = Bit is unkr                    | nown           | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                                                                                                                                                                              | '0' = Bit is clea                  | ared           |                |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              |                                    |                |                |                  |                  |              |  |  |

| bit 7            |                                                                                                                                                                                              | nparator Interru                   | •              | 0 0            |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              |                                    |                |                | ing edge of the  |                  |              |  |  |

|                  |                                                                                                                                                                                              |                                    | •              |                | of the CxOUT b   | DIT              |              |  |  |

| bit 6            |                                                                                                                                                                                              | mparator Interru                   |                | 0 0            |                  |                  |              |  |  |

|                  | <ul> <li>1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit</li> <li>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit</li> </ul> |                                    |                |                |                  |                  |              |  |  |

| bit 5-4          |                                                                                                                                                                                              | <ul> <li>Comparator I</li> </ul>   | C C            |                |                  | bit              |              |  |  |

|                  |                                                                                                                                                                                              | connects to CxII                   |                |                | . 510            |                  |              |  |  |

|                  |                                                                                                                                                                                              | connects to DAC                    |                | erence         |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              | onnects to FVF                     | R Voltage Refe | rence          |                  |                  |              |  |  |

|                  | For C1:                                                                                                                                                                                      |                                    |                |                |                  |                  |              |  |  |

|                  | For C2:                                                                                                                                                                                      | connects to C12                    | in+ pin        |                |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              | connects to Vss                    |                |                |                  |                  |              |  |  |

| bit 3-2          | Unimplemer                                                                                                                                                                                   | nted: Read as '                    | 0'             |                |                  |                  |              |  |  |

| bit 1-0          | I-0 CxNCH<1:0>: Comparator Negative Input Channel Select bits                                                                                                                                |                                    |                |                |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              | connects to C12                    |                |                |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              | connects to C12                    |                |                |                  |                  |              |  |  |

|                  |                                                                                                                                                                                              | connects to C12<br>connects to C12 |                |                |                  |                  |              |  |  |

| Note 1: Cx       |                                                                                                                                                                                              | C12IN+ pin wh                      | •              | norator 2      |                  |                  |              |  |  |

#### REGISTER 19-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

**Note 1:** CxVP connects to C12IN+ pin when using Comparator 2.

#### **REGISTER 19-3: CMOUT: COMPARATOR OUTPUT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

|       | _   | _   | _   | _   | _   | MC2OUT | MC1OUT |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:                            |          |                            |                                                       |

|------------------------------------|----------|----------------------------|-------------------------------------------------------|

| R = Reada                          | ible bit | W = Writable bit           | U = Unimplemented bit, read as '0'                    |

| u = Bit is u                       | nchanged | x = Bit is unknown         | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set                   |          | '0' = Bit is cleared       |                                                       |

| bit 7-2 Unimplemented: Read as '0' |          | nented: Read as '0'        |                                                       |

| bit 1                              | MC2OUT   | : Mirror Copy of C2OUT bit |                                                       |

bit 0 MC10UT: Mirror Copy of C10UT bit

© 2011-2013 Microchip Technology Inc.

| Name   | Bit 7                                         | Bit 6           | Bit 5         | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-----------------------------------------------|-----------------|---------------|---------|--------|--------|--------|--------|---------------------|

| INTCON | GIE                                           | PEIE            | TMR0IE        | INTE    | IOCE   | TMR0IF | INTF   | IOCF   | 88                  |

| PIE1   | TMR1GIE                                       | ADIE            | RCIE          | TXIE    | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 89                  |

| PIR1   | TMR1GIF                                       | ADIF            | RCIF          | TXIF    | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 93                  |

| PIE3   | _                                             | _               | CCP4IE        | CCP3IE  | TMR6IE | _      | TMR4IE | _      | 91                  |

| PIR3   | —                                             | _               | CCP4IF        | CCP3IF  | TMR6IF | —      | TMR4IF | _      | 95                  |

| PR2    | Timer2 Module Period Register                 |                 |               |         |        |        |        |        | 189*                |

| PR4    | Timer4 Module Period Register                 |                 |               |         |        |        |        |        | 189*                |

| PR6    | Timer6 Module Period Register                 |                 |               |         |        |        |        | 189*   |                     |

| T2CON  | —                                             |                 | T2OUT         | PS<3:0> |        | TMR2ON | T2CKP  | S<1:0> | 191                 |

| T4CON  | — T4OUTPS<3:0> TMR4ON T4CKPS<1:0>             |                 |               |         |        |        |        | 191    |                     |

| T6CON  |                                               |                 |               |         |        |        |        | 191    |                     |

| TMR2   | Holding Register for the 8-bit TMR2 Time Base |                 |               |         |        |        |        | 189*   |                     |

| TMR4   | Holding Register for the 8-bit TMR4 Time Base |                 |               |         |        |        |        | 189*   |                     |

| TMR6   | Holding Reg                                   | ister for the 8 | -bit TMR6 Tin | ne Base |        |        |        |        | 189*                |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

Legend: — = unimplemented read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

| R/W-0/0                                                                                       | R/W-0/0                                                                   | R/W-1/1                                  | R/W-0/0         | R-0/0          | U-0              | U-0              | R/W-0/0      |  |  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------|-----------------|----------------|------------------|------------------|--------------|--|--|

| MDEN                                                                                          | MDOE                                                                      | MDSLR                                    | MDOPOL          | MDOUT          |                  | —                | MDBIT        |  |  |

| bit 7                                                                                         |                                                                           |                                          |                 |                |                  |                  | bit (        |  |  |

|                                                                                               |                                                                           |                                          |                 |                |                  |                  |              |  |  |

| Legend:                                                                                       |                                                                           |                                          |                 |                |                  |                  |              |  |  |

| R = Readable                                                                                  | bit                                                                       | W = Writable                             | bit             | U = Unimple    | mented bit, read | as '0'           |              |  |  |

| u = Bit is unch                                                                               | anged                                                                     | x = Bit is unk                           | nown            | -n/n = Value   | at POR and BOP   | R/Value at all o | other Resets |  |  |

| '1' = Bit is set                                                                              |                                                                           | '0' = Bit is cle                         | ared            |                |                  |                  |              |  |  |

| bit 7                                                                                         | MDEN: Modu                                                                | ılator Module E                          | nable bit       |                |                  |                  |              |  |  |

|                                                                                               |                                                                           | or module is en<br>or module is dis      |                 | • • •          | als              |                  |              |  |  |

| bit 6                                                                                         | MDOE: Modu                                                                | ulator Module F                          | Pin Output Ena  | able bit       |                  |                  |              |  |  |

|                                                                                               | 1 = Modulato                                                              | or pin output enabled                    |                 |                |                  |                  |              |  |  |

|                                                                                               | 0 = Modulato                                                              | or pin output di                         | sabled          |                |                  |                  |              |  |  |

| bit 5                                                                                         | MDSLR: MD                                                                 | OUT Pin Slew                             | Rate Limiting   | bit            |                  |                  |              |  |  |

|                                                                                               |                                                                           | 1 = MDOUT pin slew rate limiting enabled |                 |                |                  |                  |              |  |  |

|                                                                                               | 0 = MDOUT                                                                 | pin slew rate li                         | miting disable  | d              |                  |                  |              |  |  |

| bit 4                                                                                         | MDOPOL: M                                                                 | odulator Outpu                           | t Polarity Sele | ect bit        |                  |                  |              |  |  |

|                                                                                               |                                                                           | 1 = Modulator output signal is inverted  |                 |                |                  |                  |              |  |  |

| 0 = Modulator output signal is not inverted                                                   |                                                                           |                                          |                 |                |                  |                  |              |  |  |

| bit 3                                                                                         |                                                                           |                                          |                 |                |                  |                  |              |  |  |

|                                                                                               | Displays the current output value of the Modulator module. <sup>(1)</sup> |                                          |                 |                |                  |                  |              |  |  |

| bit 2-1                                                                                       | Unimplemented: Read as '0'                                                |                                          |                 |                |                  |                  |              |  |  |

| bit 0 MDBIT: Allows software to manually set modulation source input to module <sup>(2)</sup> |                                                                           |                                          |                 |                |                  |                  |              |  |  |

| Note 1: The                                                                                   | e modulated ou                                                            | tput frequency                           | can be greate   | er and asynchr | onous from the c | lock that upda   | ates this    |  |  |

#### REGISTER 23-1: MDCON: MODULATION CONTROL REGISTER

register bit, the bit value may not be valid for higher speed modulator or carrier signals.

2: MDBIT must be selected as the modulation source in the MDSRC register for this operation.

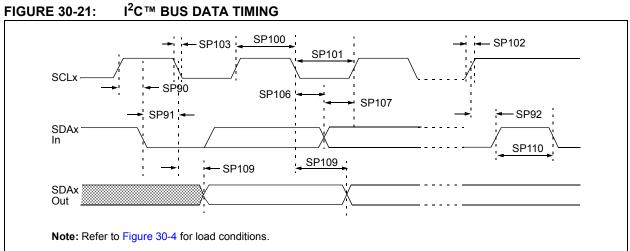

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

#### 25.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of Clock Stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 25.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

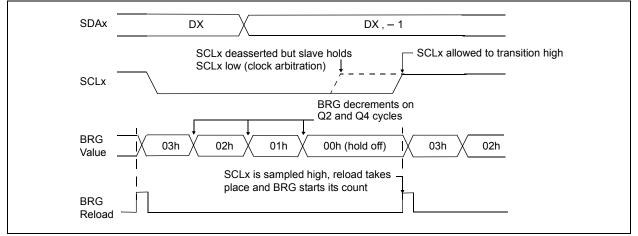

#### 25.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 25-25).

#### 25.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not Idle.

| Note: | Because queueing of events is not          |

|-------|--------------------------------------------|

|       | allowed, writing to the lower five bits of |

|       | SSPxCON2 is disabled until the Start       |

|       | condition is complete.                     |

#### 26.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 26-3 contains the formulas for determining the baud rate. Example 26-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 26-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

#### EXAMPLE 26-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPBRGH:SPBRGL:

| $X = \frac{FOSC}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $=\frac{\frac{16000000}{9600}}{64}-1$                                   |

| = [25.042] = 25                                                         |

| Calculated Baud Rate = $\frac{16000000}{64(25+1)}$                      |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

#### 26.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 26.4.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.4.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

### TABLE 26-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6   | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-------------------------------|---------|--------|--------|---------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL                       | SDO1SEL | SS1SEL | P2BSEL | CCP2SEL | P1DSEL | P1CSEL | CCP1SEL | 118                 |

| APFCON1 | _                             | _       | _      | _      | _       | _      | _      | TXCKSEL | 118                 |

| BAUDCON | ABDOVF                        | RCIDL   | —      | SCKP   | BRG16   | _      | WUE    | ABDEN   | 298                 |

| INTCON  | GIE                           | PEIE    | TMR0IE | INTE   | IOCE    | TMR0IF | INTF   | IOCF    | 88                  |

| PIE1    | TMR1GIE                       | ADIE    | RCIE   | TXIE   | SSP1IE  | CCP1IE | TMR2IE | TMR1IE  | 89                  |

| PIR1    | TMR1GIF                       | ADIF    | RCIF   | TXIF   | SSP1IF  | CCP1IF | TMR2IF | TMR1IF  | 93                  |

| RCSTA   | SPEN                          | RX9     | SREN   | CREN   | ADDEN   | FERR   | OERR   | RX9D    | 297                 |

| TRISB   | TRISB7                        | TRISB6  | TRISB5 | TRISB4 | TRISB3  | TRISB2 | TRISB1 | TRISB0  | 126                 |

| TXREG   | EUSART Transmit Data Register |         |        |        |         |        | 289*   |         |                     |

| TXSTA   | CSRC                          | TX9     | TXEN   | SYNC   | SENDB   | BRGH   | TRMT   | TX9D    | 296                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Transmission. \* Page provides register information.

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                      |

| Operands:        | $0 \le k \le 255$                                                                                             |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| TRIS                           | Load TRIS Register with W                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                        | [ <i>label</i> ] TRIS f                                                                                         | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |

| Operands:                      | $5 \le f \le 7$                                                                                                 | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |