#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1847-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

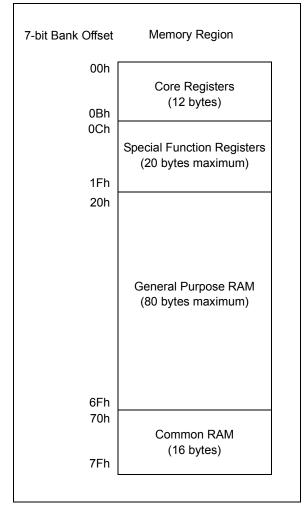

#### 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

#### 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

#### 3.3.4 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-2.

#### TABLE 3-2: MEMORY MAP TABLES

| Device        | Banks | Table No. |

|---------------|-------|-----------|

| PIC16(L)F1847 | 0-7   | Table 3-3 |

|               | 8-15  | Table 3-4 |

|               | 16-23 | Table 3-5 |

|               | 24-31 | Table 3-6 |

|               | 31    | Table 3-7 |

| Address             | Name     | Bit 7                           | Bit 6         | Bit 5             | Bit 4             | Bit 3        | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------------------|----------|---------------------------------|---------------|-------------------|-------------------|--------------|-------------|--------|--------|----------------------|---------------------------------|

| Bank 5              |          |                                 |               |                   |                   |              |             |        | -      |                      |                                 |

| 280h <sup>(1)</sup> | INDF0    | Addressing th<br>(not a physica |               | es contents of    | FSR0H/FSR0        | L to address | data memory | /      |        | XXXX XXXX            | XXXX XXXX                       |

| 281h <sup>(1)</sup> | INDF1    | Addressing th<br>(not a physica |               | es contents of    | FSR1H/FSR1        | L to address | data memory | /      |        | XXXX XXXX            | XXXX XXXX                       |

| 282h <sup>(1)</sup> | PCL      | Program Cou                     | nter (PC) Lea | ast Significant I | Byte              |              |             |        |        | 0000 0000            | 0000 0000                       |

| 283h <sup>(1)</sup> | STATUS   | _                               | _             | _                 | TO                | PD           | Z           | DC     | С      | 1 1000               | q quuu                          |

| 284h <sup>(1)</sup> | FSR0L    | Indirect Data                   | Memory Addr   | ress 0 Low Poi    | inter             |              |             |        |        | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(1)</sup> | FSR0H    | Indirect Data                   | Memory Addr   | ress 0 High Po    | inter             |              |             |        |        | 0000 0000            | 0000 0000                       |

| 286h <sup>(1)</sup> | FSR1L    | Indirect Data                   | Memory Addr   | ress 1 Low Poi    | inter             |              |             |        |        | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(1)</sup> | FSR1H    | Indirect Data                   | Memory Addr   | ress 1 High Po    | inter             |              |             |        |        | 0000 0000            | 0000 0000                       |

| 288h <sup>(1)</sup> | BSR      | —                               | _             | _                 |                   |              | BSR<4:0>    |        |        | 0 0000               | 0 0000                          |

| 289h <sup>(1)</sup> | WREG     | Working Reg                     | ster          |                   |                   |              |             |        |        | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1)</sup> | PCLATH   | _                               | Write Buffer  | for the upper 7   | ' bits of the Pro | gram Counte  | er          |        |        | -000 0000            | -000 0000                       |

| 28Bh <sup>(1)</sup> | INTCON   | GIE                             | PEIE          | TMR0IE            | INTE              | IOCE         | TMR0IF      | INTF   | IOCF   | 0000 000x            | 0000 000u                       |

| 28Ch                |          | Unimplemented                   |               |                   |                   |              |             |        |        | _                    | _                               |

| 28Dh                |          | Unimplemented                   |               |                   |                   |              |             |        | _      | _                    |                                 |

| 28Eh                | _        | Unimplemented                   |               |                   |                   |              |             |        | _      | _                    |                                 |

| 28Fh                | _        | Unimplement                     | ed            |                   |                   |              |             |        |        | _                    | _                               |

| 290h                | _        | Unimplement                     | ed            |                   |                   |              |             |        |        | _                    | _                               |

| 291h                | CCPR1L   | Capture/Com                     | pare/PWM Re   | egister 1 (LSB)   | )                 |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |

| 292h                | CCPR1H   | Capture/Com                     | pare/PWM Re   | egister 1 (MSB    | 3)                |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |

| 293h                | CCP1CON  | P1M                             | <1:0>         | DC1E              | 3<1:0>            |              | CCP1N       | /<3:0> |        | 0000 0000            | 0000 0000                       |

| 294h                | PWM1CON  | P1RSEN                          |               |                   | Р                 | 1DC<6:0>     |             |        |        | 0000 0000            | 0000 0000                       |

| 295h                | CCP1AS   | CCP1ASE                         |               | CCP1AS<2:0        | >                 | PSS1A        | C<1:0>      | PSS1B  | D<1:0> | 0000 0000            | 0000 0000                       |

| 296h                | PSTR1CON | _                               | _             | _                 | STR1SYNC          | STR1D        | STR1C       | STR1B  | STR1A  | 0 0001               | 0 0001                          |

| 297h                | _        | Unimplement                     | ed            |                   |                   |              |             |        |        | _                    | _                               |

| 298h                | CCPR2L   | Capture/Com                     | pare/PWM Re   | egister 2 (LSB)   | )                 |              |             |        |        | XXXX XXXX            | սսսս սսսս                       |

| 299h                | CCPR2H   | Capture/Com                     | pare/PWM Re   | egister 2 (MSB    | 3)                |              |             |        |        | XXXX XXXX            | սսսս սսսս                       |

| 29Ah                | CCP2CON  | P2M•                            | <1:0>         | DC2E              | 3<1:0>            |              | CCP2N       | /<3:0> |        | 0000 0000            | 0000 0000                       |

| 29Bh                | PWM2CON  | P2RSEN                          |               |                   | Р                 | 2DC<6:0>     |             |        |        | 0000 0000            | 0000 0000                       |

| 29Ch                | CCP2AS   | CCP2ASE                         |               | CCP2AS<2:0        | >                 | PSS2A        | C<1:0>      | PSS2B  | D<1:0> | 0000 0000            | 0000 0000                       |

| 29Dh                | PSTR2CON | _                               | _             | _                 | STR2SYNC          | STR2D        | STR2C       | STR2B  | STR2A  | 0 0001               | 0 0001                          |

| 29Eh                | CCPTMRS  | C4TSE                           | L<1:0>        | C3TSE             | L<1:0>            | C2TSE        | L<1:0>      | C1TSE  | L<1:0> | 0000 0000            | 0000 0000                       |

| 29Fh                |          | Unimplemented                   |               |                   |                   |              |             |        |        |                      | 1                               |

#### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

| R/W-0/0          | R/W-0/0                      | R/W-0/0                    | R/W-0/0        | R/W-0/0        | U-0              | U-0            | R/W-0/0      |

|------------------|------------------------------|----------------------------|----------------|----------------|------------------|----------------|--------------|

| OSFIE            | C2IE                         | C1IE                       | EEIE           | BCL1IE         | —                | _              | CCP2IE       |

| bit 7            |                              |                            |                |                |                  |                | bit 0        |

|                  |                              |                            |                |                |                  |                |              |

| Legend:          |                              |                            |                |                |                  |                |              |

| R = Readable     |                              | W = Writable               |                |                | mented bit, read |                |              |

| u = Bit is uncl  | 0                            | x = Bit is unk             |                | -n/n = Value a | at POR and BOF   | R/Value at all | other Resets |

| '1' = Bit is set |                              | '0' = Bit is cle           | ared           |                |                  |                |              |

| bit 7            |                              | llator Fail Interr         | unt Enable bit |                |                  |                |              |

|                  |                              | the Oscillator F           | •              |                |                  |                |              |

|                  |                              | the Oscillator             | •              |                |                  |                |              |

| bit 6            | C2IE: Compa                  | arator C2 Interr           | upt Enable bit |                |                  |                |              |

|                  |                              | the Comparato              |                |                |                  |                |              |

|                  | 0 = Disables                 | the Comparate              | or C2 interrup | t              |                  |                |              |

| bit 5            | •                            | arator C1 Interr           | •              |                |                  |                |              |

|                  |                              | the Comparato              |                |                |                  |                |              |

| h:+ 4            |                              | the Comparate              | •              |                |                  |                |              |

| bit 4            |                              | OM Write Com<br>the EEPROM |                | •              |                  |                |              |

|                  |                              | the EEPROM                 |                |                |                  |                |              |

| bit 3            |                              | SP1 Bus Collis             |                | •              |                  |                |              |

|                  |                              | the MSSP1 Bu               |                |                |                  |                |              |

|                  |                              | the MSSP1 B                |                |                |                  |                |              |

| bit 2-1          | Unimplemer                   | nted: Read as '            | 0'             |                |                  |                |              |

| bit 0            | CCP2IE: CC                   | P2 Interrupt En            | able bit       |                |                  |                |              |

|                  |                              | the CCP2 inter             |                |                |                  |                |              |

|                  | 0 = Disables                 | the CCP2 inte              | rrupt          |                |                  |                |              |

|                  |                              |                            |                |                |                  |                |              |

|                  | PEIE of the IN to enable any |                            |                |                |                  |                |              |

#### **PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 REGISTER 8-3:**

set to enable any peripheral interrupt.

| R/W-x/u                           | R/W-x/u | U-0                                | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u | R/W-x/u |

|-----------------------------------|---------|------------------------------------|---------|--------------|------------------|---------|---------|

| LATA7                             | LATA6   | —                                  | LATA4   | LATA3        | LATA2            | LATA1   | LATA0   |

| bit 7                             | •       |                                    |         |              |                  |         | bit 0   |

|                                   |         |                                    |         |              |                  |         |         |

| Legend:                           |         |                                    |         |              |                  |         |         |

| R = Readable bit W = Writable bit |         | U = Unimplemented bit, read as '0' |         |              |                  |         |         |

| R = Readable                      | bit     | VV = VVritable                     | bit     | U = Unimplen | nented bit, read | as '0'  |         |

#### REGISTER 12-5: LATA: PORTA DATA LATCH REGISTER

| bit 7-6 | LATA<7:6>: RA<7:6> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

| bit 5   | Unimplemented: Read as '0'                                |

'1' = Bit is set

bit 4-0 LATA<4:0>: RA<4:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-6: WPUA: WEAK PULL-UP PORTA REGISTER

'0' = Bit is cleared

| U-0   | U-0 | R/W-1/1 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|---------|-----|-----|-----|-----|-------|

| —     | —   | WPUA5   | —   | —   | —   | —   | —     |

| bit 7 |     |         |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 5   | WPUA5: Weak Pull-up RA5 Control bit                     |

|         | If MCLRE in Configuration Words = 0, MCLR is disabled): |

|         | 1 = Weak Pull-up enabled <sup>(1)</sup>                 |

|         | 0 = Weak Pull-up disabled                               |

|         | If MCLRE in Configuration Words = 1, MCLR is enabled):  |

|         | Weak Pull-up is always enabled.                         |

| bit 4-0 | Unimplemented: Read as '0'                              |

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 16-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u                               | R/W-x/u                           | R/W-x/u            | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|---------------------------------------|-----------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| —                                     | —                                 | —                  | —       | _                                                     |         | ADRE    | S<9:8>  |  |

| bit 7                                 |                                   |                    |         |                                                       |         |         | bit 0   |  |

|                                       |                                   |                    |         |                                                       |         |         |         |  |

| Legend:                               |                                   |                    |         |                                                       |         |         |         |  |

| R = Readable                          | R = Readable bit W = Writable bit |                    | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unch                       | anged                             | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared |                                   |                    |         |                                                       |         |         |         |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper two bits of 10-bit conversion result

#### **REGISTER 16-6:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u     | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------------|------------|---------|---------|---------|---------|---------|---------|--|

|             | ADRES<7:0> |         |         |         |         |         |         |  |

| bit 7 bit 0 |            |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

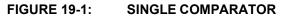

### 19.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- Programmable Speed/Power optimization

- · PWM shutdown

- Programmable and Fixed Voltage Reference

#### **19.1** Comparator Overview

A single comparator is shown in Figure 19-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |  |  |  |  |  |  |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|--|--|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |  |  |  |  |  |  |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |  |  |  |  |  |  |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |  |  |  |  |  |  |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |  |  |  |  |  |  |

#### **EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES** TABLE 24-9

**Note 1:** PWM Steering enables outputs in Single mode.

#### EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH FIGURE 24-6: STATE)

| PxM<1:0>               | Signal        | 0 ◀ Pulse<br>Width | PRX+1             |

|------------------------|---------------|--------------------|-------------------|

|                        |               |                    | ── Period ──►     |

| 00 (Single Output)     | PxA Modulated | <br>'Delay         | Delay             |

|                        | PxA Modulated |                    |                   |

| 10 (Half-Bridge)       | PxB Modulated |                    |                   |

|                        | PxA Active    | _ <u>'</u><br>_ '  |                   |

| (Full-Bridge,          | PxB Inactive  | _                  |                   |

| <sup>01</sup> Forward) | PxC Inactive  |                    |                   |

|                        | PxD Modulated |                    |                   |

|                        | PxA Inactive  | :                  | 1 i<br>1 1<br>1 1 |

| (Full-Bridge,          | PxB Modulated |                    |                   |

| Reverse)               | PxC Active —  |                    |                   |

|                        | PxD Inactive  | _                  |                   |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

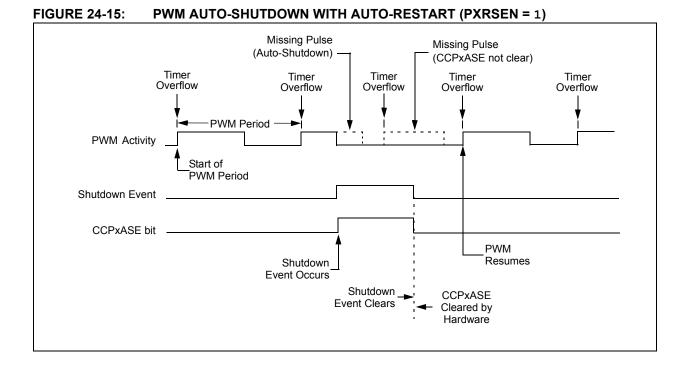

#### 24.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register. If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

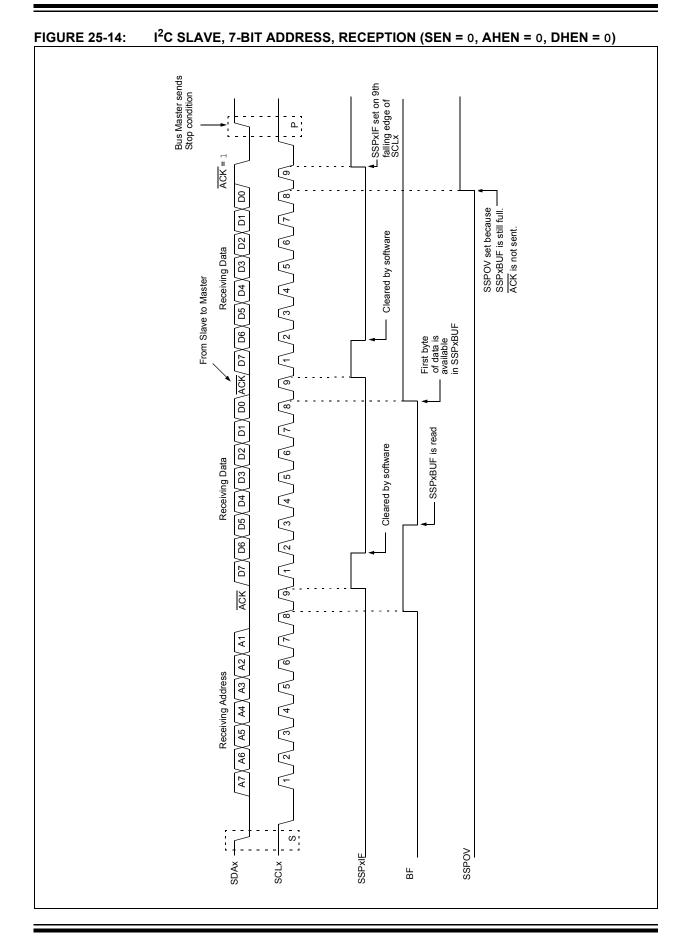

#### 25.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 25-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

| R/W-0/0                                                                   | R-0/0                            | R/W-0/0                                                                                                              | R/S/HS-0/0                                                                           | R/S/HS-0/0                    | R/S/HS-0/0        | R/S/HS-0/0       | R/W/HS-0/0   |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------|-------------------|------------------|--------------|--|--|--|--|

| GCEN                                                                      | ACKSTAT                          | ACKDT                                                                                                                | ACKEN                                                                                | RCEN                          | PEN               | RSEN             | SEN          |  |  |  |  |

| bit 7                                                                     | ·                                |                                                                                                                      |                                                                                      |                               |                   |                  | bit 0        |  |  |  |  |

|                                                                           |                                  |                                                                                                                      |                                                                                      |                               |                   |                  |              |  |  |  |  |

| Legend:                                                                   |                                  |                                                                                                                      |                                                                                      |                               |                   |                  |              |  |  |  |  |

| R = Readable                                                              | e bit                            | W = Writable                                                                                                         | bit                                                                                  | U = Unimpler                  | mented bit, read  | 1 as '0'         |              |  |  |  |  |

| u = Bit is unc                                                            | hanged                           | x = Bit is unk                                                                                                       | nown                                                                                 | -n/n = Value a                | at POR and BO     | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared HC = Cleared by hardware S = User s |                                  |                                                                                                                      |                                                                                      |                               |                   | S = User set     |              |  |  |  |  |

|                                                                           |                                  |                                                                                                                      |                                                                                      |                               |                   |                  |              |  |  |  |  |

| bit 7                                                                     |                                  | eral Call Enable                                                                                                     |                                                                                      | .,                            |                   |                  |              |  |  |  |  |

|                                                                           |                                  | terrupt when a<br>call address dis                                                                                   | •                                                                                    | ddress (0x00 d                | or 00h) is receiv | ed in the SSP    | SR           |  |  |  |  |

| bit 6                                                                     | ACKSTAT: A                       | cknowledge St                                                                                                        | atus bit (in I <sup>2</sup> C                                                        | mode only)                    |                   |                  |              |  |  |  |  |

|                                                                           |                                  | edge was not r                                                                                                       |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           |                                  | edge was recei                                                                                                       |                                                                                      |                               |                   |                  |              |  |  |  |  |

| bit 5                                                                     |                                  | nowledge Data                                                                                                        | bit (in I <sup>2</sup> C mo                                                          | de only)                      |                   |                  |              |  |  |  |  |

|                                                                           | In Receive m                     |                                                                                                                      |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           | 1 = Not Ackn                     |                                                                                                                      | ed when the user initiates an Acknowledge sequence at the end of a receive<br>vledge |                               |                   |                  |              |  |  |  |  |

|                                                                           | 0 = Acknowle                     | •                                                                                                                    |                                                                                      |                               |                   |                  |              |  |  |  |  |

| bit 4                                                                     | ACKEN: Ack                       | nowledge Seq                                                                                                         | uence Enable                                                                         | bit (in I <sup>2</sup> C Mas  | ter mode only)    |                  |              |  |  |  |  |

|                                                                           | In Master Re                     | n Master Receive mode:                                                                                               |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           |                                  | Initiate Acknowledge sequence on SDAx and SCLx pins, and transmit ACKDT data bit. Automatically cleared by hardware. |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           |                                  | edge sequence                                                                                                        |                                                                                      |                               |                   |                  |              |  |  |  |  |

| bit 3                                                                     | RCEN: Recei                      | ive Enable bit                                                                                                       | (in I <sup>2</sup> C Master                                                          | mode only)                    |                   |                  |              |  |  |  |  |

|                                                                           | 1 = Enables I<br>0 = Receive i   | Receive mode                                                                                                         | for I <sup>2</sup> C                                                                 |                               |                   |                  |              |  |  |  |  |

| bit 2                                                                     | PEN: Stop Co                     | ondition Enable                                                                                                      | e bit (in I <sup>2</sup> C Ma                                                        | ster mode only                | y)                |                  |              |  |  |  |  |

|                                                                           | SCKx Releas                      | e Control:                                                                                                           |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           | 1 = Initiate St<br>0 = Stop cond |                                                                                                                      | n SDAx and S                                                                         | CLx pins. Auto                | matically cleare  | ed by hardware   |              |  |  |  |  |

| bit 1                                                                     | RSEN: Repe                       | ated Start Con                                                                                                       | dition Enable b                                                                      | oit (in I <sup>2</sup> C Mast | er mode only)     |                  |              |  |  |  |  |

|                                                                           |                                  | epeated Start<br>d Start conditio                                                                                    |                                                                                      | DAx and SCL>                  | c pins. Automati  | cally cleared b  | y hardware.  |  |  |  |  |

| bit 0                                                                     | -                                | ondition Enable                                                                                                      |                                                                                      | le hit                        |                   |                  |              |  |  |  |  |

|                                                                           | In Master mo                     |                                                                                                                      |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           |                                  | art condition o                                                                                                      | n SDAx and S                                                                         | CLx pins. Auto                | matically cleare  | ed by hardware   |              |  |  |  |  |

|                                                                           | In Slave mod                     | <u>e:</u>                                                                                                            |                                                                                      |                               |                   |                  |              |  |  |  |  |

|                                                                           |                                  | etching is enat<br>etching is disal                                                                                  |                                                                                      | ave transmit ar               | nd slave receive  | e (stretch enabl | ed)          |  |  |  |  |

| Note 1: Fo                                                                | or bits ACKEN, F                 | RCEN, PEN. R                                                                                                         | SEN, SEN: If t                                                                       | he I <sup>2</sup> C module    | is not in the IdI | e mode, this bi  | t may not be |  |  |  |  |

#### **REGISTER 25-3:** SSPxCON2: SSPx CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

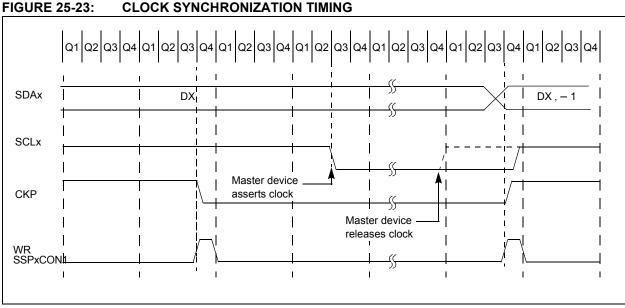

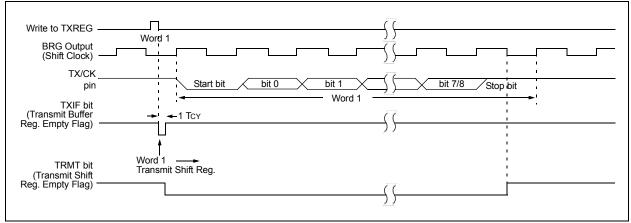

#### 26.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 26.1.1.5 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the 9th, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 26.1.2.7** "Address **Detection**" for more information on the address mode.

#### 26.1.1.6 Asynchronous Transmission Setup:

- 1. Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set 9th data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 6. If 9-bit transmission is selected, the 9th bit should be loaded into the TX9D data bit.

- 7. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 26-3: ASYNCHRONOUS TRANSMISSION

### TABLE 26-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name     | Bit 7    | Bit 6   | Bit 5  | Bit 4       | Bit 3          | Bit 2  | Bit 1  | Bit 0        | Register<br>on Page |

|----------|----------|---------|--------|-------------|----------------|--------|--------|--------------|---------------------|

| APFCON0  | RXDTSEL  | SDO1SEL | SS1SEL | P2BSEL      | CCP2SEL        | P1DSEL | P1CSEL | CCP1SEL      | 118                 |

| APFCON1  | _        | —       | -      | —           | —              | —      | _      | TXCKSEL      | 118                 |

| BAUDCON  | ABDOVF   | RCIDL   | _      | SCKP        | BRG16          | —      | WUE    | ABDEN        | 298                 |

| INTCON   | GIE      | PEIE    | TMR0IE | INTE        | IOCE           | TMR0IF | INTF   | IOCF         | 88                  |

| PIE1     | TMR1GIE  | ADIE    | RCIE   | TXIE        | SSP1IE         | CCP1IE | TMR2IE | TMR1IE       | 89                  |

| PIR1     | TMR1GIF  | ADIF    | RCIF   | TXIF        | SSP1IF         | CCP1IF | TMR2IF | TMR1IF       | 93                  |

| RCSTA    | SPEN     | RX9     | SREN   | CREN        | ADDEN          | FERR   | OERR   | RX9D         | 297                 |

| SPBRGL   | BRG<7:0> |         |        |             |                |        |        |              | 299*                |

| SPBRGH   |          |         |        | BRG         | <15:8>         |        |        |              | 299*                |

| TRISB    | TRISB7   | TRISB6  | TRISB5 | TRISB4      | TRISB3         | TRISB2 | TRISB1 | TRISB0       | 126                 |

| TXREG    |          |         | EU     | SART Transr | nit Data Regis | ster   |        |              | 289*                |

| TXSTA    | CSRC     | TX9     | TXEN   | SYNC        | SENDB          | BRGH   | TRMT   | TX9D         | 296                 |

| Lawawali |          |         |        | 0           |                |        |        | <b>-</b> · · | _                   |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

\* Page provides register information.

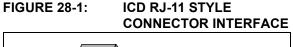

#### 28.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16193X/PIC16LF193X Memory Programming Specification*" (DS41360A).

#### 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.4 "MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 28.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 28-1.

| PIC16LF       | 1847            | Standard Operating Conditions (unless otherwise stated) |                                         |      |       |            |                                    |  |  |

|---------------|-----------------|---------------------------------------------------------|-----------------------------------------|------|-------|------------|------------------------------------|--|--|

| PIC16F18      | 847             |                                                         |                                         |      |       |            |                                    |  |  |

| Param. Device |                 | Min.                                                    | Тур†                                    | Max. | Units | Conditions |                                    |  |  |

| No.           | Characteristics |                                                         | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |       | VDD        | Note                               |  |  |

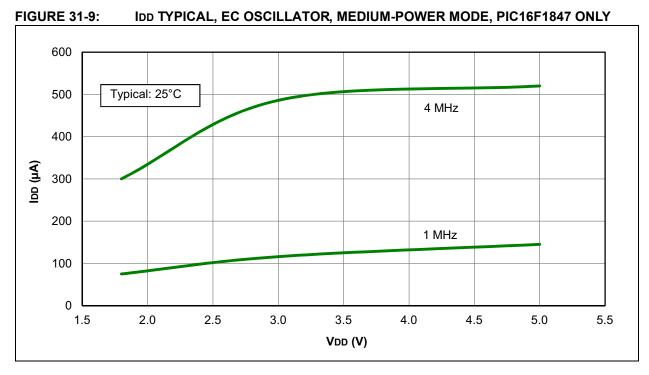

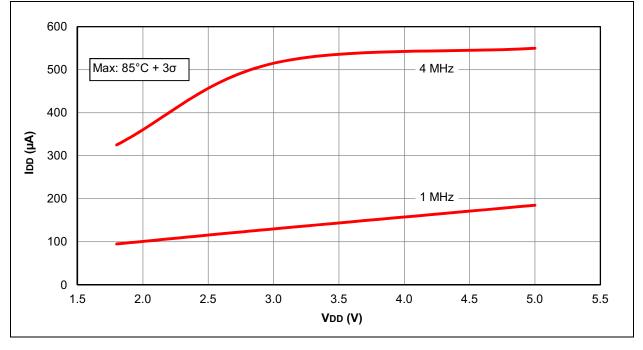

| D014          |                 | _                                                       | 260                                     | 338  | μΑ    | 1.8        | Fosc = 4 MHz                       |  |  |

|               |                 | —                                                       | 415                                     | 540  | μA    | 3.0        | EC Oscillator<br>Medium-power mode |  |  |

| D014          |                 | —                                                       | 300                                     | 325  | μA    | 1.8        | Fosc = 4 MHz                       |  |  |

|               |                 | —                                                       | 486                                     | 515  | μA    | 3.0        | EC Oscillator<br>Medium-power mode |  |  |

|               |                 | _                                                       | 520                                     | 550  | μA    | 5.0        |                                    |  |  |

| D015          |                 | _                                                       | 10                                      | 16   | μA    | 1.8        | Fosc = 32 kHz                      |  |  |

|               |                 | —                                                       | 12                                      | 18   | μA    | 3.0        | LFINTOSC                           |  |  |

| D015          |                 | —                                                       | 21                                      | 28   | μA    | 1.8        | Fosc = 32 kHz                      |  |  |

|               |                 | _                                                       | 25                                      | 34   | μA    | 3.0        | LFINTOSC                           |  |  |

|               |                 | —                                                       | 28                                      | 36   | μA    | 5.0        |                                    |  |  |

| D016          |                 | —                                                       | 175                                     | 215  | μΑ    | 1.8        | Fosc = 500 kHz                     |  |  |

|               |                 | —                                                       | 216                                     | 245  | μA    | 3.0        | MFINTOSC                           |  |  |

| D016          |                 | _                                                       | 175                                     | 200  | μA    | 1.8        | Fosc = 500 kHz                     |  |  |

|               |                 | _                                                       | 195                                     | 225  | μA    | 3.0        | MFINTOSC                           |  |  |

|               |                 | —                                                       | 215                                     | 245  | μA    | 5.0        |                                    |  |  |

| D017          |                 | _                                                       | 0.80                                    | 1.10 | mA    | 1.8        | Fosc = 8 MHz                       |  |  |

|               |                 | —                                                       | 1.36                                    | 1.80 | mA    | 3.0        | HFINTOSC                           |  |  |

| D017          |                 |                                                         | 0.80                                    | 1.10 | mA    | 1.8        | Fosc = 8 MHz                       |  |  |

|               |                 | _                                                       | 1.40                                    | 1.60 | mA    | 3.0        | HFINTOSC                           |  |  |

|               |                 | _                                                       | 1.55                                    | 1.80 | mA    | 5.0        |                                    |  |  |

| D018          |                 |                                                         | 1.20                                    | 1.60 | mA    | 1.8        | Fosc = 16 MHz                      |  |  |

|               |                 |                                                         | 2.10                                    | 2.90 | mA    | 3.0        | HFINTOSC                           |  |  |

| D018          |                 |                                                         | 1.20                                    | 1.60 | mA    | 1.8        | Fosc = 16 MHz                      |  |  |

|               |                 |                                                         | 2.20                                    | 2.30 | mA    | 3.0        | HFINTOSC                           |  |  |

|               |                 | —                                                       | 2.30                                    | 2.60 | mA    | 5.0        |                                    |  |  |

| D019          |                 |                                                         | 3.40                                    | 3.60 | mA    | 3.0        | Fosc = 32 MHz                      |  |  |

|               |                 |                                                         | 4.10                                    | 4.20 | mA    | 3.6        | HFINTOSC (Note 3)                  |  |  |

| TABLE 30-2: SUF | PLY CURRENT (IDD | ) <sup>(1,2)</sup> (CONTINUED) |

|-----------------|------------------|--------------------------------|

|-----------------|------------------|--------------------------------|

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- **2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: 8 MHz internal oscillator with 4x PLL enabled.

- **4:** 8 MHz crystal oscillator with 4x PLL enabled.

- 5: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

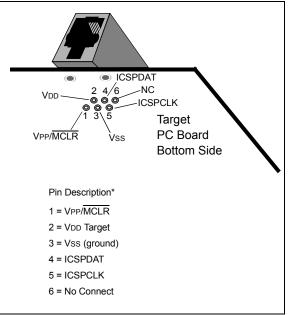

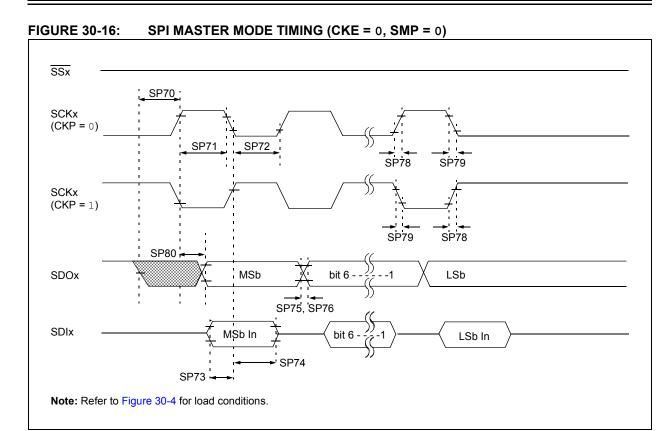

#### FIGURE 30-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

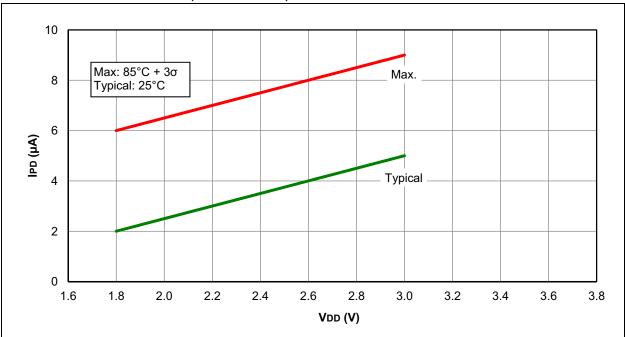

FIGURE 31-31: IPD, CAPACITIVE SENSING (CPS) MODULE, LOW-CURRENT RANGE, CPSRM = 0, CPSRNG = 01, PIC16LF1847 ONLY

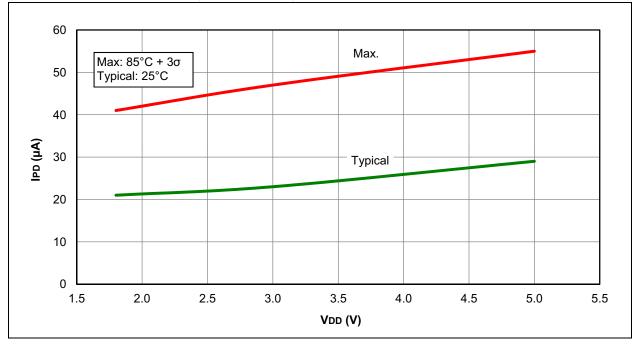

FIGURE 31-32: IPD, CAPACITIVE SENSING (CPS) MODULE, LOW-CURRENT RANGE, CPSRM = 0, CPSRNG = 01, PIC16F1847 ONLY

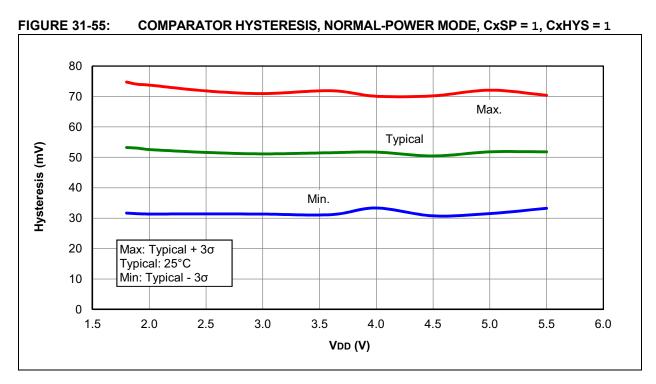

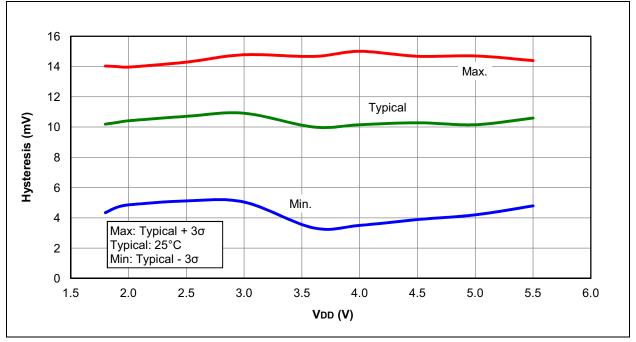

FIGURE 31-56: COMPARATOR HYSTERESIS, LOW-POWER MODE, CxSP = 0, CxHYS = 1

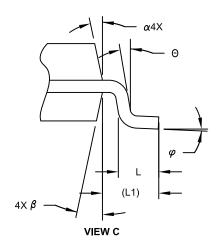

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |          |      |

|--------------------------|-------------|-----------|----------|------|

| Dimension Li             | nits        | MIN       | NOM      | MAX  |

| Number of Pins           | N           |           | 18       |      |

| Pitch                    | е           |           | 1.27 BSC |      |

| Overall Height           | A           | -         | -        | 2.65 |

| Molded Package Thickness | A2          | 2.05      | -        | -    |

| Standoff §               | A1          | 0.10      | -        | 0.30 |

| Overall Width            | E           | 10.30 BSC |          |      |

| Molded Package Width     | E1          | 7.50 BSC  |          |      |

| Overall Length           | D           | 11.55 BSC |          |      |

| Chamfer (Optional)       | h           | 0.25      | -        | 0.75 |

| Foot Length              | L           | 0.40      | -        | 1.27 |

| Footprint                | L1          |           | 1.40 REF |      |

| Lead Angle               | Θ           | 0°        | -        | -    |

| Foot Angle               | φ           | 0°        | -        | 8°   |

| Lead Thickness           | С           | 0.20      | -        | 0.33 |

| Lead Width               | b           | 0.31      | _        | 0.51 |

| Mold Draft Angle Top     | α           | 5°        | -        | 15°  |

| Mold Draft Angle Bottom  | β           | 5°        | -        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2