Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                                           |                                                                          |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

| Product Status                                    | Active                                                                   |  |  |  |

| Core Processor                                    | PIC                                                                      |  |  |  |

| Core Size                                         | 8-Bit                                                                    |  |  |  |

| Speed                                             | 32MHz                                                                    |  |  |  |

| Connectivity                                      | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |  |  |  |

| Peripherals Brown-out Detect/Reset, POR, PWM, WDT |                                                                          |  |  |  |

| Number of I/O                                     | 15                                                                       |  |  |  |

| Program Memory Size                               | 14KB (8K x 14)                                                           |  |  |  |

| Program Memory Type                               | FLASH                                                                    |  |  |  |

| EEPROM Size                                       | 256 x 8                                                                  |  |  |  |

| RAM Size                                          | 1K x 8                                                                   |  |  |  |

| Voltage - Supply (Vcc/Vdd)                        | 1.8V ~ 5.5V                                                              |  |  |  |

| Data Converters                                   | A/D 12x10b                                                               |  |  |  |

| Oscillator Type                                   | Internal                                                                 |  |  |  |

| Operating Temperature                             | -40°C ~ 125°C (TA)                                                       |  |  |  |

| Mounting Type Through Hole                        |                                                                          |  |  |  |

| Package / Case 18-DIP (0.300", 7.62mm)            |                                                                          |  |  |  |

| Supplier Device Package                           | 18-PDIP                                                                  |  |  |  |

| Purchase URL                                      | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1847-e-p |  |  |  |

DS40001453E-page 25

TABLE 3-6: PIC16(L)F1847 MEMORY MAP, BANKS 24-31

|                | BANK 24                      |        | BANK 25                      |       | BANK 26                      |        | BANK 27                      |       | BANK 28                      |      | BANK 29                      |      | BANK 30                      |      | BANK 31                            |

|----------------|------------------------------|--------|------------------------------|-------|------------------------------|--------|------------------------------|-------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------------|

| C00h           | INDF0                        | C80h   | INDF0                        | D00h  | INDF0                        | D80h   | INDF0                        | E00h  | INDF0                        | E80h | INDF0                        | F00h | INDF0                        | F80h | INDF0                              |

| C01h           | INDF1                        | C81h   | INDF1                        | D01h  | INDF1                        | D81h   | INDF1                        | E01h  | INDF1                        | E81h | INDF1                        | F01h | INDF1                        | F81h | INDF1                              |

| C02h           | PCL                          | C82h   | PCL                          | D02h  | PCL                          | D82h   | PCL                          | E02h  | PCL                          | E82h | PCL                          | F02h | PCL                          | F82h | PCL                                |

| C03h           | STATUS                       | C83h   | STATUS                       | D03h  | STATUS                       | D83h   | STATUS                       | E03h  | STATUS                       | E83h | STATUS                       | F03h | STATUS                       | F83h | STATUS                             |

| C04h           | FSR0L                        | C84h   | FSR0L                        | D04h  | FSR0L                        | D84h   | FSR0L                        | E04h  | FSR0L                        | E84h | FSR0L                        | F04h | FSR0L                        | F84h | FSR0L                              |

| C05h           | FSR0H                        | C85h   | FSR0H                        | D05h  | FSR0H                        | D85h   | FSR0H                        | E05h  | FSR0H                        | E85h | FSR0H                        | F05h | FSR0H                        | F85h | FSR0H                              |

| C06h           | FSR1L                        | C86h   | FSR1L                        | D06h  | FSR1L                        | D86h   | FSR1L                        | E06h  | FSR1L                        | E86h | FSR1L                        | F06h | FSR1L                        | F86h | FSR1L                              |

| C07h           | FSR1H                        | C87h   | FSR1H                        | D07h  | FSR1H                        | D87h   | FSR1H                        | E07h  | FSR1H                        | E87h | FSR1H                        | F07h | FSR1H                        | F87h | FSR1H                              |

| C08h           | BSR                          | C88h   | BSR                          | D08h  | BSR                          | D88h   | BSR                          | E08h  | BSR                          | E88h | BSR                          | F08h | BSR                          | F88h | BSR                                |

| C09h           | WREG                         | C89h   | WREG                         | D09h  | WREG                         | D89h   | WREG                         | E09h  | WREG                         | E89h | WREG                         | F09h | WREG                         | F89h | WREG                               |

| C0Ah           | PCLATH                       | C8Ah   | PCLATH                       | D0Ah  | PCLATH                       | D8Ah   | PCLATH                       | E0Ah  | PCLATH                       | E8Ah | PCLATH                       | F0Ah | PCLATH                       | F8Ah | PCLATH                             |

| C0Bh           | INTCON                       | C8Bh   | INTCON                       | D0Bh  | INTCON                       | D8Bh   | INTCON                       | E0Bh  | INTCON                       | E8Bh | INTCON                       | F0Bh | INTCON                       | F8Bh | INTCON                             |

| C0Ch           | _                            | C8Ch   | _                            | D0Ch  | _                            | D8Ch   | _                            | E0Ch  | 1                            | E8Ch | 1                            | F0Ch | 1                            | F8Ch | _                                  |

| C0Dh           | _                            | C8Dh   | _                            | D0Dh  | _                            | D8Dh   | _                            | E0Dh  | _                            | E8Dh | _                            | F0Dh | _                            | F8Dh | _                                  |

| C0Eh           | _                            | C8Eh   | _                            | D0Eh  | _                            | D8Eh   | _                            | E0Eh  |                              | E8Eh |                              | F0Eh |                              | F8Eh | _                                  |

| C0Fh           | _                            | C8Fh   | _                            | D0Fh  | _                            | D8Fh   | _                            | E0Fh  | 1                            | E8Fh |                              | F0Fh |                              | F8Fh | _                                  |

| C10h           | _                            | C90h   | _                            | D10h  | _                            | D90h   | _                            | E10h  | 1                            | E90h |                              | F10h |                              | F90h | _                                  |

| C11h           | _                            | C91h   | _                            | D11h  | _                            | D91h   | _                            | E11h  | 1                            | E91h |                              | F11h |                              | F91h | _                                  |

| C12h           | _                            | C92h   | _                            | D12h  | _                            | D92h   | _                            | E12h  | 1                            | E92h | 1                            | F12h | 1                            | F92h | _                                  |

| C13h           | _                            | C93h   | _                            | D13h  | _                            | D93h   | _                            | E13h  | _                            | E93h | _                            | F13h | _                            | F93h | _                                  |

| C14h           | _                            | C94h   |                              | D14h  |                              | D94h   | _                            | E14h  | _                            | E94h | _                            | F14h | _                            | F94h | _                                  |

| C15h           | _                            | C95h   | _                            | D15h  | _                            | D95h   | _                            | E15h  | _                            | E95h | _                            | F15h | _                            | F95h | _                                  |

| C16h           | _                            | C96h   | _                            | D16h  | _                            | D96h   | _                            | E16h  | 1                            | E96h |                              | F16h |                              | F96h | _                                  |

| C17h           | _                            | C97h   | _                            | D17h  | _                            | D97h   | _                            | E17h  | _                            | E97h | _                            | F17h | _                            | F97h | _                                  |

| C18h           | _                            | C98h   |                              | D18h  |                              | D98h   | _                            | E18h  | _                            | E98h | _                            | F18h | _                            | F98h | _                                  |

| C19h           | _                            | C99h   |                              | D19h  |                              | D99h   | _                            | E19h  | _                            | E99h | _                            | F19h | _                            | F99h | _                                  |

| C1Ah           | _                            | C9Ah   |                              | D1Ah  |                              | D9Ah   | _                            | E1Ah  | _                            | E9Ah | _                            | F1Ah | _                            | F9Ah | _                                  |

| C1Bh           | _                            | C9Bh   |                              | D1Bh  |                              | D9Bh   | _                            | E1Bh  | _                            | E9Bh | _                            | F1Bh | _                            | F9Bh | _                                  |

| C1Ch           | _                            | C9Ch   | _                            | D1Ch  | _                            | D9Ch   | _                            | E1Ch  | _                            | E9Ch | _                            | F1Ch | _                            | F9Ch | _                                  |

| C1Dh           | _                            | C9Dh   | _                            | D1Dh  | _                            | D9Dh   | _                            | E1Dh  | 1                            | E9Dh |                              | F1Dh |                              | F9Dh | _                                  |

| C1Eh           | _                            | C9Eh   | _                            | D1Eh  | _                            | D9Eh   | _                            | E1Eh  | _                            | E9Eh | _                            | F1Eh | _                            | F9Eh | _                                  |

| C1Fh           | _                            | C9Fh   | _                            | D1Fh  | _                            | D9Fh   | _                            | E1Fh  | _                            | E9Fh | _                            | F1Fh | _                            | F9Fh | _                                  |

| C20h           |                              | CA0h   |                              | D20h  |                              | DA0h   |                              | E20h  |                              | EA0h |                              | F20h |                              | FA0h |                                    |

|                | Unimplemented<br>Read as '0' |        | Unimplemented<br>Read as '0' |       | Unimplemented<br>Read as '0' |        | Unimplemented<br>Read as '0' |       | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | See Table 3-7 for more information |

| C6Fh           |                              | CEFh   |                              | D6Fh  |                              | DEFh   |                              | E6Fh  |                              | EEFh |                              | F6Fh |                              | FEFh |                                    |

| C70h           |                              | CF0h   |                              | D70h  |                              | DF0h   |                              | E70h  |                              | EF0h |                              | F70h |                              | FF0h |                                    |

| 0.011          | Accesses                     | 31 011 | Accesses                     | 3,011 | Accesses                     | 5. 011 | Accesses                     | 2.011 | Accesses                     | 011  | Accesses                     |      | Accesses                     |      | Accesses                           |

|                | 70h – 7Fh                    |        | 70h – 7Fh                    |       | 70h – 7Fh                    |        | 70h – 7Fh                    |       | 70h – 7Fh                    |      | 70h – 7Fh                    |      | 70h – 7Fh                    |      | 70h – 7Fh                          |

| CFFh           |                              | CFFh   |                              | D7Fh  |                              | DFFh   |                              | E7Fh  |                              | EFFh |                              | F7Fh |                              | FFFh |                                    |

| ٠ <sub>[</sub> |                              | L      |                              |       |                              |        |                              |       |                              |      |                              | 1    |                              |      |                                    |

**Legend:** = Unimplemented data memory locations, read as '0'.

**TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)**

| INDLL               | 00. 0                                                                                  | LOIALI                         |                | INECIOI          | -IX OCIVIIVI    | AIT! (00     | // / / / / / / / / / / / / / / / / / / | <u> </u> |        |                      |                                 |

|---------------------|----------------------------------------------------------------------------------------|--------------------------------|----------------|------------------|-----------------|--------------|----------------------------------------|----------|--------|----------------------|---------------------------------|

| Address             | Name                                                                                   | Bit 7                          | Bit 6          | Bit 5            | Bit 4           | Bit 3        | Bit 2                                  | Bit 1    | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank 5              | Bank 5                                                                                 |                                |                |                  |                 |              |                                        |          |        |                      |                                 |

| 280h <sup>(1)</sup> | INDF0                                                                                  | Addressing the (not a physical |                | es contents of   | FSR0H/FSR0      | L to address | data memory                            | 1        |        | xxxx xxxx            | xxxx xxxx                       |

| 281h <sup>(1)</sup> | INDF1                                                                                  | Addressing the (not a physical |                | es contents of   | FSR1H/FSR1      | L to address | data memory                            | 1        |        | xxxx xxxx            | xxxx xxxx                       |

| 282h <sup>(1)</sup> | PCL                                                                                    | Program Cou                    | inter (PC) Lea | st Significant E | Byte            |              |                                        |          |        | 0000 0000            | 0000 0000                       |

| 283h <sup>(1)</sup> | STATUS                                                                                 | _                              | _              | _                | TO              | PD           | Z                                      | DC       | С      | 1 1000               | q quuu                          |

| 284h <sup>(1)</sup> | FSR0L                                                                                  | Indirect Data                  | Memory Addr    | ess 0 Low Poi    | nter            |              |                                        |          |        | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(1)</sup> | FSR0H                                                                                  | Indirect Data                  | Memory Addr    | ess 0 High Po    | inter           |              |                                        |          |        | 0000 0000            | 0000 0000                       |

| 286h <sup>(1)</sup> | FSR1L                                                                                  | Indirect Data                  | Memory Addr    | ess 1 Low Poi    | nter            |              |                                        |          |        | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(1)</sup> | FSR1H                                                                                  | Indirect Data                  | Memory Addr    | ess 1 High Po    | inter           |              |                                        |          |        | 0000 0000            | 0000 0000                       |

| 288h <sup>(1)</sup> | BSR                                                                                    | _                              | _              | _                |                 |              | BSR<4:0>                               |          |        | 0 0000               | 0 0000                          |

| 289h <sup>(1)</sup> | WREG                                                                                   | Working Reg                    | ister          |                  |                 |              |                                        |          |        | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1)</sup> | PCLATH                                                                                 | _                              | Write Buffer f | or the upper 7   | bits of the Pro | gram Counte  | er                                     |          |        | -000 0000            | -000 0000                       |

| 28Bh <sup>(1)</sup> | INTCON                                                                                 | GIE                            | PEIE           | TMR0IE           | INTE            | IOCE         | TMR0IF                                 | INTF     | IOCF   | 0000 000x            | 0000 000u                       |

| 28Ch                | _                                                                                      | Unimplement                    | ed             | ·                |                 |              |                                        | ·        | ·      | _                    | _                               |

| 28Dh                | _                                                                                      | Unimplement                    | Unimplemented  |                  |                 |              |                                        |          |        |                      | _                               |

| 28Eh                | _                                                                                      | Unimplement                    | ed             |                  |                 |              |                                        |          |        | _                    | _                               |

| 28Fh                | _                                                                                      | Unimplement                    | ed             |                  |                 |              |                                        |          |        | _                    | _                               |

| 290h                | _                                                                                      | Unimplement                    | ed             |                  |                 |              |                                        |          |        | _                    | _                               |

| 291h                | CCPR1L                                                                                 | Capture/Com                    | pare/PWM Re    | egister 1 (LSB)  | )               |              |                                        |          |        | xxxx xxxx            | uuuu uuuu                       |

| 292h                | CCPR1H                                                                                 | Capture/Com                    | pare/PWM Re    | egister 1 (MSB   | 5)              |              |                                        |          |        | xxxx xxxx            | uuuu uuuu                       |

| 293h                | CCP1CON                                                                                | P1M·                           | <1:0>          | DC1B             | I<1:0>          |              | CCP1N                                  | /<3:0>   |        | 0000 0000            | 0000 0000                       |

| 294h                | PWM1CON                                                                                | P1RSEN                         |                | •                | Р               | 1DC<6:0>     |                                        |          |        | 0000 0000            | 0000 0000                       |

| 295h                | CCP1AS                                                                                 | CCP1ASE                        |                | CCP1AS<2:0>      | >               | PSS1A        | C<1:0>                                 | PSS1B    | D<1:0> | 0000 0000            | 0000 0000                       |

| 296h                | PSTR1CON                                                                               | _                              | _              | _                | STR1SYNC        | STR1D        | STR1C                                  | STR1B    | STR1A  | 0 0001               | 0 0001                          |

| 297h                | _                                                                                      | Unimplement                    | ed             |                  |                 |              | •                                      |          | •      | _                    | _                               |

| 298h                | CCPR2L                                                                                 | Capture/Com                    | pare/PWM Re    | egister 2 (LSB)  |                 |              |                                        |          |        | xxxx xxxx            | uuuu uuuu                       |

| 299h                | CCPR2H                                                                                 | Capture/Com                    | pare/PWM Re    | egister 2 (MSB   | )               |              |                                        |          |        | xxxx xxxx            | uuuu uuuu                       |

| 29Ah                | CCP2CON                                                                                | P2M·                           | <1:0>          | DC2B             | I<1:0>          |              | CCP2N                                  | /<3:0>   |        | 0000 0000            | 0000 0000                       |

| 29Bh                | PWM2CON                                                                                | P2RSEN                         |                | P2DC<6:0>        |                 |              |                                        |          |        | 0000 0000            | 0000 0000                       |

| 29Ch                | CCP2AS                                                                                 | CCP2ASE                        |                | CCP2AS<2:0>      | >               | PSS2A        | C<1:0>                                 | PSS2B    | D<1:0> | 0000 0000            | 0000 0000                       |

| 29Dh                | PSTR2CON                                                                               | _                              | _              | _                | STR2SYNC        | STR2D        | STR2C                                  | STR2B    | STR2A  | 0 0001               | 0 0001                          |

| 29Eh                | CCPTMRS                                                                                | C4TSE                          | L<1:0>         | C3TSE            | L<1:0>          | C2TSE        | L<1:0>                                 | C1TSE    | L<1:0> | 0000 0000            | 0000 0000                       |

| 29Fh                | _                                                                                      | Unimplement                    | ed             |                  |                 |              |                                        |          |        | _                    | _                               |

| I edend:            | y = unknown y = unchanged or = value depends on condition = unimplemented y = reserved |                                |                |                  |                 |              |                                        |          |        |                      |                                 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

1: These registers can be addressed from any bank.

Unimplemented, read as '1'. 2:

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

| R/P-1  | R/P-1 | U-1 | R/P-1 | R/P-1  | R/P-1 |

|--------|-------|-----|-------|--------|-------|

| LVP    | DEBUG |     | BORV  | STVREN | PLLEN |

| bit 13 |       |     |       |        | bit 8 |

| U-1   | U-1 | U-1 | R-1      | U-1 | U-1 | R/P-1 | R/P-1 |

|-------|-----|-----|----------|-----|-----|-------|-------|

| _     | _   | _   | Reserved | _   | _   | WRT   | <1:0> |

| bit 7 |     |     |          |     |     |       | bit 0 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1'

'0' = Bit is cleared '1' = Bit is set -n = Value when blank or after Bulk Erase

bit 13 LVP: Low-Voltage Programming Enable bit<sup>(1)</sup>

1 = Low-voltage programming enabled

0 = High-voltage on MCLR must be used for programming

bit 12 **DEBUG:** In-Circuit Debugger Mode bit<sup>(2)</sup>

1 = In-Circuit Debugger disabled, ICSPCLK and ICSPDAT are general purpose I/O pins

0 = In-Circuit Debugger enabled, ICSPCLK and ICSPDAT are dedicated to the debugger

bit 11 **Unimplemented:** Read as '1'

bit 10 **BORV:** Brown-out Reset Voltage Selection bit<sup>(3)</sup>

1 = Brown-out Reset voltage (Vbor), low trip point selected.

0 = Brown-out Reset voltage (Vbor), high trip point selected.

bit 9 STVREN: Stack Overflow/Underflow Reset Enable bit

1 = Stack Overflow or Underflow will cause a Reset

0 = Stack Overflow or Underflow will not cause a Reset

bit 8 PLLEN: PLL Enable bit

1 = 4xPLL enabled 0 = 4xPLL disabled

U = 4XPLL disabled

bit 7-5 **Unimplemented:** Read as '1'

bit 4 **Reserved:** This location should be programmed to a '1'.

bit 3-2 **Unimplemented:** Read as '1'

bit 1-0 WRT<1:0>: Flash Memory Self-Write Protection bits

11 = Write protection off

10 = 000h to 1FFh write-protected, 200h to 1FFFh may be modified by EECON control

01 = 000h to FFFh write-protected, 1000h to 1FFFh may be modified by EECON control

00 = 000h to 1FFFh write-protected, no addresses may be modified by EECON control

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

**3:** See Vbor parameter for specific trip point voltages.

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| R-1/q  | R-0/q | R-q/q | R-0/q  | R-0/q  | R-q/q  | R-0/0  | R-0/q  |

|--------|-------|-------|--------|--------|--------|--------|--------|

| T10SCR | PLLR  | OSTS  | HFIOFR | HFIOFL | MFIOFR | LFIOFR | HFIOFS |

| bit 7  |       |       |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Conditional

bit 7 T10SCR: Timer1 Oscillator Ready bit

<u>If T10SCEN = 1</u>:

1 = Timer1 oscillator is ready

0 = Timer1 oscillator is not ready

If T1OSCEN = 0:

1 = Timer1 clock source is always ready

bit 6 PLLR 4x PLL Ready bit

1 = 4x PLL is ready

0 = 4x PLL is not ready

bit 5 Oscillator Start-up Time-out Status bit

1 = Running from the clock defined by the FOSC<2:0> bits of the Configuration Words

0 = Running from an internal oscillator (FOSC<2:0> = 100)

bit 4 HFIOFR: High Frequency Internal Oscillator Ready bit

1 = HFINTOSC is ready

0 = HFINTOSC is not ready

bit 3 **HFIOFL:** High Frequency Internal Oscillator Locked bit

1 = HFINTOSC is at least 2% accurate

0 = HFINTOSC is not 2% accurate

bit 2 MFIOFR: Medium Frequency Internal Oscillator Ready bit

1 = MFINTOSC is ready

0 = MFINTOSC is not ready

bit 1 LFIOFR: Low Frequency Internal Oscillator Ready bit

1 = LFINTOSC is ready

0 = LFINTOSC is not ready

bit 0 **HFIOFS:** High Frequency Internal Oscillator Stable bit

1 = HFINTOSC is at least 0.5% accurate

0 = HFINTOSC is not 0.5% accurate

#### 7.4 MCLR

The MCLR is an optional external input that can reset the device. The MCLR function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 7-2).

TABLE 7-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| X     | 1   | Enabled  |

#### 7.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

| Note: | A Reset does not drive the $\overline{\text{MCLR}}$ pin low. |

|-------|--------------------------------------------------------------|

|-------|--------------------------------------------------------------|

#### 7.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See Section 12.3 "PORTA Registers" for more information.

## 7.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the WDT Reset. See **Section 10.0** "Watchdog Timer" for more information.

#### 7.6 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{\text{RI}}$  bit in the PCON register will be set to '0'. See Table 7-4 for default conditions after a RESET instruction has occurred.

#### 7.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See Section 3.5.2 "Overflow/Underflow Reset" for more information.

#### 7.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

#### 7.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overline{\text{PWRTE}}$  bit of Configuration Words.

#### 7.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- Power-up Timer runs to completion (if enabled).

- Oscillator start-up timer runs to completion (if required for oscillator source).

- MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution immediately (see Figure 7-4). This is useful for testing purposes or to synchronize more than one device operating in parallel.

### 11.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- Load the starting address of the row to be modified.

- Read the existing data from the row into a RAM image.

- Modify the RAM image to contain the new data to be written into program memory.

- Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

# 11.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-2.

When read access is initiated on an address outside the parameters listed in Table 11-2, the EEDATH:EEDATL register pair is cleared.

TABLE 11-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### **EXAMPLE 11-3: CONFIGURATION WORD AND DEVICE ID ACCESS**

```

* This code block will read 1 word of program memory at the memory address:

PROG ADDR LO (must be 00h-08h) data will be returned in the variables;

PROG DATA HI, PROG DATA LO

BANKSEL EEADRL

; Select correct Bank

MOVLW PROG ADDR LO

; Store LSB of address

MOVWF EEADRL

CLRF

EEADRH

; Clear MSB of address

EECON1, CFGS

BSF

; Select Configuration Space

INTCON, GIE

BCF

; Disable interrupts

EECON1, RD

; Initiate read

BSF

; Executed (See Figure 11-1)

NOP

NOP

; Ignored (See Figure 11-1)

INTCON, GIE

BSF

; Restore interrupts

MOVF

EEDATL, W

; Get LSB of word

PROG DATA LO

; Store in user location

MOVWF

MOVF

EEDATH, W

; Get MSB of word

MOVWF

PROG DATA HI

; Store in user location

```

## 11.6 Write/Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

#### **EXAMPLE 11-6: EEPROM WRITE/VERIFY**

```

BANKSEL EEDATL ;

MOVF EEDATL, W ;EEDATL not changed ;from previous write

BSF EECON1, RD ;YES, Read the ;value written

XORWF EEDATL, W ;

BTFSS STATUS, Z ;Is data the same

GOTO WRITE_ERR ;No, handle error ;Yes, continue

```

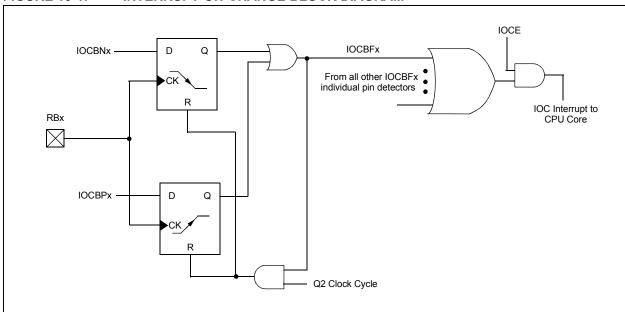

#### 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-on-change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- · Interrupt-on-change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

#### 13.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCE bit of the INTCON register must be set. If the IOCE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 13.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

#### 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the Interrupt-on-change pins of the port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCE bit is set. The IOCF bit of the INTCON register reflects the status of all IOCBFx bits.

#### 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### **EXAMPLE 13-1:**

| MOVLW | 0xff   |   |

|-------|--------|---|

| XORWF | IOCBF, | W |

| ANDWF | IOCBF, | F |

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

FIGURE 13-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM

NOTES:

NOTES:

#### 18.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- · Programmable input selection

- · SR latch output is available externally

- Separate Q and Q outputs

- · Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

### 18.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync C2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to Set or Reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 19.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source is available that can periodically Set or Reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to Set or Reset the SR latch, respectively.

#### 18.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to an I/O pin at the same time.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 18.3 Effects of a Reset

Upon any device Reset, the SR latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

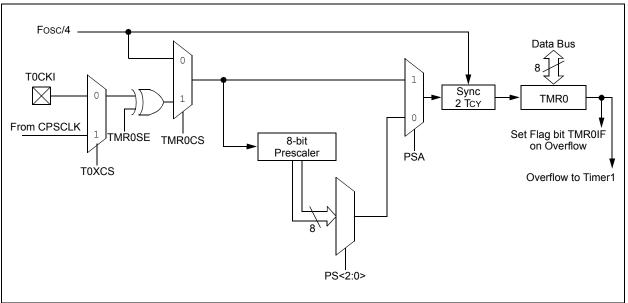

#### 20.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- · TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

#### 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-Bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when

TMR0 is written.

#### 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

#### FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

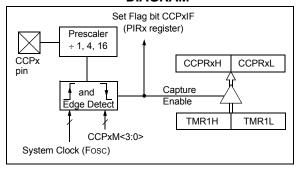

#### 24.1 **Capture Mode**

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, CCP3 and CCP4.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 24-1 shows a simplified diagram of the Capture operation.

#### 24.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON0 or APFCON1 register. Refer to Section 12.1 "Alternate Pin Function" for more details.

If the CCPx pin is configured as an output, Note:

a write to the port can cause a capture condition.

#### **FIGURE 24-1: CAPTURE MODE OPERATION BLOCK** DIAGRAM

#### 24.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### SOFTWARE INTERRUPT MODE 24.1.3

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 24.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 24-1 demonstrates the code to perform this function.

#### **EXAMPLE 24-1: CHANGING BETWEEN CAPTURE PRESCALERS**

| BANKSEL | CCPxCON     | ;Set Bank bits to point ;to CCPxCON                              |

|---------|-------------|------------------------------------------------------------------|

| CLRF    | CCPxCON     | ;Turn CCP module off                                             |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with                                             |

|         |             | ;the new prescaler                                               |

| MOVWF   | CCPxCON     | <pre>;move value and CCP ON ;Load CCPxCON with this ;value</pre> |

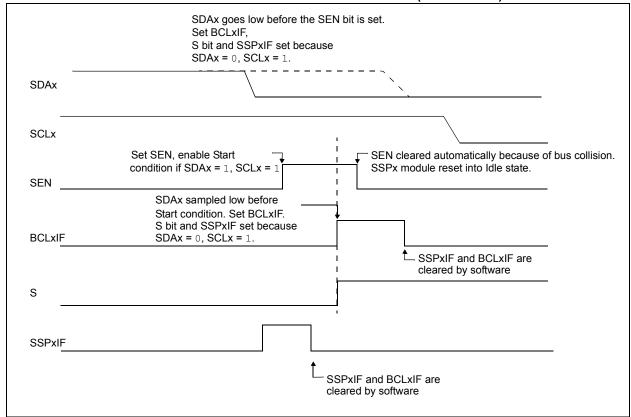

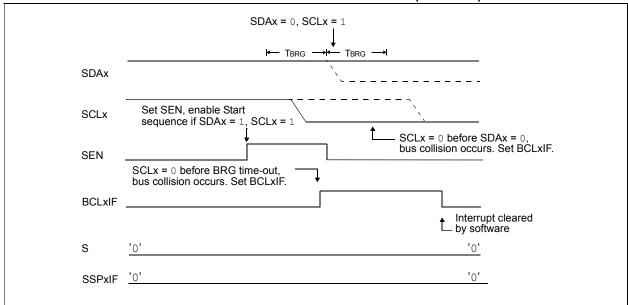

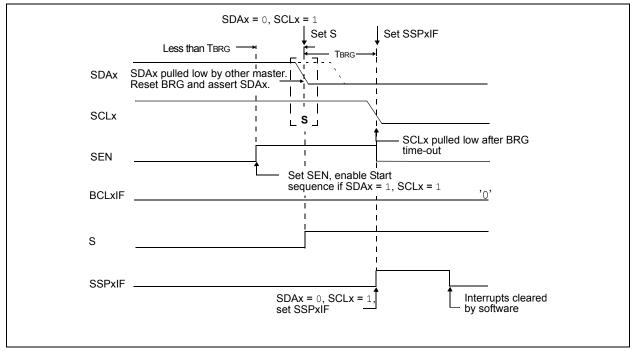

## 25.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx are sampled low at the beginning of the Start condition (Figure 25-33).

- SCLx is sampled low before SDAx is asserted low (Figure 25-34).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLxIF flag is set and

- the MSSPx module is reset to its Idle state (Figure 25-33).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 25-35). If, however, a '1' is sampled on the

SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note:

The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 25-33: BUS COLLISION DURING START CONDITION (SDAX ONLY)

### FIGURE 25-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

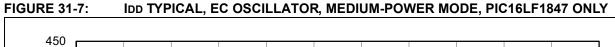

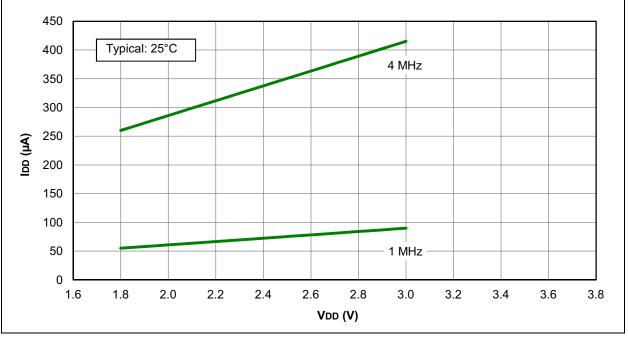

**FIGURE 31-8:** IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1847 ONLY

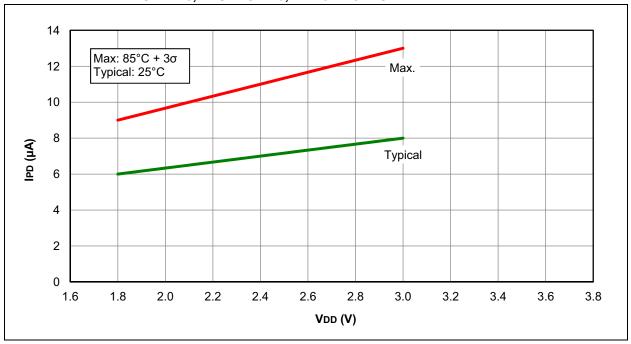

FIGURE 31-33: IPD, CAPACITIVE SENSING (CPS) MODULE, MEDIUM-CURRENT RANGE, CPSRM = 0, CPSRNG = 10, PIC16LF1847 ONLY

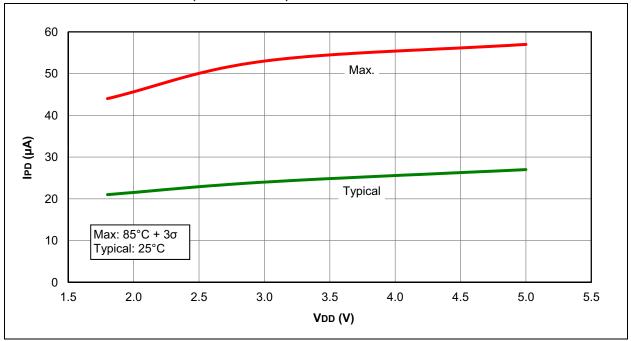

FIGURE 31-34: IPD, CAPACITIVE SENSING (CPS) MODULE, MEDIUM-CURRENT RANGE, CPSRM = 0, CPSRNG = 10, PIC16F1847 ONLY

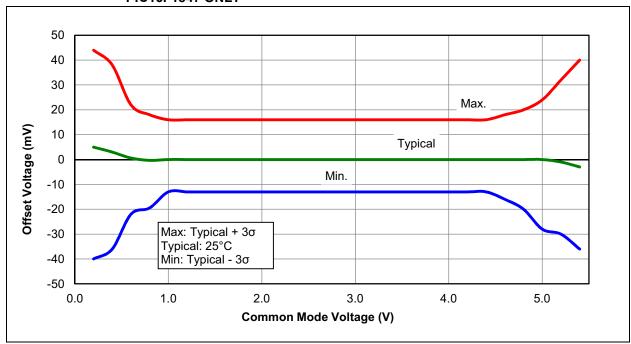

FIGURE 31-59: COMPARATOR INPUT OFFSET AT 25°C, NORMAL-POWER MODE, CxSP = 1, PIC16F1847 ONLY

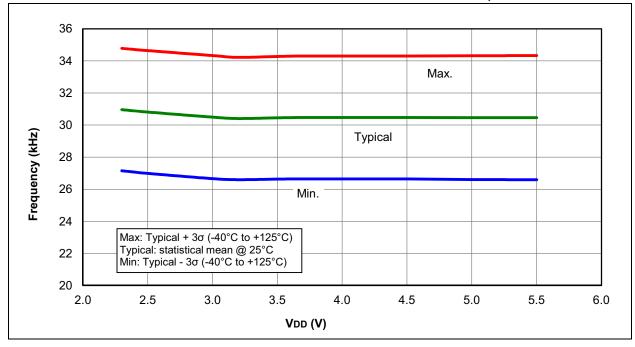

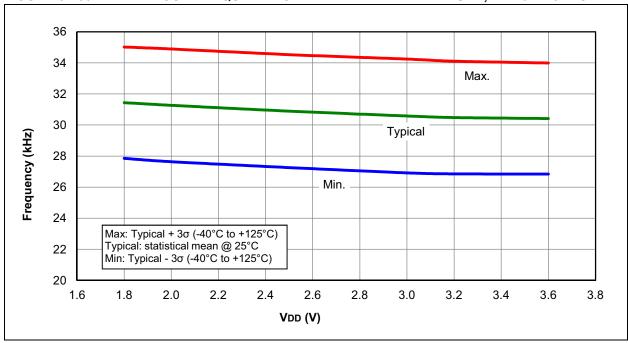

FIGURE 31-60: LFINTOSC FREQUENCY OVER VDD AND TEMPERATURE, PIC16LF1847 ONLY

FIGURE 31-61: LFINTOSC FREQUENCY OVER VDD AND TEMPERATURE, PIC16F1847 ONLY