Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 15                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

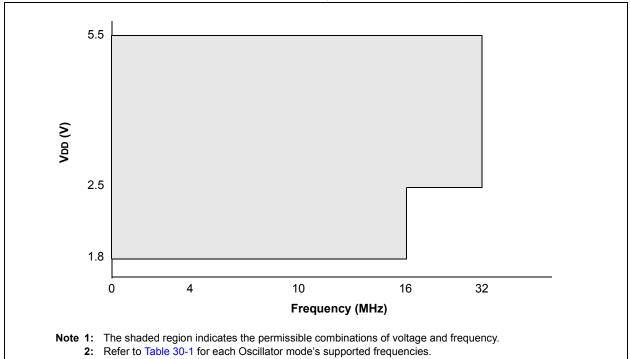

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1847t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

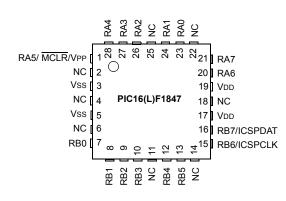

# Pin Diagram – 28-Pin QFN/UQFN

**Note 1:** See Table 1 for location of all peripheral functions.

2: It is recommended that the exposed bottom pad be connected to Vss.

# 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC16(L)F1847: Data Memory, Program Memory and Data EEPROM Memory<sup>(1)</sup>.

- Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Device Memory Maps

- Special Function Registers Summary

- Data EEPROM memory<sup>(1)</sup>

Note 1: The Data EEPROM Memory and the method to access Flash memory through the EECON registers is described in Section 11.0 "Data EEPROM and Flash Program Memory Control". The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a  $32K \times 14$  program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1847 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

## TABLE 3-1:DEVICE SIZES AND ADDRESSES

| Device        | Program Memory Space (Words) | Last Program Memory Address |  |

|---------------|------------------------------|-----------------------------|--|

| PIC16(L)F1847 | 8,192                        | 1FFFh                       |  |

# PIC16(L)F1847

# TABLE 3-7:PIC16(L)F1847 MEMORY MAP,<br/>BANK 31

|         |           | Bank 31                            |                      |

|---------|-----------|------------------------------------|----------------------|

|         | FA0h      | Builton                            |                      |

|         |           | Unimplemented<br>Read as '0'       |                      |

|         | FE3h      |                                    |                      |

|         | FE4h      | STATUS_SHAD                        |                      |

|         | FE5h      | WREG_SHAD                          |                      |

|         | FE6h      | BSR_SHAD                           |                      |

|         | FE7h      | PCLATH_SHAD                        |                      |

|         | FE8h      | FSR0L_SHAD                         |                      |

|         | FE9h      | FSR0H_SHAD                         |                      |

|         | FEAh      | FSR1L_SHAD                         |                      |

|         | FEBh      | FSR1H_SHAD                         |                      |

|         | FECh      | —                                  |                      |

|         | FEDh      | STKPTR                             |                      |

|         | FEEh      | TOSL                               |                      |

|         | FEFh TOSH |                                    |                      |

| Legend: |           | = Unimplemented da<br>read as '0'. | ta memory locations, |

# 3.3.5 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device        | Bank(s) | Page No. |

|---------------|---------|----------|

|               | 0       | 27       |

|               | 1       | 28       |

|               | 2       | 29       |

|               | 3       | 30       |

|               | 4       | 31       |

| PIC16(L)F1847 | 5       | 32       |

|               | 6       | 33       |

|               | 7       | 34       |

|               | 8       | 35       |

|               | 9-30    | 36       |

|               | 31      | 37       |

# 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

# 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

| Note: | The DEBUG bit in Configuration Word is      |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

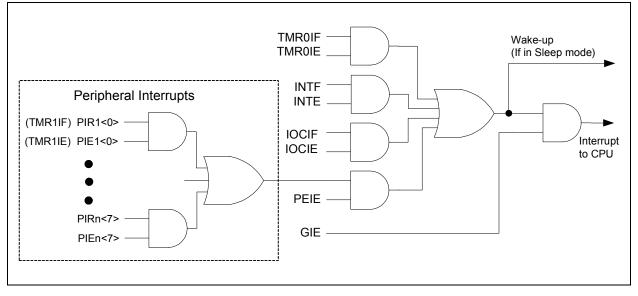

# 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce Interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 8-1.

### FIGURE 8-1: INTERRUPT LOGIC

| FIGURE 8  | 3-2: II       | NTERRUPT            | LATENCY           |                  |        |             |             |             |

|-----------|---------------|---------------------|-------------------|------------------|--------|-------------|-------------|-------------|

|           |               |                     |                   |                  |        |             |             |             |

|           |               |                     |                   |                  |        |             |             |             |

| OSC1      |               |                     |                   |                  |        |             |             |             |

| I         |               |                     |                   |                  |        |             |             |             |

|           |               |                     |                   |                  |        |             |             |             |

| CLKOUT    |               |                     | Interru<br>during | pt Sampled<br>Q1 |        |             |             |             |

| Interrupt |               |                     |                   |                  |        |             |             |             |

| GIE       |               |                     |                   |                  |        |             |             |             |

| 50        |               |                     | PC                |                  | 000.4h | 00055       | /           | /           |

| PC        | PC-1          | PC<br>Tuction at PC | /                 |                  | 0004h  | 0005h       | <u> </u>    | <u> </u>    |

| Execute   |               |                     | Inst(PC)          | NOP              | NOP    | Inst(0004h) |             |             |

|           |               |                     | /                 |                  |        |             |             |             |

| Interrupt |               |                     |                   |                  |        |             |             |             |

| GIE       |               |                     |                   |                  |        |             |             |             |

| PC        | PC-1          | PC                  | PC+1/FSR<br>ADDR  | New PC/<br>PC+1  | 0004h  | 0005h       |             |             |

| Execute-  | 2 Cycle Instr | ruction at PC       | Inst(PC)          | NOP              | NOP    | Inst(0004h) |             |             |

|           |               |                     |                   |                  |        |             |             |             |

| Interrupt |               |                     |                   |                  |        |             |             |             |

| GIE       |               |                     |                   |                  |        |             |             |             |

| PC        | PC-1          | PC                  | FSR ADDR          | PC+1             | PC+2   | 0004h       | 0005h       |             |

| Execute   | 3 Cycle Instr | uction at PC        | INST(PC)          | NOP              | NOP    | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt |               |                     |                   |                  | /      |             |             |             |

| GIE       |               |                     |                   |                  |        |             |             |             |

|           | []            | []                  | ·                 |                  |        |             |             |             |

| PC        | PC-1          | PC                  | FSR ADDR          | PC+1             |        | +2          | 0004h       | 0005h       |

| Execute   | 3 Cycle Instr | uction at PC        | INST(PC)          | NOP              | NOP    | NOP         | NOP         | Inst(0004h) |

|           |               |                     |                   |                  |        |             |             |             |

# 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |  |

|       | Refer to Section 16.2.6 "ADC Conver-     |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |

### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

## 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

## 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device        | CCPx |  |

|---------------|------|--|

| PIC16(L)F1847 | CCP4 |  |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 24.0** "Capture/Compare/PWM **Modules**" for more information.

| R/W-x/u          | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|--------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                    | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                    |         |                |                  |                | bit 0        |

|                  |         |                    |         |                |                  |                |              |

| Legend:          |         |                    |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable bi    | t       | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unknown |         | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clear | ed      |                |                  |                |              |

# **REGISTER 16-3:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

bit 7-0 **ADRES<9:2>:** ADC Result Register bits Upper eight bits of 10-bit conversion result

#### **REGISTER 16-4:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<1:0> |         | —       | —       | —       | —       | —       | —       |

| bit 7      |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result bit 5-0 Reserved: Do not use.

-----

# PIC16(L)F1847

| FIGURE 21-5:           | TIMER1 GATE SINGLE-PULS               | E MODE                                        |

|------------------------|---------------------------------------|-----------------------------------------------|

|                        |                                       |                                               |

| TMR1GE                 |                                       |                                               |

| T1GPOL                 |                                       |                                               |

| T1GSPM                 |                                       |                                               |

| T1GG <u>O/</u><br>DONE | ✓ Set by software Counting enabled on | Cleared by hardware on falling edge of T1GVAL |

| T1G_IN                 | rising edge of T1G                    |                                               |

| Т1СКІ                  |                                       |                                               |

| T1GVAL                 |                                       |                                               |

| Timer1                 | N N                                   | + 1 N + 2                                     |

| TMR1GIF                | Cleared by software                   | Set by hardware on falling edge of T1GVAL     |

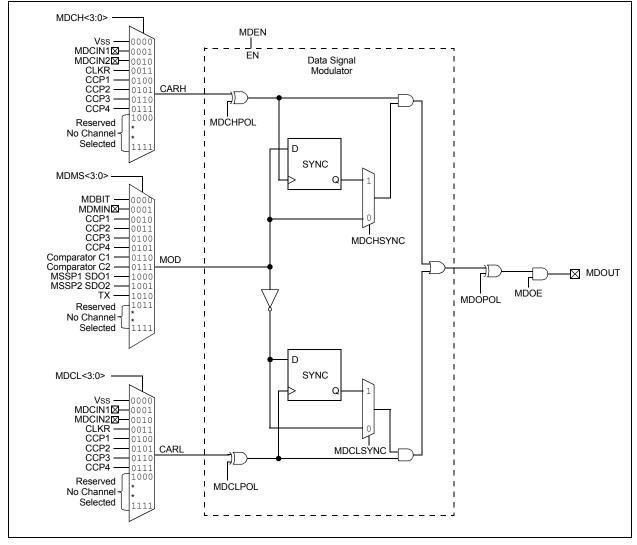

# 23.0 DATA SIGNAL MODULATOR

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal. Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- · Carrier Source Polarity Select

- Carrier Source Pin Disable

- Programmable Modulator Data

- Modulator Source Pin Disable

- Modulated Output Polarity Select

- Slew Rate Control

Figure 23-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

# 24.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two Enhanced Capture/Compare/PWM modules (ECCP1 and ECCP2,) and two standard Capture/Compare/PWM modules (CCP3 and CCP4).

The Capture and Compare functions are identical for all four CCP modules (ECCP1, ECCP2, CCP3 and CCP4). The only differences between CCP modules are in the Pulse-Width Modulation (PWM) function. The standard PWM function is identical in modules, CCP3 and CCP4. In CCP modules ECCP1 and ECCP2, the Enhanced PWM function has slight variations from one another. Full-Bridge ECCP modules have four available I/O pins while Half-Bridge ECCP modules only have two available I/O pins. See Table 24-1 for more information.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, CCP3 and CCP4. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

TABLE 24-1:PWM RESOURCES

| Device Name   | ECCP1                       | ECCP1 ECCP2                 |              | CCP4         |

|---------------|-----------------------------|-----------------------------|--------------|--------------|

| PIC16(L)F1847 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM | Standard PWM |

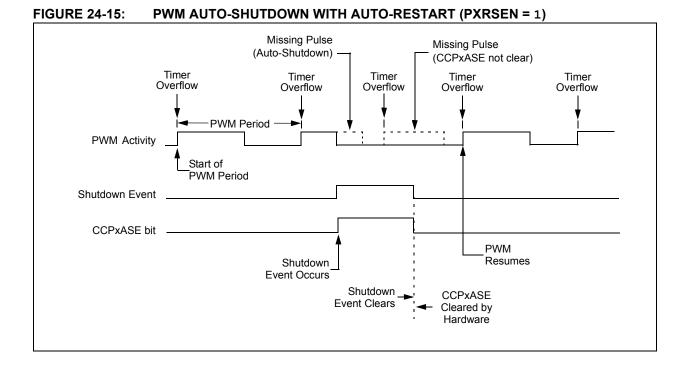

### 24.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register. If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

# PIC16(L)F1847

# 26.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 26-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the 9th data bit.

#### 26.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 26-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 26.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 26.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 26.1.1.3 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

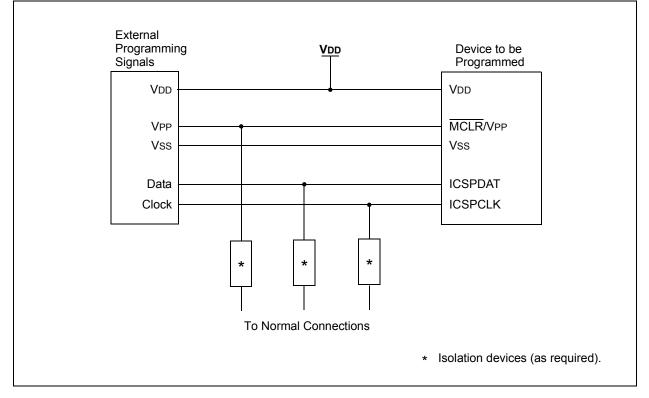

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-3 for more information.

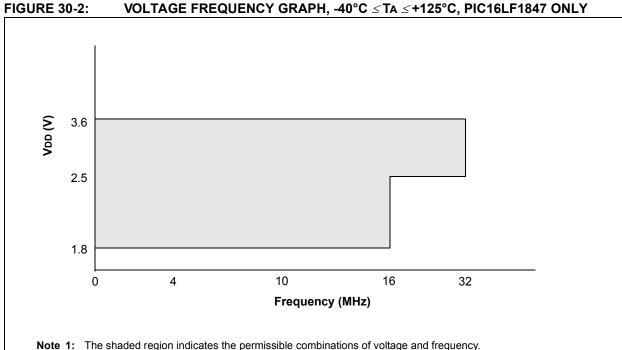

2: Refer to Table 30-1 for each oscillator mode's supported frequencies.

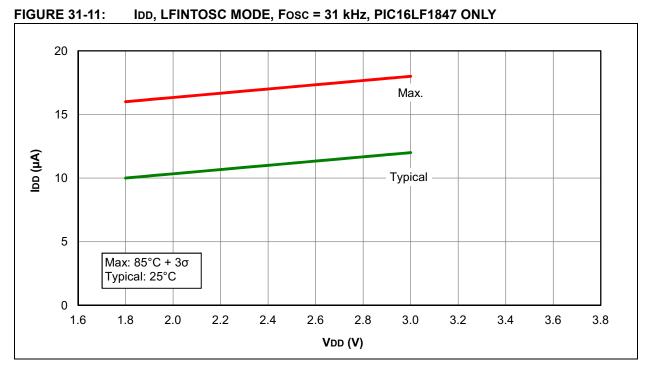

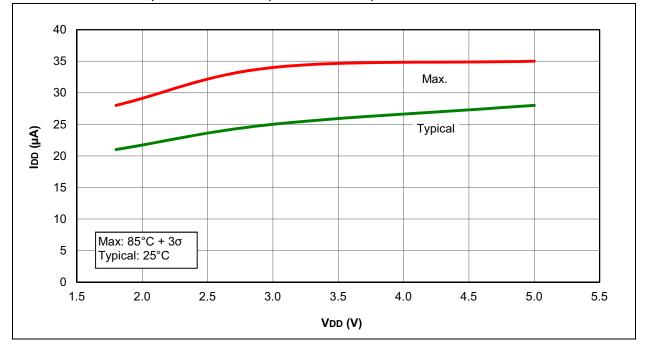

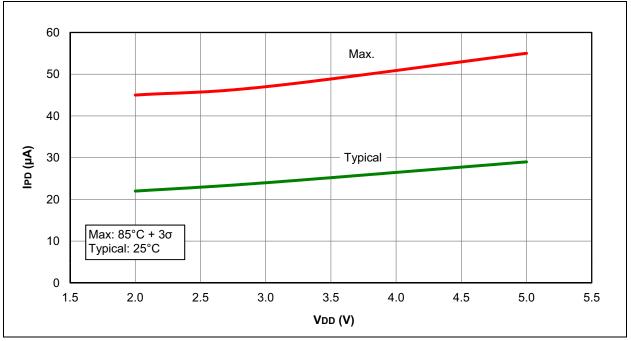

FIGURE 31-12: IDD, LFINTOSC MODE, FOSC = 31 kHz, PIC16F1847 ONLY

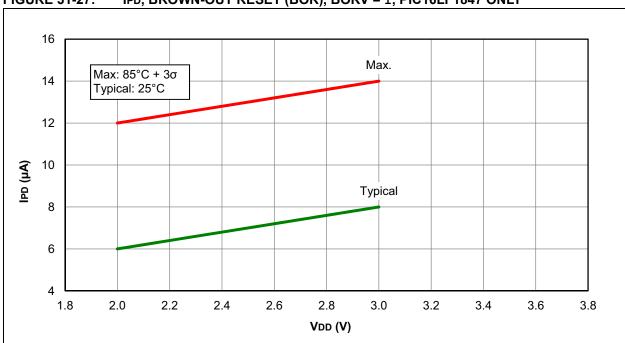

FIGURE 31-27: IPD, BROWN-OUT RESET (BOR), BORV = 1, PIC16LF1847 ONLY

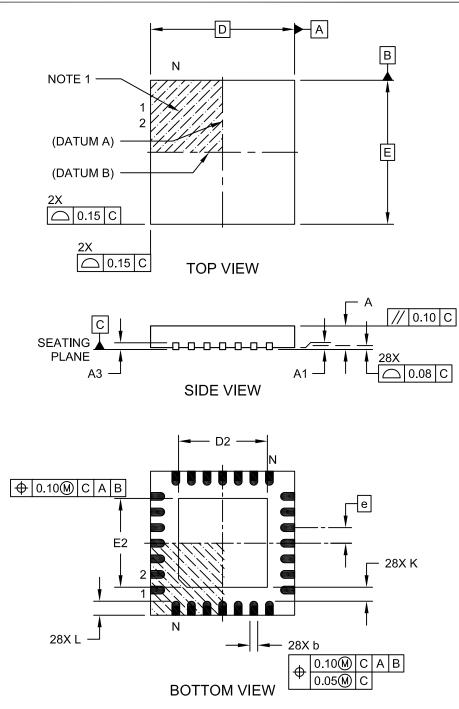

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2

28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 4x4 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

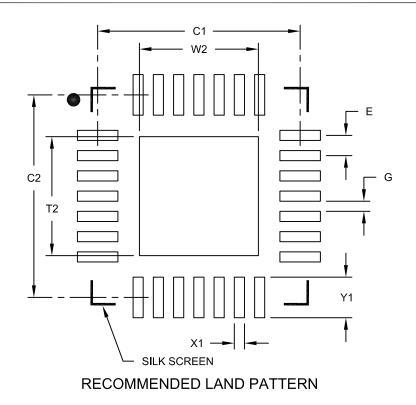

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | Е  | 0.40 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 2.35 |

| Optional Center Pad Length | T2 |             |      | 2.35 |

| Contact Pad Spacing        | C1 |             | 4.00 |      |

| Contact Pad Spacing        | C2 |             | 4.00 |      |

| Contact Pad Width (X28)    | X1 |             |      | 0.20 |

| Contact Pad Length (X28)   | Y1 |             |      | 0.80 |

| Distance Between Pads      | G  | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2152A