Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

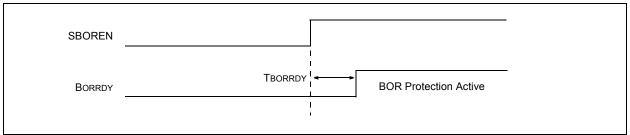

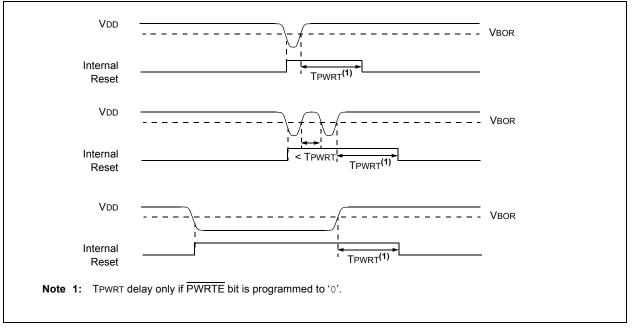

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 15                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1847-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

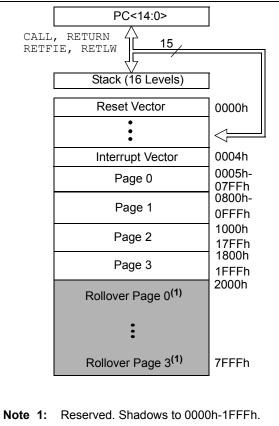

## FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1847

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

## 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | DEX                 |

| CALL constants    |                     |

| ; THE CONSTANT IS | IN W                |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

## 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

| EXAMPLE 3-2: | ACCESSING PROGRAM |

|--------------|-------------------|

|              | MEMORY VIA FSR    |

| constants  |         |         |         |      |  |

|------------|---------|---------|---------|------|--|

| RETLW      | DATA0   |         | ;Index0 | data |  |

| RETLW      | DATA1   |         | ;Index1 | data |  |

| RETLW      | data2   |         |         |      |  |

| RETLW      | data3   |         |         |      |  |

| my_functi  | on      |         |         |      |  |

| ; LO       | IS OF C | ODE     |         |      |  |

| MOVLW      | LOW c   | constan | ts      |      |  |

| MOVWF      | FSR1I   | L       |         |      |  |

| MOVLW      | HIGH    | consta  | nts     |      |  |

| MOVWF      | FSR1H   | H       |         |      |  |

| MOVIW      | 0[FSR1  | ]       |         |      |  |

| ; THE PROG | RAM MEM | MORY IS | IN W    |      |  |

|            |         |         |         |      |  |

| FIGURE 5-7:            | INTERNAL OSCILLATOR SWITCH TIMING                                     |

|------------------------|-----------------------------------------------------------------------|

|                        |                                                                       |

| HFINTOSC/→<br>MFINTOSC | LFINTOSC (FSCM and WDT disabled)                                      |

| HFINTOSC/<br>MFINTOSC  |                                                                       |

| LFINTOSC               |                                                                       |

| IRCF <3:0>             | $\neq 0$ $= 0$                                                        |

| System Clock           |                                                                       |

|                        |                                                                       |

|                        | LFINTOSC (Either FSCM or WDT enabled)                                 |

| MFINTOSC               |                                                                       |

| HFINTOSC/<br>MFINTOSC  |                                                                       |

| LFINTOSC               |                                                                       |

| IRCF <3:0>             | $\neq 0$ $X = 0$                                                      |

| System Clock           |                                                                       |

|                        |                                                                       |

|                        | HFINTOSC/MFINTOSC                                                     |

|                        | LFINTOSC/MFINTOSC<br>LFINTOSC turns off unless WDT or FSCM is enabled |

| LFINTOSC               |                                                                       |

|                        | Start-up Time '2-cycle Sync ' Running                                 |

| HFINTOSC/<br>MFINTOSC  |                                                                       |

| IRCF <3:0>             | = 0 × ≠ 0                                                             |

| System Clock           |                                                                       |

|                        |                                                                       |

|                        |                                                                       |

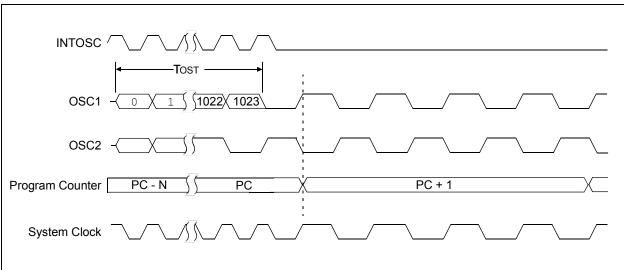

### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

## 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

## FIGURE 5-8: TWO-SPEED START-UP

## **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator.

## 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| WDTE<br>Config bits | SWDTEN | Device<br>Mode | WDT<br>Mode |

|---------------------|--------|----------------|-------------|

| WDT_ON (11)         | Х      | Х              | Active      |

| WDT_NSLEEP (10)     | Х      | Awake          | Active      |

| WDT_NSLEEP (10)     | Х      | Sleep          | Disabled    |

| WDT_SWDTEN (01)     | 1      | Х              | Active      |

| WDT_SWDTEN (01)     | 0      | Х              | Disabled    |

| WDT_OFF (00)        | Х      | х              | Disabled    |

TABLE 10-1: WDT OPERATING MODES

## 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds. After a Reset, the default time-out period is two seconds.

## 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail event

- WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 10-2 for more information.

## 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See Section 3.0 "Memory Organization" for more information.

### TABLE 10-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT                          |  |

|----------------------------------------------------------|------------------------------|--|

| WDTE<1:0> = 00                                           |                              |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |

| CLRWDT Command                                           | Cleared                      |  |

| Oscillator Fail Detected                                 |                              |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |

## 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The Data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Words, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

## 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

## 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when the write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

### EXAMPLE 11-4: ERASING ONE ROW OF PROGRAM MEMORY -

|   |                      | $\Box \Box \Box \Box \Box = \mp$ . |                 |                                                            |

|---|----------------------|------------------------------------|-----------------|------------------------------------------------------------|

| ; | This                 | row erase                          | routine assumes | the following:                                             |

| ; | 1. A                 | valid addr                         | ess within the  | erase block is loaded in ADDRH:ADDRL                       |

| ; | 2. AI                | DDRH and AD                        | DRL are located | in shared data memory 0x70 - 0x7F                          |

|   |                      |                                    |                 |                                                            |

|   |                      |                                    |                 |                                                            |

|   |                      | BCF                                | INTCON, GIE     | ; Disable ints so required sequences will execute properly |

|   |                      | BANKSEL                            | EEADRL          |                                                            |

|   |                      | MOVF                               | ADDRL,W         | ; Load lower 8 bits of erase address boundary              |

|   |                      | MOVWF                              | EEADRL          |                                                            |

|   |                      | MOVF                               | ADDRH,W         | ; Load upper 6 bits of erase address boundary              |

|   |                      | MOVWF                              | EEADRH          |                                                            |

|   |                      | BSF                                | EECON1, EEPGD   | ; Point to program memory                                  |

|   |                      | BCF                                | EECON1,CFGS     | ; Not configuration space                                  |

|   |                      | BSF                                | EECON1, FREE    | ; Specify an erase operation                               |

|   |                      | BSF                                | EECON1,WREN     | ; Enable writes                                            |

|   |                      |                                    |                 |                                                            |

|   |                      | MOVLW                              | 55h             | ; Start of required sequence to initiate erase             |

|   |                      | MOVWF                              | EECON2          | ; Write 55h                                                |

|   | Required<br>Sequence | MOVLW                              | 0AAh            | ;                                                          |

|   | uire                 | MOVWF                              | EECON2          | ; Write AAh                                                |

|   | ed                   | BSF                                | EECON1,WR       | ; Set WR bit to begin erase                                |

|   | ЖŴ                   | NOP                                |                 | ; Any instructions here are ignored as processor           |

|   |                      |                                    |                 | ; halts to begin erase sequence                            |

|   |                      | NOP                                |                 | ; Processor will stop here and wait for erase complete.    |

|   |                      |                                    |                 |                                                            |

|   |                      |                                    |                 | ; after erase processor continues with 3rd instruction     |

|   |                      | BCF                                | EECON1,WREN     | ; Disable writes                                           |

|   |                      | BSF                                | INTCON, GIE     | ; Enable interrupts                                        |

|   |                      | -                                  |                 | ,                                                          |

| Name    | Bit 7      | Bit 6        | Bit 5       | Bit 4                | Bit 3                    | Bit 2     | Bit 1   | Bit 0  | Register<br>on Page |

|---------|------------|--------------|-------------|----------------------|--------------------------|-----------|---------|--------|---------------------|

| ADCON0  | _          |              |             | CHS<4:0>             |                          |           | GO/DONE | ADON   | 143                 |

| ADCON1  | ADFM       |              | ADCS<2:0>   |                      | —                        | ADNREF    | ADPRE   | F<1:0> | 144                 |

| ADRESH  | ADC Result | Register Hig | h           |                      |                          |           |         |        | 145, 146            |

| ADRESL  | ADC Result | Register Lov | egister Low |                      |                          |           |         |        | 145, 146            |

| ANSELA  |            | —            | —           | ANSA4                | ANSA3                    | ANSA2     | ANSA1   | ANSA0  | 122                 |

| ANSELB  | ANSB7      | ANSB6        | ANSB5       | ANSB4                | ANSB3                    | ANSB2     | ANSB1   | —      | 127                 |

| CCP4CON |            | _            | DC4E        | DC4B<1:0> CCPxM<3:0> |                          |           |         |        | 226                 |

| INTCON  | GIE        | PEIE         | TMR0IE      | INTE                 | IOCE                     | TMR0IF    | INTF    | IOCF   | 88                  |

| PIE1    | TMR1GIE    | ADIE         | RCIE        | TXIE                 | SSP1IE                   | CCP1IE    | TMR2IE  | TMR1IE | 89                  |

| PIR1    | TMR1GIF    | ADIF         | RCIF        | TXIF                 | SSP1IF                   | CCP1IF    | TMR2IF  | TMR1IF | 93                  |

| TRISA   | TRISA7     | TRISA6       | TRISA5      | TRISA4               | TRISA3                   | TRISA2    | TRISA1  | TRISA0 | 120                 |

| TRISB   | TRISB7     | TRISB6       | TRISB5      | TRISB4               | TRISB3                   | TRISB2    | TRISB1  | TRISB0 | 126                 |

| FVRCON  | FVREN      | FVRRDY       | TSEN        | TSRNG                | TSRNG CDAFVR<1:0> ADFVR< |           |         | R<1:0> | 134                 |

| DACCON0 | DACEN      | DACLPS       | DACOE       | - DACPSS<1:0>        |                          |           | —       | DACNSS | 154                 |

| DACCON1 |            | —            | —           |                      | •                        | DACR<4:0> | •       | •      | 154                 |

TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for ADC module.

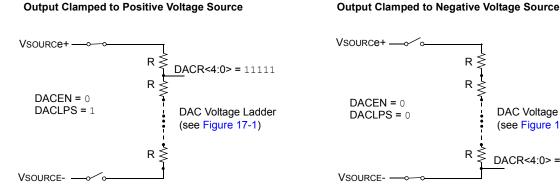

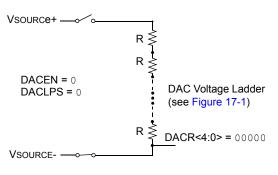

#### 17.4 Low Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSOURCE+), or the negative voltage source, (VSOURCE-) can be disabled.

The negative voltage source is disabled by setting the DACLPS bit in the DACCON0 register. Clearing the DACLPS bit in the DACCON0 register disables the positive voltage source.

#### 17.4.1 OUTPUT CLAMPED TO POSITIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE+ with the least amount of power consumption by performing the following:

- Clearing the DACEN bit in the DACCON0 register.

- Setting the DACLPS bit in the DACCON0 register.

- · Configuring the DACPSS bits to the proper positive source.

- Configuring the DACR<4:0> bits to '11111' in the DACCON1 register.

This is also the method used to output the voltage level from the FVR to an output pin. See Section 17.3 "DAC Voltage Reference Output" for more information.

Reference Figure 17-3 for output clamping examples.

#### 17.4.2 OUTPUT CLAMPED TO NEGATIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE- with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- · Clearing the DACLPS bit in the DACCON0 register.

- · Configuring the DACNSS bits to the proper negative source.

- Configuring the DACR<4:0> bits to '00000' in the DACCON1 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

Reference Figure 17-3 for output clamping examples.

#### FIGURE 17-3: OUTPUT VOLTAGE CLAMPING EXAMPLES

#### 17.5 **Operation During Sleep**

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 17.6 Effects of a Reset

A device Reset affects the following:

- · DAC is disabled.

- · DAC output voltage is removed from the DACOUT pin.

- The DACR<4:0> range select bits are cleared.

## 18.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- Programmable input selection

- SR latch output is available externally

- Separate Q and  $\overline{Q}$  outputs

- · Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

## 18.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to Set or Reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 19.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source is available that can periodically Set or Reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to Set or Reset the SR latch, respectively.

## 18.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to an I/O pin at the same time.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

## 18.3 Effects of a Reset

Upon any device Reset, the SR latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

| R/W-0/0          | R/W-0/0      | R/W-0/0                              | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|--------------|--------------------------------------|-----------------|-------------------|------------------|----------------|--------------|

| SRSPE            | SRSCKE       | SRSC2E                               | SRSC1E          | SRRPE             | SRRCKE           | SRRC2E         | SRRC1E       |

| bit 7            |              |                                      |                 | -                 |                  |                | bit 0        |

|                  |              |                                      |                 |                   |                  |                |              |

| Legend:          |              |                                      |                 |                   |                  |                |              |

| R = Readable     | bit          | W = Writable                         | bit             | U = Unimpler      | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged        | x = Bit is unkr                      | nown            | -n/n = Value a    | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |              | '0' = Bit is cle                     | ared            |                   |                  |                |              |

|                  |              |                                      |                 |                   |                  |                |              |

| bit 7            |              | Latch Periphera                      |                 |                   |                  |                |              |

|                  |              | is set when the                      |                 |                   |                  |                |              |

|                  | •            | has no effect or                     | •               | of the SR latch   |                  |                |              |

| bit 6            |              | R Latch Set Clo                      |                 |                   |                  |                |              |

|                  |              | t of SR latch is<br>has no effect or |                 |                   | 1                |                |              |

| bit 5            |              | R Latch C2 Set                       |                 |                   |                  |                |              |

| bit o            |              | is set when the                      |                 | tor output is hi  | b                |                |              |

|                  |              |                                      |                 |                   | of the SR latch  |                |              |

| bit 4            | SRSC1E: SF   | R Latch C1 Set                       | Enable bit      |                   |                  |                |              |

|                  | 1 = SR latch | is set when the                      | e C1 Compara    | tor output is hig | gh               |                |              |

|                  | 0 = C1 Com   | parator output l                     | nas no effect o | n the set input   | of the SR latch  |                |              |

| bit 3            | SRRPE: SR    | Latch Peripher                       | al Reset Enabl  | e bit             |                  |                |              |

|                  |              | is reset when                        |                 | U U               |                  |                |              |

|                  | •            | has no effect or                     | •               |                   | tch              |                |              |

| bit 2            |              | R Latch Reset (                      |                 |                   |                  |                |              |

|                  |              | put of SR latch<br>has no effect or  |                 |                   | tch              |                |              |

| bit 1            |              | R Latch C2 Res                       | -               |                   |                  |                |              |

|                  | 1 = SR latch | is reset when                        | the C2 Compa    | rator output is   | high             |                |              |

|                  |              |                                      |                 |                   | out of the SR la | tch            |              |

| bit 0            | SRRC1E: SF   | R Latch C1 Res                       | et Enable bit   |                   |                  |                |              |

|                  |              | is reset when                        |                 |                   |                  |                |              |

|                  | 0 = C1 Com   | parator output I                     | nas no effect o | n the Reset inp   | out of the SR la | tch            |              |

|                  |              |                                      |                 |                   |                  |                |              |

## REGISTER 18-2: SRCON1: SR LATCH CONTROL 1 REGISTER

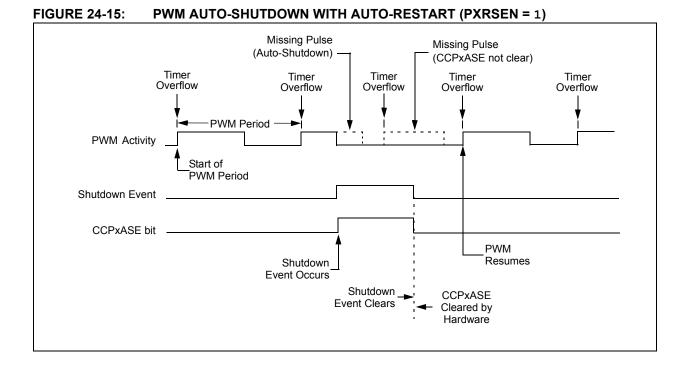

## 24.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register. If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

## 25.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the 9th bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see Section 25.5.6 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the 9th SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the 9th clock pulse.

## 25.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

## 25.5.3.2 7-Bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 25-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

## 26.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 26.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 26.4.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name    | Bit 7   | Bit 6                        | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|---------|------------------------------|--------|--------|---------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL | SDO1SEL                      | SS1SEL | P2BSEL | CCP2SEL | P1DSEL | P1CSEL | CCP1SEL | 118                 |

| APFCON1 | —       | —                            |        | _      | _       | _      | _      | TXCKSEL | 118                 |

| BAUDCON | ABDOVF  | RCIDL                        | —      | SCKP   | BRG16   | _      | WUE    | ABDEN   | 298                 |

| INTCON  | GIE     | PEIE                         | TMR0IE | INTE   | IOCE    | TMR0IF | INTF   | IOCF    | 88                  |

| PIE1    | TMR1GIE | ADIE                         | RCIE   | TXIE   | SSP1IE  | CCP1IE | TMR2IE | TMR1IE  | 89                  |

| PIR1    | TMR1GIF | ADIF                         | RCIF   | TXIF   | SSP1IF  | CCP1IF | TMR2IF | TMR1IF  | 93                  |

| RCREG   |         | EUSART Receive Data Register |        |        |         |        |        | 292*    |                     |

| RCSTA   | SPEN    | RX9                          | SREN   | CREN   | ADDEN   | FERR   | OERR   | RX9D    | 297                 |

| TRISB   | TRISB7  | TRISB6                       | TRISB5 | TRISB4 | TRISB3  | TRISB2 | TRISB1 | TRISB0  | 126                 |

| TXSTA   | CSRC    | TX9                          | TXEN   | SYNC   | SENDB   | BRGH   | TRMT   | TX9D    | 296                 |

## TABLE 26-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Reception.

\* Page provides register information.

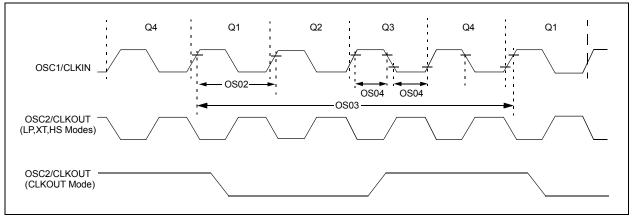

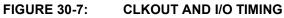

## TABLE 30-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param.<br>No. | Sym.  | Characteristic                          | Min. | Тур†   | Max.   | Units | Conditions                |

|---------------|-------|-----------------------------------------|------|--------|--------|-------|---------------------------|

| OS01          | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 0.5    | MHz   | External Clock (ECL)      |

|               |       |                                         | DC   | —      | 4      | MHz   | External Clock (ECM)      |

|               |       |                                         | DC   | —      | 20     | MHz   | External Clock (ECH)      |

|               |       | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768 | _      | kHz   | LP Oscillator             |

|               |       |                                         | 0.1  | _      | 4      | MHz   | XT Oscillator             |

|               |       |                                         | 1    | _      | 4      | MHz   | HS Oscillator             |

|               |       |                                         | 1    |        | 20     | MHz   | HS Oscillator, VDD > 2.7V |

|               |       |                                         | DC   | _      | 4      | MHz   | EXTRC, VDD > 2.0V         |

| OS02 To       | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   |        | ×      | μs    | LP Oscillator             |

|               |       |                                         | 250  | _      | ×      | ns    | XT Oscillator             |

|               |       |                                         | 50   |        | ×      | ns    | HS Oscillator             |

|               |       |                                         | 50   | _      | ×      | ns    | External Clock (EC)       |

|               |       | Oscillator Period <sup>(1)</sup>        | —    | 30.5   | _      | μs    | LP Oscillator             |

|               |       |                                         | 250  | _      | 10,000 | ns    | XT Oscillator             |

|               |       |                                         | 50   | _      | 1,000  | ns    | HS Oscillator             |

|               |       |                                         | 250  | _      | —      | ns    | EXTRC                     |

| OS03          | TCY   | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY    | DC     | ns    | Tcy = 4/Fosc              |

| OS04*         | TosH, | External CLKIN High                     | 2    | _      | _      | μs    | LP Oscillator             |

|               | TosL  | External CLKIN Low                      | 100  | —      | —      | ns    | XT Oscillator             |

|               |       |                                         | 20   | —      | —      | ns    | HS Oscillator             |

| OS05*         | TosR, | External CLKIN Rise                     | 0    | —      | _      | ns    | LP Oscillator             |

|               | TosF  | External CLKIN Fall                     | 0    | _      | —      | ns    | XT Oscillator             |

|               |       |                                         | 0    | —      | _      | ns    | HS Oscillator             |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

| Standard Operating Conditions (unless otherwise stated) |          |                                                               |               |          |          |       |                                                                      |  |  |

|---------------------------------------------------------|----------|---------------------------------------------------------------|---------------|----------|----------|-------|----------------------------------------------------------------------|--|--|

| Param.<br>No.                                           | Sym.     | Characteristic                                                | Min.          | Typ†     | Max.     | Units | Conditions                                                           |  |  |

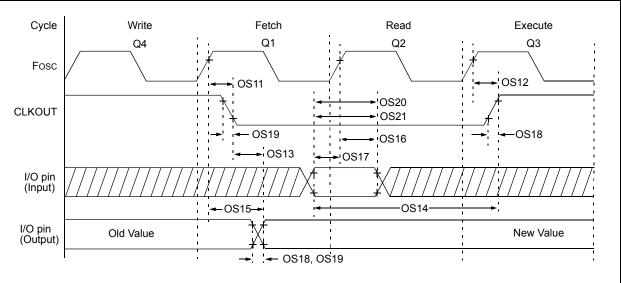

| OS11                                                    | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                               | —             | —        | 70       | ns    | $3.3V \leq V\text{DD} \leq 5.0V$                                     |  |  |

| OS12                                                    | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                               | _             | —        | 72       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                       |  |  |

| OS13                                                    | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                      | —             | _        | 20       | ns    |                                                                      |  |  |

| OS14                                                    | TioV2ckH | Port input valid before CLKOUT <sup>(1)</sup>                 | Tosc + 200 ns | —        | —        | ns    |                                                                      |  |  |

| OS15                                                    | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                            | —             | 50       | 70*      | ns    | $3.3V \leq V\text{DD} \leq 5.0V$                                     |  |  |

| OS16                                                    | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in setup time) | 50            | _        | _        | ns    | $3.3V \le V\text{DD} \le 5.0V$                                       |  |  |

| OS17                                                    | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)   | 20            | —        | _        | ns    |                                                                      |  |  |

| OS18*                                                   | TioR     | Port output rise time                                         |               | 40<br>15 | 72<br>32 | ns    | $\begin{array}{l} VDD = 1.8V \\ 3.3V \leq VDD \leq 5.0V \end{array}$ |  |  |

| OS19*                                                   | TioF     | Port output fall time                                         |               | 28<br>15 | 55<br>30 | ns    | $\begin{array}{l} VDD = 1.8V \\ 3.3V \leq VDD \leq 5.0V \end{array}$ |  |  |

| OS20*                                                   | Tinp     | INT pin input high or low time                                | 25            |          |          | ns    |                                                                      |  |  |

| OS21*                                                   | Tioc     | Interrupt-on-change new input level time                      | 25            |          |          | ns    |                                                                      |  |  |

| Standard Operating Conditions (unless otherwise stated) |

|---------------------------------------------------------|

| Standard Operating Conditions (unless otherwise stated) |

|                                                         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

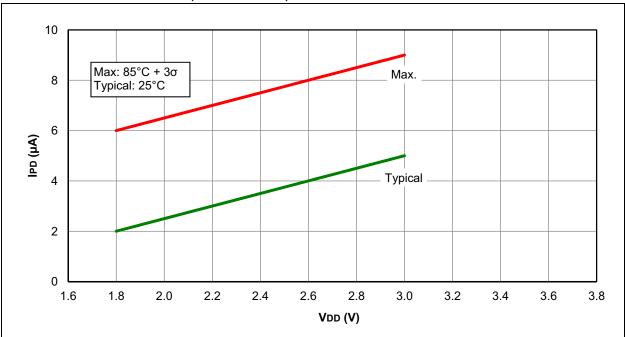

FIGURE 31-31: IPD, CAPACITIVE SENSING (CPS) MODULE, LOW-CURRENT RANGE, CPSRM = 0, CPSRNG = 01, PIC16LF1847 ONLY

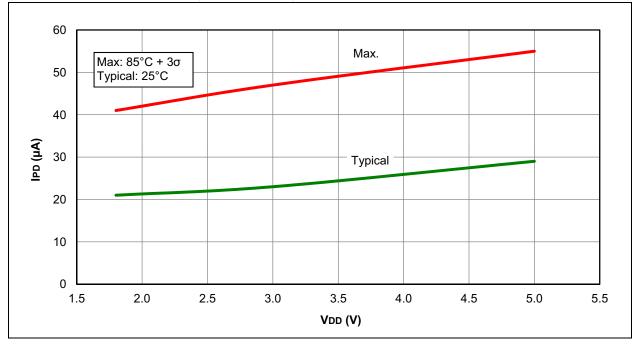

FIGURE 31-32: IPD, CAPACITIVE SENSING (CPS) MODULE, LOW-CURRENT RANGE, CPSRM = 0, CPSRNG = 01, PIC16F1847 ONLY

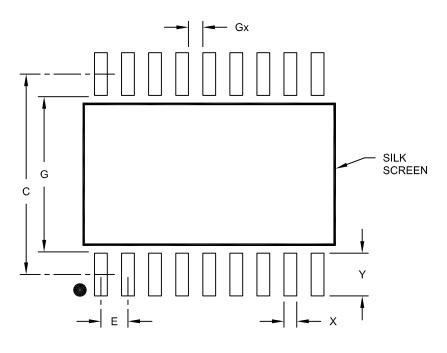

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| RECOMMENDED LAND PATTERN | ١ |

|--------------------------|---|

|--------------------------|---|

|                       | Units            | MILLIMETERS |      |      |  |

|-----------------------|------------------|-------------|------|------|--|

| Dimension             | Dimension Limits |             | NOM  | MAX  |  |

| Contact Pitch         | E                | E 1.27 BSC  |      |      |  |

| Contact Pad Spacing   | С                |             | 9.40 |      |  |

| Contact Pad Width     | X                |             |      | 0.60 |  |

| Contact Pad Length    | Y                |             |      | 2.00 |  |

| Distance Between Pads | Gx               | 0.67        |      |      |  |

| Distance Between Pads | G                | 7.40        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A