Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

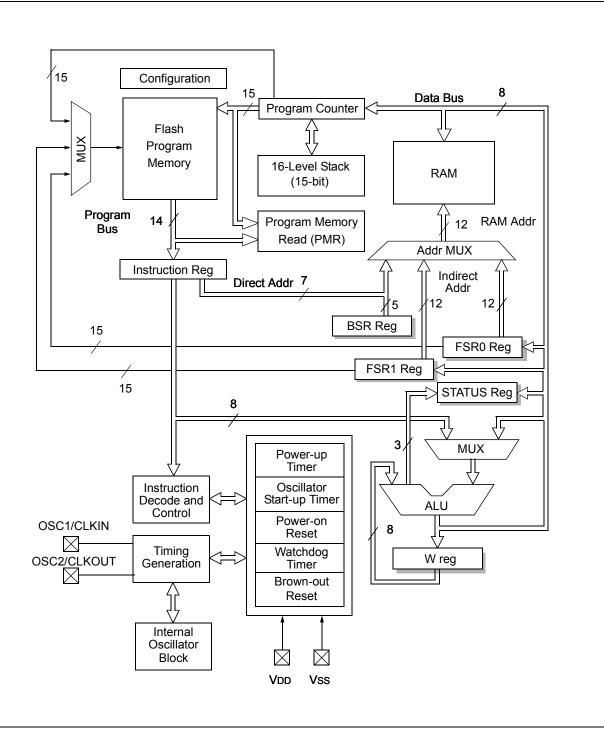

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 15                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1847-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address             | Name    | Bit 7                             | Bit 6                                                                                                     | Bit 5            | Bit 4           | Bit 3                   | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------------------|---------|-----------------------------------|-----------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------------|-------------|--------|--------|----------------------|---------------------------------|

| Bank 0              | -       |                                   |                                                                                                           |                  |                 |                         |             |        |        |                      |                                 |

| 000h <sup>(1)</sup> | INDF0   | Addressing th<br>(not a physical  |                                                                                                           | es contents of   | FSR0H/FSR0      | L to address            | data memory | 1      |        | ****                 | ****                            |

| 001h <sup>(1)</sup> | INDF1   | 0                                 | Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                  |                 |                         |             |        |        |                      |                                 |

| 002h <sup>(1)</sup> | PCL     | Program Cou                       | inter (PC) Lea                                                                                            | st Significant E | lyte            |                         |             |        |        | 0000 0000            | 0000 0000                       |

| 003h <sup>(1)</sup> | STATUS  | —                                 | _                                                                                                         | _                | TO              | PD                      | Z           | DC     | С      | 1 1000               | q quuu                          |

| 004h <sup>(1)</sup> | FSR0L   | Indirect Data                     | Memory Addr                                                                                               | ess 0 Low Poir   | nter            |                         |             |        |        | 0000 0000            | uuuu uuuu                       |

| 005h <sup>(1)</sup> | FSR0H   | Indirect Data                     | Memory Addr                                                                                               | ess 0 High Poi   | nter            |                         |             |        |        | 0000 0000            | 0000 0000                       |

| 006h <sup>(1)</sup> | FSR1L   | Indirect Data                     | Memory Addr                                                                                               | ess 1 Low Poir   | nter            |                         |             |        |        | 0000 0000            | uuuu uuuu                       |

| 007h <sup>(1)</sup> | FSR1H   | Indirect Data                     | Memory Addr                                                                                               | ess 1 High Poi   | nter            |                         |             |        |        | 0000 0000            | 0000 0000                       |

| 008h <sup>(1)</sup> | BSR     | _                                 | _                                                                                                         | _                | BSR4            | BSR3                    | BSR2        | BSR1   | BSR0   | 0 0000               | 0 0000                          |

| 009h <sup>(1)</sup> | WREG    | Working Reg                       | ister                                                                                                     |                  | •               | •                       | •           | •      | •      | 0000 0000            | uuuu uuuu                       |

| 00Ah <sup>(1)</sup> | PCLATH  | _                                 | Write Buffer f                                                                                            | or the upper 7   | bits of the Pro | ogram Counte            | r           |        |        | -000 0000            | -000 0000                       |

| 00Bh <sup>(1)</sup> | INTCON  | GIE                               | PEIE                                                                                                      | TMR0IE           | INTE            | IOCE                    | TMR0IF      | INTF   | IOCF   | 0000 000x            | 0000 000u                       |

| 00Ch                | PORTA   | RA7                               | RA6                                                                                                       | RA5              | RA4             | RA3                     | RA2         | RA1    | RA0    | XXXX XXXX            | XXXX XXXX                       |

| 00Dh                | PORTB   | RB7                               | RB6                                                                                                       | RB5              | RB4             | RB3                     | RB2         | RB1    | RB0    | XXXX XXXX            | XXXX XXXX                       |

| 00Eh                |         | Unimplement                       | ed                                                                                                        |                  |                 |                         |             |        |        | _                    | _                               |

| 00Fh                |         | Unimplement                       | ed                                                                                                        |                  |                 |                         |             |        |        | _                    | _                               |

| 010h                | —       | Unimplement                       | ed                                                                                                        |                  |                 |                         |             |        |        | _                    | _                               |

| 011h                | PIR1    | TMR1GIF                           | ADIF                                                                                                      | RCIF             | TXIF            | SSP1IF                  | CCP1IF      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| 012h                | PIR2    | OSFIF                             | C2IF                                                                                                      | C1IF             | EEIF            | BCL1IF                  | _           | _      | CCP2IF | 0000 00              | 0000 00                         |

| 013h                | PIR3    | _                                 | _                                                                                                         | CCP4IF           | CCP3IF          | TMR6IF                  | _           | TMR4IF | _      | 00 0-0-              | 00 0-0-                         |

| 014h                | PIR4    | _                                 | -                                                                                                         | _                | _               | _                       | _           | BCL2IF | SSP2IF | 00                   | 00                              |

| 015h                | TMR0    | Timer0 Modu                       | le Register                                                                                               |                  | •               |                         | •           | •      | •      | XXXX XXXX            | uuuu uuuu                       |

| 016h                | TMR1L   | Holding Regi                      | ster for the Lea                                                                                          | ast Significant  | Byte of the 16  | 6-bit TMR1 Re           | gister      |        |        | XXXX XXXX            | uuuu uuuu                       |

| 017h                | TMR1H   | Holding Regi                      | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register                                |                  |                 |                         |             |        |        |                      | uuuu uuuu                       |

| 018h                | T1CON   | TMR1C                             | S<1:0>                                                                                                    | T1CKP            | S<1:0>          | T10SCEN                 | T1SYNC      | _      | TMR10N | 0000 00-0            | uuuu uu-u                       |

| 019h                | T1GCON  | TMR1GE                            | T1GPOL                                                                                                    | T1GTM            | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL      | T1GSS  | S<1:0> | 0000 0x00            | uuuu uxuu                       |

| 01Ah                | TMR2    | Timer2 Modu                       | le Register                                                                                               |                  |                 | •                       | •           | •      |        | 0000 0000            | 0000 0000                       |

| 01Bh                | PR2     | Timer2 Perio                      | d Register                                                                                                |                  |                 |                         |             |        |        | 1111 1111            | 1111 1111                       |

| 01Ch                | T2CON   | - T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |                                                                                                           |                  |                 |                         |             |        | S<1:0> | -000 0000            | -000 0000                       |

| 01Dh                | —       | Unimplement                       | ed                                                                                                        |                  |                 |                         |             |        |        | —                    | —                               |

| 01Eh                | CPSCON0 | CPSON                             | CPSRM                                                                                                     | _                | _               | CPSRN                   | G<1:0>      | CPSOUT | T0XCS  | 00 0000              | 00 0000                         |

| 01Fh                | CPSCON1 | _                                 | CPSCH<3:0>                                                                                                |                  |                 |                         |             |        |        | 0000                 | 0000                            |

| TABLE 3-8: | SPECIAL FUNCTION REGISTER SUMMARY |

|------------|-----------------------------------|

|            |                                   |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

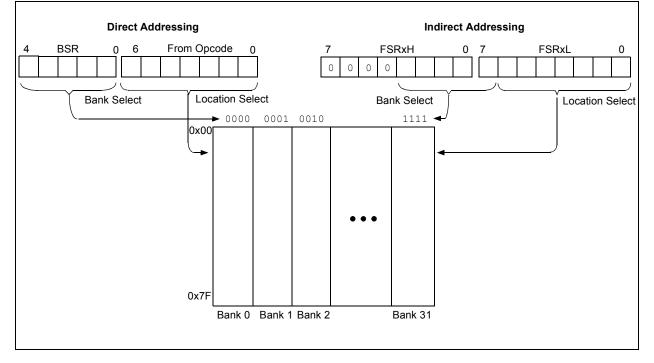

### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0x1FFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire data EEPROM will be erased when the code protection is turned off during an erase. Once the Data Code Protection bit is enabled, (CPD = 0), the Bulk Erase Program Memory Command (through ICSP) can disable the Data Code Protection (CPD = 1). When a Bulk Erase Program Memory Command is executed, the entire program Flash memory, data EEPROM and configuration memory will be erased.

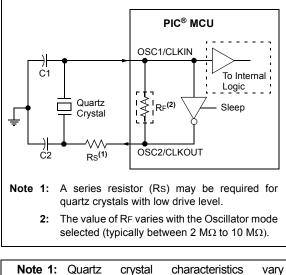

### FIGURE 5-3:

#### QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- lote 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

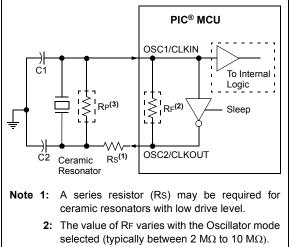

### FIGURE 5-4: CERAMIC RESONATOR OPERATION

(XT OR HS MODE)

An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

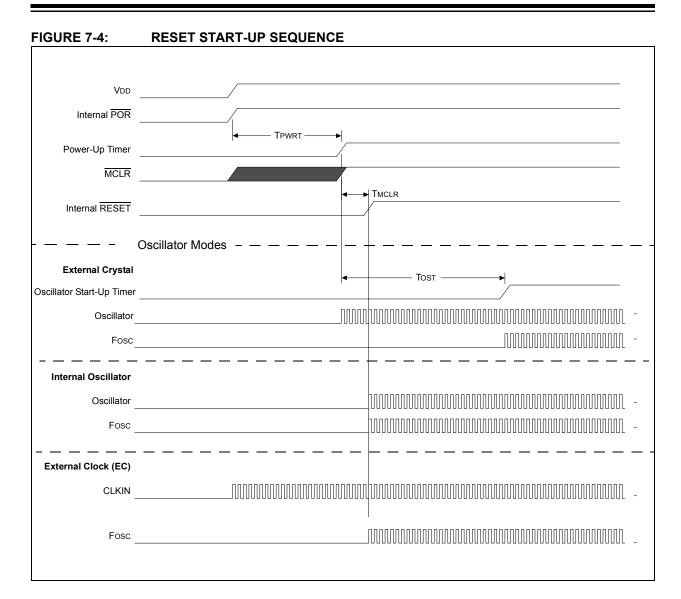

# 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see Section 5.4 "Two-Speed Clock Start-up Mode").

## 5.2.1.4 4xPLL

The oscillator module contains a 4xPLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4xPLL must fall within specifications. See the PLL Clock Timing Specifications in Section 30.0 "Electrical Specifications"

The 4xPLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Words to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Words is programmed to a '1', then the value of SPLLEN is ignored.

NOTES:

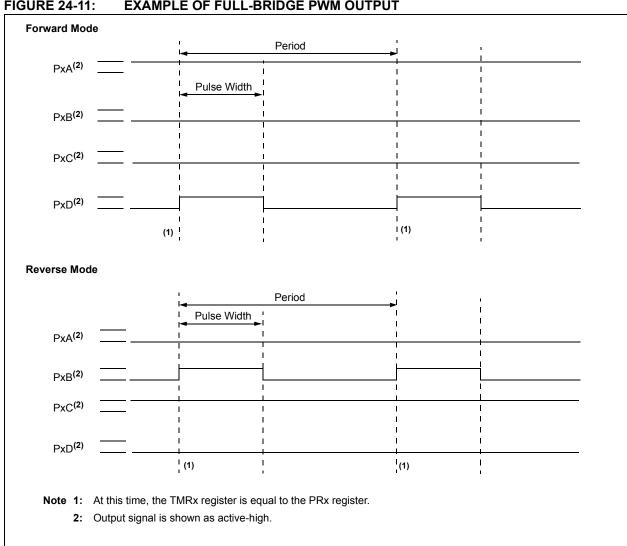

FIGURE 24-11: **EXAMPLE OF FULL-BRIDGE PWM OUTPUT**

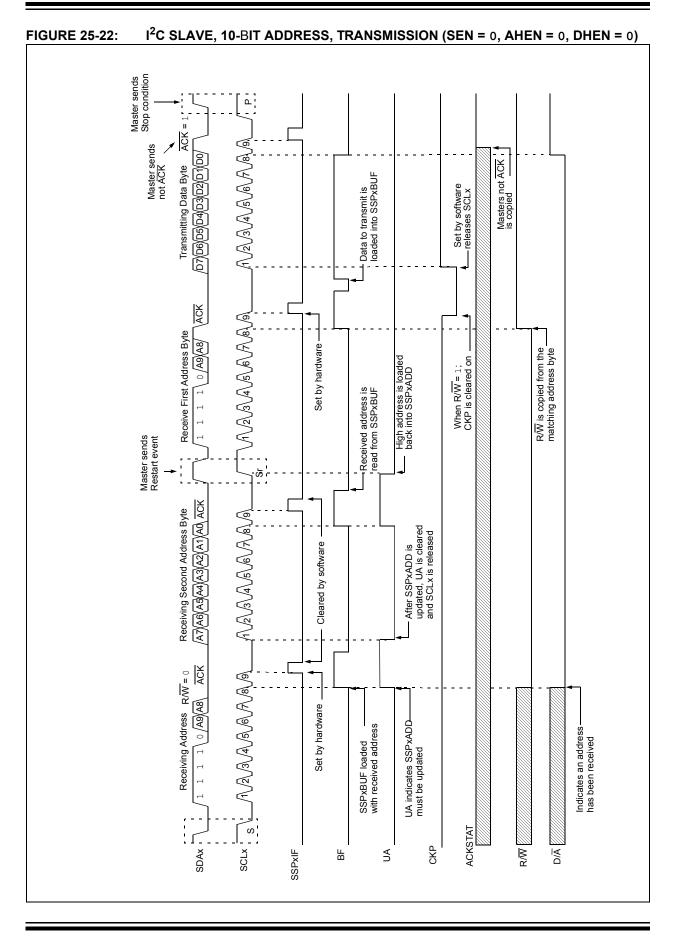

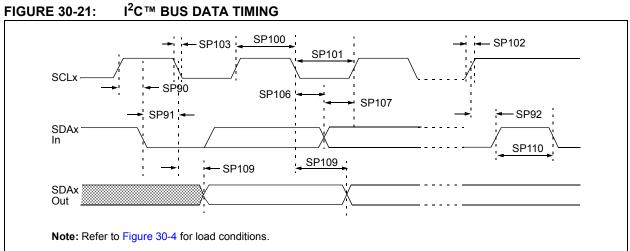

# 25.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the 9th bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see Section 25.5.6 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the 9th SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the 9th clock pulse.

### 25.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

### 25.5.3.2 7-Bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 25-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

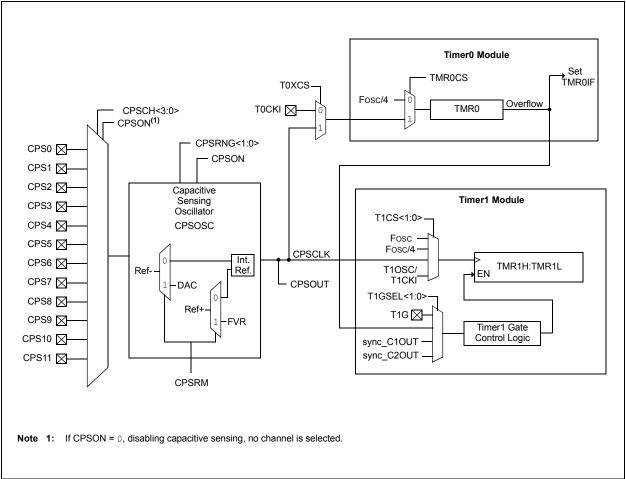

# 27.0 CAPACITIVE SENSING MODULE

The Capacitive Sensing (CPS) module allows for an interaction with an end user without a mechanical interface. In a typical application, the CPS module is attached to a pad on a Printed Circuit Board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the CPS module. The CPS module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- · Multiple Power modes

- High power range with variable voltage references

- Multiple timer resources

- · Software control

- · Operation during Sleep

### FIGURE 27-1: CAPACITIVE SENSING BLOCK DIAGRAM

# 29.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [label]ADDFSR FSRn, k                                                                         |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | ECDs is limited to the serve 0000h                                                            |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |  |  |  |  |  |

| Status Affected: | Z                                                                                                               |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \to (W)$                                                                                             |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

| ADDWF            | Add W and f                                                                                                                                                                     |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                   |

| Status Affected: | C, Z                                                                                                                                                                      |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is 'o' the result is placed in W. If 'd' |

flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'.

| ADDWFC           | ADD W and CARRY bit to f                                                                                                                                                  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |  |  |  |  |

| PIC16LF       | 1847            | Standard Operating Conditions (unless otherwise stated) |            |      |       |     |                        |  |  |

|---------------|-----------------|---------------------------------------------------------|------------|------|-------|-----|------------------------|--|--|

| PIC16F1       | 847             |                                                         |            |      |       |     |                        |  |  |

| Param. Device |                 |                                                         | <b>T</b> t |      | Unite |     | Conditions             |  |  |

| No.           | Characteristics | Min.                                                    | Тур†       | Max. | Units | VDD | Note                   |  |  |

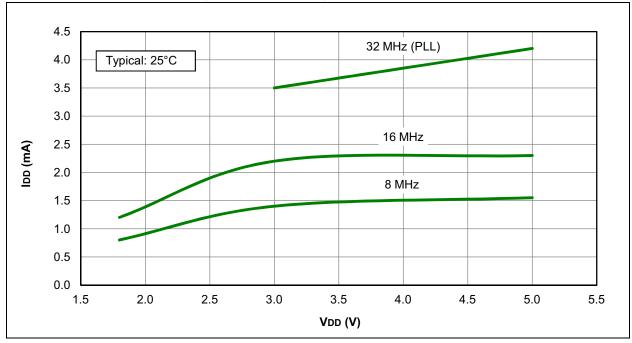

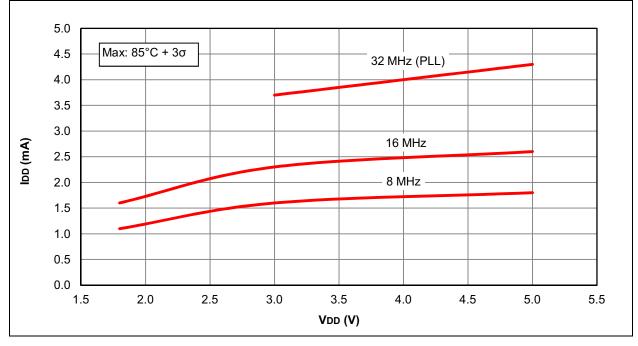

| D019          |                 | —                                                       | 3.50       | 3.70 | mA    | 3.0 | Fosc = 32 MHz          |  |  |

|               |                 | _                                                       | 4.20       | 4.30 | mA    | 5.0 | HFINTOSC (Note 3)      |  |  |

| D020          |                 | —                                                       | 3.20       | 3.50 | mA    | 3.0 | Fosc = 32 MHz          |  |  |

|               |                 | _                                                       | 3.70       | 3.90 | mA    | 3.6 | HS Oscillator (Note 4) |  |  |

| D020          |                 | —                                                       | 3.30       | 3.60 | mA    | 3.0 | Fosc = 32 MHz          |  |  |

|               |                 | _                                                       | 3.70       | 4.10 | mA    | 5.0 | HS Oscillator (Note 4) |  |  |

| D021          |                 | —                                                       | 252        | 350  | μA    | 1.8 | Fosc = 4 MHz           |  |  |

|               |                 | _                                                       | 480        | 580  | μA    | 3.0 | EXTRC (Note 5)         |  |  |

| D021          |                 | —                                                       | 302        | 425  | μA    | 1.8 | Fosc = 4 MHz           |  |  |

|               |                 | —                                                       | 440        | 680  | μA    | 3.0 | EXTRC (Note 5)         |  |  |

|               |                 | —                                                       | 511        | 780  | μA    | 5.0 | 1                      |  |  |

# TABLE 30-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance + only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- **3:** 8 MHz internal oscillator with 4x PLL enabled.

- 4: 8 MHz crystal oscillator with 4x PLL enabled.

- 5: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

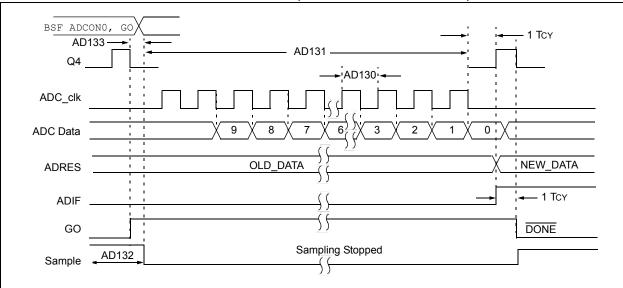

**Note 1:** If the ADC clock source is selected as FRC, a time of TCY is added before the ADC clock starts. This allows the SLEEP instruction to be executed.

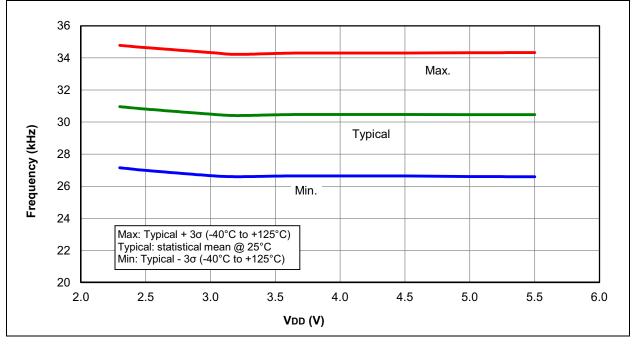

FIGURE 31-61: LFINTOSC FREQUENCY OVER VDD AND TEMPERATURE, PIC16F1847 ONLY

# 32.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 32.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 32.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | MILLIMETERS |          |      |  |  |

|------------------------|--------|-------------|----------|------|--|--|

| Dimension              | Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins         | N      | 28          |          |      |  |  |

| Pitch                  | е      |             | 0.40 BSC |      |  |  |

| Overall Height         | A      | 0.45        | 0.50     | 0.55 |  |  |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3     | 0.127 REF   |          |      |  |  |

| Overall Width          | E      | 4.00 BSC    |          |      |  |  |

| Exposed Pad Width      | E2     | 2.55        | 2.65     | 2.75 |  |  |

| Overall Length         | D      | 4.00 BSC    |          |      |  |  |

| Exposed Pad Length     | D2     | 2.55        | 2.65     | 2.75 |  |  |

| Contact Width          | b      | 0.15        | 0.20     | 0.25 |  |  |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | K      | 0.20        | -        | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620773642

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.