Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 15                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1847t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIN ALLOCATION TABLE**

| TABLE 1: | 18/20/28- | PIN SUM | IMARY | (PIC1 | 6(L)F | 1847) |

|----------|-----------|---------|-------|-------|-------|-------|

|          |           |         |       |       |       |       |

|     |                  |             |                 |       |      |                 |           | •                         | • •      | ,               |                                                                           |                                                                                      |                                       |            |           |                  |                        |

|-----|------------------|-------------|-----------------|-------|------|-----------------|-----------|---------------------------|----------|-----------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|------------|-----------|------------------|------------------------|

| O/I | 18-Pin PDIP/SOIC | 20-Pin SSOP | 28-Pin QFN/UQFN | ANSEL | ADC  | Reference       | Cap Sense | Comparator                | SR Latch | Timers          | ссР                                                                       | EUSART                                                                               | dSSM                                  | Interrupt  | Modulator | Pull-up          | Basic                  |

| RA0 | 17               | 19          | 23              | Y     | AN0  | —               | CPS0      | C12IN0-                   | -        | _               |                                                                           | —                                                                                    | SDO2                                  | I          | —         | Ν                | —                      |

| RA1 | 18               | 20          | 24              | Y     | AN1  | —               | CPS1      | C12IN1-                   | —        | —               | _                                                                         | _                                                                                    | SS2                                   | -          | —         | Ν                | —                      |

| RA2 | 1                | 1           | 26              | Y     | AN2  | VREF-<br>DACOUT | CPS2      | C12IN2-<br>C12IN+         | _        | —               | —                                                                         | —                                                                                    | —                                     | _          | —         | Ν                | —                      |

| RA3 | 2                | 2           | 27              | Y     | AN3  | VREF+           | CPS3      | C12IN3-<br>C1IN+<br>C1OUT | SRQ      | —               | CCP3                                                                      | —                                                                                    | _                                     |            | —         | Ν                | —                      |

| RA4 | 3                | 3           | 28              | Υ     | AN4  | _               | CPS4      | C2OUT                     | SRNQ     | <b>T0CKI</b>    | CCP4                                                                      | _                                                                                    | _                                     |            | —         | Ν                | —                      |

| RA5 | 4                | 4           | 1               | Ν     |      |                 |           | —                         |          | -               |                                                                           | —                                                                                    | SS1 <sup>(1)</sup>                    |            | _         | Y <sup>(2)</sup> | MCLR<br>VPP            |

| RA6 | 15               | 17          | 20              | Ν     |      |                 | _         | _                         | _        | —               | P1D <sup>(1)</sup><br>P2B <sup>(1)</sup>                                  |                                                                                      | SDO1 <sup>(1)</sup>                   |            | _         | Ν                | OSC2<br>CLKOUT<br>CLKR |

| RA7 | 16               | 18          | 21              | Ν     |      |                 |           | _                         |          | _               | P1C <sup>(1)</sup><br>CCP2 <sup>(1)</sup><br>P2A <sup>(1)</sup>           | _                                                                                    |                                       |            | _         | Ν                | OSC1<br>CLKIN          |

| RB0 | 6                | 7           | 7               | N     | _    |                 | —         | —                         | SRI      | T1G             | CCP1 <sup>(1)</sup><br>P1A <sup>(1)</sup><br>FLT0                         | —                                                                                    |                                       | INT<br>IOC | -         | Y                | -                      |

| RB1 | 7                | 8           | 8               | Y     | AN11 | —               | CPS11     | —                         | _        | _               | _                                                                         | RX <sup>(1,3)</sup><br>DT <sup>(1,3)</sup>                                           | SDA1<br>SDI1                          | IOC        | —         | Y                | —                      |

| RB2 | 8                | 9           | 9               | Y     | AN10 |                 | CPS10     | _                         | _        | -               | _                                                                         | RX <sup>(1)</sup><br>DT <sup>(1)</sup><br>TX <sup>(1,3)</sup><br>CK <sup>(1,3)</sup> | SDA2<br>SDI2<br>SDO1 <sup>(1,3)</sup> | IOC        | MDMIN     | Y                | —                      |

| RB3 | 9                | 10          | 10              | Y     | AN9  | _               | CPS9      | —                         | _        | _               | CCP1 <sup>(1,3)</sup><br>P1A <sup>(1,3)</sup>                             | _                                                                                    | _                                     | IOC        | MDOUT     | Y                | —                      |

| RB4 | 10               | 11          | 12              | Y     | AN8  | -               | CPS8      | —                         | -        | -               |                                                                           | —                                                                                    | SCL1<br>SCK1                          | IOC        | MDCIN2    | Y                | —                      |

| RB5 | 11               | 12          | 13              | Y     | AN7  |                 | CPS7      | _                         | -        | _               | P1B                                                                       | TX <sup>(1)</sup><br>CK <sup>(1)</sup>                                               | SCL2<br>SCK2<br>SS1 <sup>(1,3)</sup>  | IOC        | _         | Y                | —                      |

| RB6 | 12               | 13          | 15              | Y     | AN5  | _               | CPS5      | —                         | _        | T1CKI<br>T1OSCI | $\begin{array}{c} P1C^{(1,3)} \\ CCP2^{(1,3)} \\ P2A^{(1,3)} \end{array}$ | —                                                                                    | —                                     | IOC        | _         | Y                | ICSPCLK                |

| RB7 | 13               | 14          | 16              | Y     | AN6  | _               | CPS6      | —                         | _        | T1OSCO          | P1D <sup>(1,3)</sup><br>P2B <sup>(1,3)</sup>                              |                                                                                      | —                                     | IOC        | MDCIN1    | Y                | ICSPDAT                |

| VDD | 14               | 15,<br>16   | 17,<br>19       |       |      | —               | -         | —                         | -        | —               | —                                                                         | —                                                                                    | —                                     | -          | —         |                  | VDD                    |

| Vss | 5                | 5,6         | 3,5             | _     | —    | _               | _         | _                         | _        | _               | _                                                                         | _                                                                                    | _                                     | _          | _         | —                | Vss                    |

Note 1:

Pin functions can be moved using th<u>e APF</u>CON register(s).

Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

Default function location.

NOTES:

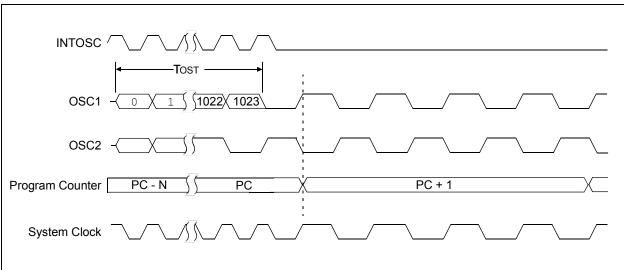

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

### FIGURE 5-8: TWO-SPEED START-UP

# 6.5 Register Definitions: Reference Clock Control

### REGISTER 6-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0          | R/W-0/0                                | R/W-1/1                              | R/W-1/1       | R/W-0/0              | R/W-0/0          | R/W-0/0        | R/W-0/0            |  |  |

|------------------|----------------------------------------|--------------------------------------|---------------|----------------------|------------------|----------------|--------------------|--|--|

| CLKREN           | CLKROE                                 | CLKRSLR                              | CLKRE         | )C<1:0>              | (                | CLKRDIV<2:0>   | >                  |  |  |

| bit 7            |                                        |                                      |               |                      |                  |                | bit 0              |  |  |

| Legend:          |                                        |                                      |               |                      |                  |                |                    |  |  |

| R = Readable     | , hit                                  | W = Writable I                       | <b>.</b> :+   |                      | monted bit read  |                |                    |  |  |

|                  |                                        |                                      |               |                      | mented bit, read |                | - the set Decester |  |  |

| u = Bit is unc   | •                                      | x = Bit is unkn                      |               | -n/n = value a       | at POR and BO    | R/Value at all | other Resets       |  |  |

| '1' = Bit is set |                                        | '0' = Bit is clea                    | ared          |                      |                  |                |                    |  |  |

| bit 7            | CLKREN: Re                             | eference Clock I                     | Module Enable | e bit                |                  |                |                    |  |  |

|                  | 1 = Referen                            | ce clock module                      | is enabled    |                      |                  |                |                    |  |  |

|                  | 0 = Reference clock module is disabled |                                      |               |                      |                  |                |                    |  |  |

| bit 6            | CLKROE: R                              | eference Clock                       | Output Enable | e bit <sup>(3)</sup> |                  |                |                    |  |  |

|                  | 1 = Referen                            | ce Clock output                      | is enabled on | CLKR pin             |                  |                |                    |  |  |

|                  | 0 = Referen                            | ce Clock output                      | disabled on C | LKR pin              |                  |                |                    |  |  |

| bit 5            | CLKRSLR: F                             | Reference Clock                      | Slew Rate C   | ontrol Limiting      | Enable bit       |                |                    |  |  |

|                  | 1 = Slew Ra                            | te limiting is ena                   | abled         |                      |                  |                |                    |  |  |

|                  | 0 = Slew Ra                            | te limiting is dis                   | abled         |                      |                  |                |                    |  |  |

| bit 4-3          | CLKRDC<1:                              | 0>: Reference (                      | Clock Duty Cy | cle bits             |                  |                |                    |  |  |

|                  | 11 = Clock outputs duty cycle of 75%   |                                      |               |                      |                  |                |                    |  |  |

|                  |                                        | 10 = Clock outputs duty cycle of 50% |               |                      |                  |                |                    |  |  |

|                  |                                        | outputs duty cyc                     |               |                      |                  |                |                    |  |  |

|                  |                                        | outputs duty cyc                     |               |                      |                  |                |                    |  |  |

| bit 2-0          |                                        | :0> Reference (                      |               | oits                 |                  |                |                    |  |  |

|                  |                                        | clock value divid                    |               |                      |                  |                |                    |  |  |

|                  |                                        | clock value divid                    |               |                      |                  |                |                    |  |  |

|                  |                                        | clock value divid                    |               |                      |                  |                |                    |  |  |

|                  |                                        | clock value divid                    |               |                      |                  |                |                    |  |  |

|                  |                                        | clock value divid                    |               |                      |                  |                |                    |  |  |

|                  | 001 = Base                             | clock value divid                    |               |                      |                  |                |                    |  |  |

|                  | 000 = Base                             |                                      |               |                      |                  |                |                    |  |  |

- 2: In this mode, the duty cycle will always be equal to the source clock duty cycle, unless a duty cycle of 0% is selected.

- **3:** To route CLKR to pin, CLKOUTEN of Configuration Words = 1 is required. CLKOUTEN of Configuration Words = 0 will result in Fosc/4. See Section 6.3 "Conflicts with the CLKR pin" for details.

#### EXAMPLE 11-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG ADDR HI : PROG ADDR LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELEEADRL; Select Bank for EEPROM registersMOVLWPROG_ADDR_LO;MOVWFEEADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWLEEADRH; Store MSB of address

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

; Initiate read

BSF

EECON1,RD

NOP

; Executed (Figure 11-1)

NOP

; Ignored (Figure 11-1)

BSF

INTCON, GIE

; Restore interrupts

EEDATL,W

MOVF

; Get LSB of word

MOVWF

PROG_DATA_LO ; Store in user location

EEDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in user location

MOVE

MOVWF

```

### **19.3 Comparator Hysteresis**

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

# 19.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 19.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from either comparator, C1 or C2, can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 19-2) and the Timer1 Block Diagram (Figure 21-1) for more information.

### **19.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a Falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

# 19.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- C1IN+ or C12IN+ analog pin

- DAC

- FVR (Fixed Voltage Reference)

- · Vss (Ground)

See Section TABLE 14-1: "Summary of Registers Associated with the Fixed Voltage Reference" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

| U-0             | U-0                  | U-0                                                                                                                                                                    | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-1/1      |  |  |  |  |

|-----------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|--------------|--|--|--|--|

| _               | —                    | _                                                                                                                                                                      | STRxSYNC         | STRxD           | STRxC             | STRxB            | STRxA        |  |  |  |  |

| bit 7           |                      |                                                                                                                                                                        |                  | •               | •                 | •                | bit (        |  |  |  |  |

|                 |                      |                                                                                                                                                                        |                  |                 |                   |                  |              |  |  |  |  |

| Legend:         |                      |                                                                                                                                                                        |                  |                 |                   |                  |              |  |  |  |  |

| R = Readab      | le bit               | W = Writable                                                                                                                                                           | bit              | U = Unimpler    | mented bit, read  | d as '0'         |              |  |  |  |  |

| u = Bit is un   | changed              | x = Bit is unk                                                                                                                                                         | nown             | -n/n = Value a  | at POR and BC     | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is se | et                   | '0' = Bit is cle                                                                                                                                                       | eared            |                 |                   |                  |              |  |  |  |  |

|                 |                      |                                                                                                                                                                        |                  |                 |                   |                  |              |  |  |  |  |

| bit 7-5         | Unimplemen           | Unimplemented: Read as '0'                                                                                                                                             |                  |                 |                   |                  |              |  |  |  |  |

| bit 4           |                      | Steering Sync                                                                                                                                                          |                  |                 |                   |                  |              |  |  |  |  |

|                 |                      | <ul> <li>1 = Output steering update occurs on next PWM period</li> <li>0 = Output steering update occurs at the beginning of the instruction cycle boundary</li> </ul> |                  |                 |                   |                  |              |  |  |  |  |

|                 | -                    |                                                                                                                                                                        |                  | eginning of the | e instruction cyc | cle boundary     |              |  |  |  |  |

| bit 3           |                      | ering Enable bi                                                                                                                                                        |                  |                 |                   |                  |              |  |  |  |  |

|                 | •                    | 1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0>                                                                                                 |                  |                 |                   |                  |              |  |  |  |  |

|                 | •                    | 0 = PxD pin is assigned to port pin                                                                                                                                    |                  |                 |                   |                  |              |  |  |  |  |

| bit 2           |                      | ering Enable bi                                                                                                                                                        |                  |                 |                   |                  |              |  |  |  |  |

|                 |                      |                                                                                                                                                                        | waveform with p  | olarity control | from CCPxM<       | 1:0>             |              |  |  |  |  |

|                 | •                    | s assigned to                                                                                                                                                          | •                |                 |                   |                  |              |  |  |  |  |

| bit 1           | STRxB: Stee          | STRxB: Steering Enable bit B                                                                                                                                           |                  |                 |                   |                  |              |  |  |  |  |

|                 | 1 <b>= PxB pin h</b> | has the PWM                                                                                                                                                            | vaveform with p  | olarity control | from CCPxM<       | 1:0>             |              |  |  |  |  |

|                 | 0 = PxB pin is       | 0 = PxB pin is assigned to port pin                                                                                                                                    |                  |                 |                   |                  |              |  |  |  |  |

| bit 0           | STRxA: Stee          | ering Enable bi                                                                                                                                                        | t A              |                 |                   |                  |              |  |  |  |  |

|                 | 1 <b>= PxA pin h</b> | has the PWM                                                                                                                                                            | vaveform with p  | olarity control | from CCPxM<       | 1:0>             |              |  |  |  |  |

|                 | 0 = PxA pin i        | s assigned to                                                                                                                                                          | port pin         |                 |                   |                  |              |  |  |  |  |

| Note 1. T       | he PWM Steerin       | a mode is ava                                                                                                                                                          | ilable only wher |                 | N register bite ( | ~~DvM~2·2> -     | - 11 and     |  |  |  |  |

# **REGISTER 24-5: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

© 2011-2013 Microchip Technology Inc.

| Name    | Bit 7     | Bit 6   | Bit 5  | Bit 4       | Bit 3         | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-----------|---------|--------|-------------|---------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL   | SDO1SEL | SS1SEL | P2BSEL      | CCP2SEL       | P1DSEL | P1CSEL | CCP1SEL | 118                 |

| APFCON1 | —         | _       | _      | _           | _             | _      | _      | TXCKSEL | 118                 |

| BAUDCON | ABDOVF    | RCIDL   |        | SCKP        | BRG16         |        | WUE    | ABDEN   | 298                 |

| INTCON  | GIE       | PEIE    | TMR0IE | INTE        | IOCE          | TMR0IF | INTF   | IOCF    | 88                  |

| PIE1    | TMR1GIE   | ADIE    | RCIE   | TXIE        | SSP1IE        | CCP1IE | TMR2IE | TMR1IE  | 89                  |

| PIR1    | TMR1GIF   | ADIF    | RCIF   | TXIF        | SSP1IF        | CCP1IF | TMR2IF | TMR1IF  | 93                  |

| RCREG   |           |         | EU     | SART Receiv | ve Data Regis | ter    |        |         | 292*                |

| RCSTA   | SPEN      | RX9     | SREN   | CREN        | ADDEN         | FERR   | OERR   | RX9D    | 297                 |

| SPBRGL  |           |         |        | BRG         | <7:0>         |        |        |         | 299*                |

| SPBRGH  | BRG<15:8> |         |        |             |               |        |        | 299*    |                     |

| TRISB   | TRISB7    | TRISB6  | TRISB5 | TRISB4      | TRISB3        | TRISB2 | TRISB1 | TRISB0  | 126                 |

| TXSTA   | CSRC      | TX9     | TXEN   | SYNC        | SENDB         | BRGH   | TRMT   | TX9D    | 296                 |

# TABLE 26-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Asynchronous Reception.

\* Page provides register information.

## 26.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

### 26.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 26-7), and asynchronously if the device is in Sleep mode (Figure 26-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 26.3.3.1 Special Considerations

Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

### 26.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 26.4.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.4.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

# TABLE 26-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name                                | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|-------------------------------------|---------|---------|--------|--------|---------|--------|--------|---------|---------------------|

| APFCON0                             | RXDTSEL | SDO1SEL | SS1SEL | P2BSEL | CCP2SEL | P1DSEL | P1CSEL | CCP1SEL | 118                 |

| APFCON1                             | _       | _       | _      | _      | _       | _      | _      | TXCKSEL | 118                 |

| BAUDCON                             | ABDOVF  | RCIDL   | —      | SCKP   | BRG16   | _      | WUE    | ABDEN   | 298                 |

| INTCON                              | GIE     | PEIE    | TMR0IE | INTE   | IOCE    | TMR0IF | INTF   | IOCF    | 88                  |

| PIE1                                | TMR1GIE | ADIE    | RCIE   | TXIE   | SSP1IE  | CCP1IE | TMR2IE | TMR1IE  | 89                  |

| PIR1                                | TMR1GIF | ADIF    | RCIF   | TXIF   | SSP1IF  | CCP1IF | TMR2IF | TMR1IF  | 93                  |

| RCSTA                               | SPEN    | RX9     | SREN   | CREN   | ADDEN   | FERR   | OERR   | RX9D    | 297                 |

| TRISB                               | TRISB7  | TRISB6  | TRISB5 | TRISB4 | TRISB3  | TRISB2 | TRISB1 | TRISB0  | 126                 |

| TXREG EUSART Transmit Data Register |         |         |        |        |         |        |        | 289*    |                     |

| TXSTA                               | CSRC    | TX9     | TXEN   | SYNC   | SENDB   | BRGH   | TRMT   | TX9D    | 296                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Transmission. \* Page provides register information.

# 26.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 26.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 26.4.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 26.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 26.4.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

### 26.5.3 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a Reset, see Section 12.1 "Alternate Pin Function" for more information.

| Mnen                | nonic, | Description                                   | Cycles |     | 14-Bit | Opcode | Ð    | Status   | Notes |

|---------------------|--------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands            |        | Description                                   | Cycles | MSb | MSb    |        | LSb  | Affected | Notes |

|                     |        | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA                 | k      | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW                 | -      | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL                | k      | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW               | -      | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO                | k      | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE              | k      | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW               | k      | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN              | -      | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| INHERENT OPERATIONS |        |                                               |        |     |        |        |      |          |       |

| CLRWDT              | -      | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP                 | -      | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION              | -      | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET               | -      | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP               | -      | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS                | f      | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|                     |        | C-COMPILER OPT                                | IMIZED |     |        |        |      |          |       |

| ADDFSR              | n, k   | Add Literal k to FSRn                         | 1      | 11  | 0001   | Onkk   | kkkk |          |       |

| MOVIW               | n mm   | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|                     |        | modifier, mm                                  |        |     |        |        |      |          |       |

|                     | k[n]   | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | Onkk   | kkkk | Z        | 2     |

| MOVWI               | n mm   | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 1nmm |          | 2, 3  |

|                     |        | modifier, mm                                  |        |     |        |        |      |          |       |

|                     | k[n]   | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   | kkkk |          | 2     |

### TABLE 29-3: DEVICE(S) ENHANCED INSTRUCTION SET (CONTINUED)

Note 1:If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See Table in the MOVIW and MOVWI instruction descriptions.

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<6:3>) \rightarrow PC<14:11> \end{array}$                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT           | Clear Watchdog Timer                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRWDT                                                                                                           |

| Operands:        | None                                                                                                                              |

| Operation:       | $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$ |

| Status Affected: | TO, PD                                                                                                                            |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT.<br>Status bits TO and PD are set.  |

| CALLW                            | Subroutine Call With W                                                                                                                                                                                                                            | COMF             | Complement f                                                                                                                                                  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                          | [ label ] CALLW                                                                                                                                                                                                                                   | Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                     |  |  |

| Operands:                        | None                                                                                                                                                                                                                                              | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                            |  |  |

| Operation:                       | $\begin{array}{l} (PC) +1 \rightarrow TOS, \\ (W) \rightarrow PC < 7:0 >, \end{array}$                                                                                                                                                            | Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |  |  |

|                                  | $(PCLATH<6:0>) \rightarrow PC<14:8>$                                                                                                                                                                                                              | Status Affected: | Z                                                                                                                                                             |  |  |

| Status Affected:<br>Description: | None<br>Subroutine call with W. First, the<br>return address (PC + 1) is pushed<br>onto the return stack. Then, the con-<br>tents of W is loaded into PC<7:0>,<br>and the contents of PCLATH into<br>PC<14:8>. CALLW is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| DECF             | Decrement f                                                                                                                                       |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |  |  |  |  |

| Status Affected: | Z                                                                                                                                                 |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |

| CLRW             | Clear W                                                                                    |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CLRW                                                                      |  |  |  |  |

| Operands:        | None                                                                                       |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |  |  |  |  |

| Status Affected: | Z                                                                                          |  |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                              |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                          |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $TOS \rightarrow PC,$<br>1 $\rightarrow$ GIE                                                                                                                                                                       |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                               |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                  |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                             |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                             |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |  |  |  |

| Operands:        | None                                                                                                                                                  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |  |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                      | RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |

| Operands:        | 0 ≤ k ≤ 255                                                                                                                                                                   | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  | Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                          | Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                             |                  | C Register f                                                                                                                                                                                                      |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                             | Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |

| Example:         | CALL TABLE;W contains table<br>;offset value                                                                                                                                  | Cycles:          | 1                                                                                                                                                                                                                 |  |  |  |  |

|                  | <ul> <li>;W now has table value</li> </ul>                                                                                                                                    | Example:         | RLF REG1,0                                                                                                                                                                                                        |  |  |  |  |

| TABLE            | •<br>•<br>ADDWF PC ;W = offset<br>RETLW kl ;Begin table                                                                                                                       |                  | Before Instruction           REG1         =         1110         0110           C         =         0           After Instruction                                                                                 |  |  |  |  |

|                  | RETLW k2 ;<br>•                                                                                                                                                               |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |

|                  |                                                                                                                                                                               |                  | W = 1100 1100                                                                                                                                                                                                     |  |  |  |  |

|                  | •<br>RETLW kn ; End of table                                                                                                                                                  |                  | C = 1                                                                                                                                                                                                             |  |  |  |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                        |                  |                                                                                                                                                                                                                   |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                        |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit<br>literal 'k'. The result is placed in the<br>W register. |  |  |  |  |  |

| TRIS                                                               | Load TRIS Register with W                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                            | [ <i>label</i> ] TRIS f                                                                                         | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |

| Operands:                                                          | $5 \le f \le 7$                                                                                                 | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |

| Operation: $(W) \rightarrow TRIS$ register 'f'Status Affected:None |                                                                                                                 | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |

| Description:                                                       | Move data from W register to TRIS                                                                               | Status Affected: | Z                                                                                                                                                                               |  |  |

|                                                                    | register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |

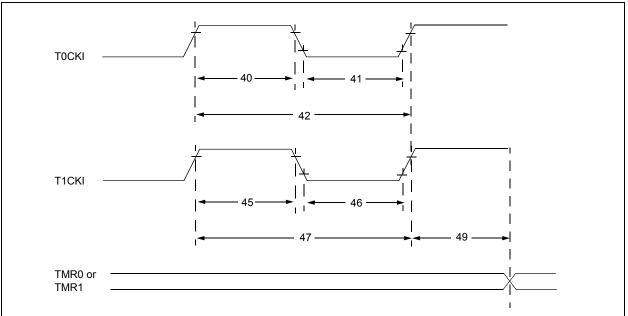

| TABLE 30-12: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standa        | rd Operating | Conditions (u                                        | nless otherwis                                                                           | e stated)      |                                           |        |        |       |                        |

|---------------|--------------|------------------------------------------------------|------------------------------------------------------------------------------------------|----------------|-------------------------------------------|--------|--------|-------|------------------------|

| Param.<br>No. | Sym.         | Characteristic                                       |                                                                                          |                | Min.                                      | Тур†   | Max.   | Units | Conditions             |

| 40*           | T⊤0H         | T0CKI High F                                         | Pulse Width                                                                              | No Prescaler   | 0.5 Tcy + 20                              | _      | _      | ns    |                        |

|               |              | -                                                    |                                                                                          | With Prescaler | 10                                        | _      |        | ns    |                        |

| 41*           | T⊤0L         | T0CKI Low F                                          | ulse Width                                                                               | No Prescaler   | 0.5 Tcy + 20                              | _      | _      | ns    |                        |