Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 15                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1847t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC16(L)F1847: Data Memory, Program Memory and Data EEPROM Memory<sup>(1)</sup>.

- Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Device Memory Maps

- Special Function Registers Summary

- Data EEPROM memory<sup>(1)</sup>

Note 1: The Data EEPROM Memory and the method to access Flash memory through the EECON registers is described in Section 11.0 "Data EEPROM and Flash Program Memory Control". The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a  $32K \times 14$  program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1847 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

#### TABLE 3-1:DEVICE SIZES AND ADDRESSES

| Device        | Program Memory Space (Words) | Last Program Memory Address |

|---------------|------------------------------|-----------------------------|

| PIC16(L)F1847 | 8,192                        | 1FFFh                       |

| FIGURE 5-7:            | INTERNAL OSCILLATOR SWITCH TIMING                                     |

|------------------------|-----------------------------------------------------------------------|

|                        |                                                                       |

| HFINTOSC/→<br>MFINTOSC | LFINTOSC (FSCM and WDT disabled)                                      |

| HFINTOSC/<br>MFINTOSC  |                                                                       |

| LFINTOSC               |                                                                       |

| IRCF <3:0>             | $\neq 0$ $= 0$                                                        |

| System Clock           |                                                                       |

|                        |                                                                       |

|                        | LFINTOSC (Either FSCM or WDT enabled)                                 |

| MFINTOSC               |                                                                       |

| HFINTOSC/<br>MFINTOSC  |                                                                       |

| LFINTOSC               |                                                                       |

| IRCF <3:0>             | $\neq 0$ $X = 0$                                                      |

| System Clock           |                                                                       |

|                        |                                                                       |

|                        | HFINTOSC/MFINTOSC                                                     |

|                        | LFINTOSC/MFINTOSC<br>LFINTOSC turns off unless WDT or FSCM is enabled |

| LFINTOSC               |                                                                       |

|                        | Start-up Time '2-cycle Sync ' Running                                 |

| HFINTOSC/<br>MFINTOSC  |                                                                       |

| IRCF <3:0>             | = 0 × ≠ 0                                                             |

| System Clock           |                                                                       |

|                        |                                                                       |

|                        |                                                                       |

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH REFERENCE CLOCK SOURCES

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3                    | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |  |  |  |  |

|---------|--------|--------|---------|-------|--------------------------|-------|-------|-------|---------------------|--|--|--|--|

| CLKRCON | CLKREN | CLKROE | CLKRSLR | CLKRI | CLKRDC<1:0> CLKRDIV<2:0> |       |       |       |                     |  |  |  |  |

| Logondi |        |        |         |       |                          |       |       |       |                     |  |  |  |  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

#### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH REFERENCE CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | FOSC<2:0   |         |         | 46                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

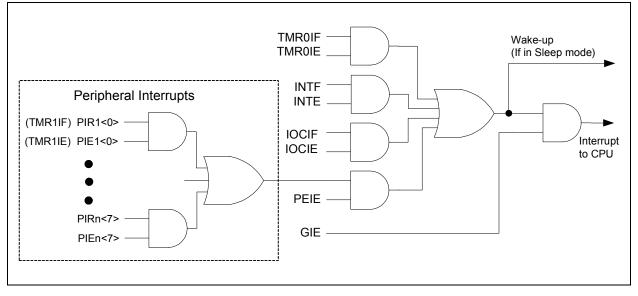

### 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce Interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 8-1.

#### FIGURE 8-1: INTERRUPT LOGIC

| TMR1GIE<br>bit 7<br>Legend:<br>R = Readable<br>u = Bit is uncha<br>'1' = Bit is set<br>bit 7<br>bit 6<br>bit 5<br>bit 5 | anged                           | RCIE<br>W = Writable<br>x = Bit is unkr<br>'0' = Bit is clea |                 | U = Unimpler    | CCP1IE          | TMR2IE           | TMR1IE<br>bit 0 |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------|-----------------|-----------------|-----------------|------------------|-----------------|

| Legend:<br>R = Readable<br>u = Bit is unch<br>'1' = Bit is set<br>bit 7<br>bit 6<br>bit 5                               | anged                           | x = Bit is unkr                                              |                 | U = Unimpler    | mented hit road |                  | bit (           |

| R = Readable<br>u = Bit is unch<br>'1' = Bit is set<br>bit 7<br>bit 6<br>bit 5                                          | anged                           | x = Bit is unkr                                              |                 | U = Unimpler    | mented hit road |                  |                 |

| R = Readable<br>u = Bit is unch<br>'1' = Bit is set<br>bit 7<br>bit 6<br>bit 5                                          | anged                           | x = Bit is unkr                                              |                 | U = Unimpler    | mented hit road |                  |                 |

| '1' = Bit is set<br>bit 7<br>bit 6<br>bit 5                                                                             |                                 |                                                              | nown            |                 | nemeu bit, redu | as '0'           |                 |

| bit 7<br>bit 6<br>bit 5                                                                                                 |                                 | '0' = Bit is clea                                            |                 | -n/n = Value a  | at POR and BOI  | R/Value at all o | ther Resets     |

| bit 6<br>bit 5                                                                                                          |                                 |                                                              | ared            |                 |                 |                  |                 |

| bit 6<br>bit 5                                                                                                          | I'MR1GIE Ti                     | mer1 Gate Inte                                               | rrunt Enable I  | hit             |                 |                  |                 |

| bit 5                                                                                                                   | 1 = Enables t                   | he Timer1 Gate                                               | e Acquisition i | nterrupt        |                 |                  |                 |

| bit 5                                                                                                                   |                                 | the Timer1 Gat                                               | •               | •               |                 |                  |                 |

|                                                                                                                         | -                               | -to-Digital Con                                              |                 | Interrupt Enabl | e bit           |                  |                 |

|                                                                                                                         |                                 | he ADC interru<br>the ADC interru                            |                 |                 |                 |                  |                 |

| bit 4                                                                                                                   | RCIE: USAR                      | T Receive Inter                                              | rupt Enable b   | it              |                 |                  |                 |

| bit 4                                                                                                                   |                                 | he USART rec                                                 |                 |                 |                 |                  |                 |

| bit 4                                                                                                                   | 0 = Disables                    | the USART rec                                                | eive interrupt  |                 |                 |                  |                 |

|                                                                                                                         |                                 | Transmit Inter                                               | •               |                 |                 |                  |                 |

|                                                                                                                         |                                 | he USART trar<br>the USART tra                               |                 |                 |                 |                  |                 |

| bit 3                                                                                                                   |                                 | chronous Seria                                               | •               |                 | nable bit       |                  |                 |

|                                                                                                                         | 1 = Enables t                   | he MSSP1 inte                                                | errupt          | , ,             |                 |                  |                 |

| hit 0                                                                                                                   |                                 | the MSSP1 inte                                               | •               |                 |                 |                  |                 |

| bit 2                                                                                                                   |                                 | P1 Interrupt En<br>he CCP1 interr                            |                 |                 |                 |                  |                 |

|                                                                                                                         |                                 | the CCP1 inter                                               |                 |                 |                 |                  |                 |

| bit 1                                                                                                                   | TMR2IE: TM                      | R2 to PR2 Mate                                               | ch Interrupt Ei | nable bit       |                 |                  |                 |

|                                                                                                                         |                                 | he Timer2 to P                                               |                 |                 |                 |                  |                 |

|                                                                                                                         |                                 | the Timer2 to F                                              |                 | •               |                 |                  |                 |

| bit 0                                                                                                                   |                                 | er1 Overflow Ir                                              |                 |                 |                 |                  |                 |

|                                                                                                                         |                                 | he Timer1 over<br>the Timer1 ove                             |                 |                 |                 |                  |                 |

|                                                                                                                         |                                 |                                                              |                 |                 |                 |                  |                 |

|                                                                                                                         | PEIE of the IN<br>to enable any |                                                              |                 |                 |                 |                  |                 |

#### REGISTER 8-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

#### 12.3 PORTA Registers

#### 12.3.1 DATA REGISTER

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-4). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA5, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize PORTA.

Reading the PORTA register (Register 12-3) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

#### 12.3.2 DIRECTION CONTROL

The TRISA register (Register 12-4) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | to configure an analog channel as a digital |  |  |  |  |  |  |  |  |  |  |

|       | input. Pins configured as analog inputs     |  |  |  |  |  |  |  |  |  |  |

|       | will read '0'.                              |  |  |  |  |  |  |  |  |  |  |

#### EXAMPLE 12-1: INITIALIZING PORTA

| BANKSEL PORTA  | ;                      |

|----------------|------------------------|

| CLRF PORTA     | ;Init PORTA            |

| BANKSEL LATA   | ;Data Latch            |

| CLRF LATA      | ;                      |

| BANKSEL ANSELA | ;                      |

| CLRF ANSELA    | ;digital I/O           |

| BANKSEL TRISA  | ;                      |

| MOVLW 0Ch      | ;Set RA<3:2> as inputs |

| MOVWF TRISA    | ;and set RA<7:4,1:0>   |

|                | ;as outputs            |

|                |                        |

#### 12.3.3 WEAK PULL-UPS

Each of the PORTA pins has an individually configurable internal weak pull-up. Control bit WPUA<5> enables or disables the pull-up (see Register 12-6). The weak pull-up is automatically turned off when the port pin is configured as an output. The <u>pull-up is</u> disabled on a Power-on Reset by the WPUEN bit of the OPTION\_REG register.

#### 12.3.4 ANALOG CONTROL

The ANSELA register (Register 12-7) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The TRISA register (Register 12-4) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

Note: The ANSELA register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

### 14.3 Register Definitions: FVR Control

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0             | R-q/q                                     | R/W-0/0                                                                                | R/W-0/0                            | R/W-0/0                          | R/W-0/0                                               | R/W-0/0          | R/W-0/0              |

|---------------------|-------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|----------------------------------|-------------------------------------------------------|------------------|----------------------|

| FVREN <sup>(1</sup> | ) FVRRDY <sup>(2)</sup>                   | TSEN <sup>(3)</sup>                                                                    | TSRNG <sup>(3)</sup>               | CDAFV                            | ′R<1:0> <sup>(1)</sup>                                | ADFVR            | <1:0> <sup>(1)</sup> |

| bit 7               | ·                                         |                                                                                        |                                    |                                  |                                                       |                  | bit (                |

|                     |                                           |                                                                                        |                                    |                                  |                                                       |                  |                      |

| Legend:             |                                           |                                                                                        |                                    |                                  |                                                       |                  |                      |

| R = Readal          | ole bit                                   | W = Writable                                                                           | bit                                | U = Unimpler                     | mented bit, read                                      | l as '0'         |                      |

| u = Bit is ur       | nchanged                                  | x = Bit is unk                                                                         | nown                               | -n/n = Value                     | at POR and BO                                         | R/Value at all c | other Resets         |

| '1' = Bit is s      | et                                        | '0' = Bit is cle                                                                       | ared                               | q = Value de                     | pends on condit                                       | ion              |                      |

| bit 7               | 1 = Fixed Vo                              | d Voltage Refe<br>Itage Referenc                                                       | e is enabled                       | bit <sup>(1)</sup>               |                                                       |                  |                      |

| bit 6               | FVRRDY: Fix                               | Itage Referenc<br>ed Voltage Re<br>Itage Referenc                                      | ference Ready                      | •                                |                                                       |                  |                      |

|                     |                                           | Itage Reference                                                                        |                                    |                                  | enabled                                               |                  |                      |

| bit 5               |                                           | erature Indicate                                                                       |                                    | )                                |                                                       |                  |                      |

|                     | 0 = Tempera                               | ture Indicator i<br>ture Indicator i                                                   | s disabled                         |                                  |                                                       |                  |                      |

| bit 4               | 1 = VOUT = V                              | perature Indica<br>/DD - 4VT (High<br>/DD - 2VT (Low                                   | n Range)                           | lection bit <sup>(3)</sup>       |                                                       |                  |                      |

| bit 3-2             |                                           | D>: Comparato                                                                          |                                    |                                  |                                                       |                  |                      |

|                     | 10 = Compar                               | ator FVR Buffe                                                                         | er Gain is 2x, w                   | vith output VCD                  | DAFVR = 4x VFVF<br>DAFVR = 2x VFVF<br>DAFVR = 1x VFVF | <sub>{</sub> (4) |                      |

|                     |                                           | ator FVR Buffe                                                                         |                                    |                                  |                                                       |                  |                      |

| bit 1-0             | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV | : ADC FVR Bu<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer is off | is 4x, with out<br>is 2x, with out | put VADFVR = 4<br>put VADFVR = 2 | 2x Vfvr <b><sup>(4)</sup></b>                         |                  |                      |

|                     | To minimize currer ng the Buffer Gair     |                                                                                        |                                    | R is disabled, t                 | he FVR buffers                                        | should be turne  | ed off by clear      |

- 2: FVRRDY is always '1' for the PIC16F1847 devices.

- 3: See Section 15.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR>1:0> |       | ADFVF | २<1:0> | 134                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

NOTES:

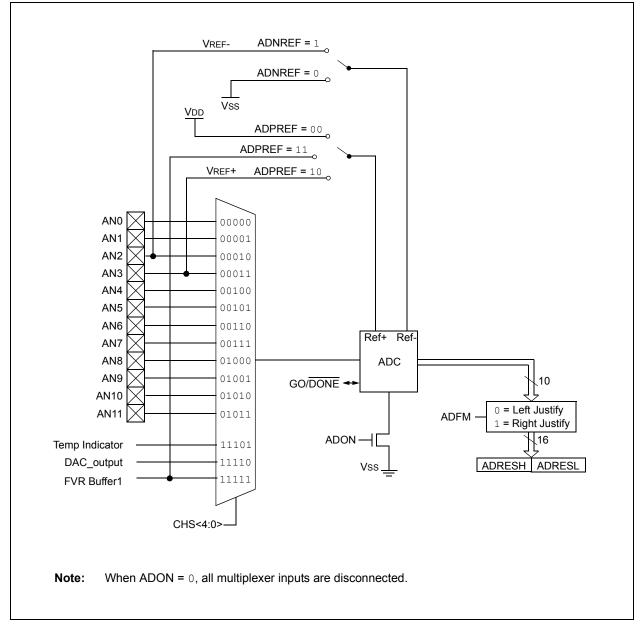

### 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC. The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### FIGURE 16-1: ADC BLOCK DIAGRAM

| R/W-0/0          | R/W-0/0      | R/W-0/0                              | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|--------------|--------------------------------------|-----------------|-------------------|------------------|----------------|--------------|

| SRSPE            | SRSCKE       | SRSC2E                               | SRSC1E          | SRRPE             | SRRCKE           | SRRC2E         | SRRC1E       |

| bit 7            |              |                                      |                 | -                 |                  |                | bit 0        |

|                  |              |                                      |                 |                   |                  |                |              |

| Legend:          |              |                                      |                 |                   |                  |                |              |

| R = Readable     | bit          | W = Writable                         | bit             | U = Unimpler      | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged        | x = Bit is unkr                      | nown            | -n/n = Value a    | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |              | '0' = Bit is cle                     | ared            |                   |                  |                |              |

|                  |              |                                      |                 |                   |                  |                |              |

| bit 7            |              | Latch Periphera                      |                 |                   |                  |                |              |

|                  |              | is set when the                      |                 |                   |                  |                |              |

|                  | •            | has no effect or                     | •               | of the SR latch   |                  |                |              |

| bit 6            |              | R Latch Set Clo                      |                 |                   |                  |                |              |

|                  |              | t of SR latch is<br>has no effect or |                 |                   | 1                |                |              |

| bit 5            |              | R Latch C2 Set                       |                 |                   |                  |                |              |

| bit o            |              | is set when the                      |                 | tor output is hi  | b                |                |              |

|                  |              |                                      |                 |                   | of the SR latch  |                |              |

| bit 4            | SRSC1E: SF   | R Latch C1 Set                       | Enable bit      |                   |                  |                |              |

|                  | 1 = SR latch | is set when the                      | e C1 Compara    | tor output is hig | gh               |                |              |

|                  | 0 = C1 Com   | parator output l                     | nas no effect o | n the set input   | of the SR latch  |                |              |

| bit 3            | SRRPE: SR    | Latch Peripher                       | al Reset Enabl  | e bit             |                  |                |              |

|                  |              | is reset when                        |                 | U U               |                  |                |              |

|                  | •            | has no effect or                     | •               |                   | tch              |                |              |

| bit 2            |              | R Latch Reset (                      |                 |                   |                  |                |              |

|                  |              | put of SR latch<br>has no effect or  |                 |                   | tch              |                |              |

| bit 1            |              | R Latch C2 Res                       | -               |                   |                  |                |              |

|                  | 1 = SR latch | is reset when                        | the C2 Compa    | rator output is   | high             |                |              |

|                  |              |                                      |                 |                   | out of the SR la | tch            |              |

| bit 0            | SRRC1E: SF   | R Latch C1 Res                       | et Enable bit   |                   |                  |                |              |

|                  |              | is reset when                        |                 |                   |                  |                |              |

|                  | 0 = C1 Com   | parator output I                     | nas no effect o | n the Reset inp   | out of the SR la | tch            |              |

|                  |              |                                      |                 |                   |                  |                |              |

#### REGISTER 18-2: SRCON1: SR LATCH CONTROL 1 REGISTER

| R/W-1/1         | R/W-1/1                  | R/W-1/1                                                                          | R/W-1/1                              | R/W-1/1      | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |  |  |  |

|-----------------|--------------------------|----------------------------------------------------------------------------------|--------------------------------------|--------------|------------------|------------------|--------------|--|--|--|--|--|

| WPUEN           | INTEDG                   | TMR0CS                                                                           | TMR0SE                               | PSA          |                  | PS<2:0>          |              |  |  |  |  |  |

| bit 7           |                          |                                                                                  |                                      |              |                  |                  | bit (        |  |  |  |  |  |

|                 |                          |                                                                                  |                                      |              |                  |                  |              |  |  |  |  |  |

| Legend:         |                          |                                                                                  |                                      |              |                  |                  |              |  |  |  |  |  |

| R = Readable    | e bit                    | W = Writabl                                                                      | e bit                                | U = Unimpler | mented bit, read | d as '0'         |              |  |  |  |  |  |

| u = Bit is unc  | hanged                   | x = Bit is un                                                                    | known                                | -n/n = Value | at POR and BC    | R/Value at all c | other Resets |  |  |  |  |  |

| '1' = Bit is se | t                        | '0' = Bit is c                                                                   | leared                               |              |                  |                  |              |  |  |  |  |  |

|                 |                          |                                                                                  |                                      |              |                  |                  |              |  |  |  |  |  |

| bit 7           |                          | eak Pull-up Er                                                                   |                                      |              | <b> </b> -    )  |                  |              |  |  |  |  |  |

|                 |                          |                                                                                  | lisabled (except<br>bled by individu | •            | ,                |                  |              |  |  |  |  |  |

| bit 6           | •                        | •                                                                                | •                                    |              | Valabo           |                  |              |  |  |  |  |  |

|                 |                          | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of RB0/INT pin |                                      |              |                  |                  |              |  |  |  |  |  |

|                 |                          |                                                                                  | e of RB0/INT p                       |              |                  |                  |              |  |  |  |  |  |

| bit 5           | TMR0CS: Ti               | TMR0CS: Timer0 Clock Source Select bit                                           |                                      |              |                  |                  |              |  |  |  |  |  |

|                 |                          | n on RA4/T00                                                                     |                                      |              |                  |                  |              |  |  |  |  |  |

|                 |                          | •                                                                                | le clock (Fosc/                      | 4)           |                  |                  |              |  |  |  |  |  |

| bit 4           |                          |                                                                                  | Edge Select bit                      |              |                  |                  |              |  |  |  |  |  |

|                 |                          | 0                                                                                | ow transition on<br>gh transition on | •            |                  |                  |              |  |  |  |  |  |

| bit 3           | PSA: Presca              | aler Assignme                                                                    | nt bit                               |              |                  |                  |              |  |  |  |  |  |

|                 |                          |                                                                                  | by the Timer0 m                      |              | e)               |                  |              |  |  |  |  |  |

|                 |                          |                                                                                  | ne Timer0 modu                       | le           |                  |                  |              |  |  |  |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pr | escaler Rate                                                                     | Select bits                          |              |                  |                  |              |  |  |  |  |  |

|                 | Bit                      | Value Timer                                                                      | 0 Rate                               |              |                  |                  |              |  |  |  |  |  |

|                 |                          | 000 1:                                                                           |                                      |              |                  |                  |              |  |  |  |  |  |

|                 |                          | 001 1:<br>010 1:                                                                 |                                      |              |                  |                  |              |  |  |  |  |  |

|                 |                          | 011 1:                                                                           | 16                                   |              |                  |                  |              |  |  |  |  |  |

|                 |                          |                                                                                  | 32<br>64                             |              |                  |                  |              |  |  |  |  |  |

|                 |                          | TAT 1.                                                                           | U <del>-1</del>                      |              |                  |                  |              |  |  |  |  |  |

#### REGISTER 20-1: OPTION\_REG: OPTION REGISTER

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

1:128

1:256

110 111

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0  | Register<br>on Page |

|------------|------------------------|--------|--------|--------|--------|---------|---------|--------|---------------------|

| CPSCON0    | CPSON                  | CPSRM  | —      | —      | CPSRN  | IG<1:0> | CPSOUT  | T0XCS  | 323                 |

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | IOCE   | TMR0IF  | INTF    | IOCF   | 88                  |

| OPTION_REG | WPUEN                  | INTEDG | TMR0CS | TMR0SE | PSA    |         | PS<2:0> |        | 175                 |

| TMR0       | Timer0 Module Register |        |        |        |        | 173*    |         |        |                     |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1  | TRISA0 | 120                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

#### 25.4.9 ACKNOWLEDGE SEQUENCE

The 9h SCLx pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDAx line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDAx line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCLx on the bus, the ACKTIM bit of the SSPx-CON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

#### 25.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSPx Slave mode operates in one of four modes selected in the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 25.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 25-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSPx Mask register (Register 25-5) affects the address matching process. See **Section 25.5.9 "SSPx Mask Register"** for more information.

#### 25.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 25.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCLx is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCLx is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 25.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the 9th bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see Section 25.5.6 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the 9th SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the 9th clock pulse.

#### 25.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 25.5.3.2 7-Bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 25-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

| R/W-0/0          | R-0/0                                                                                | R/W-0/0                                                                                                                                                        | R/S/HS-0/0                    | R/S/HS-0/0                            | R/S/HS-0/0        | R/S/HS-0/0       | R/W/HS-0/0   |  |

|------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------|-------------------|------------------|--------------|--|

| GCEN             | ACKSTAT                                                                              | ACKDT                                                                                                                                                          | ACKEN                         | RCEN                                  | PEN               | RSEN             | SEN          |  |

| bit 7            |                                                                                      |                                                                                                                                                                |                               |                                       |                   |                  | bit 0        |  |

|                  |                                                                                      |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

| Legend:          |                                                                                      |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

| R = Readable     | e bit                                                                                | W = Writable bit                                                                                                                                               |                               | U = Unimpler                          | mented bit, read  | l as '0'         |              |  |

| u = Bit is unch  | nanged                                                                               | x = Bit is unk                                                                                                                                                 | nown                          | -n/n = Value a                        | at POR and BO     | R/Value at all o | other Resets |  |

| '1' = Bit is set |                                                                                      | '0' = Bit is cle                                                                                                                                               | ared                          | HC = Cleared by hardware S = User set |                   |                  |              |  |

|                  |                                                                                      |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

| bit 7            |                                                                                      | eral Call Enable                                                                                                                                               |                               | .,                                    |                   |                  |              |  |

|                  |                                                                                      | terrupt when a<br>call address dis                                                                                                                             | •                             | ddress (0x00 d                        | or 00h) is receiv | ed in the SSP    | SR           |  |

| bit 6            | ACKSTAT: A                                                                           | cknowledge St                                                                                                                                                  | atus bit (in I <sup>2</sup> C | mode only)                            |                   |                  |              |  |

|                  |                                                                                      | edge was not r                                                                                                                                                 |                               |                                       |                   |                  |              |  |

| 1.1.F            |                                                                                      | edge was recei                                                                                                                                                 |                               |                                       |                   |                  |              |  |

| bit 5            |                                                                                      | nowledge Data                                                                                                                                                  | bit (in I <sup>2</sup> C mo   | de only)                              |                   |                  |              |  |

|                  | In Receive m                                                                         |                                                                                                                                                                | user initiates a              | an Acknowledg                         | e sequence at     | the end of a re  | ceive        |  |

|                  | 1 = Not Ackn                                                                         |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

|                  | 0 = Acknowledge                                                                      |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

| bit 4            | ACKEN: Acknowledge Sequence Enable bit (in I <sup>2</sup> C Master mode only)        |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

|                  |                                                                                      | In Master Receive mode:                                                                                                                                        |                               |                                       |                   |                  |              |  |

|                  | 1 = Initiate Acknowledge sequence on SDAx and SCLx pins, and transmit ACKDT data bit |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

|                  |                                                                                      | Automatically cleared by hardware.<br>0 = Acknowledge sequence idle                                                                                            |                               |                                       |                   |                  |              |  |

| bit 3            |                                                                                      | <b>RCEN:</b> Receive Enable bit (in $l^2$ C Master mode only)                                                                                                  |                               |                                       |                   |                  |              |  |

|                  |                                                                                      | $1 = \text{Enables Receive mode for } l^2C$                                                                                                                    |                               |                                       |                   |                  |              |  |

|                  | 0 = Receive i                                                                        | 0 = Receive idle                                                                                                                                               |                               |                                       |                   |                  |              |  |

| bit 2            | PEN: Stop Co                                                                         | ondition Enable                                                                                                                                                | e bit (in I <sup>2</sup> C Ma | ster mode only                        | y)                |                  |              |  |

|                  | SCKx Releas                                                                          |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

|                  | 1 = Initiate St<br>0 = Stop cond                                                     |                                                                                                                                                                | n SDAx and S                  | CLx pins. Auto                        | matically cleare  | d by hardware    |              |  |

| bit 1            | RSEN: Repe                                                                           | ated Start Con                                                                                                                                                 | dition Enable b               | oit (in I <sup>2</sup> C Mast         | er mode only)     |                  |              |  |

|                  |                                                                                      | <ul> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul> |                               |                                       |                   | y hardware.      |              |  |

| bit 0            | SEN: Start Condition Enable/Stretch Enable bit                                       |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

|                  | In Master mo                                                                         | de:                                                                                                                                                            |                               |                                       |                   |                  |              |  |

|                  | 1 = Initiate St<br>0 = Start cond                                                    |                                                                                                                                                                | n SDAx and S                  | CLx pins. Auto                        | matically cleare  | ed by hardware   |              |  |

|                  | In Slave mod                                                                         |                                                                                                                                                                |                               |                                       |                   |                  |              |  |

|                  |                                                                                      | etching is enat<br>etching is disal                                                                                                                            |                               | ave transmit ar                       | nd slave receive  | e (stretch enabl | ed)          |  |

| Note 1: Fo       | r bits ACKEN, F                                                                      | RCEN, PEN, R                                                                                                                                                   | SEN, SEN: If t                | he I <sup>2</sup> C module            | is not in the Idl | e mode, this bi  | t may not be |  |

#### **REGISTER 25-3:** SSPxCON2: SSPx CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

#### REGISTER 27-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0              | U-0                                             | U-0                | U-0         | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0    |

|------------------|-------------------------------------------------|--------------------|-------------|-----------------|-----------------|------------------|------------|

| _                | —                                               | —                  | _           |                 | CPSCH           | 1<3:0>           |            |

| bit 7            |                                                 |                    |             |                 |                 |                  | bit (      |

|                  |                                                 |                    |             |                 |                 |                  |            |

| Legend:          |                                                 |                    |             |                 |                 |                  |            |

| R = Readable     | e bit                                           | W = Writable bit   |             | U = Unimplem    | ented bit, read | as '0'           |            |

| u = Bit is unch  | nanged                                          | x = Bit is unkno   | own         | -n/n = Value at | POR and BOR     | /Value at all ot | ner Resets |

| '1' = Bit is set |                                                 | '0' = Bit is clear | ed          |                 |                 |                  |            |

|                  |                                                 |                    |             |                 |                 |                  |            |

| bit 7-4          | Unimplement                                     | ed: Read as '0'    |             |                 |                 |                  |            |

| bit 3-0          | -                                               | Capacitive Sens    | ing Channel | Select bits     |                 |                  |            |

|                  | If CPSON = $0$ :                                | •                  |             |                 |                 |                  |            |

|                  | These bits are ignored. No channel is selected. |                    |             |                 |                 |                  |            |

|                  | If $CPSON = 1$ :                                |                    |             |                 |                 |                  |            |

|                  |                                                 | Reserved. Do no    | t use.      |                 |                 |                  |            |

|                  | 1110 =                                          | Reserved. Do no    | t use.      |                 |                 |                  |            |

| 1101 <b>= F</b>  |                                                 | Reserved. Do no    | t use.      |                 |                 |                  |            |

| 1100 =           |                                                 | Reserved. Do no    | t use.      |                 |                 |                  |            |

|                  | 1011 =                                          | channel 11, (CPS   | 611)        |                 |                 |                  |            |

|                  | 1010 =                                          | channel 10, (CPS   | S10)        |                 |                 |                  |            |

|                  | 1001 =                                          | channel 9, (CPS    | 9)          |                 |                 |                  |            |

|                  | 1000 =                                          | channel 8, (CPS8   | 3)          |                 |                 |                  |            |

|                  | 0111 =                                          | channel 7, (CPS)   | 7)          |                 |                 |                  |            |

|                  | 0110 =                                          | channel 6, (CPS    | 5)          |                 |                 |                  |            |

|                  | 0101 =                                          | channel 5, (CPS    | 5)          |                 |                 |                  |            |

|                  | 0100 =                                          | channel 4, (CPS4   | 4)          |                 |                 |                  |            |

|                  | 0011 =                                          | channel 3, (CPS    | 3)          |                 |                 |                  |            |

|                  |                                                 | channel 2, (CPS2   |             |                 |                 |                  |            |

|                  | 0001 =                                          | channel 1, (CPS    | 1)          |                 |                 |                  |            |

|                  |                                                 |                    |             |                 |                 |                  |            |

### 29.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [label]ADDFSR FSRn, k                                                                         |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | ECDs is limited to the serve 0000h                                                            |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \to (W)$                                                                                             |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |