# E·XFL

### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2010                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 15                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1847t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIN ALLOCATION TABLE**

| TABLE 1: | 18/20/28- | PIN SUM | IMARY | (PIC1 | 6(L)F | 1847) |

|----------|-----------|---------|-------|-------|-------|-------|

|          |           |         |       |       |       |       |

|     |                  |             |                 |       |      |                 |           | •                         | • •      | ,               |                                                                           |                                                                                      |                                       |            |           |                  |                        |

|-----|------------------|-------------|-----------------|-------|------|-----------------|-----------|---------------------------|----------|-----------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|------------|-----------|------------------|------------------------|

| O/I | 18-Pin PDIP/SOIC | 20-Pin SSOP | 28-Pin QFN/UQFN | ANSEL | ADC  | Reference       | Cap Sense | Comparator                | SR Latch | Timers          | ссР                                                                       | EUSART                                                                               | dSSM                                  | Interrupt  | Modulator | Pull-up          | Basic                  |

| RA0 | 17               | 19          | 23              | Y     | AN0  | —               | CPS0      | C12IN0-                   | -        | _               |                                                                           | —                                                                                    | SDO2                                  | I          | —         | Ν                | —                      |

| RA1 | 18               | 20          | 24              | Y     | AN1  | —               | CPS1      | C12IN1-                   | —        | —               | _                                                                         | _                                                                                    | SS2                                   | -          | —         | Ν                | —                      |

| RA2 | 1                | 1           | 26              | Y     | AN2  | VREF-<br>DACOUT | CPS2      | C12IN2-<br>C12IN+         | _        | —               | —                                                                         | —                                                                                    | —                                     | _          | —         | Ν                | —                      |

| RA3 | 2                | 2           | 27              | Y     | AN3  | VREF+           | CPS3      | C12IN3-<br>C1IN+<br>C1OUT | SRQ      | —               | CCP3                                                                      | —                                                                                    | _                                     |            | —         | Ν                | —                      |

| RA4 | 3                | 3           | 28              | Υ     | AN4  | _               | CPS4      | C2OUT                     | SRNQ     | <b>T0CKI</b>    | CCP4                                                                      | _                                                                                    | _                                     |            | —         | Ν                | —                      |

| RA5 | 4                | 4           | 1               | Ν     |      |                 |           | —                         |          | -               |                                                                           | —                                                                                    | SS1 <sup>(1)</sup>                    |            | _         | Y <sup>(2)</sup> | MCLR<br>VPP            |

| RA6 | 15               | 17          | 20              | Ν     |      |                 | _         | _                         | _        | —               | P1D <sup>(1)</sup><br>P2B <sup>(1)</sup>                                  |                                                                                      | SDO1 <sup>(1)</sup>                   |            | _         | Ν                | OSC2<br>CLKOUT<br>CLKR |

| RA7 | 16               | 18          | 21              | Ν     |      |                 |           | _                         |          | _               | P1C <sup>(1)</sup><br>CCP2 <sup>(1)</sup><br>P2A <sup>(1)</sup>           | _                                                                                    |                                       |            | _         | Ν                | OSC1<br>CLKIN          |

| RB0 | 6                | 7           | 7               | N     | _    |                 | —         | —                         | SRI      | T1G             | CCP1 <sup>(1)</sup><br>P1A <sup>(1)</sup><br>FLT0                         | —                                                                                    |                                       | INT<br>IOC | -         | Y                | -                      |

| RB1 | 7                | 8           | 8               | Y     | AN11 | —               | CPS11     | —                         | _        | _               | _                                                                         | RX <sup>(1,3)</sup><br>DT <sup>(1,3)</sup>                                           | SDA1<br>SDI1                          | IOC        | —         | Y                | —                      |

| RB2 | 8                | 9           | 9               | Y     | AN10 |                 | CPS10     | _                         | _        | -               | _                                                                         | RX <sup>(1)</sup><br>DT <sup>(1)</sup><br>TX <sup>(1,3)</sup><br>CK <sup>(1,3)</sup> | SDA2<br>SDI2<br>SDO1 <sup>(1,3)</sup> | IOC        | MDMIN     | Y                | —                      |

| RB3 | 9                | 10          | 10              | Y     | AN9  | _               | CPS9      | —                         | _        | _               | CCP1 <sup>(1,3)</sup><br>P1A <sup>(1,3)</sup>                             | _                                                                                    | _                                     | IOC        | MDOUT     | Y                | —                      |

| RB4 | 10               | 11          | 12              | Y     | AN8  | -               | CPS8      | —                         | -        | -               |                                                                           | —                                                                                    | SCL1<br>SCK1                          | IOC        | MDCIN2    | Y                | —                      |

| RB5 | 11               | 12          | 13              | Y     | AN7  |                 | CPS7      | _                         | -        | _               | P1B                                                                       | TX <sup>(1)</sup><br>CK <sup>(1)</sup>                                               | SCL2<br>SCK2<br>SS1 <sup>(1,3)</sup>  | IOC        | _         | Y                | —                      |

| RB6 | 12               | 13          | 15              | Y     | AN5  | _               | CPS5      | —                         | _        | T1CKI<br>T1OSCI | $\begin{array}{c} P1C^{(1,3)} \\ CCP2^{(1,3)} \\ P2A^{(1,3)} \end{array}$ | —                                                                                    | —                                     | IOC        | _         | Y                | ICSPCLK                |

| RB7 | 13               | 14          | 16              | Y     | AN6  | _               | CPS6      | —                         | _        | T1OSCO          | P1D <sup>(1,3)</sup><br>P2B <sup>(1,3)</sup>                              |                                                                                      | —                                     | IOC        | MDCIN1    | Y                | ICSPDAT                |

| VDD | 14               | 15,<br>16   | 17,<br>19       |       |      | —               | -         | —                         | -        | —               | —                                                                         | —                                                                                    | —                                     | -          | —         |                  | VDD                    |

| Vss | 5                | 5,6         | 3,5             | _     | —    | _               | _         | _                         | _        | _               | _                                                                         | _                                                                                    | _                                     | _          | _         | —                | Vss                    |

Note 1:

Pin functions can be moved using th<u>e APF</u>CON register(s).

Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

Default function location.

# PIC16(L)F1847

NOTES:

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1847 are described within this data sheet. They are available in 18/20/28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1847 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1:DEVICE PERIPHERALSUMMARY

| Peripheral                     |        | PIC16(L)F1847 |

|--------------------------------|--------|---------------|

| ADC                            |        | •             |

| Capacitive Sensing Module      |        | •             |

| Digital-to-Analog Converter (I | DAC)   | •             |

| Digital Signal Modulator (DSN  | (N     | •             |

| EUSART                         |        | •             |

| Fixed Voltage Reference (FV    | R)     | •             |

| Reference Clock Module         |        | •             |

| SR Latch                       |        | •             |

| Capture/Compare/PWM Mod        |        |               |

|                                | ECCP1  | •             |

|                                | ECCP2  | •             |

|                                | CCP3   | •             |

|                                | CCP4   | •             |

| Comparators                    |        |               |

|                                | C1     | •             |

|                                | C2     | •             |

| Master Synchronous Serial P    | orts   |               |

|                                | MSSP1  | •             |

|                                | MSSP2  | •             |

| Timers                         |        |               |

|                                | Timer0 | •             |

|                                | Timer1 | •             |

|                                | Timer2 | •             |

|                                | Timer4 | •             |

|                                | Timer6 | •             |

### TABLE 3-3: PIC16(L)F1847 MEMORY MAP, BANKS 0-7

| IADL | .⊏ <b>ა</b> -ა: P | 1010( | ∟)Г104/ №1⊏1 | NOR  | I IVIAF, DAIN | N3 0- | -1        |      |           |      |           |      |           |      |           |

|------|-------------------|-------|--------------|------|---------------|-------|-----------|------|-----------|------|-----------|------|-----------|------|-----------|

|      | BANK 0            |       | BANK 1       |      | BANK 2        |       | BANK 3    |      | BANK 4    |      | BANK 5    |      | BANK 6    |      | BANK 7    |

| 000h | INDF0             | 080h  | INDF0        | 100h | INDF0         | 180h  | INDF0     | 200h | INDF0     | 280h | INDF0     | 300h | INDF0     | 380h | INDF0     |

| 001h | INDF1             | 081h  | INDF1        | 101h | INDF1         | 181h  | INDF1     | 201h | INDF1     | 281h | INDF1     | 301h | INDF1     | 381h | INDF1     |

| 002h | PCL               | 082h  | PCL          | 102h | PCL           | 182h  | PCL       | 202h | PCL       | 282h | PCL       | 302h | PCL       | 382h | PCL       |

| 003h | STATUS            | 083h  | STATUS       | 103h | STATUS        | 183h  | STATUS    | 203h | STATUS    | 283h | STATUS    | 303h | STATUS    | 383h | STATUS    |

| 004h | FSR0L             | 084h  | FSR0L        | 104h | FSR0L         | 184h  | FSR0L     | 204h | FSR0L     | 284h | FSR0L     | 304h | FSR0L     | 384h | FSR0L     |

| 005h | FSR0H             | 085h  | FSR0H        | 105h | FSR0H         | 185h  | FSR0H     | 205h | FSR0H     | 285h | FSR0H     | 305h | FSR0H     | 385h | FSR0H     |

| 006h | FSR1L             | 086h  | FSR1L        | 106h | FSR1L         | 186h  | FSR1L     | 206h | FSR1L     | 286h | FSR1L     | 306h | FSR1L     | 386h | FSR1L     |

| 007h | FSR1H             | 087h  | FSR1H        | 107h | FSR1H         | 187h  | FSR1H     | 207h | FSR1H     | 287h | FSR1H     | 307h | FSR1H     | 387h | FSR1H     |

| 008h | BSR               | 088h  | BSR          | 108h | BSR           | 188h  | BSR       | 208h | BSR       | 288h | BSR       | 308h | BSR       | 388h | BSR       |

| 009h | WREG              | 089h  | WREG         | 109h | WREG          | 189h  | WREG      | 209h | WREG      | 289h | WREG      | 309h | WREG      | 389h | WREG      |

| 00Ah | PCLATH            | 08Ah  | PCLATH       | 10Ah | PCLATH        | 18Ah  | PCLATH    | 20Ah | PCLATH    | 28Ah | PCLATH    | 30Ah | PCLATH    | 38Ah | PCLATH    |

| 00Bh | INTCON            | 08Bh  | INTCON       | 10Bh | INTCON        | 18Bh  | INTCON    | 20Bh | INTCON    | 28Bh | INTCON    | 30Bh | INTCON    | 38Bh | INTCON    |

| 00Ch | PORTA             | 08Ch  | TRISA        | 10Ch | LATA          | 18Ch  | ANSELA    | 20Ch | WPUA      | 28Ch | —         | 30Ch |           | 38Ch | —         |

| 00Dh | PORTB             | 08Dh  | TRISB        | 10Dh | LATB          | 18Dh  | ANSELB    | 20Dh | WPUB      | 28Dh | _         | 30Dh | —         | 38Dh | —         |

| 00Eh | _                 | 08Eh  | —            | 10Eh | -             | 18Eh  | _         | 20Eh | _         | 28Eh | _         | 30Eh | _         | 38Eh | —         |

| 00Fh | _                 | 08Fh  | —            | 10Fh | —             | 18Fh  | _         | 20Fh | _         | 28Fh | —         | 30Fh | —         | 38Fh | _         |

| 010h | _                 | 090h  | —            | 110h | _             | 190h  |           | 210h | _         | 290h | —         | 310h | _         | 390h | _         |

| 011h | PIR1              | 091h  | PIE1         | 111h | CM1CON0       | 191h  | EEADRL    | 211h | SSP1BUF   | 291h | CCPR1L    | 311h | CCPR3L    | 391h | _         |

| 012h | PIR2              | 092h  | PIE2         | 112h | CM1CON1       | 192h  | EEADRH    | 212h | SSP1ADD   | 292h | CCPR1H    | 312h | CCPR3H    | 392h | —         |

| 013h | PIR3              | 093h  | PIE3         | 113h | CM2CON0       | 193h  | EEDATL    | 213h | SSP1MSK   | 293h | CCP1CON   | 313h | CCP3CON   | 393h | —         |

| 014h | PIR4              | 094h  | PIE4         | 114h | CM2CON1       | 194h  | EEDATH    | 214h | SSP1STAT  | 294h | PWM1CON   | 314h |           | 394h | IOCBP     |

| 015h | TMR0              | 095h  | OPTION_REG   | 115h | CMOUT         | 195h  | EECON1    | 215h | SSPCON1   | 295h | CCP1AS    | 315h | _         | 395h | IOCBN     |

| 016h | TMR1L             | 096h  | PCON         | 116h | BORCON        | 196h  | EECON2    | 216h | SSPCON2   | 296h | PSTR1CON  | 316h | —         | 396h | IOCBF     |

| 017h | TMR1H             | 097h  | WDTCON       | 117h | FVRCON        | 197h  | —         | 217h | SSPCON3   | 297h |           | 317h | —         | 397h | _         |

| 018h | T1CON             | 098h  | OSCTUNE      | 118h | DACCON0       | 198h  | —         | 218h | —         | 298h | CCPR2L    | 318h | CCPR4L    | 398h | —         |

| 019h | T1GCON            | 099h  | OSCCON       | 119h | DACCON1       | 199h  | RCREG     | 219h | SSP2BUF   | 299h | CCPR2H    | 319h | CCPR4H    | 399h | —         |

| 01Ah | TMR2              | 09Ah  | OSCSTAT      | 11Ah | SRCON0        | 19Ah  | TXREG     | 21Ah | SSP2ADD   | 29Ah | CCP2CON   | 31Ah | CCP4CON   | 39Ah | CLKRCON   |

| 01Bh | PR2               | 09Bh  | ADRESL       | 11Bh | SRCON1        | 19Bh  | SPBRGL    | 21Bh | SSP2MSK   | 29Bh | PWM2CON   | 31Bh | —         | 39Bh | —         |

| 01Ch | T2CON             | 09Ch  | ADRESH       | 11Ch | _             | 19Ch  | SPBRGH    | 21Ch | SSP2STAT  | 29Ch | CCP2AS    | 31Ch | _         | 39Ch | MDCON     |

| 01Dh | _                 | 09Dh  | ADCON0       | 11Dh | APFCON0       | 19Dh  | RCSTA     | 21Dh | SSP2CON   | 29Dh | PSTR2CON  | 31Dh |           | 39Dh | MDSRC     |

| 01Eh | CPSCON0           | 09Eh  | ADCON1       | 11Eh | APFCON1       | 19Eh  | TXSTA     | 21Eh | SSP2CON2  | 29Eh | CCPTMRS   | 31Eh | _         | 39Eh | MDCARL    |

| 01Fh | CPSCON1           | 09Fh  | _            | 11Fh | _             | 19Fh  | BAUDCON   | 21Fh | SSP2CON3  | 29Fh | _         | 31Fh | —         | 39Fh | MDCARH    |

| 020h |                   | 0A0h  |              | 120h |               | 1A0h  |           | 220h |           | 2A0h |           | 320h |           | 3A0h |           |

|      | General           |       | General      |      | General       |       | General   |      | General   |      | General   |      | General   |      | General   |

|      | Purpose           |       | Purpose      |      | Purpose       |       | Purpose   |      | Purpose   |      | Purpose   |      | Purpose   |      | Purpose   |

|      | Register          |       | Register     |      | Register      |       | Register  |      | Register  |      | Register  |      | Register  |      | Register  |

|      | 80 Bytes          |       | 80 Bytes     |      | 80 Bytes      |       | 80 Bytes  |      | 80 Bytes  |      | 80 Bytes  |      | 80 Bytes  |      | 80 Bytes  |

| 06Fh |                   | 0EFh  |              | 16Fh |               | 1EFh  |           | 26Fh |           | 2EFh |           | 36Fh |           | 3EFh |           |

| 070h |                   | 0F0h  |              | 170h |               | 1F0h  |           | 270h |           | 2F0h |           | 370h |           | 3F0h |           |

|      |                   |       | Accesses     |      | Accesses      |       | Accesses  |      | Accesses  |      | Accesses  |      | Accesses  |      | Accesses  |

|      | Common RAM        |       | 70h – 7Fh    |      | 70h – 7Fh     |       | 70h – 7Fh |      | 70h – 7Fh |      | 70h – 7Fh |      | 70h – 7Fh |      | 70h – 7Fh |

| 07Fh |                   | 0FFh  |              | 17Fh |               | 1FFh  |           | 27Fh |           | 2FFh |           | 37Fh |           | 3FFh |           |

|      |                   | -     |              | •    |               |       |           |      |           | -    |           |      |           |      |           |

Legend: = Unimplemented data memory locations, read as '0'.

## TABLE 3-5: PIC16(L)F1847 MEMORY MAP, BANKS 16-23

| IADI | _E 3-3. FI    | 010  |               | NOR  | I WAF, DAN    | <b>N</b> 3 II | 0-23          |      |               |      |               |      |               |      |               |

|------|---------------|------|---------------|------|---------------|---------------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|

|      | BANK 16       |      | BANK 17       |      | BANK 18       |               | BANK 19       |      | BANK 20       |      | BANK 21       |      | BANK 22       |      | BANK 23       |

| 800h | INDF0         | 880h | INDF0         | 900h | INDF0         | 980h          | INDF0         | A00h | INDF0         | A80h | INDF0         | B00h | INDF0         | B80h | INDF0         |

| 801h | INDF1         | 881h | INDF1         | 901h | INDF1         | 981h          | INDF1         | A01h | INDF1         | A81h | INDF1         | B01h | INDF1         | B81h | INDF1         |

| 802h | PCL           | 882h | PCL           | 902h | PCL           | 982h          | PCL           | A02h | PCL           | A82h | PCL           | B02h | PCL           | B82h | PCL           |

| 803h | STATUS        | 883h | STATUS        | 903h | STATUS        | 983h          | STATUS        | A03h | STATUS        | A83h | STATUS        | B03h | STATUS        | B83h | STATUS        |

| 804h | FSR0L         | 884h | FSR0L         | 904h | FSR0L         | 984h          | FSR0L         | A04h | FSR0L         | A84h | FSR0L         | B04h | FSR0L         | B84h | FSR0L         |

| 805h | FSR0H         | 885h | FSR0H         | 905h | FSR0H         | 985h          | FSR0H         | A05h | FSR0H         | A85h | FSR0H         | B05h | FSR0H         | B85h | FSR0H         |

| 806h | FSR1L         | 886h | FSR1L         | 906h | FSR1L         | 986h          | FSR1L         | A06h | FSR1L         | A86h | FSR1L         | B06h | FSR1L         | B86h | FSR1L         |

| 807h | FSR1H         | 887h | FSR1H         | 907h | FSR1H         | 987h          | FSR1H         | A07h | FSR1H         | A87h | FSR1H         | B07h | FSR1H         | B87h | FSR1H         |

| 808h | BSR           | 888h | BSR           | 908h | BSR           | 988h          | BSR           | A08h | BSR           | A88h | BSR           | B08h | BSR           | B88h | BSR           |

| 809h | WREG          | 889h | WREG          | 909h | WREG          | 989h          | WREG          | A09h | WREG          | A89h | WREG          | B09h | WREG          | B89h | WREG          |

| 80Ah | PCLATH        | 88Ah | PCLATH        | 90Ah | PCLATH        | 98Ah          | PCLATH        | A0Ah | PCLATH        | A8Ah | PCLATH        | B0Ah | PCLATH        | B8Ah | PCLATH        |

| 80Bh | INTCON        | 88Bh | INTCON        | 90Bh | INTCON        | 98Bh          | INTCON        | A0Bh | INTCON        | A8Bh | INTCON        | B0Bh | INTCON        | B8Bh | INTCON        |

| 80Ch | —             | 88Ch | _             | 90Ch | _             | 98Ch          | _             | A0Ch | _             | A8Ch | —             | B0Ch | —             | B8Ch | —             |

| 80Dh | _             | 88Dh | _             | 90Dh | —             | 98Dh          | _             | A0Dh | —             | A8Dh | _             | B0Dh | _             | B8Dh | _             |

| 80Eh | —             | 88Eh | —             | 90Eh | —             | 98Eh          | —             | A0Eh | —             | A8Eh | —             | B0Eh | —             | B8Eh | _             |

| 80Fh | _             | 88Fh | _             | 90Fh | —             | 98Fh          | _             | A0Fh | —             | A8Fh | _             | B0Fh | _             | B8Fh | _             |

| 810h | —             | 890h | —             | 910h | —             | 990h          | —             | A10h | —             | A90h | —             | B10h | —             | B90h | _             |

| 811h | —             | 891h | —             | 911h | —             | 991h          | —             | A11h | —             | A91h | —             | B11h | —             | B91h | _             |

| 812h | _             | 892h | _             | 912h | —             | 992h          | _             | A12h | _             | A92h | —             | B12h | _             | B92h | _             |

| 813h | _             | 893h | _             | 913h | —             | 993h          | _             | A13h | _             | A93h | —             | B13h | _             | B93h | _             |

| 814h | _             | 894h | _             | 914h | —             | 994h          | _             | A14h | _             | A94h | —             | B14h | _             | B94h | _             |

| 815h | —             | 895h | —             | 915h | —             | 995h          | —             | A15h | —             | A95h | —             | B15h | —             | B95h | _             |

| 816h | _             | 896h | _             | 916h | —             | 996h          | _             | A16h | —             | A96h | _             | B16h | _             | B96h | _             |

| 817h | —             | 897h | —             | 917h | —             | 997h          | —             | A17h | —             | A97h | —             | B17h | —             | B97h | —             |

| 818h | —             | 898h | —             | 918h | —             | 998h          | —             | A18h | —             | A98h | —             | B18h | —             | B98h | —             |

| 819h | _             | 899h | _             | 919h | —             | 999h          | _             | A19h | —             | A99h | _             | B19h | _             | B99h | _             |

| 81Ah | _             | 89Ah | _             | 91Ah | —             | 99Ah          | _             | A1Ah | —             | A9Ah | _             | B1Ah | _             | B9Ah | _             |

| 81Bh | _             | 89Bh | —             | 91Bh | —             | 99Bh          | —             | A1Bh | —             | A9Bh | -             | B1Bh | _             | B9Bh | —             |

| 81Ch | —             | 89Ch | —             | 91Ch | —             | 99Ch          | —             | A1Ch | —             | A9Ch | —             | B1Ch | —             | B9Ch | —             |

| 81Dh | —             | 89Dh | —             | 91Dh | —             | 99Dh          | —             | A1Dh | —             | A9Dh | —             | B1Dh | —             | B9Dh | —             |

| 81Eh | —             | 89Eh | —             | 91Eh | —             | 99Eh          | —             | A1Eh | —             | A9Eh | —             | B1Eh | —             | B9Eh | _             |

| 81Fh | _             | 89Fh | _             | 91Fh | —             | 99Fh          | _             | A1Fh | _             | A9Fh | —             | B1Fh | _             | B9Fh | _             |

| 820h |               | 8A0h |               | 920h |               | 9A0h          |               | A20h |               | AA0h |               | B20h |               | BA0h |               |

|      |               |      |               |      |               |               |               |      |               |      |               |      |               |      |               |

|      | Unimplemented |      | Unimplemented |      | Unimplemented |               | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |

|      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |               | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |

|      |               |      |               |      |               |               |               |      |               |      |               |      |               |      |               |

| 86Fh |               | 8EFh |               | 96Fh |               | 9EFh          |               | A6Fh |               | AEFh |               | B6Fh |               | BEFh |               |

| 870h |               | 8F0h |               | 970h |               | 9F0h          |               | A70h |               | AF0h |               | B70h |               | BF0h |               |

|      | Accesses      |      | Accesses      |      | Accesses      |               | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |

|      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |               | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     | _    | 70h – 7Fh     |      | 70h – 7Fh     |

| 87Fh |               | 8FFh |               | 97Fh |               | 9FFh          |               | A7Fh |               | AFFh |               | B7Fh |               | BFFh |               |

PIC16(L)F1847

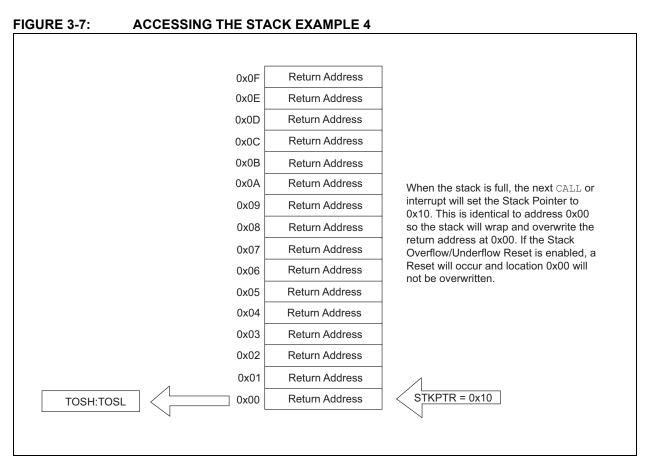

## 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is set to '1', the device will be reset if the stack is PUSHed beyond the 16th level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire data EEPROM will be erased when the code protection is turned off during an erase. Once the Data Code Protection bit is enabled, (CPD = 0), the Bulk Erase Program Memory Command (through ICSP) can disable the Data Code Protection (CPD = 1). When a Bulk Erase Program Memory Command is executed, the entire program Flash memory, data EEPROM and configuration memory will be erased.

## 11.6 Write/Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

### EXAMPLE 11-6: EEPROM WRITE/VERIFY

| BANKSEI | L EEDATL |    | ;                    |

|---------|----------|----|----------------------|

| MOVF    | EEDATL,  | W  | ;EEDATL not changed  |

|         |          |    | ;from previous write |

| BSF     | EECON1,  | RD | ;YES, Read the       |

|         |          |    | ;value written       |

| XORWF   | EEDATL,  | W  | ;                    |

| BTFSS   | STATUS,  | Ζ  | ;Is data the same    |

| GOTO    | WRITE_E  | RR | ;No, handle error    |

| :       |          |    | ;Yes, continue       |

| 1       |          |    |                      |

### 16.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- · ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined  |

|-------|---------------------------------------------|

|       | as a digital input may cause the input buf- |

|       | fer to conduct excess current.              |

### 16.1.2 CHANNEL SELECTION

There are up to 14 channel selections available:

- AN<11:0> pins

- DAC Output

- · FVR (Fixed Voltage Reference) Output

Refer to Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section TABLE 14-1: "Summary of Registers Associated with the Fixed Voltage Reference" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 16.2 "ADC Operation"** for more information.

### 16.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- VDD

- FVR 2.048V

- FVR 4.096V (Not available on LF devices)

The ADNREF bits of the ADCON1 register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See Section TABLE 14-1: "Summary of Registers Associated with the Fixed Voltage Reference" for more details on the Fixed Voltage Reference.

### 16.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal oscillator)

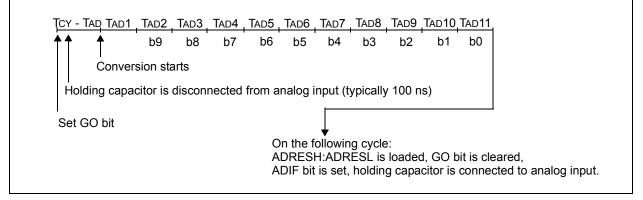

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 16-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in Section 30.0 "Electrical Specifications" for more information. Table 16-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) |                             |                             | Device Frequ                | uency (Fosc)                |                             |                             |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| ADC<br>Clock Source | ADCS<2.0>   |                             | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>      |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>      |

| Frc                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of  $1.6 \ \mu s$  for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

# PIC16(L)F1847

NOTES:

### 25.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 25-4.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See Section 25.2.3 "SPI Master Mode" for more detail.

### 25.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  Slave in 7-bit Addressing mode. Figure 25-14 and Figure 25-15 are used as visual references for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the Master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

# 25.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 25-16 displays a module using both address and data holding. Figure 25-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the 8th falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPx-CON3 register to determine if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an  $\overline{ACK}$ , not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the 9th falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to Master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after 8th falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSPSTAT register.

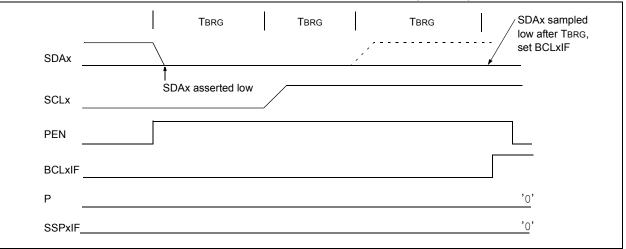

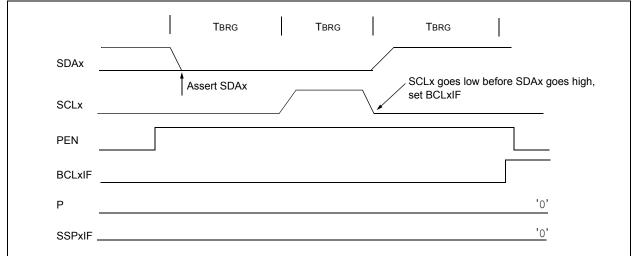

### 25.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out (Case 1).

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high (Case 2).

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 25-38). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 25-39).

### FIGURE 25-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 25-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

### REGISTER 25-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0                  | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                    | R/W-0/0                                                                                                                             | R/W-0/0                                                                                                                                                                                             | R/W-0/0                                                                                              | R/W-0/0                                    | R/W-0/0                                          | R/W-0/0                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------|---------------------------------------------|

| WCOL                        | SSPOV                                                                                                                                                                                                                                                                                                                         | SSPEN                                                                                                                               | СКР                                                                                                                                                                                                 |                                                                                                      | SSPM                                       | 1<3:0>                                           |                                             |

| pit 7                       |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                     |                                                                                                                                                                                                     |                                                                                                      |                                            |                                                  | bit (                                       |

| ogond:                      |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                     |                                                                                                                                                                                                     |                                                                                                      |                                            |                                                  |                                             |

| Legend:<br>R = Readable bit |                                                                                                                                                                                                                                                                                                                               | W = Writable bit                                                                                                                    |                                                                                                                                                                                                     | U = Unimplement                                                                                      | ed hit, read as '0'                        |                                                  |                                             |

| u = Bit is unchang          | ed                                                                                                                                                                                                                                                                                                                            | x = Bit is unknowr                                                                                                                  | <b>1</b>                                                                                                                                                                                            | •                                                                                                    | OR and BOR/Value                           | at all other Resets                              |                                             |

| 1' = Bit is set             | cu                                                                                                                                                                                                                                                                                                                            | '0' = Bit is cleared                                                                                                                |                                                                                                                                                                                                     | HS = Bit is set by                                                                                   |                                            | C = User cleared                                 |                                             |

|                             |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                     |                                                                                                                                                                                                     | TIS - DILIS SEL Dy                                                                                   | naruware                                   | C - Oser cleared                                 |                                             |

| pit 7                       | 0 = No collision<br><u>Slave mode:</u>                                                                                                                                                                                                                                                                                        | e SSPxBUF registe<br>JF register is written                                                                                         |                                                                                                                                                                                                     | while the I <sup>2</sup> C condi                                                                     |                                            |                                                  | to be started                               |

| Dit 6                       | In SPI mode:<br>1 = A new byte is<br>Overflow car<br>setting overf<br>SSPxBUF re<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is re                                                                                                                                                                          | n only occur in Slave<br>low. In Master mode<br>egister (must be clea<br>ceived while the St<br>eared in software).                 | SSPxBUF registe<br>e mode. In Slave<br>e, the overflow bit i<br>ared in software).                                                                                                                  | r is still holding the pr<br>mode, the user must<br>s not set since each r<br>is still holding the p | read the SSPxBUF,<br>lew reception (and tr | even if only transmit<br>ansmission) is initiate | ting data, to avoid<br>ad by writing to the |

| bit 5                       | In both modes, wi<br>In SPI mode:<br>1 = Enables series<br>0 = Disables series<br>1 = Enables the<br>1 = Enables the                                                                                                                                                                                                          | al port and configur<br>rial port and configu                                                                                       | pins must be pro<br>es SCKx, SDOx,<br>ures these pins a<br>gures the SDAx a                                                                                                                         | nd SCLx pins as the                                                                                  | source of the serial                       |                                                  |                                             |

| bit 4                       | 0 = Idle state for o<br><u>In I<sup>2</sup>C Slave mode</u><br>SCLx release con<br>1 = Enable clock                                                                                                                                                                                                                           | clock is a high level<br>clock is a low level<br><u>a:</u><br>trol<br>w (clock stretch). ('<br><u>de:</u>                           |                                                                                                                                                                                                     | lata setup time.)                                                                                    |                                            |                                                  |                                             |

| bit 3-0                     | 0000 = SPI Mast<br>0001 = SPI Mast<br>0010 = SPI Mast<br>0010 = SPI Slave<br>0101 = SPI Slave<br>0101 = SPI Slave<br>0101 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Maste<br>1010 = Reserved<br>1011 = I <sup>2</sup> C firmwa<br>1001 = Reserved<br>1101 = I <sup>2</sup> C Slave | mode, 7-bit addres<br>mode, 10-bit addre<br>er mode, clock = Fc<br>er mode, clock = Fc<br>are controlled Mast<br>mode, 7-bit addres | DSC/4<br>DSC/16<br>DSC/64<br>WR2 out <u>put/</u> 2<br>Kx pin, <u>SSx</u> pin of<br>Kx pin, <u>SSx</u> pin of<br>SS<br>DSC/(4 * (SSPxAE<br>DSC/(4 * (SSPxAE<br>er mode (Slave i<br>SS with Start and | control enabled<br>control disabled, SS;<br>DD+1)) <sup>(4)</sup><br>DD+1)) <sup>(5)</sup>           | nabled                                     | ) pin                                            |                                             |

| 2: Whe<br>3: Whe<br>4: SSF  | laster mode, the ove<br>en enabled, these pi<br>en enabled, the SDA<br>2xADD values of 0, 1<br>2xADD value of '0' is                                                                                                                                                                                                          | erflow bit is not set and<br>ns must be properly<br>and SCLx pins m<br>or 2 are not suppo                                           | since each new r<br>y configured as in<br>nust be configure<br>orted for I <sup>2</sup> C Mod                                                                                                       | eception (and trans<br>nput or output.<br>d as inputs.<br>e.                                         |                                            | by writing to the SS                             | PxBUF register.                             |

### REGISTER 25-5: SSPxMSK: SSPx MASK REGISTER

| R/W-1/1          | R/W-1/1                                                                 | R/W-1/1                            | R/W-1/1                           | R/W-1/1                                         | R/W-1/1                               | R/W-1/1                    | R/W-1/1      |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------|------------------------------------|-----------------------------------|-------------------------------------------------|---------------------------------------|----------------------------|--------------|--|--|--|--|--|

|                  |                                                                         |                                    | MSH                               | <<7:0>                                          |                                       |                            |              |  |  |  |  |  |

| bit 7            |                                                                         |                                    |                                   |                                                 |                                       |                            | bit 0        |  |  |  |  |  |

| <b></b>          |                                                                         |                                    |                                   |                                                 |                                       |                            |              |  |  |  |  |  |

| Legend:          |                                                                         |                                    |                                   |                                                 |                                       |                            |              |  |  |  |  |  |

| R = Readable     | bit                                                                     | W = Writable                       | bit                               | U = Unimpler                                    | mented bit, read                      | l as '0'                   |              |  |  |  |  |  |

| u = Bit is unch  | anged                                                                   | x = Bit is unkr                    | nown                              | -n/n = Value a                                  | at POR and BO                         | R/Value at all o           | other Resets |  |  |  |  |  |

| '1' = Bit is set |                                                                         | '0' = Bit is cle                   | ared                              |                                                 |                                       |                            |              |  |  |  |  |  |

|                  |                                                                         |                                    |                                   |                                                 |                                       |                            |              |  |  |  |  |  |

| bit 7-1          | MSK<7:1>:                                                               |                                    |                                   |                                                 |                                       | •                          |              |  |  |  |  |  |

|                  | 1 = The rec<br>0 = The rec                                              | eived address b<br>eived address b | it n is compai<br>it n is not use | red to SSPxADI<br>ed to detect I <sup>2</sup> C | D <n> to detect<br/>address match</n> | I <sup>2</sup> C address m | atch         |  |  |  |  |  |

| bit 0            | MSK<0>: M                                                               | ask bit for I <sup>2</sup> C S     | lave mode, 1                      | 0-bit Address                                   |                                       |                            |              |  |  |  |  |  |

|                  | I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111): |                                    |                                   |                                                 |                                       |                            |              |  |  |  |  |  |

|                  |                                                                         | eived address b                    |                                   |                                                 |                                       | I <sup>2</sup> C address m | atch         |  |  |  |  |  |

|                  | -                                                                       | eived address b                    |                                   |                                                 | address match                         |                            |              |  |  |  |  |  |

|                  | IFC Slave m                                                             | ode, 7-bit addre                   | ss, the bit is l                  | gnored                                          |                                       |                            |              |  |  |  |  |  |

## REGISTER 25-6: SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0         | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|--------------|

|                 |         |                 | ADD     | <7:0>          |                  |                  |              |

| bit 7           |         |                 |         |                |                  |                  | bit 0        |

|                 |         |                 |         |                |                  |                  |              |

| Legend:         |         |                 |         |                |                  |                  |              |

| R = Readable    | bit     | W = Writable I  | oit     | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch | anged   | x = Bit is unkn | own     | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

### Master mode:

1' = Bit is set

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCLx pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

'0' = Bit is cleared

### <u>10-Bit Slave mode — Most Significant Address byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### <u>10-Bit Slave mode — Least Significant Address byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

### 7-Bit Slave mode:

| bit 7-1 ADD<7:1>: 7-bit address |

|---------------------------------|

|---------------------------------|

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### TABLE 30-16: COMPARATOR SPECIFICATIONS<sup>(1)</sup>

| VDD = 3.0V, TA = 25°C |                      |                                            |      |          |      |          |                                            |

|-----------------------|----------------------|--------------------------------------------|------|----------|------|----------|--------------------------------------------|

| Param.<br>No.         | Sym.                 | Characteristics                            | Min. | Тур.     | Max. | Units    | Comments                                   |

| CM01                  | VIOFF                | Input Offset Voltage                       |      | ±7.5     | ±60  | mV       | CxSP = 1<br>Vicм = Vdd/2                   |

| CM02                  | VICM                 | Input Common Mode Voltage                  | 0    | _        | Vdd  | V        |                                            |

| CM03                  | CMRR                 | Common Mode Rejection Ratio                | _    | 50       | _    | dB       |                                            |

| CM04A                 |                      | Response Time Rising Edge                  |      | 400      | 800  | ns       | CxSP = 1                                   |

| CM04B                 | TRESP <sup>(2)</sup> | Response Time Falling Edge                 |      | 200      | 400  | ns       | CxSP = 1                                   |

| CM04C                 |                      | Response Time Rising Edge                  | _    | 1200     |      | ns       | <b>CxSP =</b> 0                            |

| CM04D                 |                      | Response Time Falling Edge                 |      | 550      |      | ns       | <b>CxSP =</b> 0                            |

| CM05                  | Тмс2о∨               | Comparator Mode Change to<br>Output Valid* | —    | —        | 10   | μS       |                                            |

| CM06                  | CHYSTER              | Comparator Hysteresis                      |      | 50<br>10 |      | mV<br>mV | CxHYS = 1, CxSP = 1<br>CxHYS = 1, CxSP = 0 |

These parameters are characterized but not tested.

Note 1: See Section 31.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to Vdd.

## TABLE 30-17: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS<sup>(1)</sup>

| Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |      |                              |      |        |       |       |          |

|-------------------------------------------------------------------------|------|------------------------------|------|--------|-------|-------|----------|

| Param.<br>No.                                                           | Sym. | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |

| DAC01*                                                                  | Clsb | Step Size                    | _    | VDD/32 | _     | V     |          |

| DAC02*                                                                  | CACC | Absolute Accuracy            | —    | —      | ± 1/2 | LSb   |          |

| DAC03*                                                                  | CR   | Unit Resistor Value (R)      | _    | 5000   |       | Ω     |          |

| DAC04*                                                                  | CST  | Settling Time <sup>(2)</sup> | _    | _      | 10    | μS    |          |

These parameters are characterized but not tested.

Note 1: See Section 31.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

# PIC16(L)F1847

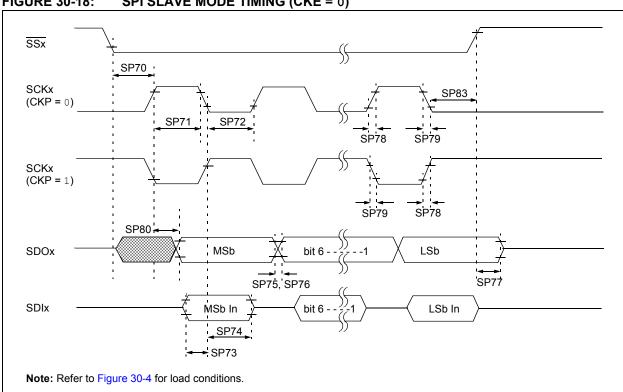

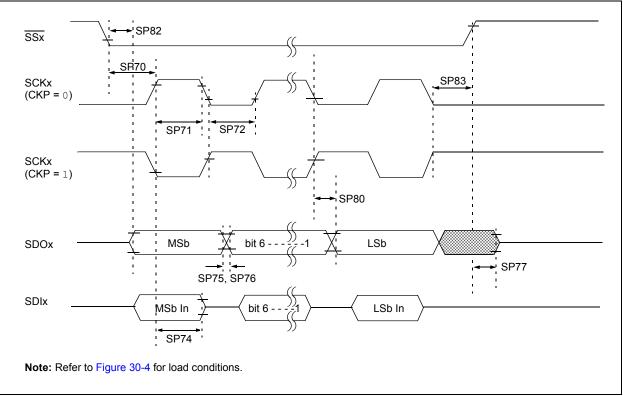

#### FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

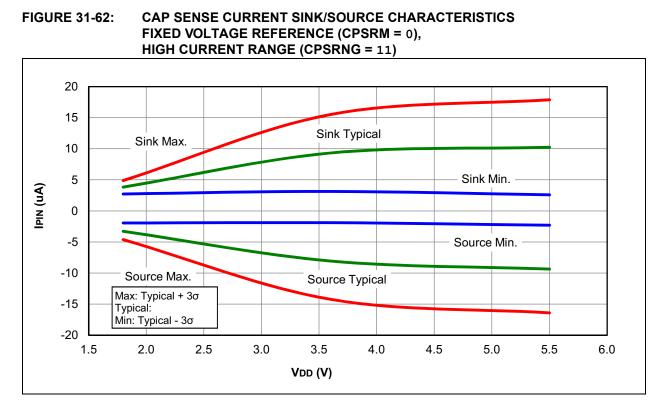

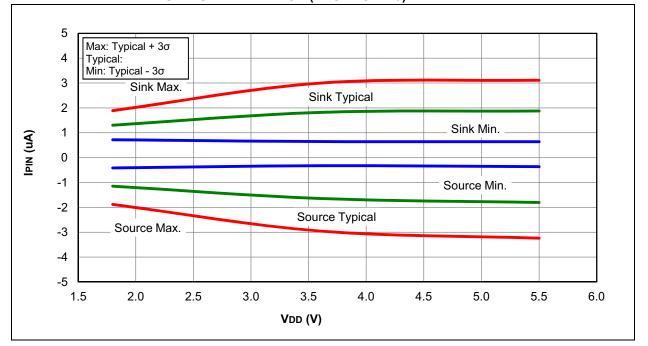

FIGURE 31-63: CAP SENSE CURRENT SINK/SOURCE CHARACTERISTICS FIXED VOLTAGE REFERENCE (CPSRM = 0), MEDIUM CURRENT RANGE (CPSRNG = 10)

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |      |      |  |

|-------------------------|--------|-------------|------|------|--|

| Dimension               | Limits | MIN         | NOM  | MAX  |  |

| Number of Pins          | N      | 28          |      |      |  |

| Pitch                   | е      | 0.65 BSC    |      |      |  |

| Overall Height          | A      | 0.80        | 0.90 | 1.00 |  |

| Standoff                | A1     | 0.00        | 0.02 | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF    |      |      |  |

| Overall Width           | E      | 6.00 BSC    |      |      |  |

| Exposed Pad Width       | E2     | 3.65        | 3.70 | 4.20 |  |

| Overall Length          | D      | 6.00 BSC    |      |      |  |

| Exposed Pad Length      | D2     | 3.65        | 3.70 | 4.20 |  |

| Terminal Width          | b      | 0.23        | 0.30 | 0.35 |  |

| Terminal Length         | L      | 0.50        | 0.55 | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20        | -    | -    |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support