# E. Fenesas Electronics America Inc - <u>R7FS5D97C2A01CBG#AC0 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                          |

|----------------------------|-------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                 |

| Core Size                  | 32-Bit Single-Core                                                                              |

| Speed                      | 120MHz                                                                                          |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, MMC/SD, QSPI, SCI, SPI, SSI, UART/USART, USB |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                                         |

| Number of I/O              | 133                                                                                             |

| Program Memory Size        | 1MB (1M x 8)                                                                                    |

| Program Memory Type        | FLASH                                                                                           |

| EEPROM Size                | 64K x 8                                                                                         |

| RAM Size                   | 640K x 8                                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                           |

| Oscillator Type            | Internal                                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                               |

| Mounting Type              | Surface Mount                                                                                   |

| Package / Case             | 176-LFBGA                                                                                       |

| Supplier Device Package    | 176-LFBGA (13x13)                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs5d97c2a01cbg-ac0           |

|                            |                                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 1. Overview

The S5D9 MCU integrates multiple series of software- and pin-compatible ARM<sup>®</sup>-based 32-bit MCUs that share the same set of Renesas peripherals to facilitate design scalability and efficient platform-based product development.

The MCU provides a high-performance ARM Cortex<sup>®</sup>-M4 core running up to 120 MHz with the following features:

- Up to 2-MB code flash memory

- 640-KB SRAM

- Graphics LCD Controller (GLCDC)

- 2D Drawing Engine (DRW)

- Capacitive Touch Sensing Unit (CTSU)

- Ethernet MAC Controller (ETHERC) with IEEE 1588 PTP, USBFS, USBHS, SD/MMC Host Interface

- Quad Serial Peripheral Interface (QSPI)

- Security and safety features

- Analog peripherals.

## 1.1 Function Outline

#### Table 1.1 ARM core

| Feature       | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM Cortex-M4 | <ul> <li>Maximum operating frequency: up to 120 MHz</li> <li>ARM Cortex-M4 core: <ul> <li>Revision: r0p1-01rel0</li> <li>ARMv7E-M architecture profile</li> <li>Single precision floating point unit compliant with the ANSI/IEEE Std 754-2008</li> </ul> </li> <li>ARM Memory Protection Unit (MPU): <ul> <li>ARMv7 Protected Memory System Architecture</li> <li>8 protect regions</li> </ul> </li> <li>SysTick timer: <ul> <li>Driven by LOCO clock</li> </ul> </li> </ul> |

#### Table 1.2 Memory

| Feature                      | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code flash memory            | Maximum 2 MB of code flash memory. See section 55, Flash Memory in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                       |

| Data flash memory            | 64 KB of data flash memory. See section 55, Flash Memory in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                              |

| Memory Mirror Function (MMF) | The MMF can be configured to mirror the wanted application image load address in code flash memory to the application image link address in the 23-bit unused memory space (memory mirror space addresses). Your application code is developed and linked to run from this MMF destination address. The application code does not need to know the load location where it is stored in code flash memory. See section 5, Memory Mirror Function (MMF) in User's Manual. |

| SRAM                         | On-chip high-speed SRAM providing either parity-bit or Error Correction Code (ECC). The first 32 KB of SRAM0 is subject to ECC. Parity check is performed for other areas. See section 53, SRAM in User's Manual.                                                                                                                                                                                                                                                       |

| Standby SRAM                 | On-chip SRAM that can retain data in Deep Software Standby mode. See section 54, Standby SRAM in User's Manual.                                                                                                                                                                                                                                                                                                                                                         |

#### Table 1.3 System (1 of 3)

| Feature         | Functional description                                                                                                    |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Operating modes | Two operating modes:<br>- Single-chip mode<br>- SCI or USB boot mode.<br>See section 3, Operating Modes in User's Manual. |  |  |  |  |  |

RENESAS

### Table 1.11 Graphics

| Feature                          | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Graphics LCD Controller (GLCDC)  | <ul> <li>The GLCDC provides multiple functions and supports various data formats and panels. Key GLCDC features include:</li> <li>GPX bus master function for accessing graphics data</li> <li>Superimposition of three planes (single color background plane, graphic 1 plane, and graphic 2 plane)</li> <li>Support for many types of 32- or 16-bit per pixel graphics data and 8-, 4-, or 1-bit LUT data format</li> <li>Digital interface signal output supporting a video image size of WVGA or greater. See section 58, Graphics LCD Controller (GLCDC) in User's Manual.</li> </ul> |  |  |  |  |  |  |

| 2D Drawing Engine (DRW)          | • Digital interface signal output supporting a video image size of WVGA or greater.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| JPEG Codec (JPEG)                | The JPEG Codec (JPEG) incorporates a JPEG codec that conforms to the JPEG baseline compression and decompression standard. This provides high-speed compression of image data and high-speed decoding of JPEG data. See section 57, JPEG Codec (JPEG) in User's Manual.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Parallel Data Capture Unit (PDC) | One PDC unit is provided for communicating with external I/O devices, including image sensors, and transferring parallel data such as an image output from the external I/O device through the DTC or DMAC to the on-chip SRAM and external address spaces (the CS and SDRAM areas). See section 44, Parallel Data Capture Unit (PDC) in User's Manual.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

## Table 1.12 Data processing

| Feature                                  | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cyclic Redundancy Check (CRC) calculator | The CRC calculator generates CRC codes to detect errors in the data. The bit order of CRC calculation results can be switched for LSB-first or MSB-first communication. Additionally, various CRC-generating polynomials are available. The snoop function allows monitoring reads from and writes to specific addresses. This function is useful in applications that require CRC code to be generated automatically in certain events, such as monitoring writes to the serial transmit buffer and reads from the serial receive buffer. See section 40, Cyclic Redundancy Check (CRC) Calculator in User's Manual. |

| Data Operation Circuit (DOC)             | The DOC compares, adds, and subtracts 16-bit data. See section 52, Data Operation Circuit (DOC) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sampling Rate Converter (SRC)            | The SRC converts the sampling rate of data produced by various audio decoders, such as the WMA, MP3, and AAC. Both 16-bit stereo and monaural data are supported. See section 42, Sampling Rate Converter (SRC) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                     |

### Table 1.13 Security

| Feature                       | Functional description                                                                                                                                                                                                                                                                                         |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secure Crypto Engine 7 (SCE7) | <ul> <li>Security algorithms:</li> <li>Symmetric algorithms: AES, 3DES, and ARC4</li> <li>Asymmetric algorithms: RSA and DSA.</li> <li>Other support features:</li> <li>TRNG (True Random Number Generator)</li> <li>Hash-value generation: SHA1, SHA224, SHA256, GHASH</li> <li>128-bit unique ID.</li> </ul> |

# 1.2 Block Diagram

Figure 1.1 shows the block diagram of the MCU superset. Some individual devices within the group have a subset of the features.

| Function        | Signal                                            | I/O    | Description                                                                                                                       |

|-----------------|---------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| SDRAM interface | CKE                                               | Output | SDRAM clock enable signal.                                                                                                        |

|                 | SDCS                                              | Output | SDRAM chip select signal, active low.                                                                                             |

|                 | RAS                                               | Output | SDRAM low address strobe signal, active low.                                                                                      |

|                 | CAS                                               | Output | SDRAM column address strobe signal, active low.                                                                                   |

|                 | WE                                                | Output | SDRAM write enable signal, active low.                                                                                            |

|                 | DQM0                                              | Output | SDRAM I/O data mask enable signal for DQ07 to DQ00.                                                                               |

|                 | DQM1                                              | Output | SDRAM I/O data mask enable signal for DQ15 to DQ08.                                                                               |

|                 | A00 to A15                                        | Output | Address bus.                                                                                                                      |

|                 | DQ00 to DQ15                                      | I/O    | Data bus.                                                                                                                         |

| GPT             | GTETRGA,<br>GTETRGB,<br>GTETRGC,<br>GTETRGD       | Input  | External trigger input pins.                                                                                                      |

|                 | GTIOC0A to<br>GTIOC13A,<br>GTIOC0B to<br>GTIOC13B | I/O    | Input capture, output compare, or PWM output pins.                                                                                |

|                 | GTIU                                              | Input  | Hall sensor input pin U.                                                                                                          |

|                 | GTIV                                              | Input  | Hall sensor input pin V.                                                                                                          |

|                 | GTIW                                              | Input  | Hall sensor input pin W.                                                                                                          |

|                 | GTOUUP                                            | Output | Three-phase PWM output for BLDC motor control (positive U phase).                                                                 |

|                 | GTOULO                                            | Output | Three-phase PWM output for BLDC motor control (negative U phase).                                                                 |

|                 | GTOVUP                                            | Output | Three-phase PWM output for BLDC motor control (positive V phase).                                                                 |

|                 | GTOVLO                                            | Output | Three-phase PWM output for BLDC motor control (negative V phase).                                                                 |

|                 | GTOWUP                                            | Output | Three-phase PWM output for BLDC motor control (positive W phase).                                                                 |

|                 | GTOWLO                                            | Output | Three-phase PWM output for BLDC motor control (negative W phase).                                                                 |

| AGT             | AGTEE0, AGTEE1                                    | Input  | External event input enable signals.                                                                                              |

|                 | AGTIO0, AGTIO1                                    | I/O    | External event input and pulse output pins.                                                                                       |

|                 | AGTO0, AGTO1                                      | Output | Pulse output pins.                                                                                                                |

|                 | AGTOA0, AGTOA1                                    | Output | Output compare match A output pins.                                                                                               |

|                 | AGTOB0, AGTOB1                                    | Output | Output compare match B output pins.                                                                                               |

| RTC             | RTCOUT                                            | Output | Output pin for 1-Hz or 64-Hz clock.                                                                                               |

|                 | RTCIC0 to RTCIC2                                  | Input  | Time capture event input pins.                                                                                                    |

| SCI             | SCK0 to SCK9                                      | I/O    | Input/output pins for the clock (clock synchronous mode).                                                                         |

|                 | RXD0 to RXD9                                      | Input  | Input pins for received data (asynchronous mode/clock synchronous mode                                                            |

|                 | TXD0 to TXD9                                      | Output | Output pins for transmitted data (asynchronous mode/clock synchronous mode).                                                      |

|                 | CTS0_RTS0 to<br>CTS9_RTS9                         | I/O    | Input/output pins for controlling the start of transmission and reception (asynchronous mode/clock synchronous mode), active low. |

|                 | SCL0 to SCL9                                      | I/O    | Input/output pins for the I <sup>2</sup> C clock (simple IIC mode).                                                               |

|                 | SDA0 to SDA9                                      | I/O    | Input/output pins for the I <sup>2</sup> C data (simple IIC mode).                                                                |

|                 | SCK0 to SCK9                                      | I/O    | Input/output pins for the clock (simple SPI mode).                                                                                |

|                 | MISO0 to MISO9                                    | I/O    | Input/output pins for slave transmission of data (simple SPI mode).                                                               |

|                 | MOSI0 to MOSI9                                    | I/O    | Input/output pins for master transmission of data (simple SPI mode).                                                              |

|                 | SS0 to SS9                                        | Input  | Chip-select input pins (simple SPI mode), active low.                                                                             |

| IIC             | SCL0 to SCL2                                      | I/O    | Input/output pins for the clock.                                                                                                  |

|                 | SDA0 to SDA2                                      | I/O    | Input/output pins for data.                                                                                                       |

| SSIE            | SSIBCK0                                           | I/O    | SSIE serial bit clock pins.                                                                                                       |

|                 | SSIBCK1                                           | ]      |                                                                                                                                   |

|                 | SSILRCK0/SSIFS0                                   | I/O    | LR clock/frame synchronization pins.                                                                                              |

|                 | SSILRCK1/SSIFS1                                   | ]      |                                                                                                                                   |

|                 | SSITXD0                                           | Output | Serial data output pins.                                                                                                          |

|                 | SSIRXD0                                           | Input  | Serial data input pins.                                                                                                           |

|                 | SSIDATA1                                          | I/O    | Serial data input/output pins.                                                                                                    |

|                 | AUDIO_CLK                                         | Input  | External clock pin for audio (input oversampling clock).                                                                          |

# Table 1.16Pin functions (2 of 5)

| in r | num     | ber        |          |          |                                        | ĺ         | 1            | Extb                 | us                | Timers |         |               |     | Com           | munica                   | ation i                  | nterfa | ces                     |                      |                          |                           |       |                  | Analog | J                | HMI  |                       |

|------|---------|------------|----------|----------|----------------------------------------|-----------|--------------|----------------------|-------------------|--------|---------|---------------|-----|---------------|--------------------------|--------------------------|--------|-------------------------|----------------------|--------------------------|---------------------------|-------|------------------|--------|------------------|------|-----------------------|

|      | LQFP176 | LGA145     | LQFP144  |          | Power, System,<br>Clock, Debug,<br>CAC | Interrupt | l/O port     | External bus         | SDRAM             | AGT    | GPT     | GPT           | RTC | USBFS,<br>CAN | SCI0,2,4,6,8<br>(30 MHz) | SCI1,3,5,7,9<br>(30 MHz) | SI     | SPI, QSPI               | SSIE                 | ETHERC (MII)<br>(25 MHz) | ETHERC (RMII)<br>(50 MHz) | USBHS | SDHI             | ADC12  | DAC12,<br>ACMPHS | CTSU | GLCDC. PDC            |

| 86   | 66      | A6         | 54       | 37       | TRDATA<br>3                            | -         | P208         | -                    | -                 | -      | GTOVLO  | -             | -   | -             | -                        | -                        | -      | QIO3                    | -                    | ET0_LI<br>NKSTA          | ET0_LI<br>NKST<br>A       | -     | SD0<br>DAT0<br>B | -      | -                | -    | LCD_DAT/<br>18_B      |

|      |         |            | 55       |          | RES                                    | -         | -            | -                    | -                 | -      | -       | -             | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

|      |         | B6<br>C8   | 56<br>57 | 39<br>40 | MD<br>-                                | -<br>NMI  | P201<br>P200 | -                    | -                 | -      | -       | -             | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

| 8    | 70      | -          | -        | -        | -                                      | -         | P908         | CS7                  | -                 | -      | -       | GTIOC<br>2A   | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DATA<br>14_B      |

| 7    | 71      | -          | -        | -        | -                                      | -         | P907         | CS6                  | -                 | -      | -       | GTIOC<br>2B   | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DATA<br>13 B      |

| 7    | 72      | -          | -        | -        | -                                      | -         | P906         | CS5                  | -                 | -      | -       | GTIOC<br>3A   | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT               |

| 7    | 73      | -          | -        | -        | -                                      | -         | P905         | CS4                  | -                 | -      | -       | GTIOC<br>3B   | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT               |

| 7    | 74      | C6         | 58       | -        | -                                      | -         | P312         | CS3                  | CAS               | AGTOA1 | -       | -             | -   | -             | -                        | CTS3_<br>RTS3/           | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

| 6    | 75      | B5         | 59       | _        |                                        | -         | P311         | CS2                  | RAS               | AGTOB1 | -       |               | -   |               |                          | SS3<br>SCK3              |        | -                       | _                    | _                        | _                         | _     |                  |        | -                | -    | LCD_DAT               |

|      |         |            | 60       |          |                                        |           | P310         |                      | A15               | AGTEE1 |         |               |     |               |                          | TXD3                     |        | QIO3                    |                      |                          |                           | -     |                  |        |                  |      | 23_A<br>LCD_DAT       |

|      |         |            |          | -        |                                        | -         |              |                      |                   | AGTEET | -       |               | -   | -             | -                        |                          | -      |                         | -                    | -                        | -                         |       | -                | -      | -                | -    | 22_A                  |

|      |         |            | 61       | -        | -                                      | -         | P309         |                      | A14               | -      | -       | -             | -   | -             | -                        | RXD3                     | -      | QIO2                    | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>21_A      |

|      |         |            | 62       | -        | -                                      | -         | P308         |                      | A13               | -      | -       | -             | -   | -             | -                        | -                        | -      | QIO1                    | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>20_A      |

| 6    | 79      | A4         | 63       | 41       | -                                      | -         | P307         | A12                  | A12               | -      | GTOUUP  | -             | -   | -             | CTS6                     | -                        | -      | QIO0                    | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>19_A      |

| 4 8  | 80      | B4         | 64       | 42       | -                                      | -         | P306         | A11                  | A11               | -      | GTOULO  | -             | -   | -             | SCK6                     | -                        | -      | QSSL                    | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>18_A      |

| 58   | 81      | D6         | 65       | 43       | -                                      | IRQ8      | P305         | A10                  | A10               | -      | GTOWUP  | -             | -   | -             | TXD6/<br>MOSI6           | -                        | -      | QSPC<br>LK              | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>17_A      |

| 4 8  | 82      | C4         | 66       | 44       | -                                      | IRQ9      | P304         | A09                  | A09               | -      | GTOWLO  | GTIOC         | -   | -             | /SDA6<br>RXD6/           | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/              |

|      |         |            |          |          |                                        |           |              |                      |                   |        |         | 7A            |     |               | MISO6<br>/SCL6           |                          |        |                         |                      |                          |                           |       |                  |        |                  |      | 16_A                  |

|      |         |            | 67<br>68 |          | VSS<br>VCC                             | -         | -            | -                    | -                 | -      | -       | -             | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

|      |         |            | 69       | 47       | -                                      | -         | P303         | A08                  | A08               | -      | -       | GTIOC<br>7B   | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>15_A      |

| 38   | 86      | A2         | 70       | 48       | -                                      | IRQ5      | P302         | A07                  | A07               | -      | GTOUUP  | GTIOC<br>4A   | -   | -             | TXD2/<br>MOSI2<br>/SDA2  | -                        | -      | SSLB3<br>_B             | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>14_A      |

| 28   | 87      | C3         | 71       | 49       | -                                      | IRQ6      | P301         | A06                  | A06               | AGTIO0 | GTOULO  | GTIOC<br>4B   | -   | -             | RXD2/<br>MISO2           | CTS9_<br>RTS9/<br>SS9    | -      | SSLB2<br>_ <sup>B</sup> | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>13_A      |

| 4 8  | 88      | B2         | 72       | 50       | TCK/SW                                 | -         | P300         | -                    | -                 | -      | GTOUUP  | GTIOC         | -   | -             | -<br>-                   | -                        | -      | SSLB1                   | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

| 3 8  | 89      | A1         | 73       | 51       | CLK<br>TMS/SW                          | -         | P108         | -                    | -                 | -      | GTOULO  | 0A_A<br>GTIOC | -   | -             | -                        | CTS9_                    | -      | _B<br>SSLB0             | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

|      |         | <b>D</b> 4 |          | 50       |                                        |           | <b>D</b> 400 |                      |                   |        | 0701410 | 0B_A          |     | 071/4         |                          | RTS9/<br>SS9<br>TXD9/    |        | _B                      |                      |                          |                           |       |                  |        |                  |      |                       |

| 1 9  | 90      | D4         | 74       | 52       | /TDO/S<br>WO                           | -         | P109         | -                    | -                 | -      | GTOVUP  | GTIOC<br>1A_A | -   | CTX1          | -                        | MOSI9<br>/SDA9           | -      | MOSIB<br>_B             | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

| 3 9  | 91      | B1         | 75       | 53       | TDI                                    | IRQ3      | P110         | -                    | -                 | -      | GTOVLO  | GTIOC<br>1B_A | -   | CRX1          | CTS2_<br>RTS2/<br>SS2    | RXD9/<br>MISO9<br>/SCL9  | -      | MISOB<br>_B             | -                    | -                        | -                         | -     | -                | -      | VCOUT            | -    | -                     |

| 4 9  | 92      | C2         | 76       | 54       | -                                      | IRQ4      | P111         | A05                  | A05               | -      | -       | GTIOC<br>3A_A | -   | -             | SCK2                     | SCK9                     |        | RSPC<br>KB_B            | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>12_A      |

| 2 9  | 93      | D3         | 77       | 55       | -                                      | -         | P112         | A04                  | A04               | -      | -       | GTIOC<br>3B_A | -   | -             | TXD2/<br>MOSI2           | SCK1                     | -      | SSLB0                   | SSIBC<br>K0_B        | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT               |

| 1 9  | 94      | C1         | 78       | 56       |                                        |           | P113         | A03                  | A03               | -      | -       | GTIOC         | -   |               | /SDA2<br>RXD2/           |                          |        |                         | SSILR                | _                        | _                         |       |                  | _      | -                |      | LCD_DAT/              |

|      |         |            |          |          |                                        |           |              |                      |                   |        |         | 2A            |     |               | MISO2<br>/SCL2           |                          |        |                         | CK0/S<br>SIFS0_<br>B |                          |                           |       |                  |        |                  |      | 10_A                  |

| 2 9  | 95      | E4         | 79       | 57       | -                                      | -         | P114         | A02                  | A02               | -      | -       | GTIOC<br>2B   | -   | -             | -                        | -                        | -      | -                       | SSIRX<br>D0_B        | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>09_A      |

| 1 9  | 96      | E3         | 80       | 58       | -                                      | -         | P115         | A01                  | A01               | -      | -       | GTIOC<br>4A   | -   | -             | -                        | -                        | -      | -                       | SSITX<br>D0_B        | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>08_A      |

|      |         | D2<br>D1   |          |          | VCC<br>VSS                             | -         | -            | -                    | -                 | -      | -       | -             | -   | -             | -                        | -                        | -      | -                       | E                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

|      |         |            | 83       |          | -                                      | -         | -<br>P608    | -<br>A00/<br>BC0     | -<br>A00/D<br>QM1 | -      | -       | GTIOC<br>4B   | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -<br>LCD_DAT/<br>07_A |

| 1    | 100     | E2         | 84       | 60       | -                                      | -         | P609         |                      | CKE               | -      | -       | GTIOC         | -   | CTX1          | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DATA              |

| 3    | 101     | F3         | 85       | 61       | -                                      | -         | P610         | CS0                  | WE                | -      | -       | 5A<br>GTIOC   | -   | CRX1          | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | 06_A<br>LCD_DATA      |

| 2    | 102     | E1         | 86       | -        | CLKOUT                                 | -         | P611         | -                    | SDCS              | -      | -       | 5B<br>-       | -   | -             | -                        | CTS7_                    | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | 05_A<br>-             |

| 1    | 103     | F2         | 87       | -        | /CACRE<br>F<br>-                       | -         | P612         | D08[                 | DQ08              | -      | -       | -             | -   | -             | -                        | RTS7/<br>SS7<br>SCK7     | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

|      |         | F1         |          |          |                                        |           |              | A08/<br>D08]         | DQ09              |        |         |               |     |               |                          | TXD7                     |        |                         |                      |                          |                           |       |                  |        |                  |      |                       |

|      |         |            |          |          |                                        |           |              | A09/<br>D09]         |                   |        |         |               |     |               |                          |                          |        |                         |                      |                          |                           |       |                  |        |                  |      |                       |

| 2    | 105     | G3         | 89       | -        | _                                      | -         | P614         | D10[<br>A10/<br>D10] | DQ10              | -      | -       | -             | -   | -             | -                        | RXD7                     | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | -                     |

| 1    | 106     | -          | -        | -        | -                                      | -         | P615         |                      | -                 | -      | -       | -             | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DAT/<br>10_B      |

| 1    | 107     | -          | -        | -        | -                                      | -         | PA08         | -                    | -                 | -      | -       | -             | -   | -             | -                        | -                        | -      | -                       | -                    | -                        | -                         | -     | -                | -      | -                | -    | LCD_DATA<br>09_B      |

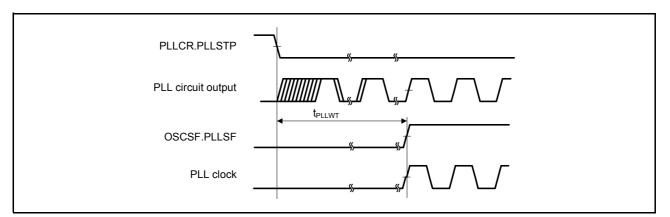

### Figure 2.7 PLL clock oscillation start timing

Note: Only operate the PLL is operated after main clock oscillation has stabilized.

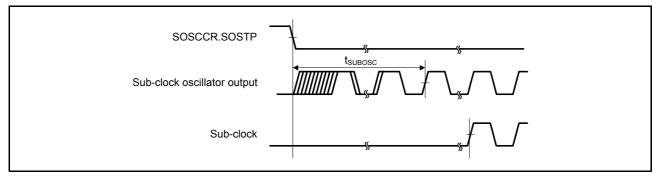

Figure 2.8 Sub-clock oscillation start timing

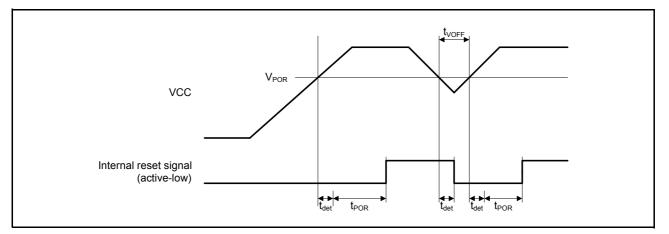

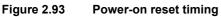

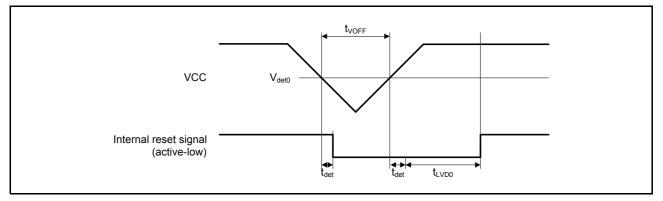

# 2.3.3 Reset Timing

#### Table 2.15 Reset timing

| Item                                                                                                                                                                                                                          |                                          | Symbol             | Min | Тур | Мах | Unit | Test conditions |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------|-----|-----|-----|------|-----------------|

| RES pulse width                                                                                                                                                                                                               | Power-on                                 | t <sub>RESWP</sub> | 1   | -   | -   | ms   | Figure 2.9      |

|                                                                                                                                                                                                                               | Deep Software Standby mode               | t <sub>RESWD</sub> | 0.6 | -   | -   | ms   | Figure 2.10     |

|                                                                                                                                                                                                                               | Software Standby mode, Subosc-speed mode | t <sub>RESWS</sub> | 0.3 | -   | -   | ms   |                 |

|                                                                                                                                                                                                                               | All other                                | t <sub>RESW</sub>  | 200 | -   | -   | μs   |                 |

| Wait time after RE                                                                                                                                                                                                            | S cancellation                           | t <sub>RESWT</sub> | -   | 29  | 33  | μs   | Figure 2.9      |

| Wait time after internal reset cancellation<br>(IWDT reset, WDT reset, software reset, SRAM parity error<br>reset, SRAM ECC error reset, bus master MPU error reset, bus<br>slave MPU error reset, stack pointer error reset) |                                          |                    | -   | 320 | 408 | μs   | -               |

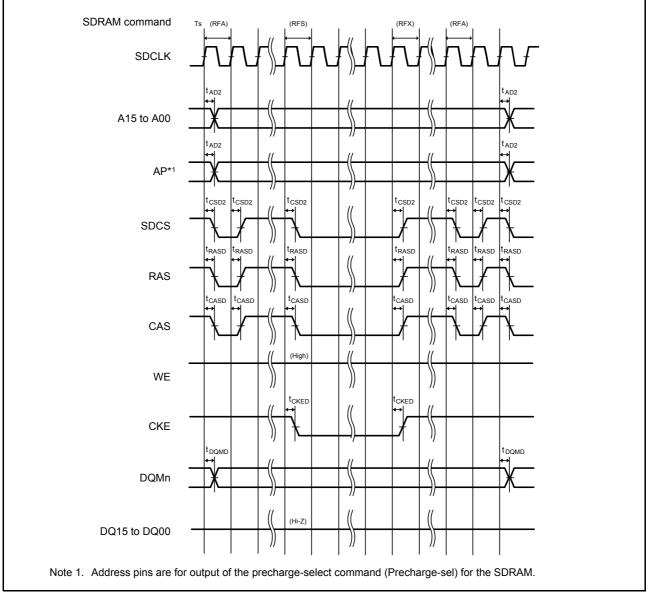

Table 2.18Bus timing (2 of 2)Condition 1: When using the CS area controller (CSC). BCLK = 8 to 120 MHz, EBCLK = 8 to 60 MHz VCC = AVCC0 = VCC\_USB = VBATT = 2.7 to 3.6 V, VREFH/VREFH0 = 2.7 V to AVCC0, VCC\_USBHS = AVCC\_USBHS = 3.0 to 3.6 V Output load conditions: VOH = VCC × 0.5, VOL = VCC × 0.5, C = 30 pF EBCLK: High drive output is selected in the port drive capability bit in the PmnPFS register. Others: Middle drive output is selected in the port drive capability bit in the PmnPFS register.

Condition 2: When using the SDRAM area controller (SDRAMC). BCLK = SDCLK = 8 to 120 MHz VCC = AVCC0 = VCC\_USB = VBATT = 3.0 to 3.6 V, VREFH/VREFH0 = 3.0 V to AVCC0, VCC\_USBHS = AVCC\_USBHS = 3.0 to 3.6 V Output load conditions: VOH = VCC × 0.5, VOL = VCC × 0.5, C = 15 pF High drive output is selected in the port drive capability bit in the PmnPFS register.

Condition 3: When using the SDRAM area controller (SDRAMC) and CS area controller (CSC) simultaneously. BCLK = SDCLK = 8 to 60 MHz VCC = AVCC0 = VCC\_USB = VBATT = 3.0 to 3.6 V, VREFH/VREFH0 = 3.0 V to AVCC0, VCC\_USBHS = AVCC\_USBHS = 3.0 to 3.6 V Output load conditions: VOH = VCC × 0.5, VOL = VCC × 0.5, C = 15 pF

High drive output is selected in the port drive capability bit in the PmnPFS register.

| Item                           | Symbol            | Min | Max | Unit | Test conditions |

|--------------------------------|-------------------|-----|-----|------|-----------------|

| Address delay 2 (SDRAM)        | t <sub>AD2</sub>  | 0.8 | 6.8 | ns   | Figure 2.23 to  |

| CS delay 2 (SDRAM)             | t <sub>CSD2</sub> | 0.8 | 6.8 | ns   | Figure 2.29     |

| DQM delay (SDRAM)              | t <sub>DQMD</sub> | 0.8 | 6.8 | ns   |                 |

| CKE delay (SDRAM)              | t <sub>CKED</sub> | 0.8 | 6.8 | ns   |                 |

| Read data setup time 2 (SDRAM) | t <sub>RDS2</sub> | 2.9 | -   | ns   |                 |

| Read data hold time 2 (SDRAM)  | t <sub>RDH2</sub> | 1.5 | -   | ns   |                 |

| Write data delay 2 (SDRAM)     | t <sub>WDD2</sub> | -   | 6.8 | ns   |                 |

| Write data hold time 2 (SDRAM) | t <sub>WDH2</sub> | 0.8 | -   | ns   |                 |

| WE delay (SDRAM)               | t <sub>WED</sub>  | 0.8 | 6.8 | ns   |                 |

| RAS delay (SDRAM)              | t <sub>RASD</sub> | 0.8 | 6.8 | ns   |                 |

| CAS delay (SDRAM)              | t <sub>CASD</sub> | 0.8 | 6.8 | ns   |                 |

#### Figure 2.29 SDRAM self-refresh timing

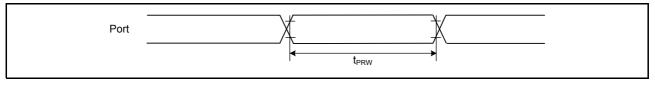

2.3.7 I/O Ports, POEG, GPT32, AGT, KINT, and ADC12 Trigger Timing

# Table 2.19 I/O ports, POEG, GPT32, AGT, KINT, and ADC12 trigger timing (1 of 2) GPT32 Conditions:

High drive output is selected in the port drive capability bit in the PmnPFS register.

AGT Conditions:

Middle drive output is selected in the port drive capability bit in the PmnPFS register.

| ltem      |                                | Symbol            | Min | Max | Unit              | Test<br>conditions |

|-----------|--------------------------------|-------------------|-----|-----|-------------------|--------------------|

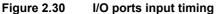

| I/O ports | Input data pulse width         | t <sub>PRW</sub>  | 1.5 | -   | t <sub>Pcyc</sub> | Figure 2.30        |

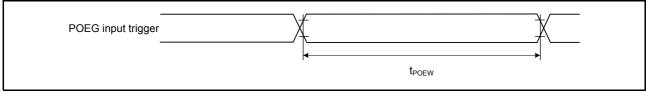

| POEG      | POEG input trigger pulse width | t <sub>POEW</sub> | 3   | -   | t <sub>Pcyc</sub> | Figure 2.31        |

#### S5D9

# Table 2.19 I/O ports, POEG, GPT32, AGT, KINT, and ADC12 trigger timing (2 of 2) GPT32 Conditions:

High drive output is selected in the port drive capability bit in the PmnPFS register.

AGT Conditions:

Middle drive output is selected in the port drive capability bit in the PmnPFS register.

| ltem                                       |                                                                                      |                                        | Symbol                | Min | Max | Unit               | Test<br>conditions |

|--------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|-----------------------|-----|-----|--------------------|--------------------|

| GPT32                                      | Input capture pulse width                                                            | Single edge                            | t <sub>GTICW</sub>    | 1.5 | -   | t <sub>PDcyc</sub> | Figure 2.32        |

|                                            |                                                                                      | Dual edge                              |                       | 2.5 | -   |                    |                    |

| GTIOCxY output skew                        | •                                                                                    | Middle drive buffer                    | t <sub>GTISK</sub> *2 | -   | 4   | ns                 | Figure 2.33        |

|                                            | (x = 0 to 7, Y= A or B)                                                              | High drive buffer                      |                       | -   | 4   |                    |                    |

|                                            | GTIOCxY output skew                                                                  | Middle drive buffer                    |                       | -   | 4   |                    |                    |

| (x = 8 to 13, Y = A or I                   | (x = 8 to 13, Y = A or B)                                                            | High drive buffer                      |                       | -   | 4   |                    |                    |

|                                            | GTIOCxY output skew<br>(x = 0 to 13, Y = A or B)Middle drive bufferHigh drive buffer | Middle drive buffer                    |                       | -   | 6   |                    |                    |

|                                            |                                                                                      | High drive buffer                      |                       | -   | 6   |                    |                    |

|                                            | OPS output skew<br>GTOUUP, GTOULO, GTOVUP,<br>GTOVLO, GTOWUP, GTOWLO                 |                                        | t <sub>GTOSK</sub>    | -   | 5   | ns                 | Figure 2.34        |

| GPT(PWM<br>Delay<br>Generation<br>Circuit) | GTIOCxY_Z output skew<br>(x = 0 to 3, Y = A or B, Z = A)                             |                                        | t <sub>HRSK</sub> *3  | -   | 2.0 | ns                 | Figure 2.35        |

| AGT                                        | AGTIO, AGTEE input cycle                                                             |                                        | t <sub>ACYC</sub> *4  | 100 | -   | ns                 | Figure 2.36        |

|                                            | AGTIO, AGTEE input high widt                                                         | t high width, low width                |                       | 40  | -   | ns                 |                    |

|                                            | AGTIO, AGTO, AGTOA, AGTO                                                             | AGTIO, AGTO, AGTOA, AGTOB output cycle |                       |     | -   | ns                 |                    |

| ADC12                                      | ADC12 trigger input pulse width                                                      | 1                                      | t <sub>TRGW</sub>     | 1.5 | -   | t <sub>Pcyc</sub>  | Figure 2.37        |

| KINT                                       | Key interrupt input low width                                                        |                                        | t <sub>KR</sub>       | 250 | -   | ns                 | Figure 2.38        |

Note 1. t<sub>Pcyc</sub>: PCLKB cycle, t<sub>PDcyc</sub>: PCLKD cycle.

Note 2. This skew applies when the same driver I/O is used. If the I/O of the middle and high drivers is mixed, operation is not guaranteed.

Note 3. The load is 30 pF.

Note 4. Constraints on AGTIO input:  $t_{Pcyc} \times 2$  ( $t_{Pcyc}$ : PCLKB cycle) <  $t_{ACYC}$ .

Figure 2.31 POEG input trigger timing

Table 2.24

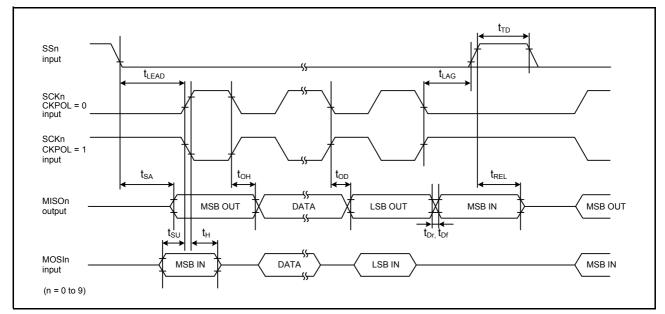

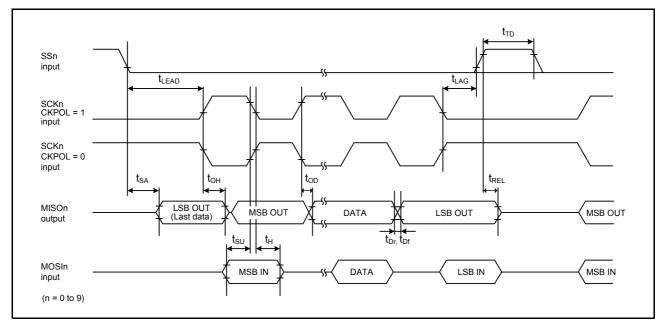

SCI timing (3) (1 of 2)

Conditions: Middle drive output is selected in the port drive capability bit in the PmnPFS register.

| ltem            |                                    | Symbol            | Min | Max                     | Unit | Test conditions |

|-----------------|------------------------------------|-------------------|-----|-------------------------|------|-----------------|

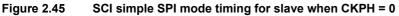

| (Standard mode) | SDA input rise time                | t <sub>Sr</sub>   | -   | 1000                    | ns   | Figure 2.46     |

|                 | SDA input fall time                | t <sub>Sf</sub>   | -   | 300                     | ns   | ]               |

|                 | SDA input spike pulse removal time | t <sub>SP</sub>   | 0   | 4 × t <sub>IICcyc</sub> | ns   | ]               |

|                 | Data input setup time              | t <sub>SDAS</sub> | 250 | -                       | ns   | ]               |

|                 | Data input hold time               | t <sub>SDAH</sub> | 0   | -                       | ns   | 1               |

|                 | SCL, SDA capacitive load           | C <sub>b*</sub> 1 | -   | 400                     | pF   | 1               |

Table 2.24

SCI timing (3) (2 of 2)

Conditions: Middle drive output is selected in the port drive capability bit in the PmnPFS register.

| Item                  |                                    | Symbol            | Min | Max                     | Unit | Test conditions |

|-----------------------|------------------------------------|-------------------|-----|-------------------------|------|-----------------|

| (Fast mode) SDA input | SDA input rise time                | t <sub>Sr</sub>   | -   | 300                     | ns   | Figure 2.46     |

|                       | SDA input fall time                | t <sub>Sf</sub>   | -   | 300                     | ns   |                 |

|                       | SDA input spike pulse removal time | t <sub>SP</sub>   | 0   | 4 × t <sub>IICcyc</sub> | ns   |                 |

|                       | Data input setup time              | t <sub>SDAS</sub> | 100 | -                       | ns   |                 |

|                       | Data input hold time               | t <sub>SDAH</sub> | 0   | -                       | ns   | 1               |

|                       | SCL, SDA capacitive load           | C <sub>b*</sub> 1 | -   | 400                     | pF   |                 |

Note:  $t_{\text{IICcyc}}$ : IIC internal reference clock (IIC $\phi$ ) cycle,  $t_{\text{Pcyc}}$ : PCLKA cycle.

Note 1. Cb indicates the total capacity of the bus line.

Figure 2.46 SCI simple IIC mode timing

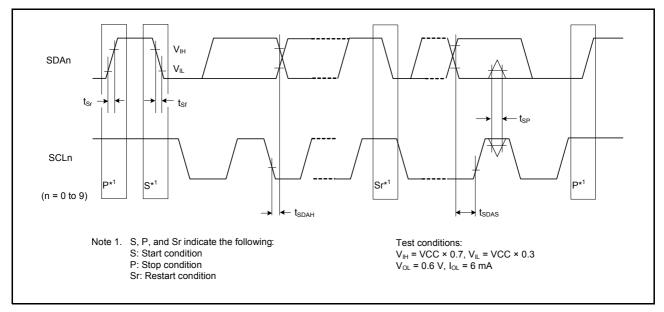

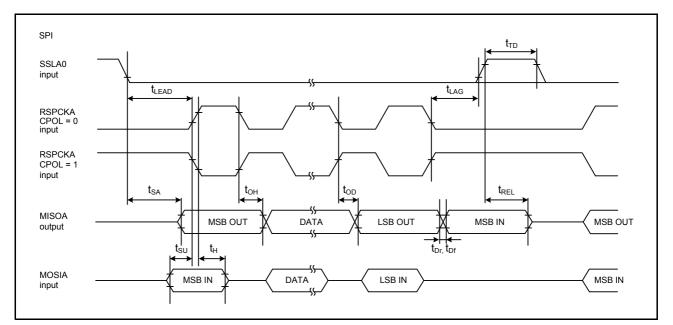

Figure 2.52 SPI timing for slave when CPHA = 0

RENESAS

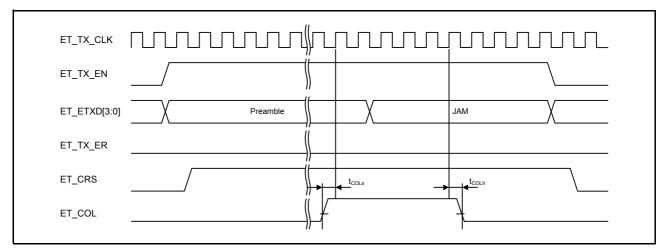

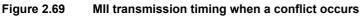

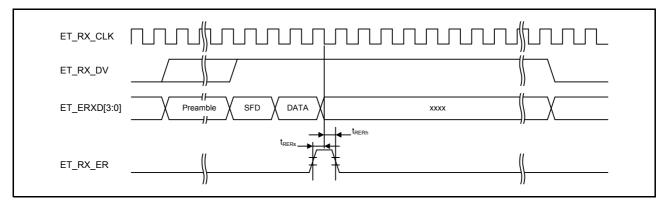

Figure 2.70 MII reception timing in normal operation

Figure 2.71 MII reception timing when an error occurs

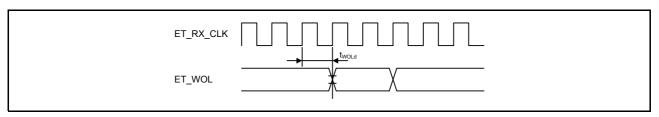

Figure 2.72 WOL output timing for MII

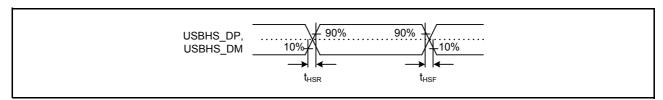

#### Figure 2.85 USBHS\_DP and USBHS\_DM output timing in high-speed mode

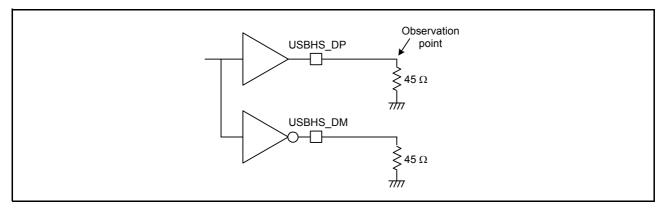

Figure 2.86 Test circuit in high-speed mode

| Table 2.37      | USBHS high-speed characteristics (USBHS_DP and USBHS_DM pin characteristics) |

|-----------------|------------------------------------------------------------------------------|

| Conditions: USE | $3HS_RREF = 2.2 \text{ k}\Omega \pm 1\%$ , USBMCLK = 12/20/24 MHZ            |

| ltem                              |                        | Symbol               | Min  | Max | Unit | Test conditions         |

|-----------------------------------|------------------------|----------------------|------|-----|------|-------------------------|

| Battery Charging<br>Specification | D+ sink current        | I <sub>DP_SINK</sub> | 25   | 175 | μA   | -                       |

|                                   | D- sink current        | I <sub>DM_SINK</sub> | 25   | 175 | μA   | -                       |

|                                   | DCD source current     | I <sub>DP_SRC</sub>  | 7    | 13  | μA   | -                       |

|                                   | Data detection voltage | V <sub>DAT_REF</sub> | 0.25 | 0.4 | V    | -                       |

|                                   | D+ source voltage      | V <sub>DP_SRC</sub>  | 0.5  | 0.7 | V    | Output current = 250 µA |

|                                   | D- source voltage      | V <sub>DM_SRC</sub>  | 0.5  | 0.7 | V    | Output current = 250 µA |

# 2.4.2 USBFS Timing

Table 2.38USBFS low-speed characteristics for host only (USB\_DP and USB\_DM pin characteristics) (1 of 2)Conditions: VCC = AVCC0 = VCC\_USB = VBATT = 3.0 to 3.6V, 2.7 ≤ VREFH0/VREFH ≤ AVCC0, VCC\_USBHS = AVCC\_USBHS = 3.0to 3.6 V, UCLK = 48 MHz

| ltem            |                                | Symbol                            | Min | Тур | Max | Unit | Test conditions                   |

|-----------------|--------------------------------|-----------------------------------|-----|-----|-----|------|-----------------------------------|

| Input           | Input high voltage             | V <sub>IH</sub>                   | 2.0 | -   | -   | V    | -                                 |

| characteristics | Input low voltage              | V <sub>IL</sub>                   | -   | -   | 0.8 | V    | -                                 |

|                 | Differential input sensitivity | V <sub>DI</sub>                   | 0.2 | -   | -   | V    | USB_DP - USB_DM                   |

|                 | Differential common-mode range | V <sub>CM</sub>                   | 0.8 | -   | 2.5 | V    | -                                 |

| Output          | Output high voltage            | V <sub>OH</sub>                   | 2.8 | -   | 3.6 | V    | I <sub>OH</sub> = -200 μA         |

| characteristics | Output low voltage             | V <sub>OL</sub>                   | 0.0 | -   | 0.3 | V    | I <sub>OL</sub> = 2 mA            |

|                 | Cross-over voltage             | V <sub>CRS</sub>                  | 1.3 | -   | 2.0 | V    | Figure 2.87                       |

|                 | Rise time                      | t <sub>LR</sub>                   | 75  | -   | 300 | ns   |                                   |

|                 | Fall time                      | t <sub>LF</sub>                   | 75  | -   | 300 | ns   |                                   |

|                 | Rise/fall time ratio           | t <sub>LR</sub> / t <sub>LF</sub> | 80  | -   | 125 | %    | t <sub>LR</sub> / t <sub>LF</sub> |

### Offset error

Offset error is the difference between the transition point of the ideal first output code and the actual first output code.

### Full-scale error

Full-scale error is the difference between the transition point of the ideal last output code and the actual last output code.

# 2.6 DAC12 Characteristics

#### Table 2.44 D/A conversion characteristics

| ltem                     | Min | Тур  | Max         | Unit | Test conditions                               |

|--------------------------|-----|------|-------------|------|-----------------------------------------------|

| Resolution               | -   | -    | 12          | Bits | -                                             |

| Without output amplifier |     |      |             |      |                                               |

| Absolute accuracy        | -   | -    | ±24         | LSB  | Resistive load 2 $M\Omega$                    |

| INL                      | -   | ±2.0 | ±8.0        | LSB  | Resistive load 2 $M\Omega$                    |

| DNL                      | -   | ±1.0 | ±2.0        | LSB  | -                                             |

| Output impedance         | -   | 8.5  | -           | kΩ   | -                                             |

| Conversion time          | -   | -    | 3.0         | μs   | Resistive load 2 MΩ,<br>Capacitive load 20 pF |

| Output voltage range     | 0   | -    | VREFH       | V    | -                                             |

| With output amplifier    |     |      |             |      |                                               |

| INL                      | -   | ±2.0 | ±4.0        | LSB  | -                                             |

| DNL                      | -   | ±1.0 | ±2.0        | LSB  | -                                             |

| Conversion time          | -   | -    | 4.0         | μs   | -                                             |

| Resistive load           | 5   | -    | -           | kΩ   | -                                             |

| Capacitive load          | -   | -    | 50          | pF   | -                                             |

| Output voltage range     | 0.2 | -    | VREFH – 0.2 | V    | -                                             |

# 2.7 TSN Characteristics

#### Table 2.45TSN characteristics

| Item                          | Symbol             | Min  | Тур  | Max | Unit  | Test conditions |

|-------------------------------|--------------------|------|------|-----|-------|-----------------|

| Relative accuracy             | -                  | -    | ±1.0 | -   | °C    | -               |

| Temperature slope             | -                  | -    | 4.0  | -   | mV/°C | -               |

| Output voltage (at 25°C)      | -                  | -    | 1.24 | -   | V     | -               |

| Temperature sensor start time | t <sub>START</sub> | -    | -    | 30  | μs    | -               |