Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | F²MC-8FX                                                                      |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 16MHz                                                                         |

| Connectivity               | LINbus, UART/USART                                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                            |

| Number of I/O              | 17                                                                            |

| Program Memory Size        | 20KB (20K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 496 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                   |

| Data Converters            | A/D 6x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 20-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f564kpf-g-sne2 |

# 2. Packages And Corresponding Products

# • MB95560H Series

| Part number Package | MB95F562H | MB95F562K | MB95F563H | MB95F563K | MB95F564H | MB95F564K |

|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| WNP032              | О         | О         | О         | О         | О         | О         |

| SOJ020              | О         | О         | О         | О         | О         | 0         |

| STG020              | О         | О         | О         | О         | О         | О         |

| STB016              | Х         | X         | Х         | Х         | Х         | Х         |

| SO016               | Х         | Х         | Х         | Х         | Х         | Х         |

| PDA008              | Х         | Х         | Х         | Х         | Х         | Х         |

| SOD008              | Х         | Х         | Х         | Х         | Х         | Х         |

#### • MB95570H Series

| Part number |           |           |           |           |           |           |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|

|             | MB95F572H | MB95F572K | MB95F573H | MB95F573K | MB95F574H | MB95F574K |

| Package     |           |           |           |           |           |           |

| WNP032      | X         | X         | X         | X         | Х         | X         |

| SOJ020      | Х         | X         | Х         | Х         | Х         | Х         |

| STG020      | Х         | X         | Х         | Х         | Х         | Х         |

| STB016      | Х         | Х         | Х         | Х         | Х         | Х         |

| SO016       | Х         | X         | Х         | Х         | Х         | Х         |

| PDA008      | О         | О         | О         | О         | О         | О         |

| SOD008      | 0         | 0         | О         | О         | 0         | 0         |

## • MB95580H Series

| Part number Package | MB95F582H | MB95F582K | MB95F583H | MB95F583K | MB95F584H | MB95F584K |

|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| WNP032              | O         | О         | О         | O         | O         | О         |

| SOJ020              | X         | Х         | Х         | Х         | Х         | Х         |

| STG020              | Х         | Х         | Х         | Х         | Х         | Х         |

| STB016              | О         | О         | О         | O         | O         | О         |

| SO016               | О         | О         | О         | O         | O         | О         |

| PDA008              | Х         | Х         | Х         | Х         | Х         | Х         |

| SOD008              | Х         | Х         | Х         | Х         | Х         | Х         |

O: Available X: Unavailable

# 5. Pin Functions (MB95560H Series, 32 pins)

| Pin no. | Pin name | I/O<br>circuit<br>type* | Function                                                           |     |  |                          |

|---------|----------|-------------------------|--------------------------------------------------------------------|-----|--|--------------------------|

| 1       | PF1      | В                       | General-purpose I/O port                                           |     |  |                          |

| !       | X1       | B                       | Main clock I/O oscillation pin                                     |     |  |                          |

| 2       | PF0      | В                       | General-purpose I/O port                                           |     |  |                          |

| 2       | X0       | 7 P                     | Main clock input oscillation pin                                   |     |  |                          |

| 3       | Vss      | _                       | Power supply pin (GND)                                             |     |  |                          |

| 4       | PG2      | С                       | General-purpose I/O port                                           |     |  |                          |

| 4       | X1A      |                         | Subclock I/O oscillation pin                                       |     |  |                          |

| 5       | PG1      | С                       | General-purpose I/O port                                           |     |  |                          |

|         | X0A      | 7                       | Subclock input oscillation pin                                     |     |  |                          |

| 6       | Vcc      | _                       | Power supply pin                                                   |     |  |                          |

| 7       | С        | _                       | Decoupling capacitor connection pin                                |     |  |                          |

|         | PF2      |                         | General-purpose I/O port                                           |     |  |                          |

| 8       | RST      | Α                       | Reset pin                                                          |     |  |                          |

|         | NOT      |                         | Dedicated reset pin on MB95F562H/F563H/F564H                       |     |  |                          |

|         | Dea      |                         | Dea                                                                | P63 |  | General-purpose I/O port |

| 9       |          | E                       | High-current pin                                                   |     |  |                          |

|         | TO11     |                         | 8/16-bit composite timer ch. 1 output pin                          |     |  |                          |

|         | P62      | Е                       | General-purpose I/O port                                           |     |  |                          |

| 10      | _        |                         | High-current pin                                                   |     |  |                          |

|         | TO10     |                         | 8/16-bit composite timer ch. 1 output pin                          |     |  |                          |

| 11      |          |                         |                                                                    |     |  |                          |

| 12      | NC       |                         | It is an internally connected pin. Always leave it unconnected.    |     |  |                          |

| 13      | 140      |                         | The same intermally conflicted pint. Always leave it unconflicted. |     |  |                          |

| 14      |          |                         |                                                                    |     |  |                          |

|         | P00      |                         | General-purpose I/O port                                           |     |  |                          |

| 15      |          | D                       | High-current pin                                                   |     |  |                          |

|         | AN00     |                         | A/D converter analog input pin                                     |     |  |                          |

|         | P64      |                         | General-purpose I/O port                                           |     |  |                          |

| 16      | -        | E                       | High-current pin                                                   |     |  |                          |

|         | EC1      |                         | 8/16-bit composite timer ch. 1 clock input pin                     |     |  |                          |

|         | P01      |                         | General-purpose I/O port                                           |     |  |                          |

| 17      |          | D                       | High-current pin                                                   |     |  |                          |

|         | AN01     |                         | A/D converter analog input pin                                     |     |  |                          |

|         | P02      |                         | General-purpose I/O port                                           |     |  |                          |

|         |          | <b>↓</b>                | High-current pin                                                   |     |  |                          |

| 18      | INT02    | D                       | External interrupt input pin                                       |     |  |                          |

|         | AN02     | _                       | A/D converter analog input pin                                     |     |  |                          |

|         | SCK      |                         | LIN-UART clock I/O pin                                             |     |  |                          |

| Pin no. | Pin name | I/O<br>circuit<br>type* | Function                                       |

|---------|----------|-------------------------|------------------------------------------------|

|         | P04      |                         | General-purpose I/O port                       |

|         | INT04    | Ī                       | External interrupt input pin                   |

| 16      | AN04     | D                       | A/D converter analog input pin                 |

|         | SIN      | Ī                       | LIN-UART data input pin                        |

|         | EC0      | 1                       | 8/16-bit composite timer ch. 0 clock input pin |

|         | P05      |                         | General-purpose I/O port                       |

|         | P05      |                         | High-current pin                               |

| 17      | INT05    | D                       | External interrupt input pin                   |

|         | AN05     | 1                       | A/D converter analog input pin                 |

|         | TO00     | 1                       | 8/16-bit composite timer ch. 0 output pin      |

|         | P06      |                         | General-purpose I/O port                       |

| 18      | F00      | J E                     | High-current pin                               |

| 10      | INT06    | <b>†</b>                | External interrupt input pin                   |

|         | TO01     | 1                       | 8/16-bit composite timer ch. 0 output pin      |

|         | P07      |                         | General-purpose I/O port                       |

| 19      | P01      | E                       | High-current pin                               |

|         | INT07    | 1                       | External interrupt input pin                   |

|         | P12      |                         | General-purpose I/O port                       |

| 20      | EC0      | F                       | 8/16-bit composite timer ch. 0 clock input pin |

|         | DBG      | 1                       | DBG input pin                                  |

<sup>\*:</sup> For the I/O circuit types, see "I/O Circuit Type".

# 7. Pin Functions (MB95570H Series, 8 pins)

| Pin no. | Pin name | I/O<br>circuit<br>type* | Function                                               |

|---------|----------|-------------------------|--------------------------------------------------------|

| 1       | Vss      | _                       | Power supply pin (GND)                                 |

| 2       | Vcc      | _                       | Power supply pin                                       |

| 3       | С        | _                       | Decoupling capacitor connection pin                    |

|         | PF2      |                         | General-purpose I/O port                               |

| 4       | RST      | А                       | Reset pin Dedicated reset pin on MB95F572H/F573H/F574H |

|         | P04      |                         | General-purpose I/O port                               |

| _       | INT04    | D                       | External interrupt input pin                           |

| 5       | AN04     | U                       | A/D converter analog input pin                         |

|         | EC0      | 1                       | 8/16-bit composite timer ch. 0 clock input pin         |

|         | P05      |                         | General-purpose I/O port<br>High-current pin           |

| 6       | AN05     | D                       | A/D converter analog input pin                         |

|         | TO00     |                         | 8/16-bit composite timer ch. 0 output pin              |

| -       | P06      | _                       | General-purpose I/O port<br>High-current pin           |

| 7       | INT06    | Е                       | External interrupt input pin                           |

|         | TO01     |                         | 8/16-bit composite timer ch. 0 output pin              |

|         | P12      |                         | General-purpose I/O port                               |

| 8       | EC0      | F                       | 8/16-bit composite timer ch. 0 clock input pin         |

|         | DBG      |                         | DBG input pin                                          |

<sup>\*:</sup> For the I/O circuit types, see "I/O Circuit Type".

| Type | Circuit                                                                                  | Remarks                                                                                                       |

|------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| D    | Pull-up control  P-ch  Digital output  N-ch                                              | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control available</li><li>Analog input</li></ul> |

|      | Analog input  A/D control Standby control Hysteresis input                               |                                                                                                               |

| Е    | Pull-up control  P-ch  Digital output  Digital output  Standby control  Hysteresis input | CMOS output     Hysteresis input     Pull-up control available                                                |

| F    | Standby control  Hysteresis input  N-ch                                                  | N-ch open drain output     Hysteresis input                                                                   |

# 11. Handling Precautions

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Cypress semiconductor devices.

## 11.1 Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

# Absolute Maximum Ratings

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

#### Recommended Operating Conditions

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

## Processing and Protection of Pins

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

(1) Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

(2) Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device.

Therefore, avoid this type of connection.

(3) Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

### • Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- (1) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- (2) Be sure that abnormal current flows do not occur during the power-on sequence.

## Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### • Precautions Related to Usage of Devices

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Supply voltage must be stabilized.

A malfunction may occur when power supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the V<sub>CC</sub> power supply voltage.

As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in  $V_{CC}$  ripple (p-p value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard  $V_{CC}$  value, and the transient fluctuation rate does not exceed 0.1 V/ms at a momentary fluctuation such as switching the power supply.

#### Notes on using the external clock

When an external clock is used, oscillation stabilization wait time is required for power-on reset, wake-up from subclock mode or stop mode.

#### 13. Pin Connection

## · Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latchups. Always pull up or pull down an unused input pin through a resistor of at least 2 k $\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

#### · Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the Vcc pin and the Vss pin to the power supply and ground outside the device. In addition, connect the current supply source to the Vcc pin and the Vss pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a decoupling capacitor between the Vcc pin and the Vss pin at a location close to this device.

#### DBG pin

Connect the DBG pin to an external pull-up resistor of 2 k $\Omega$  or above.

After power-on, ensure that the DBG pin does not stay at "L" level until the reset output is released.

The DBG pin becomes a communication pin in debug mode. Since the actual pull-up resistance depends on the tool used and the interconnection length, refer to the tool document when selecting a pull-up resistor.

## • RST pin

Connect the  $\overline{\mathsf{RST}}$  pin to an external pull-up resistor of 2 k $\Omega$  or above.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the interconnection length between a pull-up resistor and the RST pin and that between a pull-up resistor and the Vcc pin when designing the layout of the printed circuit board.

The PF2/RST pin functions as the reset input/output pin after power-on. In addition, the reset output of the PF2/RST pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function and the general purpose I/O function can be selected by the RSTEN bit in the SYSC register.

#### C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The decoupling capacitor for the V<sub>CC</sub> pin must have a capacitance equal to or larger than the capacitance of C<sub>S</sub>. For the connection to a decoupling capacitor C<sub>S</sub>, see the diagram below. To prevent the device from unintentionally entering a mode to which the device is not set to transit due to noise, minimize the distance between the C pin and C<sub>S</sub> and the distance between C<sub>S</sub> and the V<sub>SS</sub> pin when designing the layout of a printed circuit board.

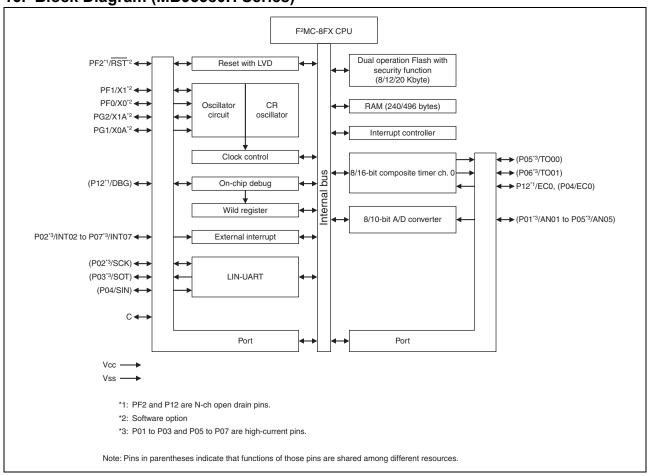

# 16. Block Diagram (MB95580H Series)

| Address              | Register abbreviation | Register name                                              | R/W        | Initial value |

|----------------------|-----------------------|------------------------------------------------------------|------------|---------------|

| 0F83н                | WRARH1                | Wild register address setting register (upper) ch. 1       | R/W        | 0000000в      |

| 0F84н                | WRARL1                | Wild register address setting register (lower) ch. 1       | R/W        | 0000000в      |

| 0F85н                | WRDR1                 | Wild register data setting register ch. 1                  | R/W        | 0000000в      |

| 0F86н                | WRARH2                | Wild register address setting register (upper) ch. 2       | R/W        | 0000000в      |

| 0F87н                | WRARL2                | Wild register address setting register (lower) ch. 2       | R/W        | 0000000в      |

| 0F88н                | WRDR2                 | Wild register data setting register ch. 2                  | R/W        | 0000000в      |

| 0F89н                |                       |                                                            |            |               |

| to<br>0F91н          | _                     | (Disabled)                                                 |            |               |

| 0F92н                | T01CR0                | 8/16-bit composite timer 01 status control register 0      | R/W        | 0000000В      |

| 0F93н                | T00CR0                | 8/16-bit composite timer 00 status control register 0      | R/W        | 0000000В      |

| 0F94н                | T01DR                 | 8/16-bit composite timer 01 data register                  | R/W        | 0000000в      |

| 0F95н                | T00DR                 | 8/16-bit composite timer 00 data register                  | R/W        | 0000000в      |

| 0F96н                | TMCR0                 | 8/16-bit composite timer 00/01 timer mode control register | R/W        | 0000000в      |

| 0F97н                | T11CR0                | 8/16-bit composite timer 11 status control register 0      | R/W        | 0000000в      |

| 0F98н                | T10CR0                | 8/16-bit composite timer 10 status control register 0      | R/W        | 0000000в      |

| 0F99н                | T11DR                 | 8/16-bit composite timer 11 data register                  | R/W        | 0000000в      |

| 0F9Ан                | T10DR                 | 8/16-bit composite timer 10 data register                  | R/W        | 0000000в      |

| 0F9Вн                | TMCR1                 | 8/16-bit composite timer 10/11 timer mode control register | R/W        | 0000000в      |

| 0F9Сн<br>to<br>0FBВн | _                     | (Disabled)                                                 | _          | _             |

| 0FBCн                | BGR1                  | LIN-UART baud rate generator register 1                    | R/W        | 0000000в      |

| 0FBDн                | BGR0                  | LIN-UART baud rate generator register 0                    | R/W        | 0000000в      |

| 0FBEн<br>to<br>0FC2н | _                     | (Disabled)                                                 |            | _             |

| 0FС3н                | AIDRL                 | A/D input disable register (lower)                         | R/W        | 0000000в      |

| 0FC4н<br>to<br>0FE3н | _                     | (Disabled)                                                 | _          | _             |

| 0FE4н                | CRTH                  | Main CR clock trimming register (upper)                    | R/W        | 000XXXXXB     |

| 0FE5н                | CRTL                  | Main CR clock trimming register (lower)                    | R/W        | 000XXXXXB     |

| 0FE6н                | _                     | (Disabled)                                                 | <b>†</b> — | _             |

| 0FE7н                | CRTDA                 | Main CR clock temperature dependent adjustment register    | R/W        | 000XXXXXB     |

| 0FE8н                | SYSC                  | System configuration register                              | R/W        | 11000011в     |

| 0FЕ9н                | CMCR                  | Clock monitoring control register                          | R/W        | 00000000в     |

| 0FEAн                | CMDR                  | Clock monitoring data register                             | R          | 00000000в     |

| Address              | Register abbreviation | Register name                                | R/W | Initial value |

|----------------------|-----------------------|----------------------------------------------|-----|---------------|

| 0FEBн                | WDTH                  | Watchdog timer selection ID register (upper) | R   | XXXXXXXXB     |

| 0FEC <sub>H</sub>    | WDTL                  | Watchdog timer selection ID register (lower) | R   | XXXXXXX       |

| 0FEDн<br>to<br>0FFFн | _                     | (Disabled)                                   |     | _             |

• R/W access symbols

R/W : Readable / Writable

R : Read only

· Initial value symbols

The initial value of this bit is "0".The initial value of this bit is "1".

X : The initial value of this bit is undefined.

Note: Do not write to an address that is "(Disabled)". If a "(Disabled)" address is read, an indeterminate value is returned.

| Address           | Register abbreviation | Register name                                                     | R/W | Initial value |

|-------------------|-----------------------|-------------------------------------------------------------------|-----|---------------|

| 006Сн             | ADC1                  | 8/10-bit A/D converter control register 1                         | R/W | 0000000В      |

| 006Dн             | ADC2                  | 8/10-bit A/D converter control register 2                         | R/W | 0000000В      |

| 006Ен             | ADDH                  | 8/10-bit A/D converter data register (upper)                      | R/W | 0000000В      |

| 006Fн             | ADDL                  | 8/10-bit A/D converter data register (lower)                      | R/W | 0000000в      |

| 0070н             | _                     | (Disabled)                                                        |     | —             |

| 0071н             | FSR2                  | Flash memory status register 2                                    | R/W | 0000000В      |

| 0072н             | FSR                   | Flash memory status register                                      | R/W | 000Х0000в     |

| 0073н             | SWRE0                 | Flash memory sector write control register 0                      | R/W | 0000000В      |

| 0074н             | FSR3                  | Flash memory status register 3                                    | R   | 000XXXXXB     |

| 0075н             | FSR4                  | Flash memory status register 4                                    | R/W | 0000000В      |

| 0076н             | WREN                  | Wild register address compare enable register                     | R/W | 0000000в      |

| 0077н             | WROR                  | Wild register data test setting register                          | R/W | 0000000в      |

| 0078н             | _                     | Mirror of register bank pointer (RP) and direct bank pointer (DP) |     | _             |

| 0079н             | ILR0                  | Interrupt level setting register 0                                | R/W | 111111111     |

| 007Ан             | ILR1                  | Interrupt level setting register 1                                | R/W | 111111111     |

| 007Вн,            |                       | (Disabled)                                                        |     |               |

| 007Сн             | <del></del>           | (Disabled)                                                        |     |               |

| 007Dн             | ILR4                  | Interrupt level setting register 4                                | R/W | 111111111     |

| 007Ен             | ILR5                  | Interrupt level setting register 5                                | R/W | 111111111     |

| 007Fн             | _                     | (Disabled)                                                        |     | _             |

| 0F80н             | WRARH0                | Wild register address setting register (upper) ch. 0              | R/W | 0000000в      |

| 0F81н             | WRARL0                | Wild register address setting register (lower) ch. 0              | R/W | 0000000В      |

| 0F82н             | WRDR0                 | Wild register data setting register ch. 0                         | R/W | 0000000в      |

| 0F83н             | WRARH1                | Wild register address setting register (upper) ch. 1              | R/W | 0000000в      |

| 0F84н             | WRARL1                | Wild register address setting register (lower) ch. 1              | R/W | 0000000В      |

| 0F85н             | WRDR1                 | Wild register data setting register ch. 1                         | R/W | 0000000в      |

| 0F86н             | WRARH2                | Wild register address setting register (upper) ch. 2              | R/W | 0000000В      |

| 0F87н             | WRARL2                | Wild register address setting register (lower) ch. 2              | R/W | 0000000В      |

| 0F88н             | WRDR2                 | Wild register data setting register ch. 2                         | R/W | 0000000В      |

| 0F89н             |                       |                                                                   |     |               |

| to                | <del>-</del>          | (Disabled)                                                        |     | —             |

| 0F91н             |                       |                                                                   |     |               |

| 0F92н             | T01CR0                | 8/16-bit composite timer 01 status control register 0             | R/W | 0000000В      |

| 0F93н             | T00CR0                | 8/16-bit composite timer 00 status control register 0             | R/W | 0000000В      |

| 0F94н             | T01DR                 | 8/16-bit composite timer 01 data register                         | R/W | 0000000в      |

| 0F95 <sub>H</sub> | T00DR                 | 8/16-bit composite timer 00 data register                         | R/W | 0000000в      |

| 0F96н             | TMCR0                 | 8/16-bit composite timer 00/01 timer mode control register        | R/W | 0000000в      |

| 0F97н             |                       |                                                                   |     |               |

| to                | _                     | (Disabled)                                                        | _   | - I           |

| 0FC2н             |                       |                                                                   |     |               |

| Address              | Register abbreviation | Register name                                           | R/W | Initial value |

|----------------------|-----------------------|---------------------------------------------------------|-----|---------------|

| 0FС3н                | AIDRL                 | A/D input disable register (lower)                      | R/W | 0000000в      |

| 0FC4н<br>to<br>0FE3н | 1                     | (Disabled)                                              |     | _             |

| 0FE4н                | CRTH                  | Main CR clock trimming register (upper)                 | R/W | 000XXXXXB     |

| 0FE5н                | CRTL                  | Main CR clock trimming register (lower)                 | R/W | 000XXXXXB     |

| 0FE6н                | _                     | (Disabled)                                              | _   | _             |

| 0FE7н                | CRTDA                 | Main CR clock temperature dependent adjustment register | R/W | 000XXXXXB     |

| 0FE8н                | SYSC                  | System configuration register                           | R/W | 11000011в     |

| 0FE9н                | CMCR                  | Clock monitoring control register                       | R/W | 0000000в      |

| 0FEAн                | CMDR                  | Clock monitoring data register                          | R   | 0000000в      |

| 0FEBн                | WDTH                  | Watchdog timer selection ID register (upper)            | R   | XXXXXXXXB     |

| 0FECн                | WDTL                  | Watchdog timer selection ID register (lower)            | R   | XXXXXXX       |

| 0FEDн<br>to<br>0FFFн | _                     | (Disabled)                                              | _   | _             |

• R/W access symbols

R/W : Readable / Writable

R : Read only

• Initial value symbols

The initial value of this bit is "0".The initial value of this bit is "1".

X : The initial value of this bit is undefined.

Note: Do not write to an address that is "(Disabled)". If a "(Disabled)" address is read, an indeterminate value is returned.

# 23. Interrupt Source Table (MB95580H Series)

|                                        |                                | Vector table address |                   |                                              | Priority order of                                                      |  |

|----------------------------------------|--------------------------------|----------------------|-------------------|----------------------------------------------|------------------------------------------------------------------------|--|

| Interrupt source                       | Interrupt<br>request<br>number | iest .               |                   | Bit name of interrupt level setting register | interruptsources<br>of the same level<br>(occurring<br>simultaneously) |  |

| External interrupt ch. 4               | IRQ00                          | FFFA⊦                | FFFB⊦             | L00 [1:0]                                    | High                                                                   |  |

| External interrupt ch. 5               | IRQ01                          | FFF8 <sub>H</sub>    | FFF9 <sub>H</sub> | L01 [1:0]                                    | <b>A</b>                                                               |  |

| External interrupt ch. 2               | IRQ02                          | FFF6⊦                | FFF7 <sub>H</sub> | L02 [1:0]                                    |                                                                        |  |

| External interrupt ch. 6               | II\QUZ                         | TTTOH                | 11178             | L02 [1.0]                                    |                                                                        |  |

| External interrupt ch. 3               | IRQ03                          | FFF4 <sub>H</sub>    | FFF5⊧             | L03 [1:0]                                    |                                                                        |  |

| External interrupt ch. 7               | IIIQUS                         | 1114                 | I I I JH          | L03 [1.0]                                    |                                                                        |  |

| _                                      | IRQ04                          | FFF2 <sub>H</sub>    | FFF3 <sub>H</sub> | L04 [1:0]                                    |                                                                        |  |

| 8/16-bit composite timer ch. 0 (lower) | IRQ05                          | FFF0 <sub>H</sub>    | FFF1 <sub>H</sub> | L05 [1:0]                                    |                                                                        |  |

| 8/16-bit composite timer ch. 0 (upper) | IRQ06                          | FFEEH                | FFEF <sub>H</sub> | L06 [1:0]                                    |                                                                        |  |

| LIN-UART (reception)                   | IRQ07                          | FFECH                | FFEDH             | L07 [1:0]                                    |                                                                        |  |

| LIN-UART (transmission)                | IRQ08                          | FFEAH                | FFEB⊦             | L08 [1:0]                                    |                                                                        |  |

| _                                      | IRQ09                          | FFE8 <sub>H</sub>    | FFE9 <sub>H</sub> | L09 [1:0]                                    |                                                                        |  |

| _                                      | IRQ10                          | FFE6 <sub>H</sub>    | FFE7 <sub>H</sub> | L10 [1:0]                                    |                                                                        |  |

| _                                      | IRQ11                          | FFE4 <sub>H</sub>    | FFE5 <sub>H</sub> | L11 [1:0]                                    |                                                                        |  |

| _                                      | IRQ12                          | FFE2 <sub>H</sub>    | FFE3 <sub>H</sub> | L12 [1:0]                                    |                                                                        |  |

| _                                      | IRQ13                          | FFE0⊦                | FFE1 <sub>H</sub> | L13 [1:0]                                    |                                                                        |  |

| _                                      | IRQ14                          | FFDE                 | FFDF <sub>H</sub> | L14 [1:0]                                    |                                                                        |  |

| _                                      | IRQ15                          | FFDC⊦                | FFDD⊦             | L15 [1:0]                                    |                                                                        |  |

| _                                      | IRQ16                          | FFDA⊦                | FFDB⊦             | L16 [1:0]                                    |                                                                        |  |

| _                                      | IRQ17                          | FFD8 <sub>H</sub>    | FFD9 <sub>H</sub> | L17 [1:0]                                    |                                                                        |  |

| 8/10-bit A/D converter                 | IRQ18                          | FFD6 <sub>H</sub>    | FFD7 <sub>H</sub> | L18 [1:0]                                    |                                                                        |  |

| Time-base timer                        | IRQ19                          | FFD4 <sub>H</sub>    | FFD5 <sub>H</sub> | L19 [1:0]                                    |                                                                        |  |

| Watch prescaler                        | IRQ20                          | FFD2 <sub>H</sub>    | FFD3 <sub>H</sub> | L20 [1:0]                                    |                                                                        |  |

| _                                      | IRQ21                          | FFD0 <sub>H</sub>    | FFD1 <sub>H</sub> | L21 [1:0]                                    |                                                                        |  |

|                                        | IRQ22                          | FFCEH                | FFCF <sub>H</sub> | L22 [1:0]                                    | ▼                                                                      |  |

| Flash memory                           | IRQ23                          | FFCCH                | FFCDH             | L23 [1:0]                                    | Low                                                                    |  |

## 24.5 A/D Converter

## 24.5.1 A/D Converter Electrical Characteristics

(Vcc = 2.7 V to 5.5 V, Vss = 0.0 V,  $T_A = -40 \, ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ )

| Parameter                     | Symbol           | Value         |               |               |      | Remarks                                                               |

|-------------------------------|------------------|---------------|---------------|---------------|------|-----------------------------------------------------------------------|

| Parameter                     | Symbol           | Min           | Тур           | Max           | Unit | Remarks                                                               |

| Resolution                    |                  | _             | _             | 10            | bit  |                                                                       |

| Total error                   |                  | -3            | _             | +3            | LSB  |                                                                       |

| Linearity error               | —                | -2.5          | _             | +2.5          | LSB  |                                                                       |

| Differential linearity error  |                  | -1.9          | _             | +1.9          | LSB  |                                                                       |

| Zero transition voltage       | Vот              | Vss – 1.5 LSB | Vss + 0.5 LSB | Vss + 2.5 LSB | ٧    |                                                                       |

| Full-scale transition voltage | V <sub>FST</sub> | Vcc – 4.5 LSB | Vcc – 2 LSB   | Vcc + 0.5 LSB | ٧    |                                                                       |

| Compare time                  |                  | 1             | _             | 10            | μs   | 4.5 V ≤ Vcc ≤ 5.5 V                                                   |

| Compare time                  | _                | 3             | _             | 10            | μs   | 2.7 V ≤ Vcc < 4.5 V                                                   |

| Sampling time                 | _                | 0.6           | _             | ∞             | μs   | $2.7~V \le V_{CC} \le 5.5~V,$ with external impedance < $3.3~k\Omega$ |

| Analog input current          | Iain             | -0.3          | _             | +0.3          | μA   |                                                                       |

| Analog input voltage          | Vain             | Vss           | —             | Vcc           | V    |                                                                       |

24.6 Flash Memory Program/Erase Characteristics

| Parameter                              | Value  |       |       | Unit  | Remarks                                                           |  |

|----------------------------------------|--------|-------|-------|-------|-------------------------------------------------------------------|--|

| Parameter                              | Min    | Тур   | Max   | Unit  | Remarks                                                           |  |

| Sector erase time<br>(2 Kbyte sector)  | _      | 0.3*1 | 1.6*2 | s     | The time of writing 00 <sub>H</sub> prior to erasure is excluded. |  |

| Sector erase time<br>(16 Kbyte sector) | _      | 0.6*1 | 3.1*2 | s     | The time of writing 00 <sub>H</sub> prior to erasure is excluded. |  |

| Byte writing time                      | _      | 17    | 272   | μs    | System-level overhead is excluded.                                |  |

| Program/erase cycle                    | 100000 | _     | _     | cycle |                                                                   |  |

| Power supply voltage at program/erase  | 2.4    | _     | 5.5   | V     |                                                                   |  |

| Flash memory data retention time       | 5*³    | _     |       | year  | Average T <sub>A</sub> = +85 °C                                   |  |

<sup>\*1:</sup>  $V_{CC} = 5.5 \text{ V}$ ,  $T_A = +25 \text{ °C}$ , 0 cycle

<sup>\*2:</sup> Vcc = 2.4 V,  $T_A = +85 ^{\circ}\text{C}$ , 100000 cycles

<sup>\*3:</sup> This value was converted from the result of a technology reliability assessment. (The value was converted from the result of a high temperature accelerated test using the Arrhenius equation with an average temperature of +85 °C).

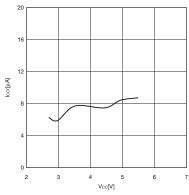

$T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Subsleep mode with the external clock operating

$I_{\text{CCT}} - V_{\text{CC}}$

$T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Watch mode with the external clock operating

Iccтs – Vcc

$T_A = +25$  °C,  $F_{MP} = 2, 4, 8, 10, 16$  MHz (divided by 2) Time-base timer mode with the external clock operating

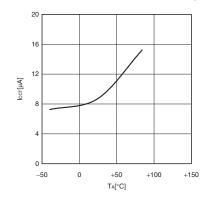

#### Iccls - Ta

$V_{CC} = 5.5 \text{ V}, F_{MPL} = 16 \text{ kHz}$  (divided by 2) Subsleep mode with the external clock operating

ICCT - TA

$V_{\text{CC}} = 5.5 \text{ V}, \; F_{\text{MPL}} = 16 \text{ kHz} \; \text{(divided by 2)}$  Watch mode with the external clock operating

$I_{\text{CCTS}} - T_{\text{A}}$

$V_{\text{CC}} = 5.5 \text{ V}, \, F_{\text{MP}} = 10, \, 16 \, \text{MHz} \, (\text{divided by 2})$  Time-base timer mode with the external clock operating

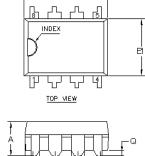

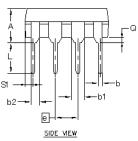

| Package Type | Package Code |

|--------------|--------------|

| DIP 8        | PDA008       |

| SYMBOL   | DIMENSIONS |      |      |  |

|----------|------------|------|------|--|

| 3 IM BOL | MIN.       | NOM. | MAX. |  |

| A        | _          | _    | 4.36 |  |

| L        | 3.00       | _    | _    |  |

| D        | 9.10       | 9.40 | 9.80 |  |

| E        | 7.62 TYP   |      |      |  |

| E1       | 6.10       | 6.35 | 6.60 |  |

| 6        | _          | _    | 15°  |  |

| С        | 0.20       | 0.25 | 0.30 |  |

| ь        | 0.38       | 0.46 | 0.54 |  |

| ь1       | _          | 1.52 | 1.82 |  |

| b2       | 0.99       |      | 1.29 |  |

| e        | 2.54 TYP   |      |      |  |

| S1       | 0.59       | 0.89 | 1.24 |  |

| Q        | 050        |      |      |  |

NOTES

1. ALL DIMENSIONS ARE IN MILLIMETER.

2. JED EC SPECIFICATION NO . REF : N/A

PACKAGE OUTLINE, 8 LEAD POIP 9.40X8.35X3.88 MM PDA008 REV®

002-16909 \*\*

| Page | Section                                 | Details                                                                                                                                                                                                                                             |

|------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48   | 2. Recommended Operating Conditions     | Revised note *2.  The value is 2.88 V when the low-voltage detection reset is used.  The minimum power supply voltage becomes 2.18 V when a product with the low-voltage detection reset is used.                                                   |

|      |                                         | Corrected the following statement in note *3.  The decoupling capacitor for the Vcc pin must have a capacitance larger than Cs.  →  The decoupling capacitor for the Vcc pin must have a capacitance equal to or larger than the capacitance of Cs. |

|      |                                         | Revised the remark in "• DBG/RST/C pins connection diagram".                                                                                                                                                                                        |

| 49   | 3. DC Characteristics                   | Revised the remark of the parameter "Input leak current (Hi-Z output leak current)".  When pull-up resistance is disabled  When the internal pull-up resistor is disabled                                                                           |

|      |                                         | Renamed the parameter "Pull-up resistance" to "Internal pull-up resistor".                                                                                                                                                                          |

|      |                                         | Revised the remark of the parameter "Internal pull-up resistor".  When pull-up resistance is enabled  →  When the internal pull-up resistor is enabled                                                                                              |

| 53   | AC Characteristics     (1) Clock Timing | Corrected the pin names of the parameter "Input clock rising time and falling time". $X0 \rightarrow X0$ , $X0A$ $X0$ , $X1$ $\rightarrow X0$ , $X1$ , $X0A$ , $X1A$                                                                                |