Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | LINbus, UART/USART                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 17                                                                             |

| Program Memory Size        | 20KB (20K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 496 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                    |

| Data Converters            | A/D 6x8/10b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                                |

| Supplier Device Package    | 20-TSSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f564kpft-g-sne2 |

# **Contents**

| Features                                                                   | 1  |

|----------------------------------------------------------------------------|----|

| 1. Product Line-up                                                         | 3  |

| 2. Packages And Corresponding Products                                     | 7  |

| 3. Differences Among Products And Notes On Product Selection               | 8  |

| 4. Pin Assignment                                                          | 9  |

| 5. Pin Functions (MB95560H Series, 32 pins)                                | 11 |

| 6. Pin Functions (MB95560H Series, 20 pins)                                | 13 |

| 7. Pin Functions (MB95570H Series, 8 pins)                                 | 15 |

| 8. Pin Functions (MB95580H Series, 32 pins)                                | 16 |

| 9. Pin Functions (MB95580H Series, 16 pins)                                | 18 |

| 10. I/O Circuit Type                                                       | 20 |

| 11. Handling Precautions                                                   |    |

| 11.1 Precautions for Product Design                                        |    |

| 11.2 Precautions for Package Mounting 11.3 Precautions for Use Environment |    |

| 12. Notes On Device Handling                                               |    |

| 13. Pin Connection                                                         |    |

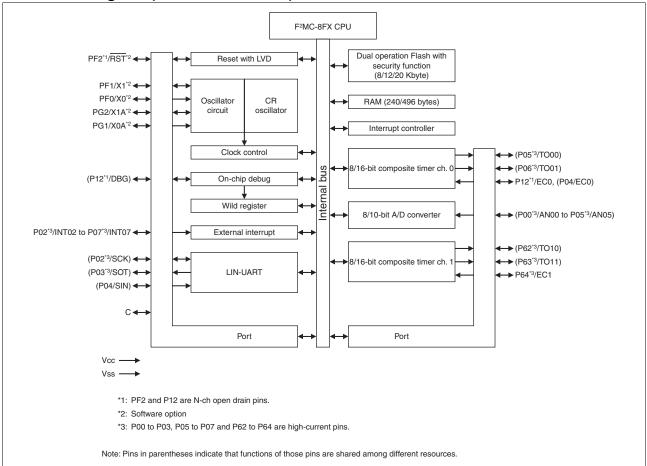

| 14. Block Diagram (MB95560H Series)                                        |    |

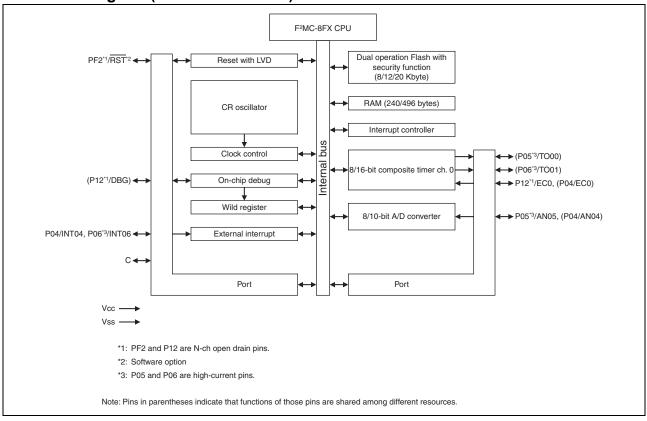

| 15. Block Diagram (MB95570H Series)                                        |    |

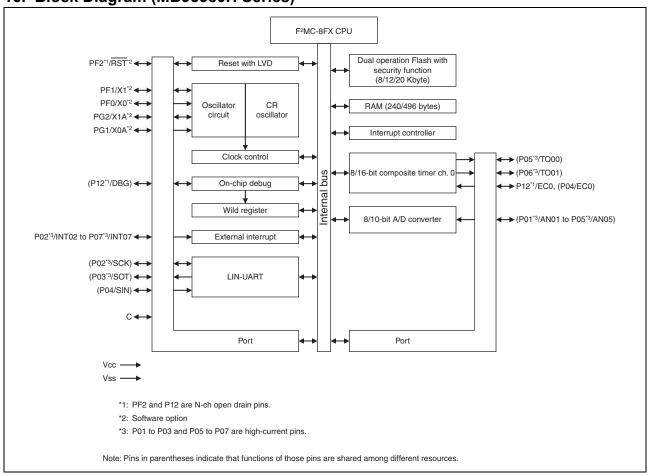

| 16. Block Diagram (MB95580H Series)                                        |    |

| 17. CPU Core                                                               |    |

| 18. I/O Map (MB95560H Series)                                              |    |

| 10. I/O INAP (IND3330011 Series)                                           | 50 |

| 19. I/O Map (MB95570H Series)                   | 34                                                       |

|-------------------------------------------------|----------------------------------------------------------|

| 20. I/O Map (MB95580H Series)                   | 37                                                       |

| 21. Interrupt Source Table (MB95560H Series)    | 40                                                       |

| 22. Interrupt Source Table (MB95570H Series)    | 41                                                       |

| 23. Interrupt Source Table (MB95580H Series)    | 42                                                       |

| 24. Electrical Characteristics                  | 43                                                       |

| 24.1 Absolute Maximum Ratings                   | 43                                                       |

| 24.2 Recommended Operating Conditions           |                                                          |

| 24.3 DC Characteristics                         |                                                          |

| 24.4 AC Characteristics                         |                                                          |

| 24.5 A/D Converter                              |                                                          |

| 24.6 Flash Memory Program/Erase Characteristics | 67                                                       |

| 25. Sample Characteristics                      | 68                                                       |

|                                                 |                                                          |

| 26. Mask Options                                |                                                          |

|                                                 | 74                                                       |

| 26. Mask Options                                | 74<br>75                                                 |

| 26. Mask Options                                | 74<br>75<br>77                                           |

| 26. Mask Options27. Ordering Information        | 74<br>75<br>77<br>84                                     |

| 26. Mask Options                                | 74<br>75<br>77<br>84<br>87                               |

| 26. Mask Options                                | 74<br>75<br>77<br>84<br>87<br>88<br>88                   |

| 26. Mask Options                                | 74<br>75<br>77<br>84<br>87<br>88<br>88<br>88             |

| 26. Mask Options                                | 74<br>75<br>77<br>84<br>87<br>88<br>88<br>88<br>88       |

| 26. Mask Options                                | 74<br>75<br>77<br>84<br>87<br>88<br>88<br>88<br>88<br>88 |

| Part number                                                                         | MB95F582H                                                                                                                                                                                                                                                                                                                                                                   | MB95F583H        | MB95F584I    | MPO       | 5F582K  | MB95F583K | MB95F584K  |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----------|---------|-----------|------------|--|--|

| Parameter                                                                           | WD35F302F                                                                                                                                                                                                                                                                                                                                                                   | MD39L303H        | WID35F364F   | IVIDS     | OF JOZK | MD30F303K | WID95F504K |  |  |

| Time-base timer Interval time: 0.256 ms to 8.3 s (external clock frequency = 4 MHz) |                                                                                                                                                                                                                                                                                                                                                                             |                  |              |           |         |           |            |  |  |

| software                                                                            | <ul> <li>Reset generation cycle         Main oscillation clock at 10 MHz: 105 ms (Min)</li> <li>The sub-CR clock can be used as the source clock of the hardware watchdog timer.</li> </ul>                                                                                                                                                                                 |                  |              |           |         |           |            |  |  |

| Wild register                                                                       | It can be used t                                                                                                                                                                                                                                                                                                                                                            | to replace 3 byt | es of data.  |           |         |           |            |  |  |

| LIN-UART                                                                            | <ul> <li>A wide range of communication speed can be selected by a dedicated reload timer.</li> <li>It has a full duplex double buffer.</li> <li>Both clock synchronous serial data transfer and clock asynchronous serial data transfer are enabled.</li> <li>The LIN function can be used as a LIN master or a LIN slave.</li> </ul>                                       |                  |              |           |         |           |            |  |  |

| 8/10-bit A/D                                                                        | 5 channels                                                                                                                                                                                                                                                                                                                                                                  |                  |              |           |         |           |            |  |  |

| converter                                                                           | 8-bit or 10-bit re                                                                                                                                                                                                                                                                                                                                                          | esolution can be | e selected.  |           |         |           |            |  |  |

|                                                                                     | 1 channel                                                                                                                                                                                                                                                                                                                                                                   |                  |              |           |         |           |            |  |  |

|                                                                                     | <ul> <li>The timer can be configured as an "8-bit timer × 2 channels" or a "16-bit timer × 1 channel".</li> <li>It has the following functions: interval timer function, PWC function, PWM function and input capture function.</li> <li>Count clock: it can be selected from internal clocks (7 types) and external clocks.</li> <li>It can output square wave.</li> </ul> |                  |              |           |         |           |            |  |  |

| External                                                                            | 6 channels                                                                                                                                                                                                                                                                                                                                                                  |                  |              |           |         |           |            |  |  |

| interrupt                                                                           | <ul> <li>Interrupt by edge detection (The rising edge, falling edge, or both edges can be selected.)</li> <li>It can be used to wake up the device from the standby mode.</li> </ul>                                                                                                                                                                                        |                  |              |           |         |           |            |  |  |

| I In chin deniid                                                                    | 1-wire serial control     It supports serial writing (asynchronous mode).                                                                                                                                                                                                                                                                                                   |                  |              |           |         |           |            |  |  |

| Watch prescaler                                                                     | Eight different t                                                                                                                                                                                                                                                                                                                                                           | ime intervals ca | n be selecte | d.        |         |           |            |  |  |

| Flash memory                                                                        | <ul> <li>It supports automatic programming (Embedded Algorithm), and program/erase/erase-suspend/erase-resume commands.</li> <li>It has a flag indicating the completion of the operation of Embedded Algorithm.</li> <li>Flash security feature for protecting the content of the Flash memory</li> </ul>                                                                  |                  |              |           |         |           |            |  |  |

|                                                                                     | Number of                                                                                                                                                                                                                                                                                                                                                                   | program/erase    | cycles       | 1000      | 1000    | 0 100000  |            |  |  |

| Data retention time 20 years 10 years 5 years                                       |                                                                                                                                                                                                                                                                                                                                                                             |                  |              |           |         |           |            |  |  |

| Standby mode                                                                        | Sleep mode, st                                                                                                                                                                                                                                                                                                                                                              | op mode, watch   | n mode, time | base time | er mode | ·         |            |  |  |

| Package                                                                             | WNP032<br>STB016<br>SO016                                                                                                                                                                                                                                                                                                                                                   |                  |              |           |         |           |            |  |  |

# 8. Pin Functions (MB95580H Series, 32 pins)

| Pin no.       | Pin name | I/O<br>circuit<br>type* | Function                                                        |  |  |

|---------------|----------|-------------------------|-----------------------------------------------------------------|--|--|

|               | PF1      | Б                       | General-purpose I/O port                                        |  |  |

| 1             | X1       | В                       | Main clock I/O oscillation pin                                  |  |  |

|               | PF0      | _                       | General-purpose I/O port                                        |  |  |

| 2             | X0       | В                       | Main clock input oscillation pin                                |  |  |

| 3             | Vss      | <u> </u>                | Power supply pin (GND)                                          |  |  |

| 4             | PG2      | С                       | General-purpose I/O port                                        |  |  |

| 4             | X1A      |                         | Subclock I/O oscillation pin                                    |  |  |

| 5             | PG1      | С                       | General-purpose I/O port                                        |  |  |

| 5             | X0A      |                         | Subclock input oscillation pin                                  |  |  |

| 6             | Vcc      | _                       | Power supply pin                                                |  |  |

| 7             | С        | _                       | Decoupling capacitor connection pin                             |  |  |

|               | PF2      |                         | General-purpose I/O port                                        |  |  |

| 8             | RST      | A                       | Reset pin Dedicated reset pin on MB95F582H/F583H/F584H          |  |  |

| 9<br>10<br>11 |          |                         |                                                                 |  |  |

| 12<br>13      | NC       | _                       | It is an internally connected pin. Always leave it unconnected. |  |  |

| 14            |          |                         |                                                                 |  |  |

| 15            |          |                         |                                                                 |  |  |

| 16            |          |                         |                                                                 |  |  |

| 17            | P01      | D                       | General-purpose I/O port<br>High-current pin                    |  |  |

|               | AN01     | ]                       | A/D converter analog input pin                                  |  |  |

|               | P02      |                         | General-purpose I/O port<br>High-current pin                    |  |  |

| 18            | INT02    | D                       | External interrupt input pin                                    |  |  |

|               | AN02     |                         | A/D converter analog input pin                                  |  |  |

|               | SCK      | 1                       | LIN-UART clock I/O pin                                          |  |  |

|               | P03      |                         | General-purpose I/O port<br>High-current pin                    |  |  |

| 19            | INT03    | D                       | External interrupt input pin                                    |  |  |

|               | AN03     | 1                       | A/D converter analog input pin                                  |  |  |

|               | SOT      | ]                       | LIN-UART data output pin                                        |  |  |

# 11.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress's recommended conditions. For detailed information about mount conditions, contact your sales representative.

### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

# Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. Cypress recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with Cypress ranking of recommended conditions.

# • Lead-Free Packaging

CAUTION: When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

# • Storage of Semiconductor Devices

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (1) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- (2) Use dry boxes for product storage. Products should be stored below 70% relative humidity, and at temperatures between 5°C and 30°C.

- When you open Dry Package that recommends humidity 40% to 70% relative humidity.

- (3) When necessary, Cypress packages semiconductor devices in highly moisture-resistant aluminum laminate bags, with a silica gel desiccant. Devices should be sealed in their aluminum laminate bags for storage.

- (4) Avoid storing packages where they are exposed to corrosive gases or high levels of dust.

# Baking

Packages that have absorbed moisture may be de-moisturized by baking (heat drying). Follow the Cypress recommended conditions for baking.

Condition: 125°C/24 h

#### Static Electricity

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

# 14. Block Diagram (MB95560H Series)

# 15. Block Diagram (MB95570H Series)

# 16. Block Diagram (MB95580H Series)

# 20. I/O Map (MB95580H Series)

| Address | Register abbreviation | Register name                                           | R/W      | Initial value         |

|---------|-----------------------|---------------------------------------------------------|----------|-----------------------|

| 0000н   | PDR0                  | Port 0 data register                                    | R/W      | 0000000В              |

| 0001н   | DDR0                  | Port 0 direction register                               | R/W      | 0000000В              |

| 0002н   | PDR1                  | Port 1 data register                                    | R/W      | 0000000В              |

| 0003н   | DDR1                  | Port 1 direction register                               | R/W      | 0000000В              |

| 0004н   | _                     | (Disabled)                                              | _        |                       |

| 0005н   | WATR                  | Oscillation stabilization wait time setting register    | R/W      | 111111111             |

| 0006н   | PLLC                  | PLL control register                                    | R/W      | 000Х0000в             |

| 0007н   | SYCC                  | System clock control register                           | R/W      | XXX11011 <sub>B</sub> |

| 0008н   | STBC                  | Standby control register                                | R/W      | 0000000В              |

| 0009н   | RSRR                  | Reset source register                                   | R/W      | 000XXXXXB             |

| 000Ан   | TBTC                  | Time-base timer control register                        | R/W      | 0000000в              |

| 000Вн   | WPCR                  | Watch prescaler control register                        | R/W      | 0000000В              |

| 000Сн   | WDTC                  | Watchdog timer control register                         | R/W      | 00XX0000 <sub>B</sub> |

| 000Дн   | SYCC2                 | System clock control register 2                         | R/W      | XXXX0011 <sub>B</sub> |

| 000Ен   | STBC2                 | Standby control register 2                              | R/W      | 0000000в              |

| 000Fн   |                       |                                                         |          |                       |

| to      | _                     | (Disabled)                                              |          |                       |

| 0027н   |                       | ,                                                       |          |                       |

| 0028н   | PDRF                  | Port F data register                                    | R/W      | 0000000в              |

| 0029н   | DDRF                  | Port F direction register                               | R/W      | 0000000в              |

| 002Ан   | PDRG                  | Port G data register                                    | R/W      | 0000000в              |

| 002Вн   | DDRG                  | Port G direction register                               | R/W      | 0000000в              |

| 002Сн   | PUL0                  | Port 0 pull-up register                                 |          | 0000000в              |

| 002Dн   |                       |                                                         |          |                       |

| to      | _                     | (Disabled)                                              | _        |                       |

| 0034н   |                       | ,                                                       |          |                       |

| 0035н   | PULG                  | Port G pull-up register                                 | R/W      | 0000000В              |

| 0036н   | T01CR1                | 8/16-bit composite timer 01 status control register 1   | R/W      | 0000000в              |

| 0037н   | T00CR1                | 8/16-bit composite timer 00 status control register 1   | R/W      | 0000000в              |

| 0038н   |                       | ·                                                       |          |                       |

| to      | _                     | (Disabled)                                              | _        |                       |

| 0048н   |                       |                                                         |          |                       |

| 0049н   | EIC10                 | External interrupt circuit control register ch. 2/ch. 3 | R/W      | 0000000В              |

| 004Ан   | EIC20                 | External interrupt circuit control register ch. 4/ch. 5 | R/W      | 0000000В              |

| 004Вн   | EIC30                 | External interrupt circuit control register ch. 6/ch. 7 | R/W      | 0000000В              |

| 004Сн,  |                       | ,                                                       |          |                       |

| 004Dн   | <del>-</del>          | (Disabled)                                              | -        |                       |

| 004Ен   | LVDR                  | LVDR reset voltage selection ID register                | R/W      | 0000000В              |

| 004Fн   | _                     | (Disabled)                                              | <u> </u> | _                     |

# 24.3 DC Characteristics

(Vcc = 5.0 V  $\pm$  10%, Vss = 0.0 V, Ta = -40 °C to +85 °C)

|                                                        | Value            |                                                                                            |                                          |           |     | •         |      | V, TA = -40 C to +63                           |

|--------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------|------------------------------------------|-----------|-----|-----------|------|------------------------------------------------|

| Parameter                                              | Symbol           | Pin name                                                                                   | Condition                                | Min       | Тур | Max       | Unit | Remarks                                        |

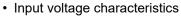

|                                                        | VIH              | P04                                                                                        | _                                        | 0.7 Vcc   | _   | Vcc + 0.3 | V    | Hysteresis input                               |

| "H" level<br>input voltage                             | V <sub>IHS</sub> | P00*3 to P03*4,<br>P05 to P07*4,<br>P12,<br>P62 to P64*3,<br>PF0*4, PF1*4,<br>PG1*4, PG2*4 | _                                        | 0.8 Vcc   |     | Vcc + 0.3 | V    | Hysteresis input                               |

|                                                        | Vінм             | PF2                                                                                        | _                                        | 0.8 Vcc   |     | Vcc + 0.3 | V    | Hysteresis input                               |

|                                                        | VIL              | P04                                                                                        | _                                        | Vss - 0.3 | _   | 0.3 Vcc   | V    | Hysteresis input                               |

| "L" level<br>input voltage                             | VILS             | P00*3 to P03*4,<br>P05 to P07*4,<br>P12,<br>P62 to P64*3,<br>PF0*4, PF1*4,<br>PG1*4, PG2*4 | _                                        | Vss - 0.3 |     | 0.2 Vcc   | V    | Hysteresis input                               |

|                                                        | VILM             | PF2                                                                                        | _                                        | Vss - 0.3 | _   | 0.2 Vcc   | V    | Hysteresis input                               |

| Open-drain<br>output<br>application<br>voltage         | VD               | P12, PF2                                                                                   | _                                        | Vss - 0.3 | _   | Vss + 5.5 | V    |                                                |

| "H" level                                              | Vон1             | P04, PF0*4,<br>PF1*4, PG1*4,<br>PG2                                                        | Iон = -4 mA                              | Vcc - 0.5 | _   | _         | V    |                                                |

| output<br>voltage                                      | V <sub>OH2</sub> | P00*3 to P03*4,<br>P05 to P07*4,<br>P62 to P64*3                                           | Iон = −8 mA                              | Vcc - 0.5 | _   | _         | V    |                                                |

| "L" level                                              | V <sub>OL1</sub> | P04, P12,<br>PF0 to PF2*4,<br>PG1*4, PG2*4                                                 | IoL = 4 mA                               | _         |     | 0.4       | V    |                                                |

| voltage                                                | V <sub>OL2</sub> | P00*3 to P03*4,<br>P05 to P07*4,<br>P62 to P64*3                                           | IoL = 12 mA                              | _         |     | 0.4       | V    |                                                |

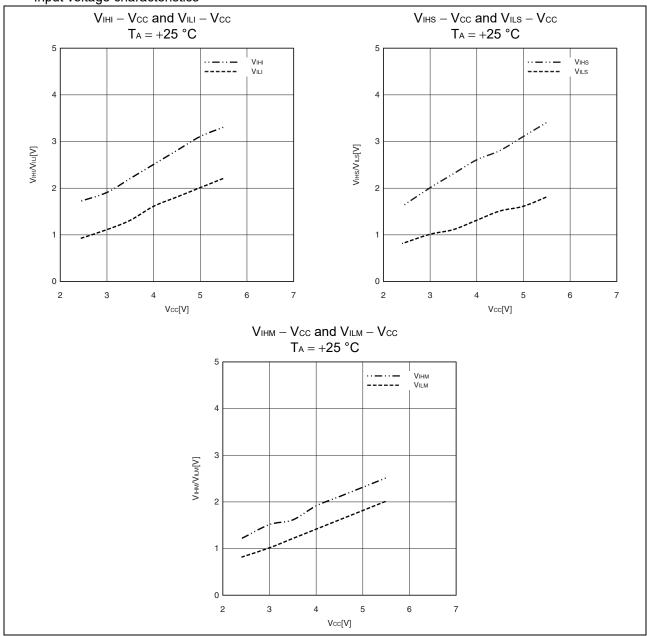

| Input leak<br>current (Hi-Z<br>output leak<br>current) | lu               | All input pins                                                                             | 0.0 V < V <sub>I</sub> < V <sub>CC</sub> | -5        | —   | +5        | μΑ   | When the internal pull-up resistor is disabled |

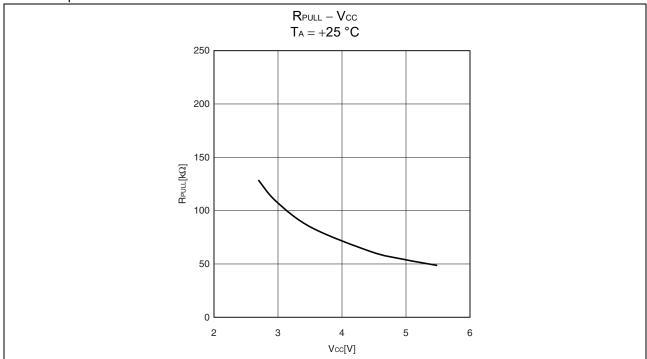

| Internal<br>pull-up<br>resistor                        | Rpull            | P00*3 to P07*4,<br>P62 to P64*3,<br>PG1*4, PG2*4                                           | V <sub>I</sub> = 0 V                     | 25        | 50  | 100       | kΩ   | When the internal pull-up resistor is enabled  |

| Input<br>capacitance                                   | Cin              | Other than Vcc<br>and Vss                                                                  | f = 1 MHz                                | _         | 5   | 15        | pF   |                                                |

#### 24.4.2 Source Clock / Machine Clock

$(Vcc = 5.0 V \pm 10\%, Vss = 0.0 V, T_A = -40 °C to +85 °C)$

| Doromotor     | Cymbol        | Pin          |         | Value  |        | Unit   | Domorko                                           |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|---------------|---------------|--------------|---------|--------|--------|--------|---------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|--|--|--|----------------------------------------|

| Parameter     | Symbol        | name         | Min     | Тур    | Max    | Unit   | Remarks                                           |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | When the main external clock is used              |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              | 61.5    | _      | 2000   | ns     | Min: FcH = 32.5 MHz, divided by 2                 |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | Max: Fcн = 1 MHz, divided by 2                    |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | When the main CR clock is used                    |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| Source clock  | <b>t</b> sclk |              | 62.5    | _      | 1000   | ns     | Min: Fcrh = 4 MHz, multiplied by 4                |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| cycle time*1  | LSCLK         |              |         |        |        |        | Max: Fcrh = 4 MHz, divided by 4                   |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         | 61     |        | μs     | When the suboscillation clock is used             |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         | 01     |        | μδ     | FcL = 32.768 kHz, divided by 2                    |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         | 20     |        | μs     | When the sub-CR clock is used                     |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         | 20     |        |        | Fcrl = 100 kHz, divided by 2                      |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               | Fsp           |              | 0.5     | _      | 16.25  | MHz    |                                                   |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| Source clock  | 1 54          |              |         | 4      | 1      | MHz    |                                                   |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| frequency     | Fspl          | _            | -       | 16.384 | -      | kHz    | When the suboscillation clock is used             |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| почистоу      |               |              | _       | 50     | _      | kHz    | When the sub-CR clock is used                     |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | Fcrl = 100 kHz, divided by 2                      |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              | 61.5    | _      | 32000  | ns     | When the main oscillation clock is used           |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | Min: F <sub>SP</sub> = 16.25 MHz, no division     |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        |                                                   |                               |  |  |  |  |  |  |  |  |  |  |  | Max: $F_{SP} = 0.5$ MHz, divided by 16 |

| Machine clock | me*2          |              | 250     | _      | 1000   |        | When the main CR clock is used                    |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| cycle time*2  |               |              |         |        |        | ns     | Min: F <sub>SP</sub> = 4 MHz, no division         |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| (minimum      | <b>t</b> MCLK |              |         |        |        |        | Max: F <sub>SP</sub> = 4 MHz, divided by 4        |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| instruction   | LIVICER       |              |         |        |        |        | When the suboscillation clock is used             |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| execution     |               |              | 61      | _      | 976.5  | μs     | Min: F <sub>SPL</sub> = 16.384 kHz, no division   |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| time)         |               |              |         |        |        |        | Max: F <sub>SPL</sub> = 16.384 kHz, divided by 16 |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | When the sub-CR clock is used                     |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              | 20      | _      | 320    | μs     | Min: F <sub>SPL</sub> = 50 kHz, no division       |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              |         |        |        |        | Max: F <sub>SPL</sub> = 50 kHz, divided by 16     |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               | Fмp           |              | 0.031   |        | 16.25  | MHz    | When the main oscillation clock is used           |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| Machine clock |               | I IVIP       | I IVIP  |        | 0.25   | _      | 16                                                | MHz                           |  |  |  |  |  |  |  |  |  |  |  |                                        |

| frequency     |               | <del>-</del> | 1.024   | _      | 16.384 | kHz    | When the suboscillation clock is used             |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

| nequency      | FMPL          | FMPL         |         | 3.125  |        | 50     | kHz                                               | When the sub-CR clock is used |  |  |  |  |  |  |  |  |  |  |  |                                        |

|               |               |              | 3.125 — |        | 50     | IXI IZ | Fcrl = 100 kHz                                    |                               |  |  |  |  |  |  |  |  |  |  |  |                                        |

<sup>\*1:</sup> This is the clock before it is divided according to the division ratio set by the machine clock division ratio select bits (SYCC:DIV[1:0]). This source clock is divided to become a machine clock according to the division ratio set by the machine clock division ratio select bits (SYCC:DIV[1:0]). In addition, a source clock can be selected from the following.

- · Main clock divided by 2

- · Main CR clock

- PLL multiplication of main CR clock (Select a multiplication rate from 2, 2.5, 3 and 4.)

- Subclock divided by 2

- Sub-CR clock divided by 2

- · Source clock (no division)

- · Source clock divided by 4

- · Source clock divided by 8

- · Source clock divided by 16

<sup>\*2:</sup> This is the operating clock of the microcontroller. A machine clock can be selected from the following.

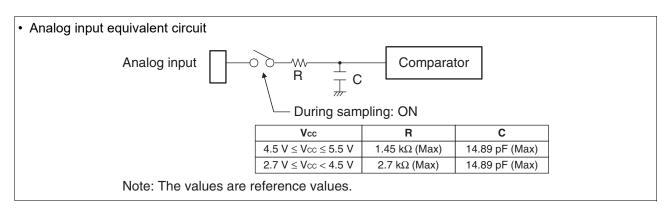

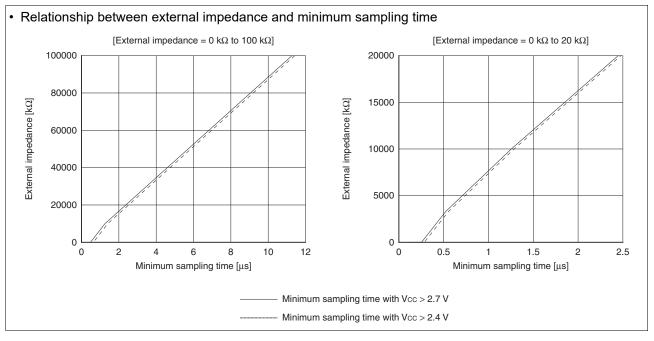

#### 24.5.2 Notes on Using A/D Converter

· External impedance of analog input and its sampling time

The A/D converter of the MB95560H/570H/580H has a sample and hold circuit. If the external impedance is too high to keep sufficient sampling time, the analog voltage charged to the capacitor of the internal sample and hold circuit is insufficient, adversely affecting A/D conversion precision. Therefore, to satisfy the A/D conversion precision standard, considering the relationship between the external impedance and minimum sampling time, either adjust the register value and operating frequency or decrease the external impedance so that the sampling time is longer than the minimum value. In addition, if sufficient sampling time cannot be secured, connect a capacitor of about 0.1  $\mu$ F to the analog input pin.

### • A/D conversion error

As |Vcc - Vss| decreases, the A/D conversion error increases proportionately.

$T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Subsleep mode with the external clock operating

$I_{\text{CCT}}-V_{\text{CC}}$

$T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Watch mode with the external clock operating

Iccтs – Vcc

$T_A = +25$  °C,  $F_{MP} = 2, 4, 8, 10, 16$  MHz (divided by 2) Time-base timer mode with the external clock operating

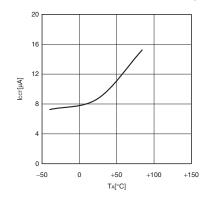

### Iccls - Ta

$V_{CC} = 5.5 \text{ V}, F_{MPL} = 16 \text{ kHz}$  (divided by 2) Subsleep mode with the external clock operating

ICCT - TA

$V_{\text{CC}} = 5.5 \text{ V}, \; F_{\text{MPL}} = 16 \text{ kHz} \; \text{(divided by 2)}$  Watch mode with the external clock operating

$I_{\text{CCTS}} - T_{\text{A}}$

$V_{\text{CC}} = 5.5 \text{ V}, \, F_{\text{MP}} = 10, \, 16 \, \text{MHz} \, (\text{divided by 2})$  Time-base timer mode with the external clock operating

# 27. Ordering Information

| Part number                                                                                                                                        | Package                          | Packing |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|

| MB95F562HWQN-G-SNE1<br>MB95F562KWQN-G-SNE1<br>MB95F563HWQN-G-SNE1<br>MB95F563KWQN-G-SNE1<br>MB95F564HWQN-G-SNE1<br>MB95F564KWQN-G-SNE1             | 32-pin plastic QFN               | Tray    |

| MB95F562HWQN-G-SNERE1<br>MB95F562KWQN-G-SNERE1<br>MB95F563HWQN-G-SNERE1<br>MB95F563KWQN-G-SNERE1<br>MB95F564HWQN-G-SNERE1<br>MB95F564KWQN-G-SNERE1 | (WNP032)                         | Reel    |

| MB95F562HPF-G-SNE2<br>MB95F562KPF-G-SNE2<br>MB95F563HPF-G-SNE2<br>MB95F563KPF-G-SNE2<br>MB95F564HPF-G-SNE2<br>MB95F564KPF-G-UNE2                   | 20-pin plastic SOP<br>(SOJ020)   | Tube    |

| MB95F562HPFT-G-SNE2<br>MB95F562KPFT-G-SNE2<br>MB95F563HPFT-G-SNE2<br>MB95F563KPFT-G-SNE2<br>MB95F564HPFT-G-SNE2<br>MB95F564KPFT-G-UNE2             | 20-pin plastic TSSOP<br>(STG020) | Tube    |

| MB95F562KPFT-G-UNERE2<br>MB95F563HPFT-G-UNERE2<br>MB95F563KPFT-G-UNERE2<br>MB95F564KPFT-G-UNERE2                                                   |                                  | Reel    |

| MB95F582HWQN-G-SNE1<br>MB95F582KWQN-G-SNE1<br>MB95F583HWQN-G-SNE1<br>MB95F583KWQN-G-SNE1<br>MB95F584HWQN-G-SNE1<br>MB95F584KWQN-G-SNE1             | 32-pin plastic QFN               | Tray    |

| MB95F582HWQN-G-SNERE1<br>MB95F582KWQN-G-SNERE1<br>MB95F583HWQN-G-SNERE1<br>MB95F583KWQN-G-SNERE1<br>MB95F584HWQN-G-SNERE1<br>MB95F584KWQN-G-SNERE1 | (WNP032)                         | Reel    |

| MB95F582HPFT-G-SNE2<br>MB95F582KPFT-G-SNE2<br>MB95F583HPFT-G-SNE2<br>MB95F583KPFT-G-SNE2<br>MB95F584HPFT-G-SNE2<br>MB95F584KPFT-G-SNE2             | 16-pin plastic TSSOP<br>(STB016) | Tube    |

| Package Type | Package Code |

|--------------|--------------|

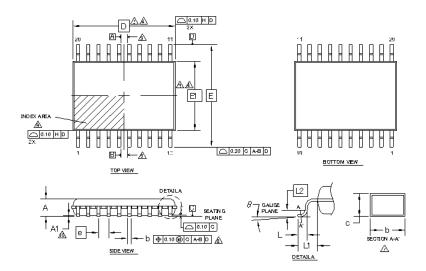

| TSSOP 20     | STG020       |

| SYMBOL  | DIMENSONS |         |      |  |  |

|---------|-----------|---------|------|--|--|

| STWIEDL | MIN.      | NOM.    | MAX. |  |  |

| A       | _         |         | 1.20 |  |  |

| A1      | 0.05      | _       | 0.15 |  |  |

| D       | 6         | 5.50B9C |      |  |  |

| E       | 6.40BSC   |         |      |  |  |

| E 1     | 4.40BSC   |         |      |  |  |

| 6       | 0°        | _       | 8*   |  |  |

| c       | 0.10      |         | 0.19 |  |  |

| ь       | 0.20      | 0.24    | 0.28 |  |  |

| L       | 0.45      | 0.60    | 0.75 |  |  |

| L 1     | 1.00 REF  |         |      |  |  |

| L 2     | 0.25 BSC  |         |      |  |  |

| e       | 0.65 BSC  |         |      |  |  |

| NOT | E8 |

|-----|----|

|     |    |

- 1. ALL DIMENSIONS ARE IN MILLIMETER.

- 2. DIMENSIONING AND TOLERANCING PER, ASVE Y14.5M 1994.

- A DIMENSIONING DINCLUDE MOLD FLASH, DIMENSIONING B1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION, INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED ⊎.025 Intil PER SIDE, D and E1 DIVENSION ARE DETERMINED A1 DATUM IT.

- ⚠ THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM.

DIMENSIONING DIANGET ARE DETERMINED AT THE OUTERMOST.

EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH,

THE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING

ANY MISNATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- $\triangle$  DATUMS A \$ B TO BE DETERMINED AT DATUM H.

- "N" IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

- $\triangle$  THE DIMENSION APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 min TO 0.25mm FROM THE LEAD TIP.

- À DIMENSION "IS DOES NOT INCLUDE THE DAMBAR PROTRUSION, ALLOW/BLE DAVBAR PROTRUSION STIALL BE 0.10mm FOTAL IN EXCESS OF THE "S" DIMENSION AT MAXIMAL MATERIAL CONDITION, THE DAMBAR MAY NOT BE LOCATED ON THE LOWER RADIUS OF "HE FOOT.

- ATHIS CHAMFER FEATURE IS OPTIONAL, LETITIS NOT PRESENT, THEN A PIN 1 IDENTIFIER MILIST BE LOCATED WITHIN THE INDEX AREA INDICATED

- A 1'A' IS DEFINED AS INTO VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY EXCLUDING THE LID AND OR THERMAL ENHANCEMENT ON CAVITY DOWN PACKAGE CONFIGURATIONS.

- 11. EDEOSPECIFICATON NO. REF: N/A

PÁCKÁGE OUTLINE, 20 LEÁD TSSOP 8.50x8.40x1.20 mm STG020 FEV®

002-15916 \*\*

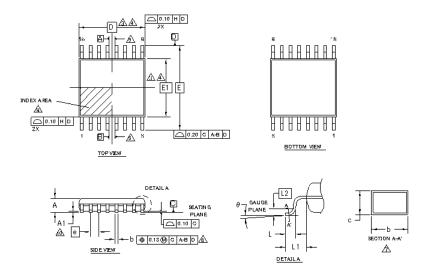

| Package Type | Package Code |

|--------------|--------------|

| TSSOP 16     | STB016       |

| SYMBOL  | DIN      | DIMENSONS |      |  |

|---------|----------|-----------|------|--|

| SIMIBUL | MIN.     | NOM.      | MAX. |  |

| A       | _        | _         | 120  |  |

| A1      | 0.05     | _         | 0.15 |  |

| D       | 4.96 BSC |           |      |  |

| E       | 6.40BSC  |           |      |  |

| E 1     | 4.40BSC  |           |      |  |

| 6       | 0°       | _         | 8°   |  |

| c       | 0.10     | _         | 0.19 |  |

| ь       | 0.16     | 0.24      | 0.32 |  |

| L       | 0.45     | 0.60      | 0.75 |  |

| L 1     | 1.00REF  |           |      |  |

| L 2     | 0.25 BSC |           |      |  |

| e       | 0.65 BSC |           |      |  |

1. ALL DIMENSIONS ARE IN MILLIMETER.

2. DIMENSIONING AND TOLERANCING PER, ASVE Y14.5M 1994.

⚠ DIMENSIONING DINCLUDE MOLD FLASH, DIMENSIONING BIDGES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION, INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.025 Imm PER SIDE, D and E1 DIVENSION ARE DETERMINED AT DATUM IT.

A THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM.

DIMENSIONING DIAGRET ARE DEFERMINED AT THE OUTERMOST

EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH,

THE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING

ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

ADATUMS A & B TO BE DETERMINED AT DATUM H.

"N" IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

$\triangle$  THE DIMENSION APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN  $0.49~\mathrm{min}$  TO 0.25mm FROM THE LEAD TIP.

TO 0.25mm FROM THE LEAD TIP.

ADMENSION "5" DOES NOT INCLUDE THE DAMBAR PROTRUSION. ALLOW/ISLE DAVBAR PROTRUSION SITALL BE 0.15mm TOTAL IN EXCESS OF THE "5" DIMENSION AT MAXIMUM MATERIAL CONDITION.

THE DAMBAR MAY NOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT.

⚠ THIS CHAMFER FEATURE IS OPTIONAL, LF IT IS NOT PRESENT. THEN A PIN 1 IDENTIFIER MILET BE LOCATED WITHIN THE INDEX AREA INDICATED.

AL 18 DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY EXCLUDING THE LID AND OR THERMAL ENHANCEMENT ON CAVITY DOWN PACKAGE CONFIGURATIONS. 11. JEDEOSPECIFICATION NO. REF: N/A

PÁCKÁGE OUTLINE, 16 LEÁD TSSÓP 4.96X8.40X1.20 MM STEO16 FEV®

002-15914 \*\*

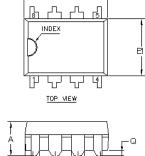

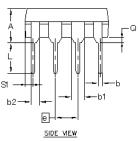

| Package Type | Package Code |

|--------------|--------------|

| DIP 8        | PDA008       |

| SYMBOL | DIN      | DIMENSIONS |      |  |

|--------|----------|------------|------|--|

| SIMBUL | MIN.     | NOM.       | MAX. |  |

| A      | _        | _          | 4.36 |  |

| L      | 3.00     | _          | _    |  |

| D      | 9.10     | 9.40       | 9.80 |  |

| E      | 7.52 TYP |            |      |  |

| E1     | 6.10     | 6.35       | 6.60 |  |

| 6      | _        | _          | 15°  |  |

| С      | 0.20     | 0.25       | 0.30 |  |

| ь      | 0.38     | 0.46       | 0.54 |  |

| b1     | _        | 1.52       | 1.82 |  |

| b2     | _        | 0.99       | 1.29 |  |

| e      | 2.54 TYP |            |      |  |

| S1     | 0.59     | 0.89       | 1.24 |  |

| Q      | 050      | _          | _    |  |

NOTES

1. ALL DIMENSIONS ARE IN MILLIMETER.

2. JED EC SPECIFICATION NO . REF : N/A

PACKAGE OUTLINE, 8 LEAD POIP 9.40X8.35X3.88 MM PDA008 REV®

002-16909 \*\*

| Page | Section                                 | Details                                                                                                                                                                                                                                             |

|------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48   | 48 2. Recommended Operating Conditions  | Revised note *2.  The value is 2.88 V when the low-voltage detection reset is used.  The minimum power supply voltage becomes 2.18 V when a product with the low-voltage detection reset is used.                                                   |

|      |                                         | Corrected the following statement in note *3.  The decoupling capacitor for the Vcc pin must have a capacitance larger than Cs.  →  The decoupling capacitor for the Vcc pin must have a capacitance equal to or larger than the capacitance of Cs. |

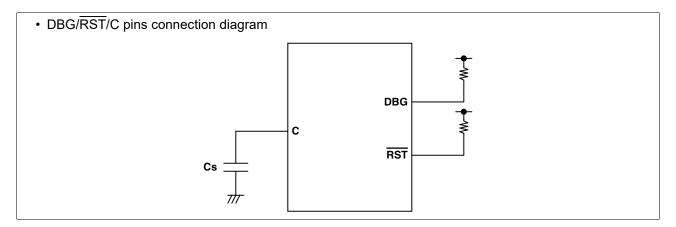

|      |                                         | Revised the remark in "• DBG/RST/C pins connection diagram".                                                                                                                                                                                        |

| 49   | 3. DC Characteristics                   | Revised the remark of the parameter "Input leak current (Hi-Z output leak current)".  When pull-up resistance is disabled  When the internal pull-up resistor is disabled                                                                           |

|      |                                         | Renamed the parameter "Pull-up resistance" to "Internal pull-up resistor".                                                                                                                                                                          |

|      |                                         | Revised the remark of the parameter "Internal pull-up resistor".  When pull-up resistance is enabled  →  When the internal pull-up resistor is enabled                                                                                              |

| 53   | AC Characteristics     (1) Clock Timing | Corrected the pin names of the parameter "Input clock rising time and falling time". $X0 \rightarrow X0$ , $X0A$ $X0$ , $X1$ $\rightarrow X0$ , $X1$ , $X0A$ , $X1A$                                                                                |

# Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc

Powermanagement ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless/Connectivity cypress.com/wireless

#### **PSoC® Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP| PSoC 6

### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2011-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-04629 Rev. \*E Revised November 21, 2017 Page 88 of 88