Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873a-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F87XA

|                                                     | PDIP | PLCC | TQFP | QFN  | I/O/P              | Buffer                 |                                                                                                                                                                     |

|-----------------------------------------------------|------|------|------|------|--------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | Pin# | Pin# | Pin# | Pin# | Туре               | Туре                   | Description                                                                                                                                                         |

| OSC1/CLKI<br>OSC1                                   | 13   | 14   | 30   | 32   | I                  | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>otherwise CMOS. |

| CLKI                                                |      |      |      |      | Ι                  |                        | External clock source input. Always associated<br>with pin function OSC1 (see OSC1/CLKI,<br>OSC2/CLKO pins).                                                        |

| OSC2/CLKO<br>OSC2                                   | 14   | 15   | 31   | 33   | 0                  | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal<br>Oscillator mode.                                |

| CLKO                                                |      |      |      |      | 0                  |                        | In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                |

| MCLR/VPP<br>MCLR                                    | 1    | 2    | 18   | 18   | I                  | ST                     | Master Clear (input) or programming voltage (output)<br>Master Clear (Reset) input. This pin is an active<br>low Reset to the device.                               |

| Vpp                                                 |      |      |      |      | Р                  |                        | Programming voltage input.                                                                                                                                          |

|                                                     |      |      | 10   | 10   |                    |                        | PORTA is a bidirectional I/O port.                                                                                                                                  |

| RA0/AN0<br>RA0<br>AN0                               | 2    | 3    | 19   | 19   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                                     |

| RA1/AN1<br>RA1<br>AN1                               | 3    | 4    | 20   | 20   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                     |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4    | 5    | 21   | 21   | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator VREF output.                                                                    |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                | 5    | 6    | 22   | 22   | I/O<br>I<br>I      | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                              |

| RA4/T0CKI/C1OUT<br>RA4                              | 6    | 7    | 23   | 23   | I/O                | ST                     | Digital I/O – Open-drain when configured as output.                                                                                                                 |

| T0CKI<br>C1OUT                                      |      |      |      |      | I<br>O             |                        | Timer0 external clock input.<br>Comparator 1 output.                                                                                                                |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT       | 7    | 8    | 24   | 24   | I/O<br>I<br>0      | TTL                    | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                  |

### TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### 2.2.2.8 PCON Register

bit 1

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

Note: BOR is unknown on Power-on Reset. It must be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     |     | _   | —   | —   | —   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

- bit 7-2 Unimplemented: Read as '0'

- **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# PIC16F87XA

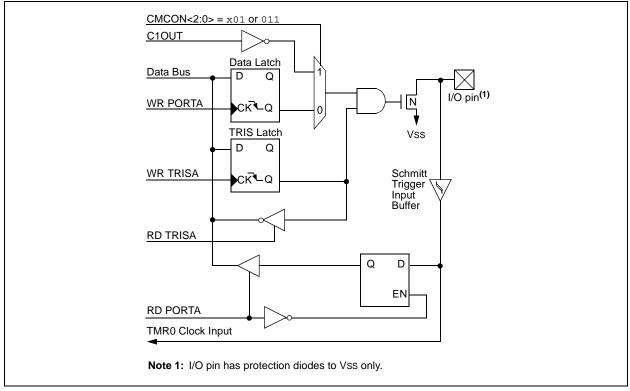

#### FIGURE 4-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

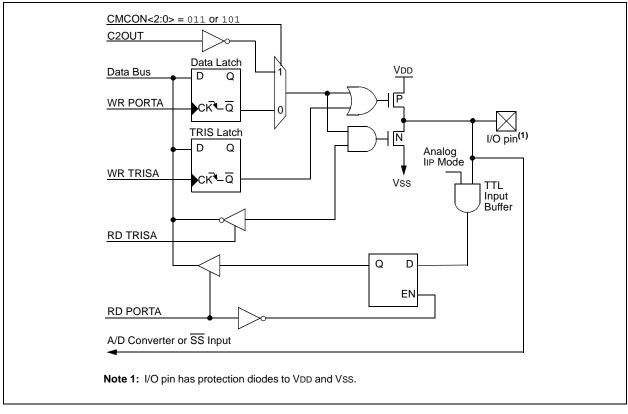

#### FIGURE 4-3: BLOCK DIAGRAM OF RA5 PIN

| Name                   | Bit#  | Buffer                | Function                                                                                                                                          |

|------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit 3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3:PORTB FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode or in-circuit debugger.

**3:** Low-Voltage ICSP Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

| TABLE 4-4: S | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value<br>POR, I |      | Valu<br>all o<br>Res | ther |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|--------|-----------------|------|----------------------|------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0    | XXXX :          | xxxx | uuuu                 | uuuu |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       | 1111 1 | 1111            | 1111 | 1111                 |      |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0    | 1111 1          | 1111 | 1111                 | 1111 |

|           |            |       |                               |       |       |       |       |       |        |                 |      |                      |      |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

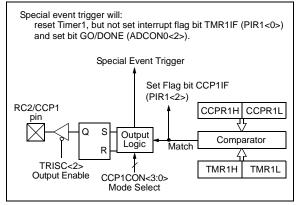

# 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

# 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2/CCP1 compare output latch to     |

|       | the default low level. This is not the   |

|       | PORTC I/O data latch.                    |

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

# 9.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

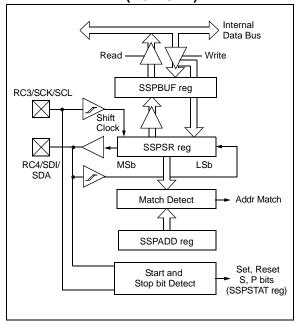

#### FIGURE 9-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

## 9.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON and SSPCON2 registers are readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the SSP is configured in  $I^2C$  Slave mode. When the SSP is configured in Master mode, the lower seven bits of SSPADD act as the baud rate generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

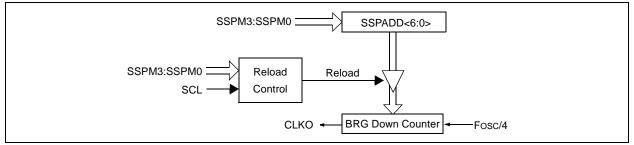

#### 9.4.7 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 9-17). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 9-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### FIGURE 9-17: BAUD RATE GENERATOR BLOCK DIAGRAM

# TABLE 9-3: I<sup>2</sup>C CLOCK RATE W/BRG

| Fcy    | FcY*2  | BRG Value     | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------------|------------------------------|

| 10 MHz | 20 MHz | 19h           | 400 kHz <sup>(1)</sup>       |

| 10 MHz | 20 MHz | 20h           | 312.5 kHz                    |

| 10 MHz | 20 MHz | 3Fh           | 100 kHz                      |

| 4 MHz  | 8 MHz  | 0Ah           | 400 kHz <sup>(1)</sup>       |

| 4 MHz  | 8 MHz  | 0Dh           | 308 kHz                      |

| 4 MHz  | 8 MHz  | 28h           | 100 kHz                      |

| 1 MHz  | 2 MHz  | 03h           | 333 kHz <sup>(1)</sup>       |

| 1 MHz  | 2 MHz  | 2 MHz 0Ah 100 |                              |

| 1 MHz  | 2 MHz  | 00h           | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

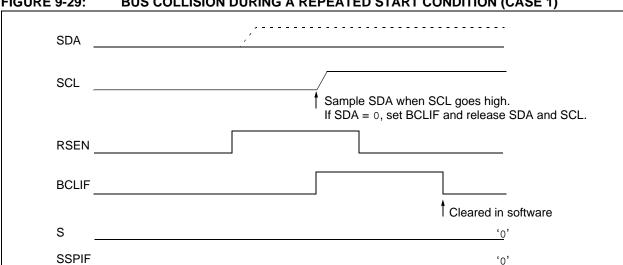

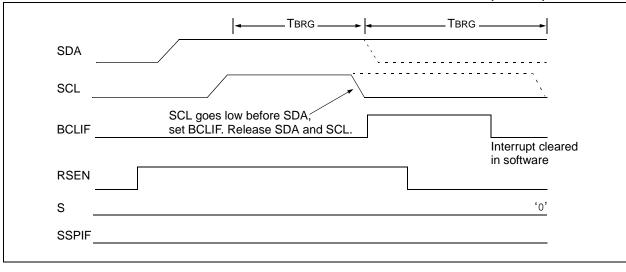

#### Bus Collision During a Repeated 9.4.17.2 Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 9-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 9-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 9-29: **BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)**

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the 40/44-pin devices.

The conversion of an analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low-voltage reference input that is software selectable to some combination of VDD, Vss, RA2 or RA3.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference) or as digital I/O.

Additional information on using the A/D module can be found in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| REGISTER 11-1: | ADCON0 REGISTER (ADDRESS 1Fh) |

|----------------|-------------------------------|

|----------------|-------------------------------|

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|----------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE  |     | ADON  |

| bit 7 |       |       |       |       | <u>.</u> |     | bit 0 |

bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in **bold**)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-3 CHS2:CHS0: Analog Channel Select bits

- 000 = Channel 0 (AN0)

- 001 = Channel 1 (AN1)

- 010 = Channel 2 (AN2)

- 011 = Channel 3 (AN3)

- 100 = Channel 4 (AN4)

- 101 = Channel 5 (AN5)

- 110 = Channel 6 (AN6)

- 111 = Channel 7 (AN7)

- **Note:** The PIC16F873A/876A devices only implement A/D channels 0 through 4; the unimplemented selections are reserved. Do not select any unimplemented channels with these devices.

bit 2 GO/DONE: A/D Conversion Status bit

<u>When ADON = 1:</u>

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

- bit 1 Unimplemented: Read as '0'

#### bit 0 ADON: A/D On bit

1 = A/D converter module is powered up

0 = A/D converter module is shut-off and consumes no operating current

# Legend:

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 12.2 Comparator Operation

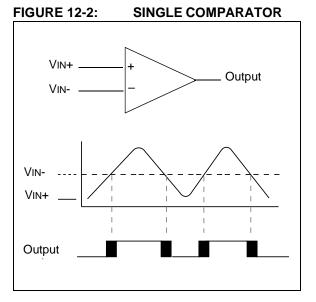

A single comparator is shown in Figure 12-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 12-2 represent the uncertainty due to input offsets and response time.

# 12.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 12-2).

### 12.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 12.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13.0 "Comparator Voltage Reference Module" contains a detailed description of the Comparator Voltage Reference module that provides this signal. The internal reference signal is used when comparators are in mode, CM<2:0> = 110 (Figure 12-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

# 12.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 17.0 "Electrical Characteristics").

# 12.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexors in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 12-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

- **3:** RA4 is an open collector I/O pin. When used as an output, a pull-up resistor is required.

| Address                | Name   | Bit 7        | Bit 6         | Bit 5   | Bit 4     | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|------------------------|--------|--------------|---------------|---------|-----------|------------|--------|--------|--------|-----------------|---------------------------------|

| 9Ch                    | CMCON  | C2OUT        | C10UT         | C2INV   | C1INV     | CIS        | CM2    | CM1    | CM0    | 0000 0111       | 0000 0111                       |

| 9Dh                    | CVRCON | CVREN        | CVROE         | CVRR    | _         | CVR3       | CVR2   | CVR1   | CVR0   | 000- 0000       | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE  | INTIE     | RBIE       | TMR0IF | INTIF  | RBIF   | x000 000x       | 0000 000u                       |

| 0Dh                    | PIR2   | _            | CMIF          | _       | _         | BCLIF      | LVDIF  | TMR3IF | CCP2IF | -0 0000         | -0 0000                         |

| 8Dh                    | PIE2   | —            | CMIE          | —       | —         | BCLIE      | LVDIE  | TMR3IE | CCP2IE | -0 0000         | -0 0000                         |

| 05h                    | PORTA  | —            | —             | RA5     | RA4       | RA3        | RA2    | RA1    | RA0    | 0x 0000         | Ou 0000                         |

| 85h                    | TRISA  | _            | _             | PORTA D | ata Direc | tion Regis | ster   |        |        | 11 1111         | 11 1111                         |

### TABLE 12-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

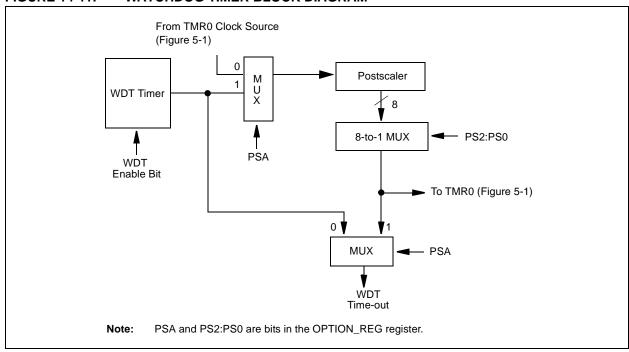

# 14.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 14.1 "Configuration Bits").

WDT time-out period values may be found in **Section 17.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

#### FIGURE 14-11: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h     | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | Fosc1 | Fosc0 |

| 81h, 181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 14-1 for operation of these bits.

| 15.2 | Instruction | Descriptions |

|------|-------------|--------------|

|------|-------------|--------------|

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

|                  | register.                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDWF            | Add W and f                                                                                                                                                    |

| Syntax:          | [label] ADDWF f,d                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

in register 'f'.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                           |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                      |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next instruc-<br>tion is executed. If the result is '0',<br>a NOP is executed instead, making<br>it a 2 TCY instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                          | Status Affected: | Z                                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

### 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

# 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

# TABLE 17-1: COMPARATOR SPECIFICATIONS

| Operating Conditions:3.0V < VDD < 5.5V, -40°C < TA < +85°C (unless otherwise stated)4.0V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated) |       |                               |     |       |            |          |                           |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|-----|-------|------------|----------|---------------------------|--|--|--|

| Param<br>No.                                                                                                                                         | Sym   | Characteristics               | Min | Тур   | Max        | Units    | Comments                  |  |  |  |

| D300                                                                                                                                                 | VIOFF | Input Offset Voltage          | _   | ± 5.0 | ± 10       | mV       |                           |  |  |  |

| D301                                                                                                                                                 | VICM  | Input Common Mode Voltage*    | 0   | -     | Vdd - 1.5  | V        |                           |  |  |  |

| D302                                                                                                                                                 | CMRR  | Common Mode Rejection Ratio*  | 55  | -     | _          | dB       |                           |  |  |  |

| 300<br>300A                                                                                                                                          | TRESP | Response Time <sup>*(1)</sup> | _   | 150   | 400<br>600 | ns<br>ns | PIC16F87XA<br>PIC16LF87XA |  |  |  |

| 301 TMC2OV Comparator Mode Change to — — 10 μs<br>Output Valid*                                                                                      |       |                               |     |       |            |          |                           |  |  |  |

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

# TABLE 17-2: VOLTAGE REFERENCE SPECIFICATIONS

| Operating   | Operating Conditions: $3.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) $4.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +125^{\circ}C$ (unless otherwise stated) |                               |        |    |            |            |                                             |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|----|------------|------------|---------------------------------------------|--|--|

| Spec<br>No. | SVM Characteristics Min IVn Max Units Comments                                                                                                                                               |                               |        |    |            |            |                                             |  |  |

| D310        | VRES                                                                                                                                                                                         | Resolution                    | Vdd/24 | —  | Vdd/32     | LSb        |                                             |  |  |

| D311        | VRAA                                                                                                                                                                                         | Absolute Accuracy             | _      | _  | 1/2<br>1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |  |

| D312        | VRur                                                                                                                                                                                         | Unit Resistor Value (R)*      | —      | 2k | —          | Ω          |                                             |  |  |

| 310         | TSET                                                                                                                                                                                         | Settling Time* <sup>(1)</sup> | —      | —  | 10         | μS         |                                             |  |  |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

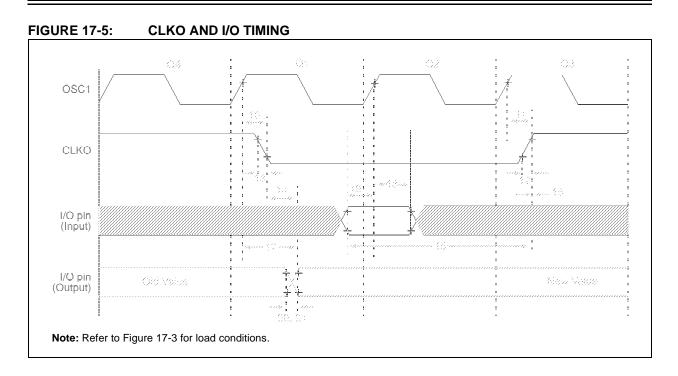

| Param<br>No. | Symbol   | Characteristic                     | Min           | Тур† | Мах | Units        | Conditions |          |

|--------------|----------|------------------------------------|---------------|------|-----|--------------|------------|----------|

| 10*          | TosH2ckL | OSC1 ↑ to CLKO $↓$                 |               | _    | 75  | 200          | ns         | (Note 1) |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                   |               | —    | 75  | 200          | ns         | (Note 1) |

| 12*          | TCKR     | CLKO Rise Time                     |               | —    | 35  | 100          | ns         | (Note 1) |

| 13*          | ТскF     | CLKO Fall Time                     |               | —    | 35  | 100          | ns         | (Note 1) |

| 14*          | TCKL2IOV | CLKO ↓ to Port Out Valid           |               | —    |     | 0.5 TCY + 20 | ns         | (Note 1) |

| 15*          | ТюV2скН  | Port In Valid before CLKO ↑        | Tosc + 200    | —    | _   | ns           | (Note 1)   |          |

| 16*          | TCKH2IOI | Port In Hold after CLKO ↑          | 0             | —    | _   | ns           | (Note 1)   |          |

| 17*          | TosH2IoV | OSC1 ↑ (Q1 cycle) to Port Out Va   | —             | 100  | 255 | ns           |            |          |

| 18*          | TosH2iol | OSC1 ↑ (Q2 cycle) to Port Input    | Standard (F)  | 100  | —   | —            | ns         |          |

|              |          | Invalid (I/O in hold time)         | Extended (LF) | 200  | —   | _            | ns         |          |

| 19*          | TIOV20sH | Port Input Valid to OSC1 ↑ (I/O in | setup time)   | 0    |     | —            | ns         |          |

| 20*          | TIOR     | Port Output Rise Time              | Standard (F)  | —    | 10  | 40           | ns         |          |

|              |          |                                    | Extended (LF) | —    |     | 145          | ns         |          |

| 21*          | TIOF     | Port Output Fall Time              | Standard (F)  | —    | 10  | 40           | ns         |          |

|              |          |                                    | Extended (LF) | —    |     | 145          | ns         |          |

| 22††*        | TINP     | INT pin High or Low Time           |               | Тсү  | —   | _            | ns         |          |

| 23††*        | Trbp     | RB7:RB4 Change INT High or Lo      | w Time        | Тсү  | —   | _            | ns         |          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

†† These parameters are asynchronous events not related to any internal clock edges.

**Note 1:** Measurements are taken in RC mode where CLKO output is 4 x Tosc.

\*

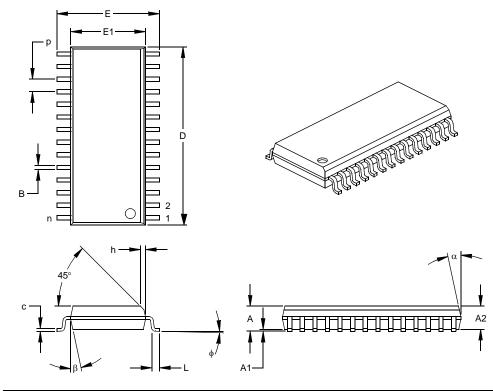

# 28-Lead Plastic Small Outline (SO) – Wide, 300 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       | INCHES* |      |      | N     | <b>1ILLIMETERS</b> | 5     |

|--------------------------|-------------|---------|------|------|-------|--------------------|-------|

| Dimens                   | sion Limits | MIN     | NOM  | MAX  | MIN   | NOM                | MAX   |

| Number of Pins           | n           |         | 28   |      |       | 28                 |       |

| Pitch                    | р           |         | .050 |      |       | 1.27               |       |

| Overall Height           | А           | .093    | .099 | .104 | 2.36  | 2.50               | 2.64  |

| Molded Package Thickness | A2          | .088    | .091 | .094 | 2.24  | 2.31               | 2.39  |

| Standoff §               | A1          | .004    | .008 | .012 | 0.10  | 0.20               | 0.30  |

| Overall Width            | E           | .394    | .407 | .420 | 10.01 | 10.34              | 10.67 |

| Molded Package Width     | E1          | .288    | .295 | .299 | 7.32  | 7.49               | 7.59  |

| Overall Length           | D           | .695    | .704 | .712 | 17.65 | 17.87              | 18.08 |

| Chamfer Distance         | h           | .010    | .020 | .029 | 0.25  | 0.50               | 0.74  |

| Foot Length              | L           | .016    | .033 | .050 | 0.41  | 0.84               | 1.27  |

| Foot Angle Top           | ø           | 0       | 4    | 8    | 0     | 4                  | 8     |

| Lead Thickness           | С           | .009    | .011 | .013 | 0.23  | 0.28               | 0.33  |

| Lead Width               | В           | .014    | .017 | .020 | 0.36  | 0.42               | 0.51  |

| Mold Draft Angle Top     | α           | 0       | 12   | 15   | 0     | 12                 | 15    |

| Mold Draft Angle Bottom  | β           | 0       | 12   | 15   | 0     | 12                 | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-052

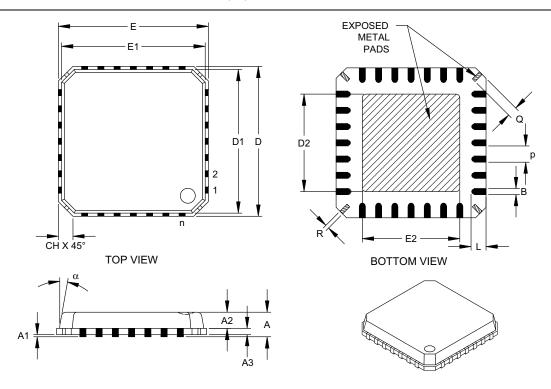

# 28-Lead Plastic Quad Flat No Lead Package (ML) 6x6 mm Body, Punch Singulated (QFN)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | INCHES |          |      | М        | ILLIMETERS | *    |

|--------------------------|--------|--------|----------|------|----------|------------|------|

| Dimension                | Limits | MIN    | NOM      | MAX  | MIN      | NOM        | MAX  |

| Number of Pins           | n      |        | 28       |      |          | 28         |      |

| Pitch                    | р      |        | .026 BSC |      |          | 0.65 BSC   |      |

| Overall Height           | Α      |        | .033     | .039 |          | 0.85       | 1.00 |

| Molded Package Thickness | A2     |        | .026     | .031 |          | 0.65       | 0.80 |

| Standoff                 | A1     | .000   | .0004    | .002 | 0.00     | 0.01       | 0.05 |

| Base Thickness           | A3     |        | .008 REF |      | 0.20 REF |            |      |

| Overall Width            | E      |        | .236 BSC |      | 6.00 BSC |            |      |

| Molded Package Width     | E1     |        | .226 BSC |      |          | 5.75 BSC   |      |

| Exposed Pad Width        | E2     | .140   | .146     | .152 | 3.55     | 3.70       | 3.85 |

| Overall Length           | D      |        | .236 BSC |      |          | 6.00 BSC   |      |

| Molded Package Length    | D1     |        | .226 BSC |      |          | 5.75 BSC   |      |

| Exposed Pad Length       | D2     | .140   | .146     | .152 | 3.55     | 3.70       | 3.85 |

| Lead Width               | В      | .009   | .011     | .014 | 0.23     | 0.28       | 0.35 |

| Lead Length              | L      | .020   | .024     | .030 | 0.50     | 0.60       | 0.75 |

| Tie Bar Width            | R      | .005   | .007     | .010 | 0.13     | 0.17       | 0.23 |

| Tie Bar Length           | Q      | .012   | .016     | .026 | 0.30     | 0.40       | 0.65 |

| Chamfer                  | СН     | .009   | .017     | .024 | 0.24     | 0.42       | 0.60 |

| Mold Draft Angle Top     | α      |        |          | 12°  |          |            | 12°  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC equivalent: mMO-220

Drawing No. C04-114

# PIC16F87XA

| Capture/Compare/PWM Requirements           |            |

|--------------------------------------------|------------|

| (CCP1 and CCP2)                            |            |

| CCP. See Capture/Compare/PWM.              |            |

| CCP1CON Register                           |            |

| CCP2CON Register                           |            |

| CCPR1H Register                            |            |

| CCPR1L Register                            | 19, 63     |

| CCPR2H Register                            |            |

| CCPR2L Register                            |            |

| CCPxM0 Bit                                 |            |

| CCPxM1 Bit                                 | 64         |

| CCPxM2 Bit                                 | 64         |

| CCPxM3 Bit                                 | 64         |

| CCPxX Bit                                  | 64         |

| CCPxY Bit                                  |            |

| CLKO and I/O Timing Requirements           | 183        |

| CMCON Register                             | 20         |

| Code Examples                              |            |

| Call of a Subroutine in Page 1 from Page 0 |            |

| Indirect Addressing                        |            |

| Initializing PORTA                         |            |

| Loading the SSPBUF (SSPSR) Register        |            |

| Reading Data EEPROM                        | 35         |

| Reading Flash Program Memory               |            |

| Saving Status, W and PCLATH Registers      |            |

| in RAM                                     |            |

| Writing to Data EEPROM                     |            |

| Writing to Flash Program Memory            |            |

| Code Protection                            | . 143, 157 |

| Comparator Module                          | 135        |

| Analog Input Connection                    |            |

| Considerations                             |            |

| Associated Registers                       |            |

| Configuration                              | 136        |

| Effects of a Reset                         | 139        |

| Interrupts                                 | 138        |

| Operation                                  |            |

| Operation During Sleep                     | 139        |

| Outputs                                    |            |

| Reference                                  |            |

| Response Time                              |            |

| Comparator Specifications                  |            |

| Comparator Voltage Reference               |            |

| Associated Registers                       |            |

| Computed GOTO                              |            |

| Configuration Bits                         | 143        |

| Configuration Word                         |            |

| Conversion Considerations                  |            |

| CVRCON Register                            |            |

| -                                          |            |

# D

| Data EEPROM and Flash Program Memory |    |

|--------------------------------------|----|

| EEADR Register                       |    |

| EEADRH Register                      |    |

| EECON1 Register                      | 33 |

| EECON2 Register                      | 33 |

| EEDATA Register                      |    |

| EEDATH Register                      |    |

|                                      |    |

| Data EEPROM Memory                          |         |

|---------------------------------------------|---------|

| Associated Registers                        | 39      |

| EEADR Register                              | 33      |

| EEADRH Register                             | 33      |

| EECON1 Register                             |         |

| EECON2 Register                             | 33      |

| Operation During Code-Protect               | 39      |

| Protection Against Spurious Writes          |         |

| Reading                                     | 35      |

| Write Complete Flag Bit (EEIF)              | 33      |

| Writing                                     |         |

| Data Memory                                 |         |

| Bank Select (RP1:RP0 Bits)                  |         |

| General Purpose Registers                   |         |

| Register File Map                           | 17, 18  |

| Special Function Registers                  |         |

| DC and AC Characteristics Graphs and Tables |         |

| DC Characteristics                          | 175–179 |

| Demonstration Boards                        |         |

| PICDEM 1                                    | 170     |

| PICDEM 17                                   | 170     |

| PICDEM 18R PIC18C601/801                    | 171     |

| PICDEM 2 Plus                               | 170     |

| PICDEM 3 PIC16C92X                          | 170     |

| PICDEM 4                                    | 170     |

| PICDEM LIN PIC16C43X                        | 171     |

| PICDEM USB PIC16C7X5                        | 171     |

| PICDEM.net Internet/Ethernet                | 170     |

| Development Support                         | 167     |

| Device Differences                          |         |

| Device Overview                             |         |

|                                             |         |

| Direct Addressing                           | 5       |

#### Ε

| EEADR Register                                      | 21, 33  |

|-----------------------------------------------------|---------|

| EEADRH Register                                     | 21, 33  |

| EECON1 Register                                     | 21, 33  |

| EECON2 Register                                     | 21, 33  |

| EEDATA Register                                     |         |

| EEDATH Register                                     |         |

| Electrical Characteristics                          | 173     |

| Errata                                              | 4       |

| Evaluation and Programming Tools                    | 171     |

| External Clock Timing Requirements                  |         |

| External Interrupt Input (RB0/INT). See Interrupt S | ources. |

| External Reference Signal                           | 137     |

|                                                     |         |

# F

| Firmware Instructions        | 159          |

|------------------------------|--------------|

| Flash Program Memory         |              |

| Associated Registers         | 39           |

| EECON1 Register              | 33           |

| EECON2 Register              | 33           |

| Reading                      | 36           |

| Writing                      | 37           |

| FSR Register                 | . 19, 20, 31 |

| G                            |              |

| General Call Address Support |              |