Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873a-i-so |

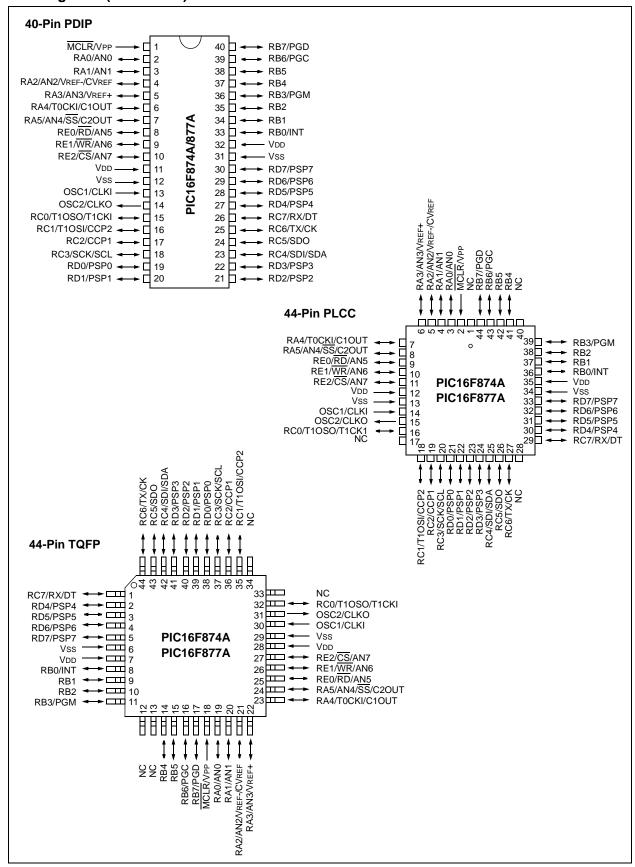

#### Pin Diagrams (Continued)

**TABLE 1-3:** PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

| Pin Name                                 | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type   | Buffer<br>Type | Description                                                                         |

|------------------------------------------|--------------|--------------|--------------|-------------|-----------------|----------------|-------------------------------------------------------------------------------------|

|                                          |              |              |              |             |                 |                | PORTC is a bidirectional I/O port.                                                  |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI | 15           | 16           | 32           | 34          | I/O<br>O<br>I   | ST             | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.           |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2   | 16           | 18           | 35           | 35          | I/O<br>I<br>I/O | ST             | Digital I/O. Timer1 oscillator input. Capture2 input, Compare2 output, PWM2 output. |

| RC2/CCP1<br>RC2<br>CCP1                  | 17           | 19           | 36           | 36          | I/O<br>I/O      | ST             | Digital I/O. Capture1 input, Compare1 output, PWM1 output.                          |

| RC3/SCK/SCL<br>RC3<br>SCK                | 18           | 20           | 37           | 37          | I/O<br>I/O      | ST             | Digital I/O. Synchronous serial clock input/output for SPI mode.                    |

| SCL                                      |              |              |              |             | I/O             |                | Synchronous serial clock input/output for I <sup>2</sup> C mode.                    |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA         | 23           | 25           | 42           | 42          | I/O<br>I<br>I/O | ST             | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                          |

| RC5/SDO<br>RC5<br>SDO                    | 24           | 26           | 43           | 43          | I/O<br>O        | ST             | Digital I/O.<br>SPI data out.                                                       |

| RC6/TX/CK<br>RC6<br>TX<br>CK             | 25           | 27           | 44           | 44          | I/O<br>O<br>I/O | ST             | Digital I/O. USART asynchronous transmit. USART1 synchronous clock.                 |

| RC7/RX/DT<br>RC7<br>RX<br>DT             | 26           | 29           | 1            | 1           | I/O<br>I<br>I/O | ST             | Digital I/O. USART asynchronous receive. USART synchronous data.                    |

Legend:

I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

**NOTES:**

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |

|-------|--------|-------|-------|-------|-------|-------|-------|--|--|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |  |  |

| bit 7 |        |       |       |       |       |       |       |  |  |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

#### Bit Value TMR0 Rate WDT Rate

| 000 | 1:2     | 1:1   |

|-----|---------|-------|

| 001 | 1:4     | 1:2   |

| 010 | 1:8     | 1:4   |

| 011 | 1:16    | 1:8   |

| 100 | 1:32    | 1:16  |

| 101 | 1:64    | 1:32  |

| 110 | 1 : 128 | 1:64  |

| 111 | 1:256   | 1:128 |

#### Legend:

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|--------------------|------------------|----------------------|--------------------|

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

**Note:** When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device

#### 3.3 Reading Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). The data is available in the very next cycle in the EEDATA register; therefore, it can be read in the next instruction (see Example 3-1). EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

The steps to reading the EEPROM data memory are:

- Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

#### **EXAMPLE 3-1: DATA EEPROM READ**

```

BSF

STATUS, RP1

BCF

STATUS, RPO

; Bank 2

DATA EE ADDR,W ; Data Memory

MOVF

MOVWF

; Address to read

BSF

STATUS, RPO

; Bank 3

BCF

EECON1, EEPGD ; Point to Data

; memory

BSF

EECON1,RD

; EE Read

; Bank 2

BCF

STATUS, RPO

MOVF

EEDATA,W

; W = EEDATA

```

#### 3.4 Writing to Data EEPROM Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment (see Example 3-2).

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- Write the 8-bit data value to be programmed in the EEDATA register.

- Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- · Set the WR bit

- 8. Enable interrupts (if using interrupts).

- Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### **EXAMPLE 3-2:** DATA EEPROM WRITE

| - 5 |                      |       |                         |                    |

|-----|----------------------|-------|-------------------------|--------------------|

|     |                      | BSF   | STATUS, RP1             | i                  |

|     |                      | BSF   | STATUS, RPO             |                    |

|     |                      | BTFSC | EECON1,WR               | ;Wait for write    |

|     |                      | GOTO  | \$-1                    | ;to complete       |

|     |                      | BCF   | STATUS, RP0             | ;Bank 2            |

|     |                      | MOVF  | DATA_EE_ADDR,W          | ;Data Memory       |

| l   |                      | MOVWF | EEADR                   | ;Address to write  |

|     |                      | MOVF  | DATA_EE_DATA,W          | ;Data Memory Value |

|     |                      | MOVWF | EEDATA                  | ;to write          |

|     |                      | BSF   | STATUS, RPO             | ;Bank 3            |

|     |                      | BCF   | EECON1, EEPGD           | ;Point to DATA     |

|     |                      |       |                         | ;memory            |

| l   |                      | BSF   | EECON1, WREN            | ;Enable writes     |

|     |                      |       |                         |                    |

| l   |                      | BCF   | INTCON, GIE             | ;Disable INTs.     |

| l   |                      | MOVLW |                         | ;                  |

| l   | g 9                  | MOVWF | EECON2<br>AAh<br>EECON2 | ;Write 55h         |

| l   | Required<br>Sequence | MOVLW | AAh                     | ;                  |

|     | Sed                  | MOVWF | EECON2                  | ;Write AAh         |

|     | ш 0)                 | BSF   | EECON1,WR               | ;Set WR bit to     |

|     | L_                   |       |                         | ;begin write       |

|     |                      | BSF   | INTCON, GIE             | ;Enable INTs.      |

|     |                      | BCF   | EECON1, WREN            | ;Disable writes    |

| ı   |                      |       |                         |                    |

#### 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

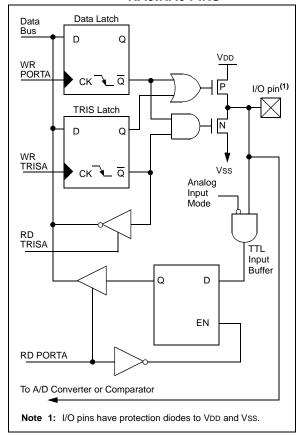

#### 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and the analog VREF input for both the A/D converters and the comparators. The operation of each pin is selected by clearing/setting the appropriate control bits in the ADCON1 and/or CMCON registers.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The comparators are in the off (digital) state.

The TRISA register controls the direction of the port pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### **EXAMPLE 4-1: INITIALIZING PORTA**

| BCF   | STATUS, | RP0   | ;                       |

|-------|---------|-------|-------------------------|

| BCF   | STATUS, |       |                         |

| CLRF  | PORTA   | 101 1 | ; Initialize PORTA by   |

| CLKF  | PORTA   |       | ,                       |

|       |         |       | ; clearing output       |

|       |         |       | ; data latches          |

| BSF   | STATUS, | RP0   | ; Select Bank 1         |

| MOVLW | 0x06    |       | ; Configure all pins    |

| MOVWF | ADCON1  |       | ; as digital inputs     |

| MOVLW | 0xCF    |       | ; Value used to         |

|       |         |       | ; initialize data       |

|       |         |       | ; direction             |

| MOVWF | TRISA   |       | ; Set RA<3:0> as inputs |

|       |         |       | ; RA<5:4> as outputs    |

|       |         |       | ; TRISA<7:6>are always  |

|       |         |       | ; read as '0'.          |

|       |         |       |                         |

## FIGURE 4-1: BLOCK DIAGRAM OF RA3:RA0 PINS

#### 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

#### 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate the shift clock.

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7                | Bit 6                    | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | Value<br>all o<br>Res | ther |

|-------------------------|--------|----------------------|--------------------------|---------|---------|---------|--------|---------|---------|---------------|------|-----------------------|------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                     | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000                  | 000u |

| 0Ch                     | PIR1   | PSPIF <sup>(1)</sup> | ADIF                     | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000                  | 0000 |

| 8Ch                     | PIE1   | PSPIE <sup>(1)</sup> | ADIE                     | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000                  | 0000 |

| 11h                     | TMR2   | Timer2 M             | Fimer2 Module's Register |         |         |         |        |         |         |               | 0000 | 0000                  | 0000 |

| 12h                     | T2CON  | _                    | TOUTPS3                  | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000                  | 0000 |

| 92h                     | PR2    | Timer2 P             | eriod Regis              | ter     |         |         |        |         |         | 1111          | 1111 | 1111                  | 1111 |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

**NOTES:**

#### 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 9.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- · Master mode

- · Multi-Master mode

- Slave mode

#### 9.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

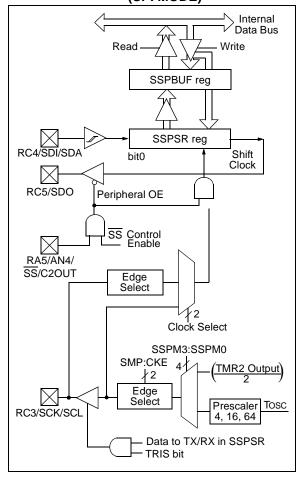

#### 9.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS) - RA5/AN4/SS/C2OUT

Figure 9-1 shows the block diagram of the MSSP module when operating in SPI mode.

FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

Note: When the SPI is in Slave mode with \$\overline{SS}\$ pin control enabled (SSPCON<3:0> = 0100), the state of the \$\overline{SS}\$ pin can affect the state read back from the TRISC<5> bit. The Peripheral OE signal from the SSP module in PORTC controls the state that is read back from the TRISC<5> bit (see Section 4.3 "PORTC and the TRISC Register" for information on PORTC). If Read-Modify-Write instructions, such as BSF, are performed on the TRISC register while the \$\overline{SS}\$ pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.

#### 9.3.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISC<4> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

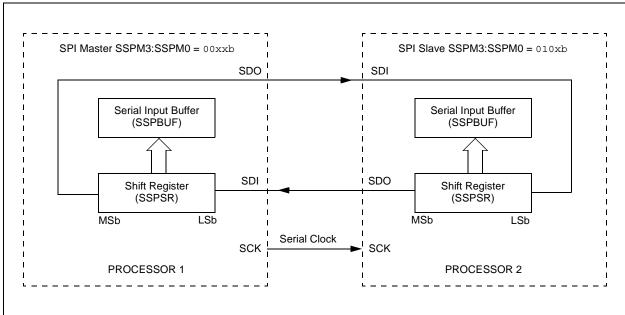

#### 9.3.4 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

FIGURE 9-2: SPI MASTER/SLAVE CONNECTION

#### 9.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 9.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.3.10 BUS MODE COMPATIBILITY

Table 9-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

TABLE 9-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | CKP                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also a SMP bit which controls when the data is sampled.

TABLE 9-2: REGISTERS ASSOCIATED WITH SPI OPERATION

| Name    | Bit 7                | Bit 6         | Bit 5                         | Bit 4      | Bit 3       | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR, BOR |      | all o | e on<br>other<br>sets |

|---------|----------------------|---------------|-------------------------------|------------|-------------|----------|--------|--------|----------------------|------|-------|-----------------------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IE                        | INT0IE     | RBIE        | TMR0IF   | INT0IF | RBIF   | 0000                 | 000x | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF                          | TXIF       | SSPIF       | CCP1IF   | TMR2IF | TMR1IF | 0000                 | 0000 | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE                          | TXIE       | SSPIE       | CCP1IE   | TMR2IE | TMR1IE | 0000                 | 0000 | 0000  | 0000                  |

| TRISC   | PORTC D              | ata Direc     | tion Regis                    | ter        |             |          |        |        | 1111                 | 1111 | 1111  | 1111                  |

| SSPBUF  | Synchron             | ous Seria     | l Port Rec                    | eive Buffe | er/Transmit | Register |        |        | xxxx                 | xxxx | uuuu  | uuuu                  |

| SSPCON  | WCOL                 | SSPOV         | SSPEN                         | CKP        | SSPM3       | SSPM2    | SSPM1  | SSPM0  | 0000                 | 0000 | 0000  | 0000                  |

| TRISA   | _                    | PORTA [       | PORTA Data Direction Register |            |             |          |        |        |                      |      | 11    | 1111                  |

| SSPSTAT | SMP                  | CKE           | $D/\overline{A}$              | Р          | S           | R/W      | UA     | BF     | 0000                 | 0000 | 0000  | 0000                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on 28-pin devices; always maintain these bits clear.

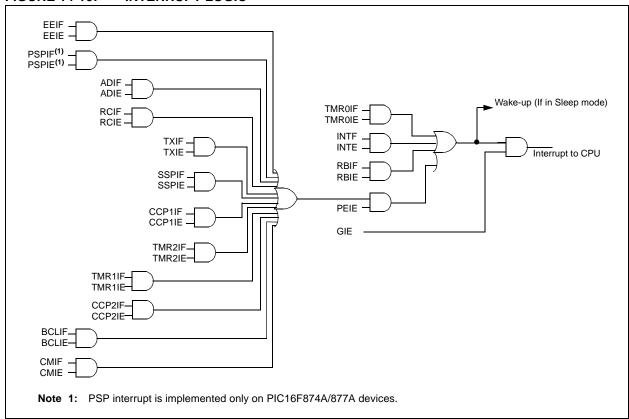

#### 9.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA while SCL outputs the serial clock. The first byte transmitted contains the slave <u>address</u> of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The baud rate generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 9.4.7 "Baud Rate Generator"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required Start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- Address is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- The user loads the SSPBUF with eight bits of data.

- Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- Interrupt is generated once the Stop condition is complete.

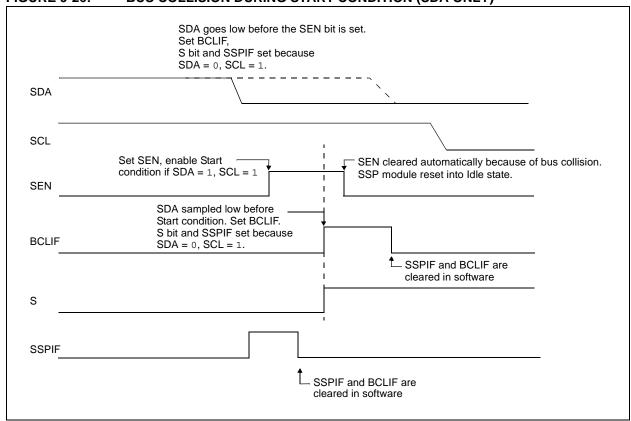

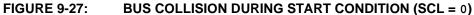

## 9.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 9-26).

- b) SCL is sampled low before SDA is asserted low (Figure 9-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 9-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

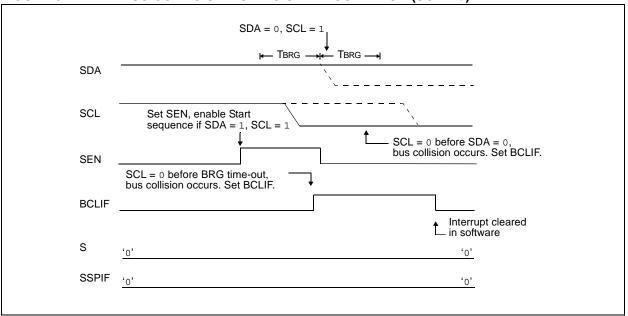

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pin is sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

FIGURE 9-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

#### FIGURE 9-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

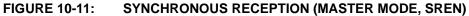

# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|---|-------|-------|-------|-------|-----|-------|------|-------|

|   | CSRC  | TX9   | TXEN  | SYNC  | _   | BRGH  | TRMT | TX9D  |

| b | oit 7 |       |       |       |     |       |      | bit 0 |

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care.

Synchronous mode:

- 1 = Master mode (clock generated internally from BRG)

- 0 = Slave mode (clock from external source)

- bit 6 **TX9**: 9-bit Transmit Enable bit

- 1 = Selects 9-bit transmission

- 0 = Selects 8-bit transmission

- bit 5 **TXEN**: Transmit Enable bit

- 1 = Transmit enabled

- 0 = Transmit disabled

Note: SREN/CREN overrides TXEN in Sync mode.

- bit 4 SYNC: USART Mode Select bit

- 1 = Synchronous mode

- 0 = Asynchronous mode

- bit 3 **Unimplemented:** Read as '0'

- bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

- 1 = High speed

- 0 = Low speed

Synchronous mode:

Unused in this mode.

- bit 1 TRMT: Transmit Shift Register Status bit

- 1 = TSR empty

- 0 = TSR full

- bit 0 **TX9D:** 9th bit of Transmit Data, can be Parity bit

| _ |   |   |   |   |   |   |

|---|---|---|---|---|---|---|

|   | _ | ~ | Δ | n | ᆈ | ١ |

| ᆫ | е | u | е | n | u | ľ |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit, CSRC (TXSTA<7>).

## 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- Enable the transmission by setting enable bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

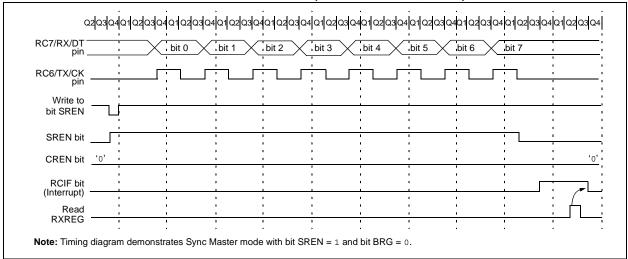

#### 14.11 Interrupts

The PIC16F87XA family has up to 15 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

**Note:** Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit, PEIE bit or GIE bit.

FIGURE 14-10: INTERRUPT LOGIC

RA4/TOCKI

RC0/T10SO/T1CKI

TMR0 or TMR1

Note: Refer to Figure 17-3 for load conditions.

TABLE 17-6: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol                        |                                                                                     | Characteristic                      | Min                   | Тур†                                      | Max | Units  | Conditions     |                                    |

|--------------|-------------------------------|-------------------------------------------------------------------------------------|-------------------------------------|-----------------------|-------------------------------------------|-----|--------|----------------|------------------------------------|

| 40*          | * TT0H T0CKI High Pulse Width |                                                                                     | No Prescaler                        | 0.5 Tcy + 20          | _                                         | _   | ns     | Must also meet |                                    |

|              |                               |                                                                                     |                                     | With Prescaler        | 10                                        | _   | _      | ns             | parameter 42                       |

| 41*          | TT0L                          |                                                                                     |                                     | No Prescaler          | 0.5 Tcy + 20                              | _   | _      | ns             | Must also meet                     |

|              |                               |                                                                                     |                                     | With Prescaler        | 10                                        | _   | _      | ns             | parameter 42                       |

| 42*          | Тт0Р                          |                                                                                     |                                     | No Prescaler          | Tcy + 40                                  | _   | _      | ns             |                                    |

|              |                               |                                                                                     |                                     | With Prescaler        | Greater of:<br>20 or <u>TCY + 40</u><br>N | _   | _      | ns             | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H                          | T1CKI High<br>Time                                                                  | Synchronous, Prescaler = 1          |                       | 0.5 Tcy + 20                              | _   | _      | ns             | Must also meet                     |

|              |                               |                                                                                     | Synchronous,<br>Prescaler = 2, 4, 8 | Standard(F)           | 15                                        | _   | _      | ns             | parameter 47                       |

|              |                               |                                                                                     |                                     | Extended( <b>LF</b> ) | 25                                        | _   | _      | ns             |                                    |

|              |                               |                                                                                     | Asynchronous                        | Standard(F)           | 30                                        | _   | _      | ns             |                                    |

|              |                               |                                                                                     |                                     | Extended( <b>LF</b> ) | 50                                        | _   | _      | ns             |                                    |

| 46*          | T <sub>T</sub> 1L             | T1CKI Low Time                                                                      | Synchronous, Prescaler = 1          |                       | 0.5 Tcy + 20                              | _   | _      | ns             | Must also meet                     |

|              |                               |                                                                                     | Synchronous,<br>Prescaler = 2, 4, 8 | Standard(F)           | 15                                        | _   | _      | ns             | parameter 47                       |

|              |                               |                                                                                     |                                     | Extended( <b>LF</b> ) | 25                                        | _   | _      | ns             |                                    |

|              |                               |                                                                                     | Asynchronous                        | Standard(F)           | 30                                        | _   |        | ns             |                                    |

|              |                               |                                                                                     |                                     | Extended( <b>LF</b> ) | 50                                        | _   |        | ns             |                                    |

| 47*          | TT1P                          | T1CKI Input<br>Period                                                               | Synchronous                         | Standard(F)           | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _   | 1      | ns             | N = prescale value (1, 2, 4, 8)    |

|              |                               |                                                                                     |                                     | Extended( <b>LF</b> ) | Greater of:<br>50 or <u>TCY + 40</u><br>N |     |        |                | N = prescale value<br>(1, 2, 4, 8) |

|              |                               |                                                                                     | Asynchronous                        | Standard(F)           | 60                                        | _   | _      | ns             |                                    |

|              |                               |                                                                                     |                                     | Extended( <b>LF</b> ) | 100                                       | _   | _      | ns             |                                    |

|              | FT1                           | Timer1 Oscillator Input Frequency Range (oscillator enabled by setting bit T1OSCEN) |                                     |                       | DC                                        |     | 200    | kHz            |                                    |

| 48           | TCKEZTMR1                     | Delay from External Clock Edge to Timer Increment                                   |                                     |                       | 2 Tosc                                    | _   | 7 Tosc | _              |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**TABLE 17-9: SPI MODE REQUIREMENTS**

| Param<br>No. | Symbol                | Characteristic                          | Min                                           | Тур†     | Max      | Units     | Conditions |  |

|--------------|-----------------------|-----------------------------------------|-----------------------------------------------|----------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | SS ↓ to SCK ↓ or SCK ↑ Input            | Tcy                                           |          | _        | ns        |            |  |

| 71*          | TscH                  | SCK Input High Time (Slave mode)        |                                               | Tcy + 20 | _        | _         | ns         |  |

| 72*          | TscL                  | SCK Input Low Time (Slave mode)         | Tcy + 20                                      | _        | _        | ns        |            |  |

| 73*          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDI Data Input to SCI     | 100                                           | _        | _        | ns        |            |  |

| 74*          | TscH2DIL,<br>TscL2DIL | Hold Time of SDI Data Input to SCK      | 100                                           | _        | _        | ns        |            |  |

| 75*          | TDOR                  | SDO Data Output Rise Time               | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _<br>_   | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TDOF                  | SDO Data Output Fall Time               | _                                             | 10       | 25       | ns        |            |  |

| 77*          | TssH2DoZ              | SS ↑ to SDO Output High-Impedance       | 10                                            | _        | 50       | ns        |            |  |

| 78*          | TscR                  | SCK Output Rise Time<br>(Master mode)   | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _        | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK Output Fall Time (Master mode       | _                                             | 10       | 25       | ns        |            |  |

| 80*          | TscH2DoV,<br>TscL2DoV | SDO Data Output Valid after<br>SCK Edge | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _        |          | 50<br>145 | ns         |  |

| 81*          | TDOV2SCH,<br>TDOV2SCL | SDO Data Output Setup to SCK Edg        | Tcy                                           | _        | _        | ns        |            |  |

| 82*          | TssL2DoV              | SDO Data Output Valid after SS ↓ E      | _                                             | _        | 50       | ns        |            |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                     | 1.5 Tcy + 40                                  | _        | _        | ns        |            |  |

These parameters are characterized but not tested.

FIGURE 17-15: I<sup>2</sup>C BUS START/STOP BITS TIMING

Note: Refer to Figure 17-3 for load conditions.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

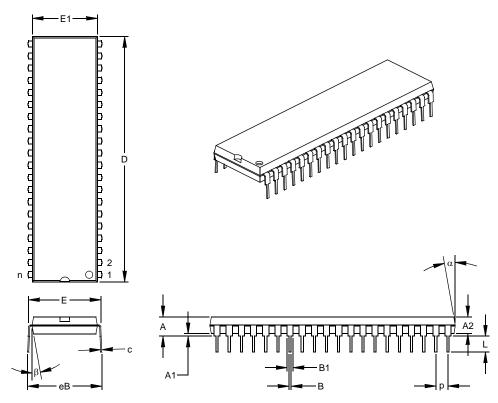

#### 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |     | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|-----|---------|-------|-------------|-------|-------|-------|

| Dimension                  | MIN | MOM     | MAX   | MIN         | NOM   | MAX   |       |

| Number of Pins             | n   |         | 40    |             |       | 40    |       |

| Pitch                      | р   |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α   | .160    | .175  | .190        | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2  | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1  | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | Е   | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1  | .530    | .545  | .560        | 13.46 | 13.84 | 14.22 |

| Overall Length             | D   | 2.045   | 2.058 | 2.065       | 51.94 | 52.26 | 52.45 |

| Tip to Seating Plane       | L   | .120    | .130  | .135        | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С   | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1  | .030    | .050  | .070        | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В   | .014    | .018  | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eВ  | .620    | .650  | .680        | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α   | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β   | 5       | 10    | 15          | 5     | 10    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-011

Drawing No. C04-016

<sup>\*</sup> Controlling Parameter § Significant Characteristic