Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873at-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

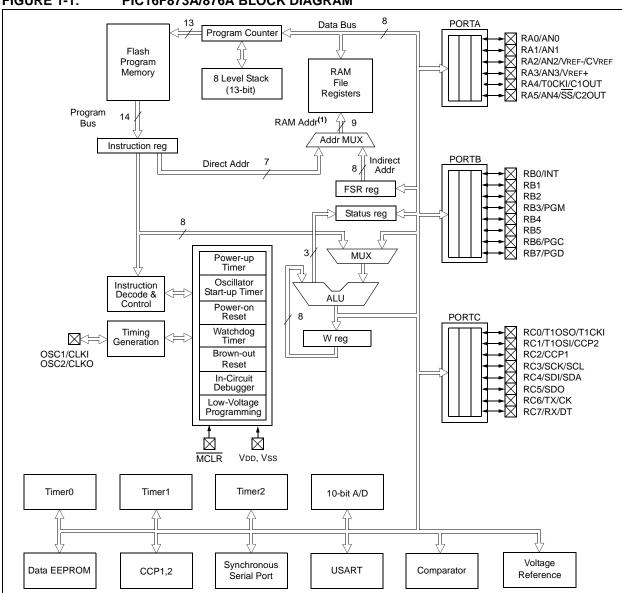

## 1.0 DEVICE OVERVIEW

This document contains device specific information about the following devices:

- PIC16F873A

- PIC16F874A

- PIC16F876A

- PIC16F877A

PIC16F873A/876A devices are available only in 28-pin packages, while PIC16F874A/877A devices are available in 40-pin and 44-pin packages. All devices in the PIC16F87XA family share common architecture with the following differences:

- The PIC16F873A and PIC16F874A have one-half of the total on-chip memory of the PIC16F876A and PIC16F877A

- The 28-pin devices have three I/O ports, while the 40/44-pin devices have five

- The 28-pin devices have fourteen interrupts, while the 40/44-pin devices have fifteen

- The 28-pin devices have five A/D input channels, while the 40/44-pin devices have eight

- The Parallel Slave Port is implemented only on the 40/44-pin devices

The available features are summarized in Table 1-1. Block diagrams of the PIC16F873A/876A and PIC16F874A/877A devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| Key Features                           | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Operating Frequency                    | DC – 20 MHz                                             |

| Resets (and Delays)                    | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 |

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | 8K                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Ports                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Timers                                 | 3                                                       | 3                                                       | 3                                                       | 3                                                       |

| Capture/Compare/PWM modules            | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Communications                | —                                                       | PSP                                                     | _                                                       | PSP                                                     |

| 10-bit Analog-to-Digital Module        | 5 input channels                                        | 8 input channels                                        | 5 input channels                                        | 8 input channels                                        |

| Analog Comparators                     | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Instruction Set                        | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

#### TABLE 1-1:PIC16F87XA DEVICE FEATURES

| Device     | vice Program Flash Data Memory |           | Data EEPROM |

|------------|--------------------------------|-----------|-------------|

| PIC16F873A | 4K words                       | 192 Bytes | 128 Bytes   |

| PIC16F876A | 8K words                       | 368 Bytes | 256 Bytes   |

Note 1: Higher order bits are from the Status register.

|                      | File<br>Address               | <i>F</i>                                                              | File<br>Address | <i>I</i>          | File<br>Address |                         | File<br>Addres |

|----------------------|-------------------------------|-----------------------------------------------------------------------|-----------------|-------------------|-----------------|-------------------------|----------------|

| ndirect addr.(       | *) 00h                        | Indirect addr.(*)                                                     | 80h             | Indirect addr.(*) | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                 | 01h                           | OPTION_REG                                                            | 81h             | TMR0              | 101h            | OPTION_REG              | 181h           |

| PCL                  | 02h                           | PCL                                                                   | 82h             | PCL               | 102h            | PCL                     | 182h           |

| STATUS               | 03h                           | STATUS                                                                | 83h             | STATUS            | 103h            | STATUS                  | 183h           |

| FSR                  | 04h                           | FSR                                                                   | 84h             | FSR               | 104h            | FSR                     | 184h           |

| PORTA                | 05h                           | TRISA                                                                 | 85h             |                   | 105h            |                         | 185h           |

| PORTB                | 06h                           | TRISB                                                                 | 86h             | PORTB             | 106h            | TRISB                   | 186h           |

| PORTC                | 07h                           | TRISC                                                                 | 87h             |                   | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup> | 08h                           | TRISD <sup>(1)</sup>                                                  | 88h             |                   | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup> | 09h                           | TRISE <sup>(1)</sup>                                                  | 89h             |                   | 109h            |                         | 189h           |

| PCLATH               | 0Ah                           | PCLATH                                                                | 8Ah             | PCLATH            | 10Ah            | PCLATH                  | 18Ah           |

| INTCON               | 0Bh                           | INTCON                                                                | 8Bh             | INTCON            | 10Bh            | INTCON                  | 18Bh           |

| PIR1                 | 0Ch                           | PIE1                                                                  | 8Ch             | EEDATA            | 10Ch            | EECON1                  | 18Ch           |

| PIR2                 | 0Dh                           | PIE2                                                                  | 8Dh             | EEADR             | 10Dh            | EECON2                  | 18Dh           |

| TMR1L                | 0Eh                           | PCON                                                                  | 8Eh             | EEDATH            | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                | 0Fh                           |                                                                       | 8Fh             | EEADRH            | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                | 10h                           |                                                                       | 90h             |                   | 110h            |                         | 190h           |

| TMR2                 | 11h                           | SSPCON2                                                               | 91h             |                   |                 |                         |                |

| T2CON                | 12h                           | PR2                                                                   | 92h             |                   |                 |                         |                |

| SSPBUF               | 13h                           | SSPADD                                                                | 93h             |                   |                 |                         |                |

| SSPCON               | 14h                           | SSPSTAT                                                               | 94h             |                   |                 |                         |                |

| CCPR1L               | 15h                           |                                                                       | 95h             |                   |                 |                         |                |

| CCPR1H               | 16h                           |                                                                       | 96h             |                   |                 |                         |                |

| CCP1CON              | 17h                           |                                                                       | 97h             |                   |                 |                         |                |

| RCSTA                | 18h                           | TXSTA                                                                 | 98h             |                   |                 |                         |                |

| TXREG                | 19h                           | SPBRG                                                                 | 99h             |                   |                 |                         |                |

| RCREG                | 1Ah                           |                                                                       | 9Ah             |                   |                 |                         |                |

| CCPR2L               | 1Bh                           |                                                                       | 9Bh             |                   |                 |                         |                |

| CCPR2H               | 1Ch                           | CMCON                                                                 | 9Ch             |                   |                 |                         |                |

| CCP2CON              | 1Dh                           | CVRCON                                                                | 9Dh             |                   |                 |                         |                |

| ADRESH               | 1Eh                           | ADRESL                                                                | 9Eh             |                   |                 |                         |                |

| ADCON0               | 1Fh                           | ADCON1                                                                | 9Fh             |                   | 120h            |                         | 1A0h           |

| General              | 20h                           | General                                                               | A0h             |                   | 12011           |                         |                |

| Purpose              |                               | Purpose                                                               |                 | accesses          |                 | accesses                |                |

| Register             |                               | Register                                                              |                 | 20h-7Fh           |                 | A0h - FFh               |                |

| 96 Bytes             |                               | 96 Bytes                                                              |                 |                   | 16Fh            |                         | 1EFh           |

|                      |                               | -                                                                     |                 |                   | 170h            |                         | 1F0h           |

|                      |                               |                                                                       |                 |                   |                 |                         |                |

| <b>D</b> 1 2         | 7Fh                           |                                                                       | FFh             | David C           | 17Fh            | Dersta 0                | 1FFh           |

| Bank 0               |                               | Bank 1                                                                |                 | Bank 2            |                 | Bank 3                  |                |

| * Not<br>ote 1: The  | a physical re<br>se registers | data memory loca<br>egister.<br>are not implemen<br>are reserved; mai | ted on the      | PIC16F873A.       |                 |                         |                |

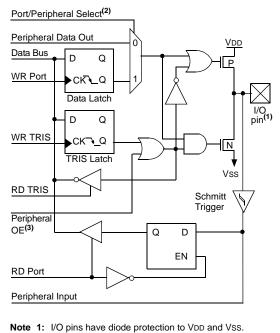

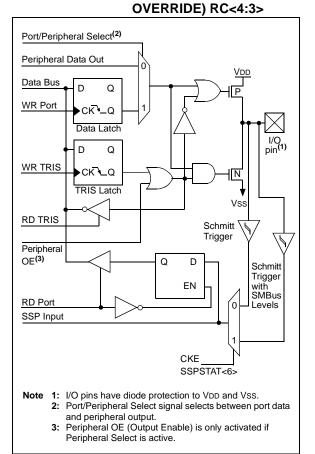

## 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels, by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as the destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 4-6: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

- Port/Peripheral Select signal selects between port

- data and peripheral output.

- **3:** Peripheral OE (Output Enable) is only activated if Peripheral Select is active.

#### FIGURE 4-7: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT

NOTES:

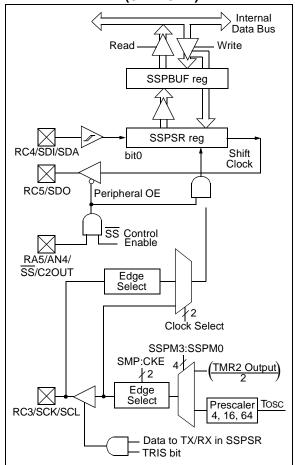

## 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 9.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

## 9.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

## 9.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/C2OUT

Figure 9-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 9-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

| Note: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON<3:0> = 0100),<br>the state of the SS pin can affect the state<br>read back from the TRISC<5> bit. The<br>Peripheral OE signal from the SSP mod-<br>ule in PORTC controls the state that is<br>read back from the TRISC<5> bit (see<br>Section 4.3 "PORTC and the TRISC<br>Register" for information on PORTC). If<br>Read-Modify-Write instructions, such as<br>BSF, are performed on the TRISC register<br>while the SS pin is high, this will cause the<br>TRISC of the table part thus displayed by |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | while the SS pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### 9.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON<5>).

The SSPCON register allows control of the I $^2$ C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I $^2$ C modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 9.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The buffer full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

#### 9.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

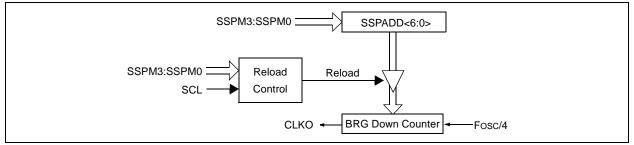

#### 9.4.7 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 9-17). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 9-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### FIGURE 9-17: BAUD RATE GENERATOR BLOCK DIAGRAM

### TABLE 9-3: I<sup>2</sup>C CLOCK RATE W/BRG

| Fcy    | FcY*2  | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|-----------|------------------------------|

| 10 MHz | 20 MHz | 19h       | 400 kHz <sup>(1)</sup>       |

| 10 MHz | 20 MHz | 20h       | 312.5 kHz                    |

| 10 MHz | 20 MHz | 3Fh       | 100 kHz                      |

| 4 MHz  | 8 MHz  | 0Ah       | 400 kHz <sup>(1)</sup>       |

| 4 MHz  | 8 MHz  | 0Dh       | 308 kHz                      |

| 4 MHz  | 8 MHz  | 28h       | 100 kHz                      |

| 1 MHz  | 2 MHz  | 03h       | 333 kHz <sup>(1)</sup>       |

| 1 MHz  | 2 MHz  | 0Ah       | 100 kHz                      |

| 1 MHz  | 2 MHz  | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

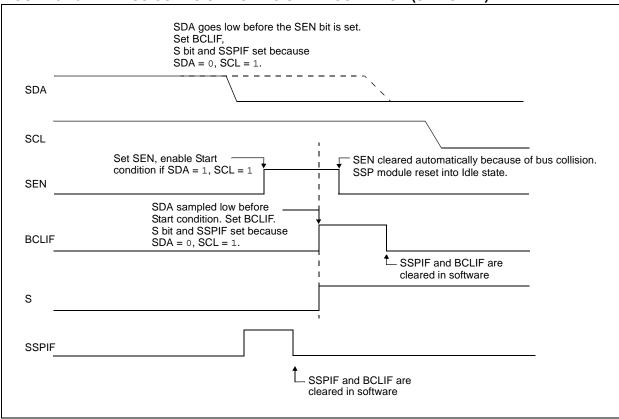

#### 9.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 9-26).

- b) SCL is sampled low before SDA is asserted low (Figure 9-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 9-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pin is sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 9-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

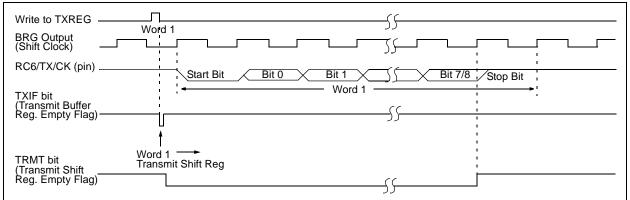

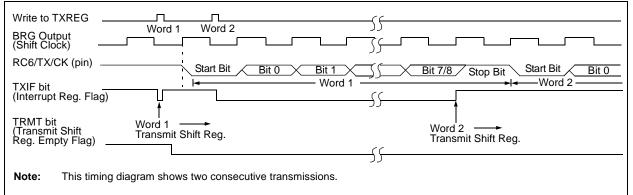

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3    | Bit 2      | Bit 1       | Bit 0      | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------|-----------|-----------|----------|------------|-------------|------------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE    | INTE      | RBIE     | TMR0IF     | INTF        | R0IF       | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | SSPIF    | CCP1IF     | TMR2IF      | TMR1IF     | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN      |          | FERR       | OERR        | RX9D       | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | nsmit Re | gister    |           |          |            |             |            | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | SSPIE    | CCP1IE     | TMR2IE      | TMR1IE     | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC      |          | BRGH       | TRMT        | TX9D       | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            |          | 0000 0000 | 0000 0000 |          |            |             |            |                       |                                 |

| Legend:                |        |                      |          | 0         |           | s '0' Sh | adad calls | are not use | d for asym | chronous trans        |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

## REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | —   | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |     |     |       |       |       | bit 0 |

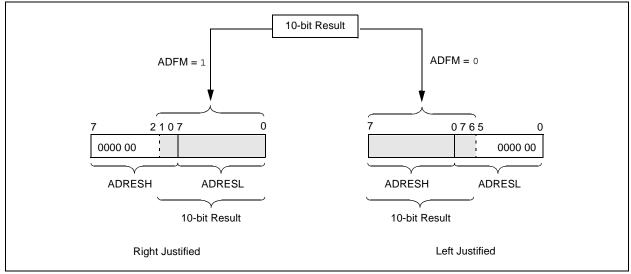

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

bit 6 ADCS2: A/D Conversion Clock Select bit (ADCON1 bits in shaded area and in bold)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-4 Unimplemented: Read as '0'

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits

| PCFG<br><3:0> | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R |

|---------------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-----|

| 0000          | Α   | Α   | А   | Α   | А     | А     | А   | Α   | Vdd   | Vss   | 8/0 |

| 0001          | А   | А   | А   | А   | VREF+ | А     | А   | А   | AN3   | Vss   | 7/1 |

| 0010          | D   | D   | D   | А   | А     | А     | А   | А   | Vdd   | Vss   | 5/0 |

| 0011          | D   | D   | D   | А   | VREF+ | А     | А   | А   | AN3   | Vss   | 4/1 |

| 0100          | D   | D   | D   | D   | А     | D     | А   | А   | Vdd   | Vss   | 3/0 |

| 0101          | D   | D   | D   | D   | VREF+ | D     | А   | А   | AN3   | Vss   | 2/1 |

| 011x          | D   | D   | D   | D   | D     | D     | D   | D   | —     | —     | 0/0 |

| 1000          | А   | А   | А   | А   | VREF+ | VREF- | А   | А   | AN3   | AN2   | 6/2 |

| 1001          | D   | D   | А   | А   | А     | А     | А   | А   | Vdd   | Vss   | 6/0 |

| 1010          | D   | D   | А   | А   | VREF+ | А     | А   | А   | AN3   | Vss   | 5/1 |

| 1011          | D   | D   | А   | А   | VREF+ | VREF- | А   | А   | AN3   | AN2   | 4/2 |

| 1100          | D   | D   | D   | А   | VREF+ | VREF- | А   | А   | AN3   | AN2   | 3/2 |

| 1101          | D   | D   | D   | D   | VREF+ | VREF- | А   | А   | AN3   | AN2   | 2/2 |

| 1110          | D   | D   | D   | D   | D     | D     | D   | А   | Vdd   | Vss   | 1/0 |

| 1111          | D   | D   | D   | D   | VREF+ | VREF- | D   | А   | AN3   | AN2   | 1/2 |

A = Analog input D = Digital I/O

C/R = # of analog input channels/# of A/D voltage references

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: On any device Reset, the port pins that are multiplexed with analog functions (ANx) are forced to be an analog input.

### 11.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion

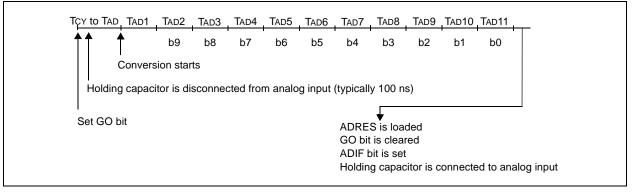

FIGURE 11-3: A/D CONVERSION TAD CYCLES

is aborted, the next acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

In Figure 11-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

#### 11.4.1 A/D RESULT REGISTERS

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16 bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 11-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

#### FIGURE 11-4: A/D RESULT JUSTIFICATION

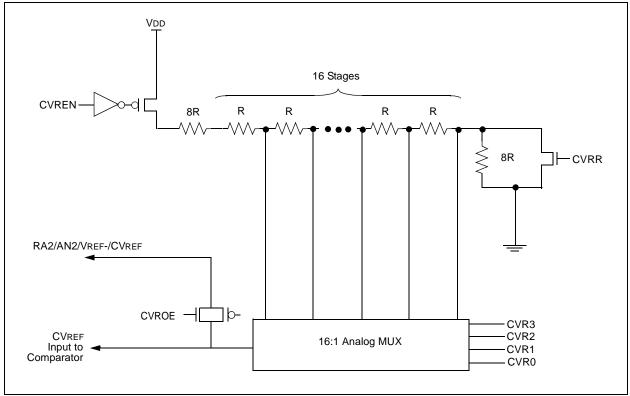

| TABLE 13-1: | REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE |

|-------------|--------------------------------------------------------|

|-------------|--------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 9Dh     | CVRCON | CVREN | CVROE | CVRR  |       | CVR3  | CVR2  | CVR1  | CVR0  | 000- 0000       | 000- 0000                       |

| 9Ch     | CMCON  | C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000 0111       | 0000 0111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

## 14.0 SPECIAL FEATURES OF THE CPU

All PIC16F87XA devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low-Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87XA devices have a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations. The erased or unprogrammed value of the Configuration Word register is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space which can be accessed only during programming.

## 14.4 MCLR

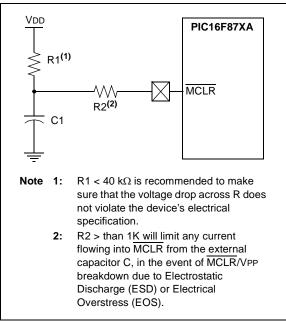

PIC16F87XA devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

The behavior of the ESD protection on the MCLR pin differs from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both Resets and current consumption outside of device specification during the Reset event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RCR network, as shown in Figure 14-5, is suggested.

FIGURE 14-5: RECOMMENDED MCLR CIRCUIT

## 14.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of <u>1.2V-1.7V</u>). To take advantage of the POR, tie the MCLR pin to VDD through an RC network, as described in **Section 14.4** "**MCLR**". A maximum rise time for VDD is specified. See **Section 17.0** "**Electrical Characteristics**" for details.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to application note, *AN607, "Power-up Trouble Shooting*" (DS00607).

## 14.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable or disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See **Section 17.0 "Electrical Characteristics"** for details (TPWRT, parameter #33).

## 14.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

## 14.8 Brown-out Reset (BOR)

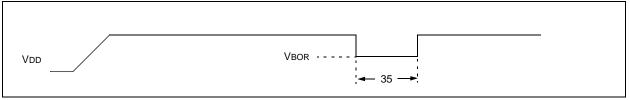

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a Reset may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in Reset for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 14.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87XA device operating in parallel.

Table 14-5 shows the Reset conditions for the Status, PCON and PC registers, while Table 14-6 shows the Reset conditions for all the registers.

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnemonic,<br>Operands                  |      | Description                                    | Cycles        |       | 14-Bit | Status | Notes |          |       |

|----------------------------------------|------|------------------------------------------------|---------------|-------|--------|--------|-------|----------|-------|

|                                        |      | Description                                    | Cycles        | MSb   |        |        | LSb   | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                                                |               |       |        |        |       |          |       |

| ADDWF                                  | f, d | Add W and f                                    | 1             | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d | AND W with f                                   | 1             | 00    | 0101   | dfff   | ffff  | Z        | 1,2   |

| CLRF                                   | f    | Clear f                                        | 1             | 00    | 0001   | lfff   | ffff  | Z        | 2     |

| CLRW                                   | -    | Clear W                                        | 1             | 00    | 0001   | 0xxx   | xxxx  | Z        |       |

| COMF                                   | f, d | Complement f                                   | 1             | 00    | 1001   | dfff   | ffff  | Z        | 1,2   |

| DECF                                   | f, d | Decrement f                                    | 1             | 00    | 0011   | dfff   | ffff  | Z        | 1,2   |

| DECFSZ                                 | f, d | Decrement f, Skip if 0                         | 1(2)          | 00    | 1011   | dfff   | ffff  |          | 1,2,3 |

| INCF                                   | f, d | Increment f                                    | 1             | 00    | 1010   | dfff   | ffff  | Z        | 1,2   |

| INCFSZ                                 | f, d | Increment f, Skip if 0                         | 1(2)          | 00    | 1111   | dfff   | ffff  |          | 1,2,3 |

| IORWF                                  | f, d | Inclusive OR W with f                          | 1             | 00    | 0100   | dfff   | ffff  | Z        | 1,2   |

| MOVF                                   | f, d | Move f                                         | 1             | 00    | 1000   | dfff   | ffff  | Z        | 1,2   |

| MOVWF                                  | f    | Move W to f                                    | 1             | 00    | 0000   | lfff   | ffff  |          |       |

| NOP                                    | -    | No Operation                                   | 1             | 00    | 0000   | 0xx0   | 0000  |          |       |

| RLF                                    | f, d | Rotate Left f through Carry                    | 1             | 00    | 1101   | dfff   | ffff  | С        | 1,2   |

| RRF                                    | f, d | Rotate Right f through Carry                   | 1             | 00    | 1100   | dfff   | ffff  | С        | 1,2   |

| SUBWF                                  | f, d | Subtract W from f                              | 1             | 00    | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d | Swap nibbles in f                              | 1             | 00    | 1110   | dfff   | ffff  |          | 1,2   |

| XORWF                                  | f, d | Exclusive OR W with f                          | 1             | 00    | 0110   | dfff   | ffff  | Z        | 1,2   |

|                                        |      | BIT-ORIENTED FILE                              | REGISTER OPER | ATION | ١S     |        |       |          |       |

| BCF                                    | f, b | Bit Clear f                                    | 1             | 01    | 00bb   | bfff   | ffff  |          | 1,2   |

| BSF                                    | f, b | Bit Set f                                      | 1             | 01    | 01bb   | bfff   | ffff  |          | 1,2   |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear                      | 1 (2)         | 01    | 10bb   | bfff   | ffff  |          | 3     |

| BTFSS                                  | f, b | Bit Test f, Skip if Set                        | 1 (2)         | 01    | 11bb   | bfff   | ffff  |          | 3     |

|                                        |      | LITERAL AND CO                                 | NTROL OPERAT  | IONS  |        |        |       |          |       |

| ADDLW                                  | k    | Add Literal and W                              | 1             | 11    | 111x   | kkkk   | kkkk  | C,DC,Z   |       |

| ANDLW                                  | k    | AND Literal with W                             | 1             | 11    | 1001   | kkkk   | kkkk  | Z        |       |

| CALL                                   | k    | Call Subroutine                                | 2             | 10    | 0kkk   | kkkk   | kkkk  |          |       |

| CLRWDT                                 | -    | Clear Watchdog Timer                           | 1             | 00    | 0000   | 0110   | 0100  | TO,PD    |       |

| GOTO                                   | k    | Go to Address                                  | 2             | 10    | 1kkk   | kkkk   | kkkk  | -        |       |

| IORLW                                  | k    | Inclusive OR Literal with W                    | 1             | 11    | 1000   | kkkk   | kkkk  | Z        |       |

| MOVLW                                  | k    | Move Literal to W                              | 1             | 11    | 00xx   | kkkk   | kkkk  |          |       |

| RETFIE                                 | -    | Return from Interrupt                          | 2             | 00    | 0000   | 0000   | 1001  |          |       |

| RETLW                                  | k    | Return with Literal in W                       | 2             | 11    | 01xx   | kkkk   |       |          |       |

| RETURN                                 | -    | Return from Subroutine                         | 2             | 00    | 0000   | 0000   | 1000  |          |       |

| SLEEP                                  | -    | Go into Standby mode                           | 1             | 00    | 0000   | 0110   | 0011  | TO,PD    |       |

| SUBLW                                  | k    | Subtract W from Literal                        | 1             | 11    |        | kkkk   |       | C,DC,Z   |       |

| XORLW                                  | k    | Exclusive OR Literal with W                    | 1             | 11    | 1010   | kkkk   |       | Z        |       |

| Note 1:                                |      | I/O register is modified as a function of itse |               |       |        |        |       |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                     |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                            |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

NOTES:

## 16.14 PICDEM 1 PIC MCU Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs.

### 16.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham.

## 16.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 Flash microcontrollers.

## 16.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

## 16.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8, 14, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow on-board hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

## 16.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board Flash memory. A generous prototype area is available for user hardware expansion.

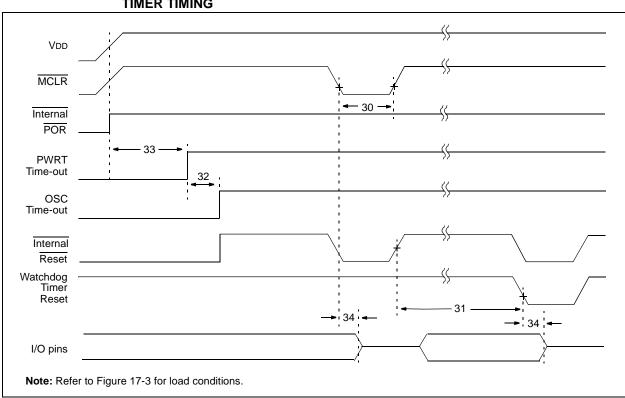

## FIGURE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### FIGURE 17-7: BROWN-OUT RESET TIMING

## TABLE 17-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Symbol | Characteristic                                           | Min | Тур†      | Max | Units | Conditions               |

|--------------|--------|----------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30           | TMCL   | MCLR Pulse Width (low)                                   | 2   | _         | -   | μS    | VDD = 5V, -40°C to +85°C |

| 31*          | Twdt   | Watchdog Timer Time-out Period<br>(no prescaler)         | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32           | Tost   | Oscillation Start-up Timer Period                        | —   | 1024 Tosc | _   | _     | Tosc = OSC1 period       |

| 33*          | TPWRT  | Power-up Timer Period                                    | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34           | Tıoz   | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | —   | _         | 2.1 | μS    |                          |

| 35           | TBOR   | Brown-out Reset Pulse Width                              | 100 | —         | _   | μS    | $VDD \leq VBOR (D005)$   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.