Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

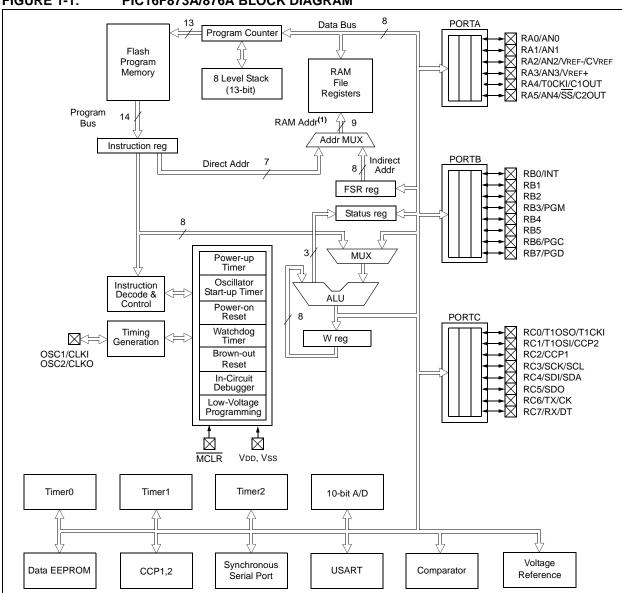

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

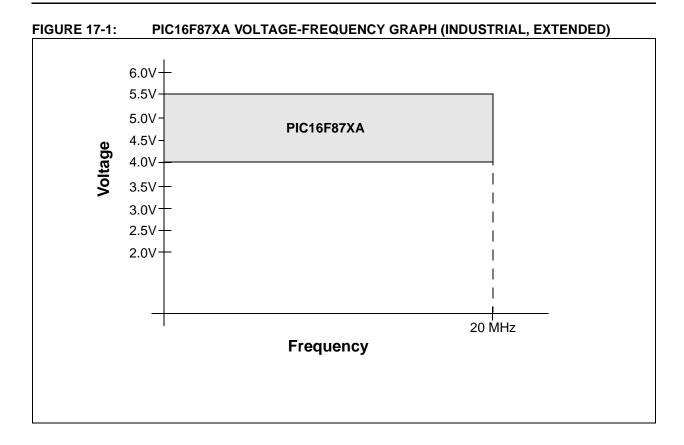

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

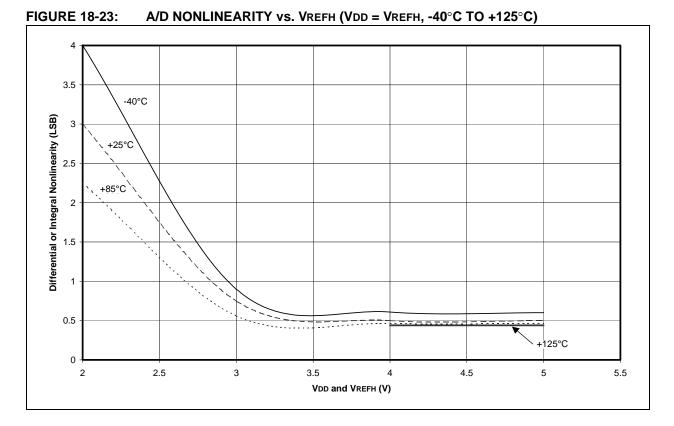

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874a-e-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device     | Program Flash | Data Memory | Data EEPROM |

|------------|---------------|-------------|-------------|

| PIC16F873A | 4K words      | 192 Bytes   | 128 Bytes   |

| PIC16F876A | 8K words      | 368 Bytes   | 256 Bytes   |

Note 1: Higher order bits are from the Status register.

| 1 1 4 1 | սու | 2-3: |  |

|---------|-----|------|--|

#### PIC16F876A/877A REGISTER FILE MAP

| Indirect addr.(*)    | 00h         | Indirect addr.(*)             |           | Indirect addr.(*)   | 100h          | Indirect addr.(*)       | 10 |

|----------------------|-------------|-------------------------------|-----------|---------------------|---------------|-------------------------|----|

| TMR0                 | 00n<br>01h  | OPTION REG                    | 80h       | TMR0                | 100h          | OPTION_REG              | 18 |

| PCL                  | 01h<br>02h  |                               | 81h       | PCL                 | 10111<br>102h |                         | 18 |

|                      | 02n<br>03h  | PCL<br>STATUS                 | 82h       | STATUS              | 10211<br>103h | PCL<br>STATUS           | 18 |

| STATUS               | 03n<br>04h  |                               | 83h       | FSR                 | 103n<br>104h  |                         | 18 |

| FSR                  |             | FSR                           | 84h       | FSR                 | 1041<br>105h  | FSR                     | 18 |

| PORTA                | 05h<br>06h  | TRISA                         | 85h       | DODTD               | 105h          | TRISB                   | 18 |

| PORTB                |             | TRISB                         | 86h       | PORTB               | 106n<br>107h  | TRISB                   | 18 |

|                      | 07h         | TRISC<br>TRISD <sup>(1)</sup> | 87h       |                     | 1071<br>108h  |                         | 18 |

| PORTD <sup>(1)</sup> | 08h         | TRISD <sup>(1)</sup>          | 88h       |                     | 109h          |                         | 18 |

| PORTE <sup>(1)</sup> | 09h         |                               | 89h       | PCLATH              | 1091<br>10Ah  | PCLATH                  | 18 |

| PCLATH               | 0Ah         | PCLATH                        | 8Ah       |                     | 10An<br>10Bh  | INTCON                  | 18 |

| INTCON               | 0Bh         | INTCON                        | 8Bh       | INTCON              | 10Bn<br>10Ch  | EECON1                  | 18 |

| PIR1                 | 0Ch         | PIE1                          | 8Ch       | EEDATA              |               |                         | 18 |

| PIR2                 | 0Dh         | PIE2                          | 8Dh       | EEADR               | 10Dh          | EECON2                  | 18 |

| TMR1L                | 0Eh         | PCON                          | 8Eh       | EEDATH              | 10Eh          | Reserved <sup>(2)</sup> | 18 |

| TMR1H                | 0Fh         |                               | 8Fh       | EEADRH              | 10Fh          | Reserved <sup>(2)</sup> | 18 |

| T1CON                | 10h         |                               | 90h       |                     | 110h          |                         | 19 |

| TMR2                 | 11h         | SSPCON2                       | 91h       |                     | 111h          |                         | 19 |

| T2CON                | 12h         | PR2                           | 92h       |                     | 112h          |                         | 19 |

| SSPBUF               | 13h         | SSPADD                        | 93h       |                     | 113h          |                         | 19 |

| SSPCON               | 14h         | SSPSTAT                       | 94h       |                     | 114h          |                         | 19 |

| CCPR1L               | 15h         |                               | 95h       |                     | 115h          |                         | 19 |

| CCPR1H               | 16h         |                               | 96h       | Conorol             | 116h          | Conorol                 | 19 |

| CCP1CON              | 17h         |                               | 97h       | General<br>Purpose  | 117h          | General<br>Purpose      | 19 |

| RCSTA                | 18h         | TXSTA                         | 98h       | Register            | 118h          | Register                | 19 |

| TXREG                | 19h         | SPBRG                         | 99h       | 16 Bytes            | 119h          | 16 Bytes                | 19 |

| RCREG                | 1Ah         |                               | 9Ah       |                     | 11Ah          |                         | 19 |

| CCPR2L               | 1Bh         |                               | 9Bh       |                     | 11Bh          |                         | 19 |

| CCPR2H               | 1Ch         | CMCON                         | 9Ch       |                     | 11Ch          |                         | 19 |

| CCP2CON              | 1Dh         | CVRCON                        | 9Dh       |                     | 11Dh          |                         | 19 |

| ADRESH               | 1Eh         | ADRESL                        | 9Eh       |                     | 11Eh          |                         | 19 |

| ADCON0               | 1Fh         | ADCON1                        | 9Fh       |                     | 11Fh          |                         | 19 |

|                      | 20h         |                               | A0h       |                     | 120h          |                         | 1A |

|                      |             | General                       |           | General             |               | General                 |    |

| General              |             | Purpose                       |           | Purpose             |               | Purpose                 |    |

| Purpose              |             | Register                      |           | Register            |               | Register                |    |

| Register             |             | 80 Bytes                      |           | 80 Bytes            |               | 80 Bytes                |    |

| 96 Bytes             |             |                               | EFh       |                     | 16Fh          |                         | 1E |

|                      |             | accesses                      | F0h       | 20222202            | 170h          | accesses                | 1F |

|                      |             | 70h-7Fh                       |           | accesses<br>70h-7Fh |               | 70h - 7Fh               |    |

| <b>_</b>             | 7Fh         |                               | FFh       |                     | 17Fh          |                         | 1F |

| Bank 0               |             | Bank 1                        |           | Bank 2              |               | Bank 3                  |    |

| Unimple              | mented d    | ata memory locati             | ons. read | <b>as</b> '0'.      |               |                         |    |

|                      | iysical reg | -                             |           |                     |               |                         |    |

| Address              | Name       | Bit 7                | Bit 6         | Bit 5                     | Bit 4          | Bit 3        | Bit 2            | Bit 1         | Bit 0        | Value on:<br>POR, BOR | Details<br>on page |

|----------------------|------------|----------------------|---------------|---------------------------|----------------|--------------|------------------|---------------|--------------|-----------------------|--------------------|

| Bank 1               |            |                      |               |                           |                |              |                  |               |              |                       |                    |

| 80h <sup>(3)</sup>   | INDF       | Addressing           | this locatio  | n uses cont               | ents of FSR t  | o address d  | ata memory (     | not a physic  | al register) | 0000 0000             | 31, 150            |

| 81h                  | OPTION_REG | RBPU                 | INTEDG        | TOCS                      | T0SE           | PSA          | PS2              | PS1           | PS0          | 1111 1111             | 23, 150            |

| 82h <sup>(3)</sup>   | PCL        | Program C            | ounter (PC)   | Least Sign                | ificant Byte   |              |                  |               |              | 0000 0000             | 30, 150            |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1           | RP0                       | TO             | PD           | Z                | DC            | С            | 0001 1xxx             | 22, 150            |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ta Memory     | Address Po                | inter          |              |                  |               |              | xxxx xxxx             | 31, 150            |

| 85h                  | TRISA      |                      |               | PORTA Da                  | ta Direction F | Register     |                  |               |              | 11 1111               | 43, 150            |

| 86h                  | TRISB      | PORTB Da             | ata Direction | Register                  |                |              |                  |               |              | 1111 1111             | 45, 150            |

| 87h                  | TRISC      | PORTC Da             | ata Directior | Register                  |                |              |                  |               |              | 1111 1111             | 47, 150            |

| 88h <sup>(4)</sup>   | TRISD      | PORTD Da             | ata Directior | n Register                |                |              |                  |               |              | 1111 1111             | 48, 151            |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF           | IBOV                      | PSPMODE        |              | PORTE Dat        | a Direction I | bits         | 0000 -111             | 50, 151            |

| 8Ah <sup>(1,3)</sup> | PCLATH     | —                    |               |                           | Write Buffer   | for the uppe | er 5 bits of the | e Program C   | Counter      | 0 0000                | 30, 150            |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE          | TMR0IE                    | INTE           | RBIE         | TMR0IF           | INTF          | RBIF         | 0000 000x             | 24, 150            |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE          | RCIE                      | TXIE           | SSPIE        | CCP1IE           | TMR2IE        | TMR1IE       | 0000 0000             | 25, 151            |

| 8Dh                  | PIE2       | —                    | CMIE          |                           | EEIE           | BCLIE        | —                | _             | CCP2IE       | -0-0 00               | 27, 151            |

| 8Eh                  | PCON       | _                    |               |                           | _              |              | _                | POR           | BOR          | dd                    | 29, 151            |

| 8Fh                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 90h                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | _                  |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT       | ACKDT                     | ACKEN          | RCEN         | PEN              | RSEN          | SEN          | 0000 0000             | 83, 151            |

| 92h                  | PR2        | Timer2 Per           | riod Registe  | r                         |                |              |                  |               |              | 1111 1111             | 62, 151            |

| 93h                  | SSPADD     | Synchrono            | us Serial Po  | ort (I <sup>2</sup> C mod | e) Address R   | egister      |                  |               |              | 0000 0000             | 79, 151            |

| 94h                  | SSPSTAT    | SMP                  | CKE           | D/A                       | Р              | S            | R/W              | UA            | BF           | 0000 0000             | 79, 151            |

| 95h                  | —          | Unimpleme            | ented         |                           | •              |              |                  |               |              | —                     |                    |

| 96h                  | _          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 97h                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 98h                  | TXSTA      | CSRC                 | TX9           | TXEN                      | SYNC           | _            | BRGH             | TRMT          | TX9D         | 0000 -010             | 111, 151           |

| 99h                  | SPBRG      | Baud Rate            | Generator     | Register                  | •              |              |                  |               |              | 0000 0000             | 113, 151           |

| 9Ah                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | _                  |

| 9Bh                  | _          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | —                  |

| 9Ch                  | CMCON      | C2OUT                | C1OUT         | C2INV                     | C1INV          | CIS          | CM2              | CM1           | CM0          | 0000 0111             | 135, 151           |

| 9Dh                  | CVRCON     | CVREN                | CVROE         | CVRR                      | _              | CVR3         | CVR2             | CVR1          | CVR0         | 000- 0000             | 141, 151           |

| 9Eh                  | ADRESL     | A/D Result           | Register Lo   | w Byte                    |                |              |                  |               |              | xxxx xxxx             | 133, 151           |

| 9Fh                  | ADCON1     | ADFM                 | ADCS2         | _                         | _              | PCFG3        | PCFG2            | PCFG1         | PCFG0        | 00 0000               | 128, 151           |

####

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Legend: Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

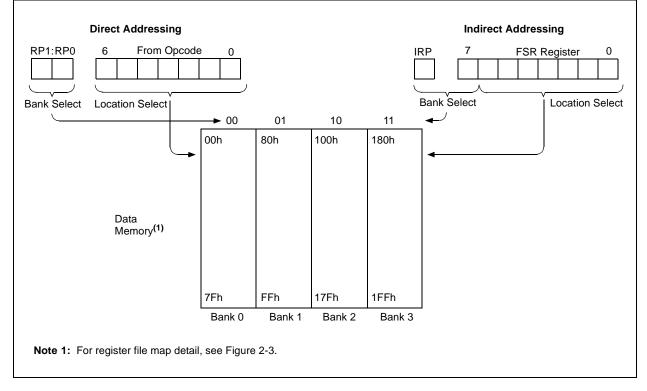

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

| 1        |       |       |                      |

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

| TABLE 8-4: | <b>REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1</b> |

|------------|--------------------------------------------------------------|

|------------|--------------------------------------------------------------|

| Address                | Name    | Bit 7                | Bit 6                                | Bit 5        | Bit 4         | Bit 3          | Bit 2      | Bit 1      | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|---------|----------------------|--------------------------------------|--------------|---------------|----------------|------------|------------|--------|-----------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                 | TMR0IE       | INTE          | RBIE           | TMR0IF     | INTF       | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                 | RCIF         | TXIF          | SSPIF          | CCP1IF     | TMR2IF     | TMR1IF | 0000 0000             | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | —                                    | _            | _             | —              | —          | _          | CCP2IF | 0                     | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                 | RCIE         | TXIE          | SSPIE          | CCP1IE     | TMR2IE     | TMR1IE | 0000 0000             | 0000 0000                       |

| 8Dh                    | PIE2    | —                    | —                                    | _            | _             | —              | —          | _          | CCP2IE | 0                     | 0                               |

| 87h                    | TRISC   | PORTC D              | ata Direc                            | tion Registe | er            |                |            |            |        | 1111 1111             | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding R            | egister fo                           | r the Least  | Significant I | Byte of the 1  | 6-bit TMR' | 1 Register |        | xxxx xxxx             | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister fo                           | r the Most S | Significant E | Byte of the 10 | 6-bit TMR1 | Register   |        | xxxx xxxx             | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                    | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS     | TMR10N | 00 0000               | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | Compare/F                            | PWM Regis    | ter 1 (LSB)   |                |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | Compare/F                            | PWM Regis    | ter 1 (MSB)   | )              |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 17h                    | CCP1CON | _                    | _                                    | CCP1X        | CCP1Y         | CCP1M3         | CCP1M2     | CCP1M1     | CCP1M0 | 00 0000               | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |              |               |                |            |            |        |                       | uuuu uuuu                       |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/F                            | PWM Regis    | ter 2 (MSB)   | )              |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 1Dh                    | CCP2CON | _                    |                                      | CCP2X        | CCP2Y         | CCP2M3         | CCP2M2     | CCP2M1     | CCP2M0 | 00 0000               | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: The PSP is not implemented on 28-pin devices; always maintain these bits clear.

|                        | =       |                      |                                      | •           |           |         |        |         |         | _             |      |       |                        |

|------------------------|---------|----------------------|--------------------------------------|-------------|-----------|---------|--------|---------|---------|---------------|------|-------|------------------------|

| Address                | Name    | Bit 7                | Bit 6                                | Bit 5       | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | all o | ie on<br>other<br>sets |

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                 | TMR0IE      | INTE      | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000  | 000u                   |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                 | RCIF        | TXIF      | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000  | 0000                   |

| 0Dh                    | PIR2    | _                    | _                                    | _           | _         | _       | _      | _       | CCP2IF  |               | 0    |       | 0                      |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                 | RCIE        | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000  | 0000                   |

| 8Dh                    | PIE2    | —                    | —                                    | _           | —         | _       | —      | —       | CCP2IE  |               | 0    |       | 0                      |

| 87h                    | TRISC   | PORTC D              | Data Directio                        | n Register  |           |         |        |         |         | 1111          | 1111 | 1111  | 1111                   |

| 11h                    | TMR2    | Timer2 M             | odule's Reg                          | ister       |           |         |        |         |         | 0000          | 0000 | 0000  | 0000                   |

| 92h                    | PR2     | Timer2 M             | odule's Peri                         | od Register |           |         |        |         |         | 1111          | 1111 | 1111  | 1111                   |

| 12h                    | T2CON   | _                    | TOUTPS3                              | TOUTPS2     | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                   |

| 15h                    | CCPR1L  | Capture/C            | Compare/PV                           | VM Registe  | r 1 (LSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 16h                    | CCPR1H  | Capture/C            | Compare/PV                           | VM Registe  | r 1 (MSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 17h                    | CCP1CON | _                    | _                                    | CCP1X       | CCP1Y     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                   |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |             |           |         |        |         |         |               |      | uuuu  | uuuu                   |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/PV                           | VM Registe  | r 2 (MSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 1Dh                    | CCP2CON | _                    | —                                    | CCP2X       | CCP2Y     | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00            | 0000 | 00    | 0000                   |

TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

NOTES:

#### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                                                                                               | R/W-0           | R-0             | R-0          | R-0          | R-0           | R-0          | R-0           |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|--------------|---------------|--------------|---------------|--|--|--|--|

|       | SMP                                                                                                 | CKE             | D/A             | Р            | S            | R/W           | UA           | BF            |  |  |  |  |

|       | bit 7                                                                                               |                 |                 |              |              |               |              | bit 0         |  |  |  |  |

| bit 7 | SMP: Sam                                                                                            | ple bit         |                 |              |              |               |              |               |  |  |  |  |

|       | SPI Master                                                                                          |                 |                 |              |              |               |              |               |  |  |  |  |

|       | 1 = Input data sampled at end of data output time                                                   |                 |                 |              |              |               |              |               |  |  |  |  |

|       | 0 = Input data sampled at middle of data output time                                                |                 |                 |              |              |               |              |               |  |  |  |  |

|       | SMP must                                                                                            | be cleared v    | when SPI is     | used in Slav | ve mode      |               |              |               |  |  |  |  |

| bit 6 |                                                                                                     | Clock Select    |                 |              | o modo.      |               |              |               |  |  |  |  |

|       | 1 = Transm                                                                                          | nit occurs on   | transition fr   | om active to | ldle clock s | state         |              |               |  |  |  |  |

|       | 0 = Transmit occurs on transition from Idle to active clock state                                   |                 |                 |              |              |               |              |               |  |  |  |  |

|       | Note:                                                                                               | Polarity of o   | clock state is  | s set by the | CKP bit (SS  | PCON1<4>      | ).           |               |  |  |  |  |

| bit 5 | D/A: Data/Address bit                                                                               |                 |                 |              |              |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                                            | c mode only.    |                 |              |              |               |              |               |  |  |  |  |

| bit 4 | P: Stop bit                                                                                         |                 |                 |              |              |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                                            | mode only.      | This bit is cle | ared when t  | he MSSP me   | odule is disa | bled, SSPEI  | N is cleared. |  |  |  |  |

| bit 3 | S: Start bit                                                                                        |                 |                 |              |              |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                                            | c mode only.    |                 |              |              |               |              |               |  |  |  |  |

| bit 2 | R/W: Read                                                                                           | I/Write bit inf | ormation        |              |              |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                                            | c mode only.    |                 |              |              |               |              |               |  |  |  |  |

| bit 1 | UA: Update                                                                                          | e Address b     | it              |              |              |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                                            | c mode only.    |                 |              |              |               |              |               |  |  |  |  |

| bit 0 | BF: Buffer                                                                                          | Full Status b   | oit (Receive    | mode only)   |              |               |              |               |  |  |  |  |

|       | BF: Buffer Full Status bit (Receive mode only) <ol> <li>Receive complete, SSPBUF is full</li> </ol> |                 |                 |              |              |               |              |               |  |  |  |  |

|       | 0 = Receiv                                                                                          | e not comple    | ete, SSPBU      | F is empty   |              |               |              |               |  |  |  |  |

|       | Legend:                                                                                             |                 |                 |              |              |               |              |               |  |  |  |  |

|       | R = Reada                                                                                           | ble bit         | W = W           | ritable bit  | U = Unim     | plemented     | bit, read as | '0'           |  |  |  |  |

|       | - n = Value                                                                                         | at POR          | '1' = B         | it is set    | '0' = Bit i  | s cleared     | x = Bit is ι | Inknown       |  |  |  |  |

### 9.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 9.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When

the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin      |

|---------|-------------------------------------------------------------|

|         | control enabled (SSPCON< $3:0> = 0100$ ),                   |

|         | the SPI module will reset if the $\overline{SS}$ pin is set |

|         | to VDD.                                                     |

2: If the SPI is used in Slave Mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#

### FIGURE 9-4: SLAVE SYNCHRONIZATION WAVEFORM

#### 9.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the No Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See **Section 9.4.4** "**Clock Stretching**" for more detail.

#### 9.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see **Section 9.4.4 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

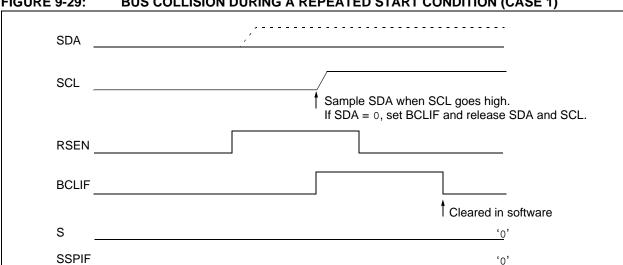

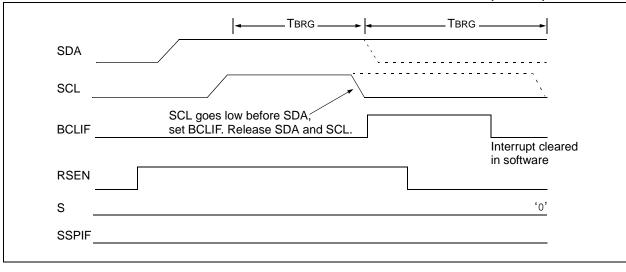

#### Bus Collision During a Repeated 9.4.17.2 Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 9-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 9-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 9-29: **BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)**

## 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit, CSRC (TXSTA<7>).

#### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a readonly bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit, TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected since the BRG is kept in Reset when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to highimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a high-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from High-Impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

### 14.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit 0 is the Brown-out Reset Status bit, BOR. The BOR bit is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if it has been cleared, indicating that a BOR has occurred.

When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit 1 is the Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power             | -up              | Brown-out         | Wake-up from |

|--------------------------|-------------------|------------------|-------------------|--------------|

|                          | <b>PWRTE =</b> 0  | <b>PWRTE</b> = 1 | Brown-out         | Sleep        |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc        | 72 ms + 1024 Tosc | 1024 Tosc    |

| RC                       | 72 ms             | —                | 72 ms             | —            |

#### TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                                               |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |

**Legend:** x = don't care, u = unchanged

### TABLE 14-5: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### 14.14 Power-down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (Status<3>) is cleared, the TO (Status<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, powerdown the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 14.14.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the Status register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (Start/Stop) bit detect interrupt.

- 6. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion.

- 10. Comparator output changes state.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 14.14.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| FIGURE 14-12: | WAKE-UP FROM SLEEP THROUGH INTERRUPT |

|---------------|--------------------------------------|

|               |                                      |

| OSC1 /                     | 21   Q2   Q3   Q4<br>\ | Q1 Q2 Q3 Q4  |                       | ¦Q1 Q2 Q3 Q4<br>∞∞∞∭/\ |                   | Q1   Q2   Q3   Q4                     | Q1 Q2 Q3 Q4 |

|----------------------------|------------------------|--------------|-----------------------|------------------------|-------------------|---------------------------------------|-------------|

| CLKO <sup>(4)</sup>        |                        | /            | -\( <b></b>           | ST(2)                  | -\/               | \/                                    | \/          |

| INT pin                    |                        |              |                       | 1<br>1                 | 1<br>1            | , , , , , , , , , , , , , , , , , , , | 1           |

| INTF Flag<br>(INTCON<1>) — |                        |              | <u>`</u>              |                        | Interrupt Latency | (2)                                   | ·<br>       |

| GIE bit<br>(INTCON<7>)     |                        |              | Processor in<br>Sleep |                        | <u> </u>          | 1 1<br>1 1<br>1                       | •<br>•<br>• |

| INSTRUCTION I              | FLOW                   |              | Oleep                 |                        | 1<br>1            | I I                                   |             |

| PC X                       | PC                     | PC+1         | X PC+2                | PC+2                   | X PC + 2          | X 0004h                               | X 0005h     |

| Instruction {<br>Fetched   | nst(PC) = Sleep        | Inst(PC + 1) | 1<br>1<br>1           | Inst(PC + 2)           | 1<br>1<br>1       | Inst(0004h)                           | Inst(0005h) |

| Instruction ∫              | Inst(PC - 1)           | Sleep        | 1<br>1                | Inst(PC + 1)           | Dummy cycle       | Dummy cycle                           | Inst(0004h) |

Note 1: XT, HS or LP Oscillator mode assumed.

2: TOST = 1024 TOSC (drawing not to scale). This delay will not be there for RC Oscillator mode.

3: GIE = 1 assumed. In this case, after wake- up, the processor jumps to the interrupt routine.

4: CLKO is not available in these oscillator modes but shown here for timing reference.

### 14.15 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the in-circuit debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 14-8 shows which features are consumed by the background debugger.

|  | TABLE 14-8: | DEBUGGER RESOURCES |

|--|-------------|--------------------|

|--|-------------|--------------------|

| I/O pins       | RB6, RB7                                   |

|----------------|--------------------------------------------|

| Stack          | 1 level                                    |

| Program Memory | Address 0000h must be NOP                  |

|                | Last 100h words                            |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB-0x1EF |

To use the in-circuit debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the in-circuit debugger module available from Microchip or one of the third party development tool companies.

### 14.16 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

### 14.17 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

If GIE = 0, execution will continue in-line.

### 16.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/Demultiplexed and 16-bit Memory modes. The board includes 2 Mb external Flash memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

## 16.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PIC microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature onboard LIN transceivers. A PIC16F874 Flash microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

# 16.22 PICkit<sup>™</sup> 1 Flash Starter Kit

A complete "development system in a box", the PICkit Flash Starter Kit includes a convenient multi-section board for programming, evaluation and development of 8/14-pin Flash PIC<sup>®</sup> microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB<sup>®</sup> IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin Flash PIC<sup>®</sup> Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin Flash PIC microcontrollers, as well as many future planned devices.

## 16.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

# 16.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

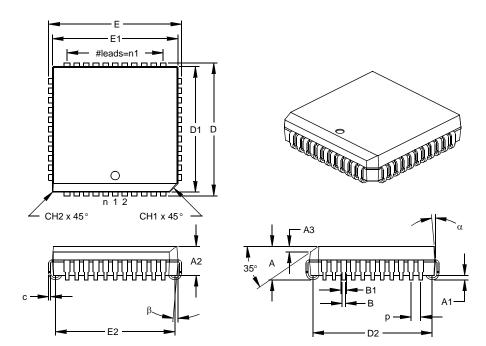

# 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |      | INCHES* |      | Ν     | IILLIMETERS |       |

|--------------------------|-----------|------|---------|------|-------|-------------|-------|

| Dimensio                 | on Limits | MIN  | NOM     | MAX  | MIN   | NOM         | MAX   |

| Number of Pins           | n         |      | 44      |      |       | 44          |       |

| Pitch                    | р         |      | .050    |      |       | 1.27        |       |

| Pins per Side            | n1        |      | 11      |      |       | 11          |       |

| Overall Height           | А         | .165 | .173    | .180 | 4.19  | 4.39        | 4.57  |

| Molded Package Thickness | A2        | .145 | .153    | .160 | 3.68  | 3.87        | 4.06  |

| Standoff §               | A1        | .020 | .028    | .035 | 0.51  | 0.71        | 0.89  |

| Side 1 Chamfer Height    | A3        | .024 | .029    | .034 | 0.61  | 0.74        | 0.86  |

| Corner Chamfer 1         | CH1       | .040 | .045    | .050 | 1.02  | 1.14        | 1.27  |

| Corner Chamfer (others)  | CH2       | .000 | .005    | .010 | 0.00  | 0.13        | 0.25  |

| Overall Width            | Е         | .685 | .690    | .695 | 17.40 | 17.53       | 17.65 |

| Overall Length           | D         | .685 | .690    | .695 | 17.40 | 17.53       | 17.65 |

| Molded Package Width     | E1        | .650 | .653    | .656 | 16.51 | 16.59       | 16.66 |

| Molded Package Length    | D1        | .650 | .653    | .656 | 16.51 | 16.59       | 16.66 |

| Footprint Width          | E2        | .590 | .620    | .630 | 14.99 | 15.75       | 16.00 |

| Footprint Length         | D2        | .590 | .620    | .630 | 14.99 | 15.75       | 16.00 |

| Lead Thickness           | С         | .008 | .011    | .013 | 0.20  | 0.27        | 0.33  |

| Upper Lead Width         | B1        | .026 | .029    | .032 | 0.66  | 0.74        | 0.81  |

| Lower Lead Width         | В         | .013 | .020    | .021 | 0.33  | 0.51        | 0.53  |

| Mold Draft Angle Top     | α         | 0    | 5       | 10   | 0     | 5           | 10    |

| Mold Draft Angle Bottom  | β         | 0    | 5       | 10   | 0     | 5           | 10    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-047

Drawing No. C04-048

| MPLAB ICE 4000 High-Performance Universal    |

|----------------------------------------------|

| In-Circuit Emulator169                       |

| MPLAB Integrated Development                 |

| Environment Software167                      |

| MPLINK Object Linker/MPLIB Object Librarian  |

| MSSP71                                       |

| I <sup>2</sup> C Mode. See I <sup>2</sup> C. |

| SPI Mode71                                   |

| SPI Mode. See SPI.                           |

| MSSP Module                                  |

| Clock Stretching90                           |

| Clock Synchronization and the CKP Bit91      |

| Control Registers (General)71                |

| Operation84                                  |

| Overview71                                   |

| SPI Master Mode76                            |

| SPI Slave Mode77                             |

| SSPBUF                                       |

| SSPSR76                                      |

| Multi-Master Mode105                         |

# 0

| Opcode Field Descriptions       |               |

|---------------------------------|---------------|

| OPTION_REG Register             |               |

| INTEDG Bit                      |               |

| PS2:PS0 Bits                    |               |

| PSA Bit                         |               |

| RBPU Bit                        |               |

| T0CS Bit                        |               |

| T0SE Bit                        |               |

| OSC1/CLKI Pin                   |               |

| OSC2/CLKO Pin                   |               |

| Oscillator Configuration        |               |

| HS                              | 145, 149      |

| LP                              |               |

| RC                              | 145, 146, 149 |

| XT                              |               |

| Oscillator Selection            |               |

| Oscillator Start-up Timer (OST) |               |

| Oscillator, WDT                 |               |

| Oscillators                     |               |

| Capacitor Selection             |               |

| Ceramic Resonator Selection     |               |

| Crystal and Ceramic Resonators  |               |

| RC                              |               |

|                                 |               |

# Ρ

| Package Information                      |                 |

|------------------------------------------|-----------------|

| Marking                                  |                 |

| Packaging Information                    |                 |

| Paging, Program Memory                   |                 |

| Parallel Slave Port (PSP)                | 13, 48, 51      |

| Associated Registers                     |                 |

| RE0/RD/AN5 Pin                           |                 |

| RE1/WR/AN6 Pin                           | 49, 51          |

| RE2/CS/AN7 Pin                           |                 |

| Select (PSPMODE Bit)                     | .48, 49, 50, 51 |

| Parallel Slave Port Requirements         |                 |

| (PIC16F874A/ 877A Only)                  |                 |

| PCL Register                             |                 |

| PCLATH Register                          | 19, 20, 30      |

| PCON Register                            |                 |

| BOR Bit                                  |                 |

| POR Bit                                  | 29              |

| PIC16F87XA Product Identification System |                 |

| PICkit 1 Flash Starter Kit               | 171             |

| PICSTART Plus Development Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| PIE1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |

| PIE2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20, 27                                                 |

| Pinout Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

| PIC16F873A/PIC16F876A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |

| PIR1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |

| PIR2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |